51单片机外扩RAM

- 格式:doc

- 大小:76.50 KB

- 文档页数:4

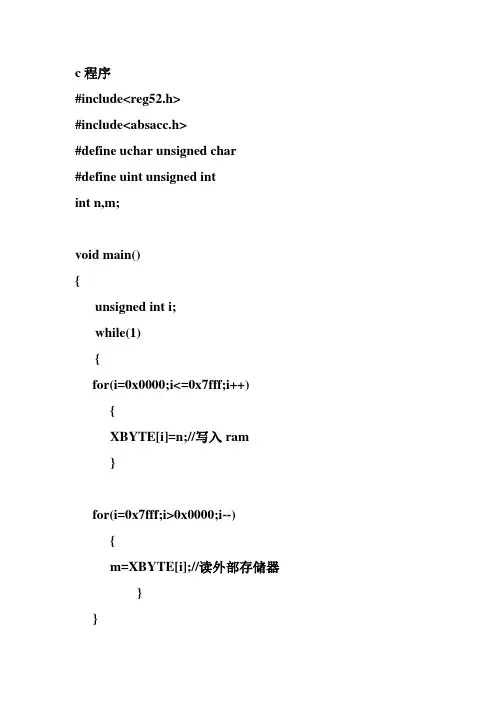

c程序#include<reg52.h>#include<absacc.h>#define uchar unsigned char#define uint unsigned intint n,m;void main(){unsigned int i;while(1){for(i=0x0000;i<=0x7fff;i++){XBYTE[i]=n;//写入ram}for(i=0x7fff;i>0x0000;i--){m=XBYTE[i];//读外部存储器}}}62256外部ram芯片相关知识:XBYTE是一个地址指针(可当成一个数组名或数组的首地址),它在文件absacc.h中由系统定义,指向外部RAM(包括I/O口)的0000H单元,XBYTE后面的中括号[ ]0x2000H 是指数组首地址0000H的偏移地址,即用XBYTE[0x2000]可访问偏移地址为0x2000的I/O端口。

这个主要是在用C51的P0,P2口做外部扩展时使用,其中XBYTE [0x0002],P2口对应于地址高位,P0口对应于地址低位。

一般P2口用于控制信号,P0口作为数据通道。

比如:P2.7接WR,P2.6接RD,P2.5接CS,那么就可以确定个外部RAM的一个地址,想往外部RAM的一个地址写一个字节时,地址可以定为XBYTE [0x4000],其中WR,CS为低,RD为高,那就是高位的4,当然其余的可以根据情况自己定,然后通过XBYTE [0x4000] = 57;这赋值语句,就可以把57写到外部RAM的0x4000处了,此地址对应一个字节。

XBYTE 的作用,可以用来定义绝对地址,是P0口和P2口的,其中P2口对应的是高位,P0口对应的是低位如XBYTE[0x1234] = 0x56;则等价于mov dptr,#1234hmov @dptr,#56h谢谢大家。

51单片机对外部ram的存取用#include "absacc.h"头文件,对于典型的电路接法,直接写ram=XBYTE[0x0000]或XB YTE[0x0000]=ram就能完成对ram的读写么,外部WR,OE,ALE信号就不用控制了么。

是不是先前要有什么设置。

最好举一个完整的例子说明一下,对外部的电路也做一下简单的说明,控制信号都是怎么接的,接法不一样对应的程序一改怎么变?初学者,渴望赐教。

提问者采纳是的。

对于典型电路接法,对应的WR、OE、ALE信号引脚接在RAM芯片对应引脚,单片机会自动配置各个引脚的时序,以完成XBYTE指令直接访问外部RAM的功能。

这里您所担心的对外部WR,OE,ALE信号的控制实际上是把典型电路接法与用单个引脚模拟端口外接RAM的使用方法混淆了。

比如89C2051单片机,其外部引脚没有P0口和WR、RD、OE、ALE这些引脚,某些情况下非得需要其配合外置RAM使用时,需要定义某些IO脚(譬如P1)模拟为数据接口、某些IO脚(譬如P1、P3)模拟为地址接口、某些IO模拟WR、RD、OE、ALE功能。

这个时候就需要控制了:先准备好要告诉RAM给它发送地址了(控制模拟ALE那个引脚的电平),然后控制模拟WR的那个引脚,准备告诉RAM你是要给它写地址;然后往地址接口上放地址数据,准备告诉RAM读什么地址(控制模拟的P0、P2口);片选通知RAM来读取地址(模拟OE的那个引脚给片选电平,通常低电平为选中);等待RAM响应后,转换WR和RD的电平读出RAM在上述地址中存储的数据。

大致如此,你可以在相应的学习板或者自己搭建的板子上试试~。

51 单片机资源扩展:扩展片外RAM

上一文中扩展了单片机的程序存储器,4KB 存储空间提升到64KB。

其

实,4K 的代码空间还凑合,但是51 自带的256B 数据存储空间使用起来还

真紧张,其中留给用户的连128B 都不到,所以不得不扩展片外RAM。

扩展RAM 方法和扩展ROM 差不多,都是占用P0/P2 口做地址线,同时P0 用锁

存器74373 分时复用地址和数据信号。

以前扩展RAM 是用汇编语言访问存储器,好处是定位精准,指哪打哪,

坏处就是:程序规模一大就有点难维护了,所以还得改用C 实现。

对应于汇编语言用R1,R0/DPTR 访问外部RAM,keil C 扩展了存储类型,增加了如pdata(等同用movx @Rn 访问方式)/xdata(等同于movx @DPTR 访问方式)存储类型用于访问片外ram。

同时,还提供了绝对地址访问的宏,

如PBYTE/XBYTE,查看定义:

[cpp] view plain copy#define PBYTE((unsigned char volatile pdata*)0);

#define XBYTE((unsigned char volatile xdata*)0);。

51MCU内部有RAM,ROM,不同于8031。

尽管如今的增强行51MCU的内部RAM,ROM可能已经很大的空间。

但就技术而言,扩展RAM,ROM还是需要学会的。

对于不同的设计方案需求,扩展可能基于以下任何一种设计:A,只扩展RAMB,只扩展ROMC,扩展ROM,RAM****************************总线扩展时,P2口是否可用做普通IO口************************************这种扩展是基于总线扩展的,所以,P0P2口就已经不可以再做它用了(有网友提供信息,总线扩展P2还可以做普通IO口用,有两种可能:1,P2口复用,如同P1利用373锁存器。

2,在总线扩展时,只用到了低地址总线,P2口未用到。

就作为普通IO口应用。

由于技术还不到位,不做评论。

)*******************************************扩展RAM****程序************************************************扩展RAM,在程序中定义的xdata类型XBYTE类型等地址范围在外部RAM的变量,对其读写的过程。

用C51语言编写程序,且使用总线扩展的RAM,则时序电路不用考虑,WR RD等信号由编译器/硬件自动完成。

**************************************编译器设置*****************************************内部RAM:0x00~~0xFF外部RAM:0x0000~~0xFFFFRAM的地址虽重复,但是两个RAM是没有关系的,所以不会造成干扰使用了外部RAM,就在工程选项---off-chip xdata memory中设置start:0x0000 size:0xFFFF(根据具体的RAM大小设置size)。

*******************************扩展RAM时的变量定位及连续读取问题********************************* ROM,RAM的扩展时,需要用到变量的绝对地址定位,函数定位等。

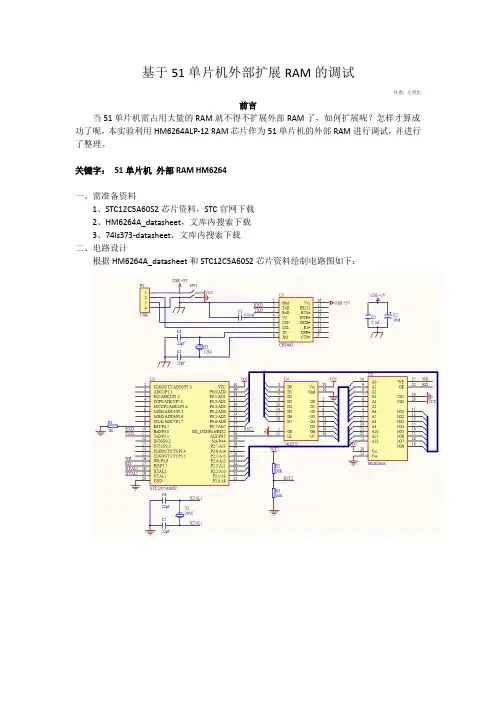

基于51单片机外部扩展RAM的调试作者:左厚臣前言当51单片机需占用大量的RAM就不得不扩展外部RAM了,如何扩展呢?怎样才算成功了呢,本实验利用HM6264ALP-12 RAM芯片作为51单片机的外部RAM进行调试,并进行了整理。

关键字:51单片机外部RAM HM6264一、需准备资料1、STC12C5A60S2芯片资料,STC官网下载2、HM6264A_datasheet,文库内搜索下载3、74ls373-datasheet,文库内搜索下载二、电路设计根据HM6264A_datasheet和STC12C5A60S2芯片资料绘制电路图如下:三、Keil编译器设置使用外部扩展RAM需在片外Xdata存储内写上外部RAM的起始地址及RAM大小,否则在编译程序时可能会报错。

四、调试程序根据HM6264A_datasheet和STC12C5A60S2芯片资料可以看出,HM6264ALP写时序读时序及地址建立时间保持时间都是纳秒级的,而STC12C5A60S2基本都是微秒级的,所以51单片机的这些时序无需改动,程序如下:#include <STC12C5A60S2.H>#define u8 unsigned char#define u16 unsigned int#define EXTRAM 2//AUXR寄存器EXTRAM位//EXTRAM =0使用内部扩展RAM//EXTRAM =1使用外部扩展RAMu16 y;u8 xdata x[8192];void main(){x[8189]=0x11;x[8190]=0x22;x[8191]=0x33;x[8192]=0x44;AUXR |= (1<<EXTRAM); //使用外部扩展RAM TMOD = 0x20;SM0 = 0;//SM1 = 1;//串口1工作方式1TH1 = 243;TR1 = 1;//启动定时器1TI=0;for(y=8189;y<8193;y++){SBUF = x[y];while(TI==0);TI=0;}while(1);}串口打印结果如下:符合程序要求。

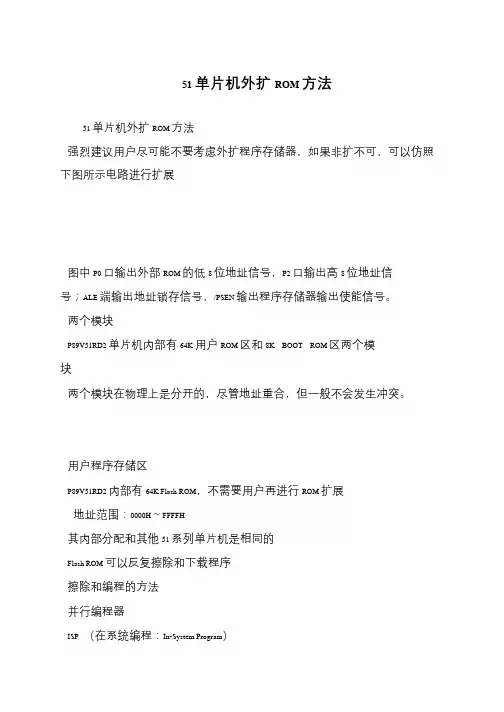

51 单片机外扩ROM 方法

51 单片机外扩ROM 方法

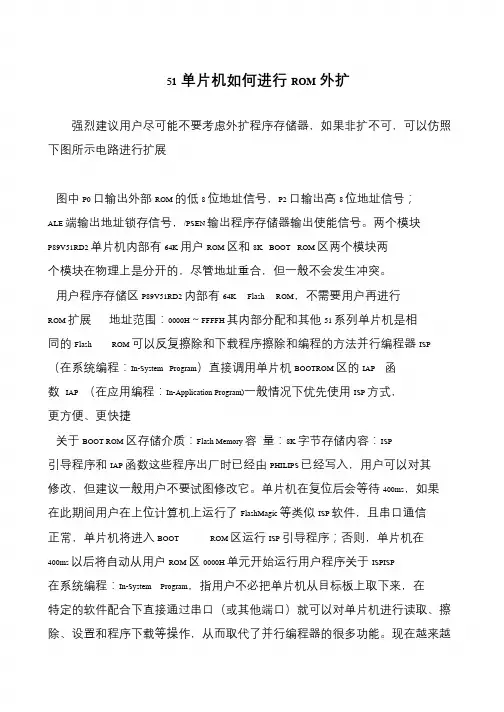

强烈建议用户尽可能不要考虑外扩程序存储器,如果非扩不可,可以仿照

下图所示电路进行扩展

图中P0 口输出外部ROM 的低8 位地址信号,P2 口输出高8 位地址信

号;ALE 端输出地址锁存信号,/PSEN 输出程序存储器输出使能信号。

两个模块

P89V51RD2 单片机内部有64K 用户ROM 区和8K BOOT ROM 区两个模块

两个模块在物理上是分开的,尽管地址重合,但一般不会发生冲突。

用户程序存储区

P89V51RD2 内部有64K Flash ROM,不需要用户再进行ROM 扩展

地址范围:0000H~FFFFH

其内部分配和其他51 系列单片机是相同的

Flash ROM 可以反复擦除和下载程序

擦除和编程的方法

并行编程器

ISP (在系统编程:In-System Program)。

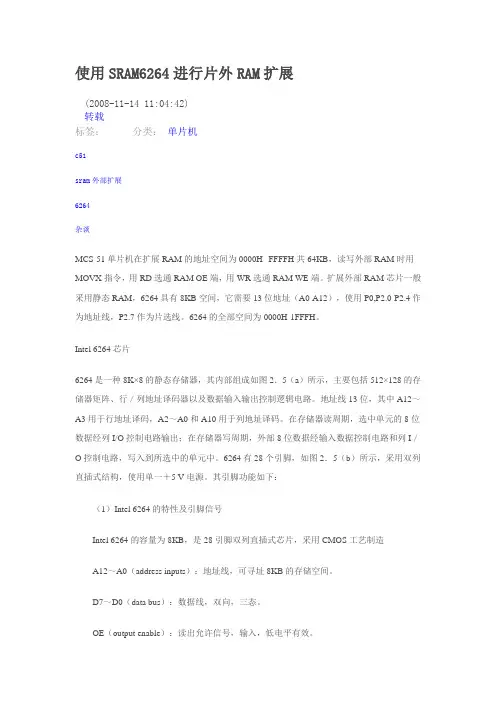

使用SRAM6264进行片外RAM扩展(2008-11-14 11:04:42)转载标签:分类:单片机c51sram外部扩展6264杂谈MCS-51单片机在扩展RAM的地址空间为0000H--FFFFH共64KB,读写外部RAM时用MOVX指令,用RD选通RAM OE端,用WR选通RAM WE端。

扩展外部RAM芯片一般采用静态RAM,6264具有8KB空间,它需要13位地址(A0-A12),使用P0,P2.0-P2.4作为地址线,P2.7作为片选线。

6264的全部空间为0000H-1FFFH。

Intel 6264芯片6264是一种8K×8的静态存储器,其内部组成如图2.5(a)所示,主要包括512×128的存储器矩阵、行/列地址译码器以及数据输入输出控制逻辑电路。

地址线13位,其中A12~A3用于行地址译码,A2~A0和A10用于列地址译码。

在存储器读周期,选中单元的8位数据经列I/O控制电路输出;在存储器写周期,外部8位数据经输入数据控制电路和列I/O控制电路,写入到所选中的单元中。

6264有28个引脚,如图2.5(b)所示,采用双列直插式结构,使用单一+5 V电源。

其引脚功能如下:(1)Intel 6264的特性及引脚信号Intel 6264的容量为8KB,是28引脚双列直插式芯片,采用CMOS工艺制造A12~A0(address inputs):地址线,可寻址8KB的存储空间。

D7~D0(data bus):数据线,双向,三态。

OE(output enable):读出允许信号,输入,低电平有效。

WE(write enable):写允许信号,输入,低电平有效。

CE1(chip enable):片选信号1,输入,在读/写方式时为低电平。

CE2(chip enable):片选信号2,输入,在读/写方式时为高电平。

VCC:+5V工作电压。

GND:信号地。

图2.5 6264的内部结构图及引脚图6264的工作方式如表2.2所示。

51单片机如何进行ROM外扩强烈建议用户尽可能不要考虑外扩程序存储器,如果非扩不可,可以仿照下图所示电路进行扩展图中P0 口输出外部ROM 的低8 位地址信号,P2 口输出高8 位地址信号;ALE 端输出地址锁存信号,/PSEN 输出程序存储器输出使能信号。

两个模块P89V51RD2 单片机内部有64K 用户ROM 区和8K BOOT ROM 区两个模块两个模块在物理上是分开的,尽管地址重合,但一般不会发生冲突。

用户程序存储区P89V51RD2 内部有64K Flash ROM,不需要用户再进行ROM 扩展地址范围:0000H~FFFFH 其内部分配和其他51 系列单片机是相同的Flash ROM 可以反复擦除和下载程序擦除和编程的方法并行编程器ISP (在系统编程:In-System Program)直接调用单片机BOOTROM 区的IAP 函数IAP (在应用编程:In-Application Program)一般情况下优先使用ISP 方式,更方便、更快捷关于BOOT ROM 区存储介质:Flash Memory 容量:8K 字节存储内容:ISP 引导程序和IAP 函数这些程序出厂时已经由PHILIPS 已经写入,用户可以对其修改,但建议一般用户不要试图修改它。

单片机在复位后会等待400ms,如果在此期间用户在上位计算机上运行了FlashMagic 等类似ISP 软件,且串口通信正常,单片机将进入BOOT ROM 区运行ISP 引导程序;否则,单片机在400ms 以后将自动从用户ROM 区0000H 单元开始运行用户程序关于ISPISP 在系统编程:In-System Program,指用户不必把单片机从目标板上取下来,在特定的软件配合下直接通过串口(或其他端口)就可以对单片机进行读取、擦除、设置和程序下载等操作,从而取代了并行编程器的很多功能。

现在越来越。

51单片机扩展外部RAM

今天这个是是以前做过的,没做成,扩展ROM的时候失败了~~不过今天主要的就是扩展外部的RAM,这个相对比较简单点,不想外部的ROM还要设置太多的编译器~~

单片机扩展外部RAM

一、扩展总线

1、简介(这种扩展是基于总线扩展的,所以,P0、P2口就已经不可以再做它用了)

1)数据总线宽度为8位,由P0口提供;

2)地址总线宽度为16位,可寻址范围2的16次,也就是64K。

低8位

A7~A0由P0口经地址锁存器提供,高8位A15~A8由P2口提供。

由于P0口是数据、地址分时复用,所以P0口输出的低8位必须用地址锁存器进行锁存;

3)控制总线由RD、WR、PSEN、ALE和EA等信号组成,用于读/写控制、片外RAM选通、地址锁存控制和片内、片外RAM选择。

地址锁存器一般选用带三态输出缓冲输出的8D锁存器74LS373。

2、片外RAM的操作时序

进行RAM的扩展,其扩展方法较为简单容易,这是由单片机的优良扩展性

能解决的。

单片机的地址总线为16位,扩展的片外RAM的做大容量为

64KB,地址为0000H~FFFFH。

1)由于51单片机采用不同的控制信号指令,尽管RAM和ROM地址是重

叠的,也不会发送混乱。

2)51单片机对片内和片外ROM的访问使用相同的指令,两者的选择是由。

如何利用51单片机同时扩展RAM和ROM

下面这个系统中,8051同时扩展片外程序存储器和数据存储器,两片存储器的片选信号都接地,即同时有效,也就是说,这两片存储器无需选择。

51同时扩展RAM和ROM

下面来分析这个问题,该系统中虽然有两片存储器,但由于两片存储器的输入,输入允许信号不同,程序存储器没有输入允许,其输出允许由8051的引脚PSEN控制,只有当程序存储器的片选信号和输出允许信号同时有效时,程序存储器的总线才挂接到CPU总线上。

否则,程序存储器的所有总线引脚都为高阻态,即相当于存储器与CPU总线断开。

数据存储器的输入允许端为WR,受控于8051的P3.6,输出允许信号为RD,受控于8051的P3.7,数据存储器要与8051挂接的条件是片选信号有效且输入,输出允许信号中至少有一个有效,可见,在该系统中,要使两片存。

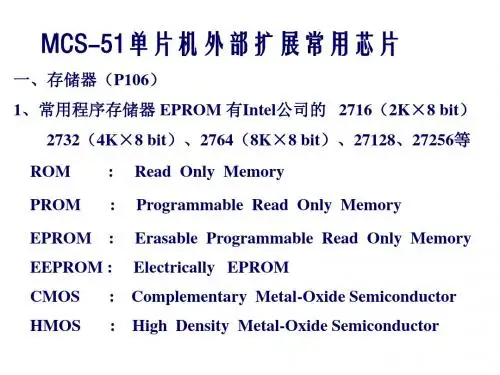

大学51系列单片机第八章习题及参考答案一、填空题1、MCS-51外扩ROM、RAM或I/O时,它的地址总线是P0、P2 口。

2、12根地址线可寻址 4 KB存储单元。

3、微机与外设间传送数据有程序传送、中断传送和DMA传送三种传送方式。

4、74LS138是具有3个输入的译码器芯片,其输出作为片选信号时,最多可以选中8 块芯片。

5、74LS273通常用来作简单输出接口扩展;而74LS244则常用来作简单输入接口扩展。

6、并行扩展存储器,产生片选信号的方式有线选法和译码法两种。

7、在存储器扩展中,无论是线选法还是译码法,最终都是为了扩展芯片的片选端提供信号。

8、起止范围为0000H-3FFFH的存储器的容量是16 KB。

9、11根地址线可选2KB 个存储单元,16KB存储单元需要14 根地址线。

10、32KB RAM存储器的首地址若为2000H,则末地址为9FFF H。

11、假定一个存储器有4096个存储单元,其首地址为0,则末地址为0FFFH 。

12、除地线公用外,6根地址线可选64 个地址,11根地址线可选2048 个地址。

13、单片机扩展的内容有程序存储器扩展、数据存储器扩展及I/O口的扩展等。

二、选择题1、当8031外扩程序存储器8KB时,需使用EPROM2716( C )A、2片B、3片C、4片D、5片2、某种存储器芯片是8KB*4/片,那么它的地址线根数是( C )A、11根B、12根C、13根D、14根3、74LS138芯片是( B )A、驱动器B、译码器C、锁存器D、编码器4、MCS-51外扩ROM、RAM和I/O口时,它的数据总线是( A )A、P0B、P1C、P2D、P35、6264芯片是( B )A、E2PROMB、RAMC、Flash ROMD、EPROM6、一个EPROM的地址有A0----A11引脚,它的容量为( B )。

A、2KBB、4KBC、11KBD、12KB7、单片机要扩展一片EPROM2764需占用( C )条P2口线。

51 单片机片外扩展RAM

一.概述

普通51 单片机可以片外扩展ROM 和RAM 各64K 字节的空间,在实际应用中很少扩展外部ROM,一般都是扩展RAM,因为普通51 单片机的内部RAM 实在太少,只有128-256 字节,处理数据量较大时往往不

够用。

而片外扩展RAM 需要占用P0 口、P2 口和P3.6、P3.7,消耗了18 个IO 口,导致IO 口又不够用。

为了解决以上矛盾,大容量的51 单片机(增强型51 单片机)应运而生,这种单片机一般内置1K-16K 的RAM 和16K-64K 的ROM,价格也相对昂贵。

在某些情况下,用普通51 单片机通过片外扩展RAM 要比直接使用增强型51 单片机更能节约成本。

所以,学习51 单片机片外扩展RAM 是很有必要的。

二.电路设计

在WSF-51DB 开发板上,扩展了32K RAM(HM62256B),地址锁存芯片用74HC573。

如果片外扩展RAM,P0 口作为数据和地址低字节的复用端口,不需要加上拉排阻,当然,加上拉排阻也没有影响。

需要注。

单片机外部RAM扩展模块

MCS-51系列单片机外部RAM为64K,在一些特殊场合下,远不能满足需要,

本文就AT89C51讨论MCS-51系列单片机大容量RAM的扩

首先介绍128K随机读取RAM HM628128。

HM628128

是32脚双列直插式128K静态随机读取RAM,它具有容

量大、功耗低、价格便宜、集成度高、速度快、设计和

使用方便等特点。

如若在系统中加入掉电保护电路,保

护数据有很高的可靠性,可以和EEPROM相媲美。

技术特性:

(1)最大存取时间为120ns;

(2)典型选通功耗75mW;典型未选通功耗10uW;

(3)使用单一5V电源供电;

(4)全静态存储器,不需要时钟及时序选通信号;

(5)周期时间与存取时间相等;

(6)采用三态输出电路,数据输入和输出端公用;

图6 HM628128外部引脚(7)所有输入和输出引脚均与TTL电平直接兼

容;

(8)有两个片选端,适合于低功耗使用,即为了保存信息,用电池作为后

备电源。

保存信息的最低电源电压Vcc=2V。

引脚安排及功能表:

图6是HM628128的外部引脚排列图,各引脚名称及功用分别如下:

A0~A16是17条地址线;I/O0~I/O7是8条双向数据线;CS1是片选1,低电平有效,CS2是片选2,高电平有效;WR是写控制线,当CS1为低电平,CS2为高电平时,WR的上升沿将I/O0~I/O7上的数据写到A0~A16选中的存储单元

中;OE是读出允许端,低电平有效。

HM628128的功能表如表3所示。

其中,H表示高电平,L表示低电平,X表示任意状态

由于AT89C51直接外部RAM容量为64K,地址线为16条,其中低8位地址和数据分时复用,因此需要外部地址锁存器和ALE锁存信号来锁存低8位地址。

又由于AT89C51的外部数据和外设地址通用,若扩展外设必然占用数据地址。

因此本系统采用P2.7(A15)口来区分数据和外设:当P2.7(A15)口为高电平时,

选择外部数据;P2.7(A15)口为低电平时,则为外设。

因此,直接外部数据容量和外设数量都为32K ,可用地址线为15条。

本系统外部扩展RAM 为256K ,地址线18条。

要达到18条地址线,则必须扩展。

理论上可行方法很多,如以P1口的某几位作为最高位地址输出、外加锁存器锁存高位地址等。

本系统采用后者,以保留P1口,况且外设空间充裕。

扩展电路如图7所示:

图7 RAM 地址扩展电路

当读写外部数据时,首先应往高位地址锁存器中送入高位地址,然后再以DPTR 为间接地址访问外部数据,注意最高位地址应为1,即数据区最低地址为8000H 。

以下程序段演示了外部数据的读写。

……

MOV DPTR ,#0020H ;0020H 为高位地址锁存器的地址

MOV A ,#00H ;00H 表示第一个32K 空间

MOVX @DPTR ,A ;写入地址数据

MOV DPTR ,#8000H ;8000H 为每个32K 的第一个字节地址

MOVX A ,@DPTR ;从地址单元读取数据

……

若最后一句换为:

MOVX @DPTR ,A

则为向RAM 中写数据。

同时作者还利用HM628128的数据保持特性为其加入了掉电保护电路。

当主电源关闭时,备用电源发挥作用,这样RAM 内的数据就不会丢失。

其特性如表4所示。

译码器

地址总线

CS1 0V

图8 CS2控制数据保持时序

根据表4和图8可知,只要在系统上电或断电期间保证使HM628128的CS2立即变为低电平(CS2≤0.2V )或WR 立即变为高电平就可使其中的数据维持不变,图9可实现这一功能。

≥Vcc-0.2V

图9掉电保护电路

其原理如下:当系统正常时,电流通过D1向HM628128供电,同时向电池BT 充电,当系统电源切断时,将由电池供电。

上电时,系统电源对C1充电,在此期间CS2是输入要经过一定的延时后才能变为高电平,同时,由于U1、U2的电源是由系统电源对C2充电来建立的,这就保证了在上电时HM628128处于写静止状态。

在系统掉电瞬间,由于U1、U2由Vs供电,仍处于工作状态,电源掉电致使U1的输入立即变低,WR端变为低电平,从而禁止对HM628128的写入。

同时C1也通过D2和R2放电,从而使CS2变为低电平。

因此在掉电瞬间和掉电后,HM628128也处于写禁止状态。

经实践证明,本电路工作可靠,RAM中数据保存完整。