Lattice fpga工具约束参数详解

- 格式:xls

- 大小:31.50 KB

- 文档页数:5

FPGA管脚约束格式

FPGA(现场可编程门阵列)是一种灵活的集成电路,它可以根据用户的需求进行编程和配置。

在FPGA的设计和实现过程中,管脚约束是一个重要的环节。

管脚约束定义了FPGA内部逻辑块与外部接口之间的连接方式,以确保正确的数据传输和时序控制。

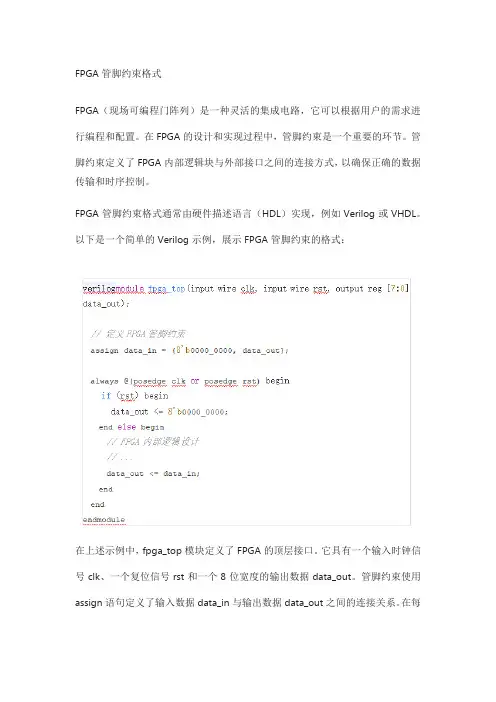

FPGA管脚约束格式通常由硬件描述语言(HDL)实现,例如Verilog或VHDL。

以下是一个简单的Verilog示例,展示FPGA管脚约束的格式:

在上述示例中,fpga_top模块定义了FPGA的顶层接口。

它具有一个输入时钟信号clk、一个复位信号rst和一个8位宽度的输出数据data_out。

管脚约束使用assign语句定义了输入数据data_in与输出数据data_out之间的连接关系。

在每

个时钟上升沿或复位信号上升沿时,内部逻辑会根据需要更新data_out的值,并通过管脚约束将其传递到外部接口。

需要注意的是,上述示例只是一个简单的示例,实际的FPGA管脚约束格式可能因具体的FPGA芯片和应用需求而有所不同。

因此,在实际应用中,需要根据具体的FPGA芯片和设计要求来编写相应的管脚约束代码。

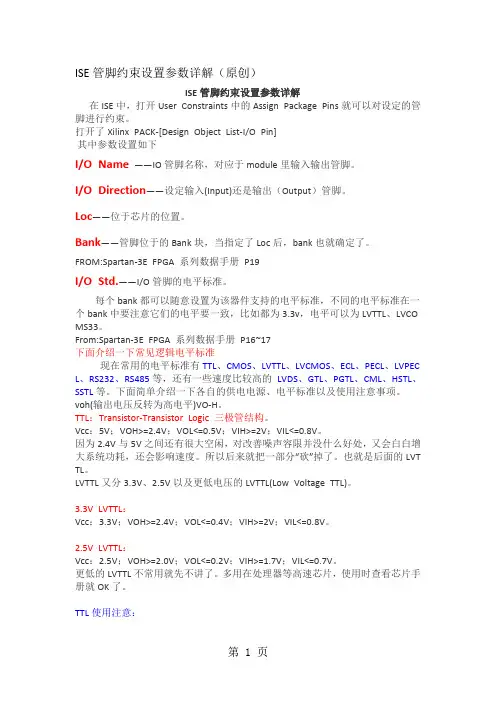

ISE管脚约束设置参数详解(原创)ISE管脚约束设置参数详解在ISE中,打开User Constraints中的Assign Package Pins就可以对设定的管脚进行约束。

打开了Xilinx PACK-[Design Object List-I/O Pin]其中参数设置如下I/O Name——IO管脚名称,对应于module里输入输出管脚。

I/O Direction——设定输入(Input)还是输出(Output)管脚。

Loc——位于芯片的位置。

Bank——管脚位于的Bank块,当指定了Loc后,bank也就确定了。

FROM:Spartan-3E FPGA 系列数据手册P19I/O Std.——I/O管脚的电平标准。

每个bank都可以随意设置为该器件支持的电平标准,不同的电平标准在一个bank中要注意它们的电平要一致,比如都为3.3v,电平可以为LVTTL、LVCO MS33。

From:Spartan-3E FPGA 系列数据手册P16~17下面介绍一下常见逻辑电平标准现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPEC L、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

voh(输出电压反转为高电平)VO-H。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVT TL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

fpga主要参数FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活可重新配置的硬件特性。

它可以被程序员用于实现特定的电路功能,适用于各种不同的应用领域。

在选择使用FPGA时,有一些主要参数需要考虑。

以下是一些重要的FPGA参数及其详细说明。

1.逻辑单元数量:逻辑单元是FPGA的基本构建块,用于实现不同的逻辑功能。

逻辑单元的数量决定了FPGA的运算能力和复杂性。

当应用需要进行大规模的并行计算时,逻辑单元数量是一个关键参数。

2. 查找表数量:查找表(Look-Up Table,LUT)是FPGA中最小的逻辑单元。

它可以存储逻辑函数,并在需要时提供输出。

查找表数量越大,FPGA的灵活性就越高,可以实现更复杂的逻辑功能。

3.存储单元数量:存储单元用于存储数据和程序。

它可以是寄存器、存储器或分布式RAM等形式。

存储单元的数量决定了FPGA的数据处理能力和存储容量。

对于需要大量数据存储的应用,存储单元数量是一个重要的考虑因素。

4.I/O接口数量:输入/输出(I/O)接口用于与其他外部设备进行数据交互。

I/O接口数量决定了FPGA连接外部设备的能力,如传感器、存储设备、网络接口等。

对于需要大量连接的应用,例如通信系统或数据采集系统,I/O接口数量是一个重要的指标。

5.时钟频率:时钟频率表示FPGA在单位时间内完成的操作次数。

它决定了FPGA的工作速度和响应性能。

高时钟频率可以使FPGA更快地执行计算任务,但对电路设计和功耗管理提出了更高的要求。

适当选择时钟频率可以平衡FPGA的性能和功耗。

6.资源利用率:资源利用率是指FPGA上实际使用的逻辑资源占总资源的比例。

对于系统设计,资源利用率越高,系统的性能就越好。

低资源利用率可能意味着设计不充分或存在冗余。

因此,在选择FPGA时,需要考虑资源利用率,以确保最佳性能和资源利用。

7.功耗:功耗是FPGA运行时所消耗的能量。

xilinx fpga中时钟输入管脚的约束在Xilinx FPGA中,时钟输入管脚的约束是非常重要的,它们可以确保时钟信号的稳定性和一致性,从而保证设计的性能和可靠性。

因此,合理设置时钟输入管脚的约束是进行FPGA设计中不可忽视的一部分。

时钟输入管脚约束主要包括以下几个方面:1.频率约束:时钟输入管脚的频率约束指定了该管脚接收的时钟信号的频率范围。

在设计中,需要根据时钟源的特性和系统的工作要求来设置合适的频率约束。

2.总线延迟约束:在一些应用中,时钟信号可能需要进行时序约束,以确保各个时钟域之间的同步稳定性。

总线延迟约束指定了时钟信号与其他信号的最大传播延迟,这样可以避免时序问题和死锁。

3.约束路径的设置:时钟输入管脚的约束路径设置是确保时钟信号按照设计要求正确到达目标寄存器的关键。

通过设置约束路径,可以规定时钟信号到达目标寄存器的最长路径,确保时钟信号的稳定性,减少时钟抖动和时钟周期不稳定等问题。

4.时钟输入和输出约束:时钟输入管脚还可能有一些其他的约束设置,如时钟输入和输出的相位约束、时钟输入和输出的组合约束等。

这些约束的目的是保证时钟信号的稳定性和相位一致性。

除了上述的基本约束外,还有一些特殊的约束需要注意:1.编译工具约束:在进行FPGA设计时,可以使用Xilinx的编译工具对设计进行优化和约束分析。

通过正确设置时钟输入管脚的约束,可以使编译工具更好地理解设计的时钟域和时序要求,从而提高设计的性能和可靠性。

2.时钟插入延迟约束:在一些高速设计中,时钟插入延迟约束非常重要。

它指定了时钟信号从输入管脚到达目标寄存器之间的最小插入延迟。

通过设置时钟插入延迟约束,可以在设计中引入适当的延迟,从而使时钟信号的到达时间更加可控和稳定。

3.锁定时钟约束:在一些需要时钟同步的设计中,可能需要设置锁定时钟约束。

这个约束规定了时钟信号之间的相位关系,确保它们在设定的相位范围内保持同步。

这对于一些高速通信和信号处理系统中的数据同步非常重要。

FPGA约束的详细介绍1、约束的目的介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。

所以首先要设计合理,才可能满足约束,约束反过来检查设计能否满足时序。

主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法。

另外quatus的语法和xdc几乎兼容,原理都一样。

时序约束中最基本的是时钟,时钟有抖动(jitter),偏移(skew),占空比失真(duty cycle distorTIon)三种特性。

1、抖动,分为周期抖动(cycle jitter),周期差抖动(cycle to cycle jitter)和长期抖动(long term jitter)。

2、偏移和时钟线的长度,时序单元的负载电容和个数有关。

FPGA的全局时钟采用全铜工艺和树状结构,偏移非常小,可以忽略。

3、占空比失真就是高低电平不对称,会吞噬时序裕量。

2、基本的时钟约束最简单的情况,设计只有一个时钟。

这时候需要对这个时钟的周期进行约束,(当然也可以对占空比进行约束,默认为50%)。

如果不对时钟进行约束,我们就不知道自己的设计是否时序收敛。

简单的说,比如系统时钟是200M的,那么周期就是5ns,也就是说信号从一个寄存器出来,经过了一系列的组合逻辑,要在下一个时钟的上升沿到来之前被目的寄存器采样到。

当然考虑到,实际情况还复杂很多。

假如设计里有很多时钟,那么哪些时钟是必须要约束的呢?首先是从端口进入FPGA的时钟。

其他衍生时钟(如通过PLL或者MMCM生成的)跟它是同源时钟,工具会自动推导。

然后是GT的rx_clk和tx_clk必须要约束。

最后是用户自己分频产生的行波时钟(用于简单的低频应用),必须约束。

create_clock -name clk_200m -period 5 [get_ports I_clk200]。

前一段时间调试了xilinx的板子上跑代码,自己加IP核,看了它的约束文件,在网上找了一些讲语法的资料,自己整理了一下,我感觉在你了解了语法之后,确实得好好看一下它自己给出的约束,有些我自己没用到,我就没整理了。

1.约束文件的概念FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF 文件,最后再经过实现后生成PCF 文件。

本节主要介绍UCF文件的使用方法。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

2.UCF文件的语法说明UCF文件的语法为:{NET|INST|PIN} "signal_name" Attribute;其中,“signal_name”是指所约束对象的名字,包含了对象所在层次的描述;“Attribute”为约束的具体描述;语句必须以分号“;”结束。

可以用“#”或“/* */”添加注释。

需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。

在UCF文件中描述管脚分配的语法为:NET “端口名称” LOC =引脚编号;NET "CLK" LOC = P30; “CLK”就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。

[原创] Lattice的ISPlever使用教程ispLEVER使用教程目录第一节 ispLEVER 简介第二节 ispLEVER开发工具的原理图输入第三节设计的编译与仿真第四节硬件描述语言和原理图混合输入第五节 ispLEVER工具中VHDL和Verilog语言的设计方法第六节 ispVM System-在系统编程的软件平台第七节约束条件编辑器(Constraint Editor)的使用方法附录一 ispLEVER System上机实习题附录二 ispLEVER软件中文件名后缀及其含义第一节 ispLEVER 简介ispLEVER 是Lattice 公司最新推出的一套EDA软件。

设计输入可采用原理图、硬件描述语言、混合输入三种方式。

能对所设计的数字电子系统进行功能仿真和时序仿真。

编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线并生成编程所需要的熔丝图文件。

软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。

软件包含Synolicity公司的“Synplify”综合工具和Lattice的ispVM器件编程工具。

ispLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

软件支持所有Lattice公司的ispLSI 、MACH、ispGDX、ispGAL、GAL器件。

ispLEVER 工具套件还支持Lattice新的ispXPGATM和ispXPLDTM产品系列,并集成了Lattice ORCA Foundry设计工具的特点和功能。

这使得ispLEVER的用户能够设计新的ispXPGA和ispXPLD产品系列,ORCA FPGA/FPSC系列和所有Lattice的业界领先的CPLD产品而不必学习新的设计工具。

软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* 原理图和硬件描述语言混合输入2. 逻辑模拟* 功能模拟* 时序模拟3. 编译器* 结构综合、映射、自动布局和布线4. 支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有ispLSI、MACH、ispGDX、ispGAL、GAL、ORCA FPGA/FPSC、ispXPGA和ispXPLD器件5. Constraints Editor工具* I/O参数设置和引脚分配6. ispVM工具* 对ISP器件进行编程软件支持的计算机平台:PC: Windows 98/NT/2000/XP第二节 ispLEVER开发工具的原理图输入I. 启动ispLEVER(按Start=>Programs=>LatticeSemiconductor=>ispLEVER Project Navigator)II. 创建一个新的设计项目A. 选择菜单File。

为什么Lattice在进入FPGA市场的第一年就能取得这么好的成绩?我想这里面可能有三个层次的深层原因:第一,针对Altera和Xilinx在高端有Stratix和Virtex、在低端有Cyclone和Spartan产品的情况下,我们选择了从中端切入的策略,从而在刚进入FPGA应用市场时能够有效地避免与已在高端和低端市场确立了自己领导地位的Altera和Xilinx发生正面冲撞,二年多来的实践证明这一策略是非常正确的;第二,我们在满足市场要求的严格质量前提下做出了自己的产品特色,例如,我们的低端LatticeECP2/M FPGA产品在保持对Cyclone和Spartan价格竞争力的前提下,再增加了一些切合用户实际应用需要而主要竞争对手还没有的功能,如更多的高速串行接口、更多的I/O口、128位AES加密和更大的内部存储空间等;第三,系统制造商心里也期望市场能涌现出较强的第3个FPGA供应商,因为这样才能形成稳定的三足鼎立之势,促进市场的有序竞争,并帮助它们稳定供应链和进一步降低运营成本。

目前FPGA和CPLD在哪些主要应用空间具有不可替代的关键地位?目前FPGA和CPLD的目标应用主要可分为以下三大类:低成本应用、对价格敏感的高性能应用、以及需要极高性能的应用。

第一类应用包括等离子或LCD TV、VoIP、机顶盒、图像渲染、音频处理和控制逻辑,第二类应用包括企业联网、GPON、企业存储、无线基站、协议转换、网络交换、图像滤波和存储器桥接,第三类应用包括光纤联网、SDH线路卡、下一代40G光通道卡、局域网交换机、DDR3存储器测试仪、高端服务器、背板高速接口、数据包成帧和分拆、高速存储器控制和高速信号处理。

Lattice目前主要有哪几条产品线?它们各针对什么目标应用?Lattice目前主要有4条产品线:针对低端市场的低成本FPGA LatticeECP2/M、针对高端市场的系统级高性能FPGA LatticeSC/M、带嵌入式闪存的非易失性FPGA LatticeXP和MachXO、以及混合信号PLD ispClock和Power Manager II,LatticeECP2和LatticeECP2M的主要区别是后者还带有SRAM存储器,LatticeSC和LatticeSCM的主要区别也一样。

xilinx fpga中时钟输入管脚的约束在Xilinx FPGA中,时钟输入管脚的约束是非常重要的,它决定了时钟信号的稳定性和数据流的正确性。

以下是一些关于时钟输入管脚约束的相关参考内容。

1. 器件手册在Xilinx FPGA的器件手册中,通常会提供关于时钟输入管脚的详细信息。

这些信息包括时钟输入管脚的功能、电气特性、使用限制等。

器件手册还可能提供特殊的时钟输入约束,如最大工作频率、时钟插入延迟等。

2. 约束文件在设计FPGA时,通常会使用一个约束文件来指定设计中的时钟输入管脚的相关约束。

约束文件是一个文本文件,其中可以定义各种约束,如时钟频率、时钟插入延迟、时钟占空比等。

对于时钟输入管脚,约束文件通常会指定时钟源(如外部晶振或PLL)以及时钟的时钟域和时钟频率。

3. Vivado Design Suite User GuideVivado是Xilinx FPGA的设计工具套件,其用户指南提供了关于时钟输入管脚约束的详细信息。

用户指南中包含了各种约束的语法和用法,如时钟约束(CLOCK)以及时钟域(CLOCK_DOMAIN)。

用户指南还提供了一些示例和最佳实践,帮助设计师正确地约束时钟输入管脚。

4. 库元件和IP核的文档库元件和IP核是在FPGA设计中常用的组件。

对于这些组件,文档中通常会提供有关时钟输入管脚约束的信息。

例如,文档可能会包含有关时钟输入的建议,如时钟频率范围、时钟上升/下降时间要求等。

5. 官方论坛和社区Xilinx官方论坛和其他在线社区,如Xilinx FPGA设计社区,是一个寻求技术支持和问题解答的好地方。

这些论坛中的讨论和帖子通常包含关于时钟输入管脚约束的有用信息,如如何正确约束复杂时钟结构、如何解决时钟插入延迟等。

6. 应用笔记和技术文章Xilinx和其他第三方通常会发布一些应用笔记和技术文章,分享关于FPGA设计的有用信息。

这些文档中可能包含有关时钟输入管脚约束的实用技巧和教程,如如何避免时钟抖动、如何降低时钟插入延迟等。

ise管脚约束设置参数详解以ISE管脚约束设置参数详解概述ISE(Integrated Software Environment)是Xilinx公司开发的一款用于设计和实现FPGA(Field-Programmable Gate Array)的软件工具。

在使用ISE进行FPGA设计时,管脚约束是非常重要的一部分,它用于指定FPGA芯片上的输入输出引脚的功能和连接关系,以确保设计的正确性和可靠性。

本文将详细介绍ISE管脚约束设置参数的相关知识。

1. 管脚约束的作用管脚约束是将设计的逻辑电路与FPGA芯片上的引脚进行连接的关键步骤。

通过正确设置管脚约束参数,可以确保逻辑电路与硬件之间的正确通信,同时还可以优化电路性能和资源利用率。

在ISE中,管脚约束的设置包括输入输出管脚的引脚类型、电平标准、时钟频率等多个方面。

2. 管脚约束的设置方法在ISE中,可以使用UCF(User Constraints File)文件或XDC (Xilinx Design Constraints)文件来进行管脚约束的设置。

UCF 文件是ISE早期版本使用的约束文件格式,而XDC文件是ISE 14.1及以后版本引入的新约束文件格式。

下面将分别介绍这两种约束文件的设置方法。

2.1 UCF文件的设置方法UCF文件是一种文本文件,可以使用任何文本编辑器进行编辑。

UCF文件中的每一行都对应着一个管脚的约束设置。

以下是UCF文件的一些常用约束参数及其设置方法:- NET:用于定义逻辑电路中的信号名称;- LOC:用于定义信号连接到FPGA芯片上的具体引脚位置;- IOSTANDARD:用于定义引脚的电平标准;- SLEW:用于定义引脚的输出斜率控制;- DRIVE:用于定义引脚的驱动能力;- PULLUP:用于定义引脚的上拉电阻;- PULLDOWN:用于定义引脚的下拉电阻。

通过在UCF文件中逐行设置这些约束参数,可以完成对管脚的约束设置。

FPGA设计之——时序设计FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

建立时间(Setup Time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(Hold Time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

FPGA设计分为异步电路设计和同步电路设计,然而很多异步电路设计都可以转化为同步电路设计,在设计时尽量采用同步电路进行设计。

对于同步电路可以转化的逻辑必须转化,不能转化的逻辑,应将异步的部分减到最小,而其前后级仍然应该采用同步设计。

为了让同步电路可靠地运行,就要对时钟偏差进行控制,以使时钟偏差减小到可用的范围。

影响时钟偏差的主要有以下几个因素:o用于连接时钟树的连线o钟树的拓扑结构o时钟的驱动o时钟线的负载o时钟的上升及下降时间在通常的FPGA设计中对时钟偏差的控制主要有以下几种方法:o控制时钟信号尽量走可编程器件的的全局时钟网络。

在可编程器件中一般都有专门的时钟驱动器及全局时钟网络,不同种类、型号的可编程器件,它们中的全局时钟网络数量不同,因此要根据不同的设计需要选择含有合适数量全局时钟网络的可编程器件。

一般来说,走全局时钟网络的时钟信号到各使用端的延时小,时钟偏差很小,基本可以忽略不计。

o若设计中时钟信号数量很多,无法让所有的信号都走全局时钟网络,那么可以通过在设计中加约束的方法,控制不能走全局时钟网络的时钟信号的时钟偏差。

o异步接口时序裕度要足够大。

局部同步电路之间接口都可以看成是异步接口,比较典型的是设计中的高低频电路接口、I/O接口,那么接口电路中后一级触发器的建立-保持时间要满足要求,时序裕度要足够大。

o在系统时钟大于30MHz时,设计难度有所加大,建议采用流水线等设计方法。

©LATTICE SEMICONDUCTOR CORPORATIONPage 1Achieving Timing ClosureJohn LiAgenda•Timing closure的概念•Timing closure的步骤•采用合适的Coding Style •进行适当的综合约束•管脚锁定•实施Lattice constrains •Map•布局布线•控制place and route •Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 2Timing closure的概念•当前FPGA的设计规模越来越大,复杂程度日益增加,同时要求系统的Perfromace也越来越高。

•获得Timing目标越来越困难.•设计者必须采用各种技术提升系统性能以满足设计的Timing要求.©LATTICE SEMICONDUCTOR CORPORATIONPage 3Timing closure procedure• 1.采用合适的coding style • 2.进行适当的综合约束• 3.管脚锁定• 4.实施Lattice constrains • 5.Map• 5.布局布线•7.控制place and route •8.Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 4关于提升FPGA系统性能,工程师最容易想到的方法就是通过进行综合约束、布局布线约束、和其他的优化技术提升系统性能,当然这些都是设计过程中所必需的,但所有这些优化方法对于系统性能的提升都是有限的,系统的性能最终还是取决于工程师的设计(coding style),其中同步设计是最重要的一点. 下面讨论一些具体的coding 技术,合理的运用这些coding技术能够尽可能的减小两级寄存器之间的延时从而获得更高的系统速度.-通用的coding style--Hierarchical Coding---Team Based的设计:多个工程师可以同时参与到一个复杂设计中来。

fpga中的参数说明FPGA中的参数说明一、引言FPGA(Field-Programmable Gate Array)是一种现场可编程门阵列芯片,具有灵活性高、性能优越、可重构等特点,在各种应用领域得到广泛应用。

本文将从不同角度介绍FPGA中的参数说明,包括时钟频率、逻辑单元数量、片上存储器容量、资源利用率和功耗等方面。

二、时钟频率时钟频率是指FPGA中的时钟信号的频率,也是FPGA运行速度的关键参数。

时钟频率越高,FPGA的运算速度越快。

在选择FPGA 时,需要根据具体应用需求和性能要求,选择合适的时钟频率。

值得注意的是,在设计FPGA电路时,还需要考虑到时钟分配、时钟域划分等问题,以确保时钟信号的稳定性和可靠性。

三、逻辑单元数量逻辑单元数量是指FPGA中可用的逻辑门数量。

逻辑门是FPGA中最基本的逻辑单元,用于实现各种逻辑功能。

逻辑单元数量越多,FPGA的逻辑处理能力越强。

在进行FPGA设计时,需要根据所需的逻辑功能和复杂度,选择适当的逻辑单元数量。

同时,逻辑单元数量的增加也会导致FPGA的面积增加,从而影响功耗和资源利用率。

四、片上存储器容量片上存储器容量是指FPGA中可用的存储器容量。

片上存储器用于存储数据和中间结果,在FPGA设计中起到关键作用。

片上存储器容量的大小直接影响到FPGA的数据处理能力和性能。

较大的片上存储器容量可以提高FPGA的数据缓存能力,减少对外部存储器的访问次数,从而提高系统的运行效率。

五、资源利用率资源利用率是指FPGA中各种资源的利用程度。

FPGA中的资源包括逻辑单元、片上存储器、DSP(Digital Signal Processing)模块等。

资源利用率越高,说明FPGA的资源利用效率越高,系统的性能也会相应提高。

在进行FPGA设计时,需要合理利用各种资源,以提高系统的性能和效率。

六、功耗功耗是指FPGA芯片在工作过程中所消耗的电能。

功耗大小直接影响到FPGA的散热需求和系统的稳定性。

fpga的时序约束FPGA的时序约束FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活性和可重构性。

在FPGA设计中,时序约束是一项重要的任务,它定义了电路中信号的传输时间和时序关系。

时序约束的正确设置对电路的性能和稳定性至关重要。

本文将介绍FPGA的时序约束及其相关内容。

一、时序约束的基本概念时序约束是指在FPGA设计中,对电路中信号的传输时间、时钟频率、延迟等进行限制和定义。

它是一种关于信号传输时序关系的约束条件,确保设计在特定时钟频率下能够正常工作。

时序约束通常包括以下几个方面:1. 时钟频率:指定电路中时钟信号的频率,即时钟周期的倒数。

时钟频率决定了电路的工作速度和性能。

2. 输入延迟:指定输入信号到达FPGA引脚到被FPGA内部逻辑电路采样的时间。

输入延迟主要取决于信号的传输路径和FPGA的布局。

3. 输出延迟:指定FPGA内部逻辑电路输出信号从采样到输出引脚的时间。

输出延迟决定了输出信号的稳定性和正确性。

4. 约束路径:指定电路中的关键路径,并要求这些路径满足一定的时序要求。

关键路径是决定电路性能的主要路径。

5. 时序检查:对设计中的时序约束进行验证,确保电路能够在特定时钟频率下正常工作。

时序检查常常使用时序分析工具进行。

二、时序约束的设置方法在FPGA设计中,时序约束通常通过HDL(Hardware Description Language)代码或专用的约束文件进行设置。

常见的HDL语言有VHDL和Verilog,这些语言提供了丰富的语法和语义来描述电路的时序行为。

时序约束的设置包括以下几个步骤:1. 确定时钟频率:根据设计的需求和目标平台的性能,确定适当的时钟频率。

时钟频率应根据FPGA器件的特性和设计的复杂度进行选择。

2. 分析设计中的关键路径:通过时序分析工具,分析设计中的关键路径。

关键路径是决定电路性能的主要路径,需要特别关注和设置时序约束。

第1篇目录1. 引言2. 约束概述3. 约束类型1. 位置约束2. 时序约束3. 电源和接地约束4. 电压约束5. 信号完整性约束4. 约束设置5. 约束验证6. 常见问题解答7. 总结1. 引言Quartus II 是一款由 Altera 公司开发的现场可编程门阵列(FPGA)设计软件。

在进行 FPGA 设计时,约束是确保设计正确性和性能的关键因素。

本手册旨在提供关于 Quartus II 约束的全面指南,帮助用户了解如何设置和使用约束,以提高设计效率和性能。

2. 约束概述约束是描述设计要求的一系列指令,用于指导 Quartus II 综合器、布局布线器和其他工具生成正确且性能优化的硬件设计。

约束可以基于设计规格、硬件资源限制或性能要求。

3. 约束类型3.1 位置约束位置约束指定了设计中的特定信号或模块应该放置在 FPGA 的哪个位置。

这有助于优化设计性能和资源利用率。

- 固定位置约束:指定一个具体的 FPGA 坐标,将信号或模块放置在该位置。

- 区域约束:指定一个 FPGA 区域,将信号或模块放置在该区域内。

3.2 时序约束时序约束定义了设计中的关键路径延迟要求,包括时钟频率、时钟边沿、数据到达时间和数据保持时间等。

- 时钟约束:指定时钟信号的频率、相位和复位特性。

- 数据路径约束:指定数据路径的延迟要求,包括时钟到数据的传播延迟。

3.3 电源和接地约束电源和接地约束确保设计中的电源和接地网络满足性能要求。

- 电源网络约束:指定电源网络的关键特性,如电压、电流和电源完整性。

- 接地网络约束:指定接地网络的关键特性,如接地电阻和接地完整性。

3.4 电压约束电压约束确保设计中的电压满足设计规格要求。

- 电源电压约束:指定电源电压的范围。

- 电压完整性约束:指定电压波动范围。

3.5 信号完整性约束信号完整性约束确保设计中的信号满足性能要求。

- 信号完整性分析:分析信号在传输过程中的衰减、反射和串扰。