(相当不错还得再看很多遍)基于CUDA的矩阵乘法和FFT性能测试

- 格式:pdf

- 大小:1.27 MB

- 文档页数:4

cuda 矩阵运算CUDA 矩阵运算概述CUDA是一种并行计算架构,可用于高性能计算和科学计算。

它允许开发人员使用标准C/C++编程语言扩展其应用程序以利用GPU的并行处理能力。

矩阵运算是计算机图形学、机器学习和科学计算等领域中常见的操作之一。

本文将介绍如何使用CUDA进行矩阵运算,以及如何优化矩阵运算的性能。

CUDA架构和矩阵运算CUDA架构通过将并行计算任务分配给多个计算单元(称为线程)来加速计算。

在矩阵运算中,可以将每个矩阵元素的计算任务分配给不同的线程。

例如,要计算两个矩阵的乘积,可以将每个元素的乘法操作分配给不同的线程进行并行计算。

CUDA编程模型CUDA编程模型在主机(CPU)和设备(GPU)之间建立了一个协作关系。

主机负责将数据从主机内存复制到设备内存,并调用设备上的核函数进行计算。

设备负责执行核函数,并将计算结果返回给主机。

CUDA提供了一组API函数,用于管理设备内存、调度核函数和数据传输等操作。

CUDA核函数在CUDA编程中,核函数是在设备上执行的函数。

核函数通过__global__关键字进行声明,并可以接受任意数量和类型的参数。

在矩阵运算中,核函数通常使用二维线程块和网格来处理矩阵的每个元素。

核函数可以使用内置的线程和块索引来确定当前线程的位置,并计算相应的元素。

CUDA内存模型CUDA提供了全局内存、共享内存和常量内存等不同类型的内存来支持矩阵运算。

全局内存用于在主机和设备之间传输数据,共享内存用于线程块内的数据共享,而常量内存用于存储只读数据。

在矩阵运算中,可以使用这些不同类型的内存来优化计算性能。

CUDA矩阵运算的优化为了提高CUDA矩阵运算的性能,可以采取以下几种优化策略:1. 使用共享内存共享内存是一种高速缓存,可以在线程块内共享数据。

通过将矩阵元素加载到共享内存中,可以减少全局内存访问的次数,从而提高计算性能。

2. 使用纹理内存纹理内存是一种特殊的全局内存,可以提供对数据的高速缓存和高效访问。

基础科研训练报告——基于CUDA的矩阵求逆并行算法研究学院:英才实验学院训练目的基于NVIDIA CUDA实现大规模矩阵求逆的并行算法。

在过程中熟悉NVIDIA CUDA并行运算平台,掌握C++面向对象的程序设计,并且深刻理解矩阵求逆并行算,将其在CUDA平台上实现出来。

需要在运行过后展示出算法中每一部分的运行时间,从而找到瓶颈,为进一步优化算法提供依据和方向。

理论基础Firstly, we introduce several practical ways to compute the inverse of a matrix. Let us review how one particular algorithm for the Cholesky factorization is usually motivated.We consider A = RTR andBy substituting the matrices A and R into A = RTR, we find thatfrom which we conclude thatConsider that before every iteration, quadrant ATL has already been overwritten by RTL . In the body of the loop, a next row and column are exposed, and updated. The row and the column are then included in ATL so that at the end of the iteration, again ATL contains the result RTL . Eventually ATL envelops the entire matrix, at which point A contains the desired R. In order to attain high performance, the computation is typically cast in terms of matrix-matrix multiplications. For the Cholesky factorization, a blocked version of the algorithm can be derived by partitioningwhere A11 and R11 are b*b . By substituting into A = RTR, we find thatwhich is the algorithm we aim to get.The other way of computing the inverse of a matrix is that we assume A to be a matrix of m*k, and B is a matrix of k*n, remarking that C=AB. To get the parallel matrix invasion algorithm of C=AB, based on the p processors we have, we firstly divide the A and B into several blocks. LikeA =(A 1T ,A 2T ,A 3T ...A P T)and B =(B 1,B 2,B 3...B P )Where Ai is a matrix of mi*k, and Bi is a matrix of k*ni, so that we can represent C intoC =AB =A 1A 2...A p æèççççöø÷÷÷÷(B 1,B 2,B 3...B P )then it ’s transparent to find that we can compute each block of C separately, following the stepswe need.① Firstly, we put the data of Ai, Bi into processor i, setting the initial k=1② Then, it is the part for transmission, where the processor I transmit the element in Bi intoprocessor i+1. Obviously, the last processor p transmits the data into the first processor. ③ Each processor computes the product of each group of AiBi, saving the results into Ci, whereremarking that The saving process is based on the sequence of AiBi. ④ When each processor receiving the data from the former processor, the data has to be savedinto the Bi matrix, covering the former data. ⑤ If k<p then set k=k+1 and continue step 2, else if k=p, each processor then compute theproduct of AiBi, and to the end.训练过程说明本次训练分为四个阶段,第一阶段是学习C++面向对象的编程,这一个阶段大概持续了1个月,我们一边看谭浩强的教材,一面找一些例子练习,不久就基本掌握了C++这门语言。

CPU-OpenMP和GPU-CUDA并行计算技术对矩阵乘法运算的加速效果分析张岩【摘要】本文对比了CPU-OpenMP和GPU-CUDA并行计算技术对不同阶矩阵乘法运算相对于CPU单线程计算的加速效果.结果表明,CPU-OpenMP并行的计算加速比与矩阵阶数无关,且低于所采用的线程数目.GPU-CUDA并行的计算加速比随矩阵阶数的增加显著增加,最大计算加速比可达570倍以上.相对于CPU单线程计算结果,CPU-OpenMP并行计算未产生误差,而GPU-CUDA并行计算会产生误差.结果表明,GPU-CUDA并行适合高阶数矩阵乘法的加速计算,而CPU-OpenMP 并行适合低阶数矩阵乘法的加速计算.【期刊名称】《科技视界》【年(卷),期】2017(000)026【总页数】3页(P45-47)【关键词】矩阵乘法;并行计算;CPU-OpenMP;GPU-CUDA【作者】张岩【作者单位】北京师范大学附属中学京西分校高三1班,中国北京 100042【正文语种】中文【中图分类】TP391在信息化技术不断发展的今天,人们处在“大数据”时代。

由于数据量巨大,普通的串行计算方式计算效率低下,无法满足人们对数据进行快速处理的需求。

因此,如何能够提高计算机处理“大数据”的计算效率已成为人们日益关注的话题。

为了减少计算时间、提升计算效率,并行计算的出现成为解决上述问题的有效方法。

与普通的串行计算相比,并行计算将计算任务分配到计算机的多个处理器协同处理,从而提高计算效率。

随着并行计算结果的发展,并行算法也逐渐成熟。

目前,人们采用的并行计算技术大致可能分为两种:一是基于CPU(Central Processing Unit)多核多线程的并行计算;二是基于 GPU(Graphics Processing Unit)的通用并行计算。

对于CPU并行计算,根据并行粒度的不同可分为“共享式内存结构”和“分布式内存结构”[1]。

对于“共享式内存结构”的并行计算,OpenMP(Open Multi-Processing)作为该类型计算技术的代表,已被广泛应用于数据处理及科学计算中。

Cuda多个矩阵的乘法简介在并行计算中,图形处理器(GPU)以其高度并行的架构和强大的计算能力而受到广泛关注。

CUDA(Compute Unified Device Architecture)是一种由NVIDIA开发的并行计算平台和编程模型,它允许开发人员利用GPU进行通用计算。

矩阵乘法是一种常见的线性代数运算,在许多科学和工程应用中都有广泛的应用。

在本文中,我们将探讨如何使用CUDA来实现多个矩阵的乘法。

CUDA编程模型CUDA编程模型基于主机(CPU)和设备(GPU)之间的协同工作。

主机负责管理数据传输和任务调度,而设备则执行实际的计算任务。

CUDA程序由两部分组成:主机代码和设备代码。

主机代码运行在CPU上,用于管理设备内存、数据传输和任务调度等操作。

设备代码运行在GPU上,用于执行实际的并行计算任务。

矩阵乘法矩阵乘法是一种将两个矩阵相乘得到第三个矩阵的操作。

给定一个m×n维度的矩阵A和一个n×p维度的矩阵B,它们的乘积C将是一个m×p维度的矩阵。

矩阵乘法的定义如下:C[i][j] = sum(A[i][k] * B[k][j]) for k = 0 to n-1其中,i表示结果矩阵C的行索引,j表示结果矩阵C的列索引。

CUDA实现使用CUDA实现多个矩阵的乘法需要经历以下步骤:1.在主机代码中分配并初始化输入矩阵A和B,并分配输出矩阵C所需的内存。

2.将输入矩阵A和B从主机内存复制到设备内存。

3.在设备代码中使用CUDA线程块和线程索引来并行计算每个元素的乘积,并将结果累加到输出矩阵C中。

4.将输出矩阵C从设备内存复制回主机内存。

5.释放设备和主机上使用的内存。

以下是一个使用CUDA实现多个矩阵乘法的示例代码:#include <stdio.h>#define N 1024__global__ void matrixMul(int *A, int *B, int *C, int n) {int row = blockIdx.y * blockDim.y + threadIdx.y;int col = blockIdx.x * blockDim.x + threadIdx.x;if (row < n && col < n) {int sum = 0;for (int k = 0; k < n; k++) {sum += A[row * n + k] * B[k * n + col];}C[row * n + col] = sum;}}int main() {int *h_A, *h_B, *h_C; // 主机上的矩阵int *d_A, *d_B, *d_C; // 设备上的矩阵int matrixSize = N * N * sizeof(int);// 分配主机内存h_A = (int*)malloc(matrixSize);h_B = (int*)malloc(matrixSize);h_C = (int*)malloc(matrixSize);// 初始化输入矩阵A和Bfor (int i = 0; i < N; i++) {for (int j = 0; j < N; j++) {h_A[i * N + j] = i;h_B[i * N + j] = j;}}// 分配设备内存cudaMalloc(&d_A, matrixSize);cudaMalloc(&d_B, matrixSize);cudaMalloc(&d_C, matrixSize);// 将输入矩阵A和B从主机内存复制到设备内存cudaMemcpy(d_A, h_A, matrixSize, cudaMemcpyHostToDevice); cudaMemcpy(d_B, h_B, matrixSize, cudaMemcpyHostToDevice);// 定义CUDA线程块和线程网格的大小dim3 blockSize(16, 16);dim3 gridSize((N + blockSize.x - 1) / blockSize.x,(N + blockSize.y - 1) / blockSize.y);// 调用设备上的函数来执行矩阵乘法matrixMul<<<gridSize, blockSize>>>(d_A, d_B, d_C, N);// 将输出矩阵C从设备内存复制回主机内存cudaMemcpy(h_C, d_C, matrixSize, cudaMemcpyDeviceToHost);// 打印输出矩阵C的前10行和列for (int i = 0; i < 10; i++) {for (int j = 0; j < 10; j++) {printf("%d ", h_C[i * N + j]);}printf("\n");}// 释放设备和主机上的内存cudaFree(d_A);cudaFree(d_B);cudaFree(d_C);free(h_A);free(h_B);free(h_C);return 0;}在这个示例中,我们使用了一个大小为1024×1024的矩阵进行计算。

FFT算法的并行化性能分析王璐;梁涛;王文义【摘要】以串行FFTW为基准,从程序运行时间、通信开销两方面分析了基于消息传递型(MPI-FFT)和共享内存型(CUFFT)并行FFT实现的性能. 实验表明,并行FFT 都可以提升计算速度至FFTW的30~80倍,对于中等规模的数据,CUFFT的计算速度略优于MPI-FFT,且其通信开销明显较低,具有较高性价比和较好的应用前景.【期刊名称】《中原工学院学报》【年(卷),期】2010(021)005【总页数】4页(P30-32,41)【关键词】并行性能;CUFFT;MPI;FFTW【作者】王璐;梁涛;王文义【作者单位】中原工学院,郑州,450007;中原工学院,郑州,450007;中原工学院,郑州,450007【正文语种】中文【中图分类】TP391离散傅里叶变换(DFT)是数字信号处理中最基本、最重要的运算,许多算法,例如卷积、滤波、波谱分析等都可以化为DFT来实现.但是DFT的计算量相当大,1965年Cooley和Tukey提出了快速傅里叶变换算法(FFT),大大提高了DFT 的计算速度.此后,有很多研究者不断改进算法.美国麻省理工学院计算机科学实验室超级计算技术组开发的FFTW(Fastest Fourier Transform in the West)是目前世界上公认的运算较快、使用广泛的串行C程序FFT,支持一维和多维的实数及复数DFT[1].随着高性能科学计算的要求和嵌入式技术的发展,不仅产生了多种基于DSP或FPGA的并行FFT实现[2],而且还出现了多种适于不同并行体系结构及编程模型的并行FFT算法[3-5].文献[6]对FFT并行化思想进行了简要的总结与分析,面向集群设备给出了基于消息传递接口(MPI)的典型并行FFT算法,是目前针对因高性价比而受到用户青睐的集群并行设备实现并行FFT的重要参考.目前,基于图形硬件(GPU)的通用计算正成为并行领域的研究热点.特别是NVidia公司于2007年推出统一计算设备架构(CUDA)后,极大增强了GPU的通用计算能力,在编程、优化等方面都得到了显著的提升.同时,NVidia公司基于CUDA也推出了面向GPU的并行FFT算法,即CUFFT.肖江等针对矩阵乘法以及CUFFT进行了计算性能测试[7].但是更详尽的性能分析,以及与其他典型并行体系结构下的并行FFT算法的比较还很少见.本文以串行FFTW作为基准,对CUFFT、基于集群与MPI的典型并行FFT算法进行了计算能力以及通信开销的详细比较,以期为各种算法的性能特点及适用场合提供更翔实的应用参考.FFT的基-2并行计算过程如图1所示[5].节点{i,0}(N/2≤i≤N-1)将接受直线边传来的数据与交叉边传来的数据,通过两点FFT蝶形计算方法可求出下一列向量.以此类推,直到第logN列才变为用原始向量进行计算.所以,经过logN步并行计算后,即可计算出一个N点一维FFT.图1中数据量为8,并行节点数为4.一般地,若数据量为DataSize,并行处理机节点数为TaskNum,则log2DataSize至log2TaskNum列都是单机的串行处理,从log2TaskNum列至0列是并行处理.经过这样的递归计算,最终把结果数据计算出来.在此过程中,并行计算节点之间需要进行数据传递,且在每一个循环阶段,都要进行同步,才可以进行下一步.在具体实现FFT并行计算过程时,集群设备通常采用消息传递机制,通过普通以太网络或专用Infiniband网络在各计算节点间进行数据传输,因此需要较多的通信开销.而图形设备(显卡)在进行并行计算时,采用共享内存型的计算模式.特别地,CUDA还提供了全局存储器、共享存储器、本地存储器等多种存储器方案,便于性能调节与优化.与消息传递型相比,GPU的通信主要在图形硬件(显卡)的板级,因此通信更可靠且更快速.2.1.1 测试环境单计算机硬件环境为CPU Intel Pentium Dual E2160 1.80GHZ,内存1G;软件环境为 WinXP操作系统;显卡为NVIDIA公司的GeForce 8400GT,支持CUDA技术;集群环境为22个结点,每个结点由2个2.8GHz处理器组成,内存总量为22G,Infiniband专用网络;分别选用了FFTW库与CUFFT库;编译环境为Micorsoft Visul Studio 2005.由于当数据量为2的幂次方时,FFT的速度最快,本文对4组二维实验数据进行FFT运算,通过对给定同样大小的数组数据进行处理的时间来进行比较.2.1.2 测试对象本文对目前比较重要的并行FFT算法进行测试.因此,选择面向集群及MPI实现的典型FFT算法和面向GPU的CUFFT进行比较测试,代表了目前高性能计算领域2种非常活跃而且通用的并行体系结构.为更好地分析并行性能,仍以串行FFTW 算法作为测试基准.(1)FFTW库程序.FFTW是世界上公认的运算较快的FFT,也是使用很广泛的傅立叶变换程序.具体实现如下:首先载入数组数据,再建立二维FFTW plan进行数据处理.主要程序如下:in=(fftw_complex*)fftw_malloc(sizeof(fftw_real)*Nx*Ny);out=(fftw_complex*)fftw_malloc(sizeof(fftw_complex)*Nx*Ny);给输入和输出的数据申请内存,这里Nx和Ny分别表示数组的行和列的大小,执行plan,完成FFT;p=fftw_plan_dft_2d(NNx,NNy,in,out,FFTW_FORWARD,FFTW_ESTIMATE).这里,FFTW_ESTIMATE也可换为FFTW_MEASRUE,FFTW_ESTIMATE会更快一些.但如果要处理很多同样大小的数据,用FFTW_MEASRUE会更好一些,因为如果用FFTW_MEASRUE模式创建一个最优方案后,只要数据大小不变,在下一次启用时会启动之前创建好的plan,这同样是最优方案.当数据大小为1024*1024时,FFTW_MEASRUE和FFTW_ESTIMATE运行结果如图2所示.(2)CUFFT.CUFFT是由NVIDIA提供的基于GPU的快速傅里叶变换(FFT)函数库.它采用分治的算法,对数据能够在实数与复数域进行FFT运算.CUFFT提供了以下功能:可以对实数或复数进行一维或多维的DFT,可以同时处理一批一维DFT;对二位和三维的傅里叶变换,每个维度长度在[2,16384]中取值.具体实现如下:首先,需要将文档中的数据载入GPU内存中,分别对*idata和*odata定义并申请存储空间:cufftReal*idata;cufftComplex*odata;cudaMalloc((void**)&idata,sizeof(cufftReal)*Nx*Ny);cufftMalloc((void**)&odata,sizeof(cufft-Complex)*Nx*Ny);定义plan,创建plan:cufftHandle plan;cufftPlan2d(&plan,Nx,Ny,CURRT_R2C);完成FFT变换:cufftExecR2C(plan,idata,odata,CUFFT_FORWARD);当数据大小为1024*1024时,运行结果如图3所示.(3)基于 MPI的并行FFT.MPI(Message Passing Interface)是一个库,FFTW3支持基于MPI的并行编程.具体实现如下:调用头文件<fftw_mpi.h>,创建计划:fftw_mpi_plan fftw_mpi_create_plan(MPI_Comm comm,int n,FFTW_FORWARD,FFTW_ESTIMATE);通过调用函数来进行变换,调用的函数为:void fftw_mpi(fftw_mpi_plan p,int n_fields,fftw_complex*local_data,fftw_complex*work);返回时调用函数:void fftw_mpi_local_sizes(fftw_mpi_plan p,int*local_n,int*local_start,int*local_n_after_transform,int*local_start_after_transform,int*total_local_size).测试结果如图4所示.从图4可以看出,随着数据量的增大(矩阵的行列分别为256,512,1024,2048),并行计算的优势越发明显,MPI-FFT和CUFFT一般比FFTW的运算速度提高30~80倍;MPI和GPU的计算时耗在数据规模较小时相差不大,随着数据规模的增加,GPU计算要稍快.但对于超大规模数据,GPU由于受到硬件容量限制,其并行性能落后于集群设备.由于GPU的造价相对于集群设备MPI更加低廉,普通用户也可以享用多节点并行的技术优势,因此对于中小规模计算具有更高的性价比.但对于超大数据量计算时,一般会选择基于MPI的集群设备.通信开销对比如图5所示.在追求减少计算用时的算法研究的同时,用于计算过程中的数据传递所用的时间,即通信开销,也是必须要重视的因素.在CUDA的GPU运算中,通信的时间主要是发生在从内存拷贝数据到GPU的全局存储器上;基于MPI的并行计算,它的通信时间是在每一级运算完毕后,再把数据分别传递给既定的下一级节点上用的时间.本文MPI选取的处理节点数为16,通过图5可以看出(处理节点个数n=16),MPI的通信开销是比较大的,这也影响了MPI并行计算的效率.而GPU计算的通信时间相对地要少得多,GPU计算在通信开销方面有很大优势.本文对FFTW、CUFFT以及 MPI-FFT等3种FFT实现方案进行了性能测试.通过计算用时和通信开销两方面的比较可以看出,基于GPU的CUFFT性能在中小数据规模情况下略高于基于MPI的FFT,具有较高的性价比.目前国内CUDA技术的发展研究正逐渐兴盛起来,相比较于大型计算机,CUDA技术使得人们在个人PC 机上也能高效地实现大量数据运算,这也将吸引人们投入更多的精力致力于CUDA技术的研究发展.从这个意义上说,CUFFT具有更好的应用前景.【相关文献】[1] Matteo Frigo,Steven G Johnson.The Design and Implementation of FFTW3[J].Proceedings of the IEEE,2005,93(2):216-231.[2]朱林,王志凌,黄天戍.基于DSP并行系统的FFT算法实现[J].武汉理工大学学报,2009,31(20):102-104,120.[3]于泽德.基于SIMD-MC2的并行FFT算法[J].现代计算机(专业版),2008(10):57-58.[4]刘文辉.基于SIMD-BF的并行FFT算法[J].商丘师范学院学报,2003,19(5):63-63.[5]孙世新,卢光辉,张艳,等.并行算法及其应用[M].北京:机械工业出版社,2005.[6]张林波,迟学斌,莫则尧,等.并行计算导论[M].北京:清华大学出版社,2006.[7]肖江,胡柯良,邓元勇.基于CUDA的矩阵乘法和FFT性能测试.[J]计算机工程,2009,35(10):7-10.[8]张舒,褚艳利,赵开勇,等.GPU高性能运算之CUDA[M].北京:中国水利水电出版社,2009:10.。

CUDA(Compute Unified Device Architecture)是NVIDIA公司推出的一种并行计算平台和API 模型,可以利用NVIDIA的GPU来进行高效的矩阵运算。

在CUDA中,矩阵运算可以通过使用CUDA库中的相关函数和工具来实现。

以下是一些常见的CUDA矩阵运算:1. 矩阵乘法:可以使用cublasSgemm、cublasDgemm等函数来执行矩阵乘法操作。

这些函数可以在GPU上并行执行,从而实现高效的矩阵乘法运算。

2. 矩阵加法:可以使用cudaMemcpy和cuprintf等函数来执行矩阵加法操作。

这些函数可以将两个矩阵的对应元素相加,并将结果存储在另一个矩阵中。

3. 矩阵乘法的逆:可以使用cublasSinv、cublasDinv等函数来执行矩阵乘法的逆操作。

这些函数可以计算出一个矩阵的逆矩阵,以便进行矩阵乘法的逆运算。

4. 矩阵转置:可以使用cudaMemcpy和cuprintf等函数来执行矩阵转置操作。

这些函数可以将一个矩阵的行和列交换,从而得到一个新的矩阵。

5. 矩阵求逆:可以使用cublasSinv、cublasDinv等函数来执行矩阵求逆操作。

这些函数可以计算出一个矩阵的逆矩阵,以便进行矩阵求逆的运算。

6. 矩阵求逆的逆:可以使用cublasSinv、cublasDinv等函数来执行矩阵求逆的逆运算。

这些函数可以计算出一个矩阵的逆矩阵,以便进行矩阵求逆的逆运算。

7. 矩阵求逆的逆的逆:可以使用cublasSinv、cublasDinv等函数来执行矩阵求逆的逆的逆运算。

这些函数可以计算出一个矩阵的逆矩阵,以便进行矩阵求逆的逆运算。

除了以上列举的矩阵运算外,还有很多其他的矩阵运算可以使用CUDA库来实现。

需要注意的是,在使用CUDA进行矩阵运算时,需要注意矩阵的维度和大小,以确保计算的正确性和效率。

cuda共享内存矩阵乘法CUDA共享内存矩阵乘法是一种高效的并行计算方法,可以充分发挥GPU的强大计算能力。

本文将详细介绍CUDA共享内存矩阵乘法的原理、优势以及实现过程,旨在为读者提供一种生动、全面、有指导意义的文章。

首先,我们来了解一下CUDA共享内存。

共享内存是一种位于SM (流多处理器)内的高速内存,可被多个线程块共享。

相比于全局内存,共享内存的访问速度更快。

在矩阵乘法中使用共享内存,可以减少全局内存的访问次数,从而提高计算效率。

在CUDA共享内存矩阵乘法中,我们首先将输入矩阵分割成多个子矩阵,每个子矩阵对应一个线程块。

每个线程块在共享内存中为子矩阵分配一块内存,并将数据从全局内存复制到共享内存中。

然后,每个线程块使用共享内存中的数据进行乘法计算,最后将结果写回全局内存。

共享内存的大小是有限的,因此需要合理设计共享内存的使用方式。

一种常见的方法是使用矩阵分块技术,将输入矩阵划分成多个小块,每个小块大小不超过共享内存的容量。

然后,每个线程块只计算属于自己负责的小块部分,减少了数据的冗余计算。

为了对共享内存中的数据进行高效访问,可以通过索引计算的方式将数据映射到共享内存中。

例如,可以使用二维索引将矩阵元素映射到共享内存的不同位置。

在进行乘法计算时,可以通过线程索引和矩阵索引的组合,访问共享内存中的数据,并将计算结果写回共享内存的适当位置。

在实现CUDA共享内存矩阵乘法时,还需要注意线程同步的问题。

因为多个线程块在共享内存中读写数据,可能会出现数据不一致的情况。

为了解决这个问题,我们可以使用__syncthreads()函数进行线程同步,保证每个线程块的计算都完成之后再进行下一步操作。

总结起来,CUDA共享内存矩阵乘法是一种高效的并行计算方法,可以通过合理地利用共享内存和线程块,并进行适当的数据分块和索引计算,从而提高矩阵乘法的计算速度。

它充分发挥了GPU的并行计算能力,减少了数据的冗余计算和全局内存的访问次数。

转载-CUDA矩阵向量乘的多种优化写在前⾯本⽂转载⾃。

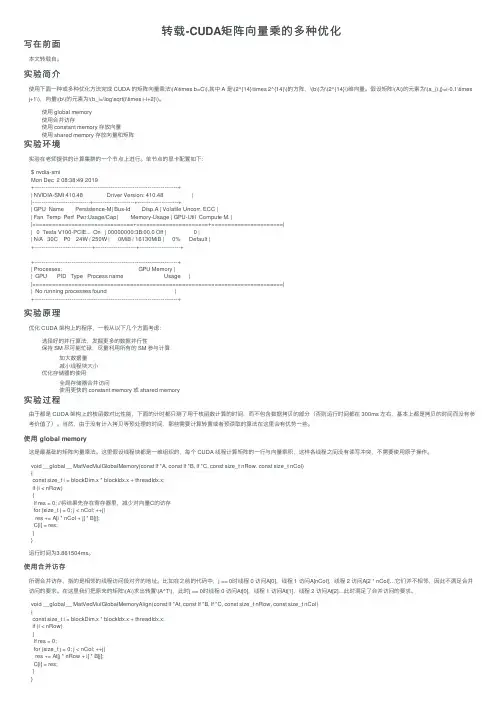

实验简介使⽤下⾯⼀种或多种优化⽅法完成 CUDA 的矩阵向量乘法\(A\times b=C\),其中 A 是\(2^{14}\times 2^{14}\)的⽅阵,\(b\)为\(2^{14}\)维向量。

假设矩阵\(A\)的元素为\(a_{i,j}=i-0.1\times j+1\),向量\(b\)的元素为\(b_i=\log\sqrt{i\times i-i+2}\)。

使⽤ global memory使⽤合并访存使⽤ constant memory 存放向量使⽤ shared memory 存放向量和矩阵实验环境实验在⽼师提供的计算集群的⼀个节点上进⾏。

单节点的显卡配置如下:$ nvdia-smiMon Dec 2 08:38:49 2019+-----------------------------------------------------------------------------+| NVIDIA-SMI 410.48 Driver Version: 410.48 ||-------------------------------+----------------------+----------------------+| GPU Name Persistence-M| Bus-Id Disp.A | Volatile Uncorr. ECC || Fan Temp Perf Pwr:Usage/Cap| Memory-Usage | GPU-Util Compute M. ||===============================+======================+======================|| 0 Tesla V100-PCIE... On | 00000000:3B:00.0 Off | 0 || N/A 30C P0 24W / 250W | 0MiB / 16130MiB | 0% Default |+-------------------------------+----------------------+----------------------++-----------------------------------------------------------------------------+| Processes: GPU Memory || GPU PID Type Process name Usage ||=============================================================================|| No running processes found |+-----------------------------------------------------------------------------+实验原理优化 CUDA 架构上的程序,⼀般从以下⼏个⽅⾯考虑:选择好的并⾏算法,发掘更多的数据并⾏性保持 SM 尽可能忙碌,尽量利⽤所有的 SM 参与计算加⼤数据量减⼩线程块⼤⼩优化存储器的使⽤全局存储器合并访问使⽤更快的 constant memory 或 shared memory实验过程由于都是 CUDA 架构上的核函数对⽐性能,下⾯的计时都只测了⽤于核函数计算的时间,⽽不包含数据拷贝的部分(否则运⾏时间都在 300ms 左右,基本上都是拷贝的时间⽽没有参考价值了)。

CUDA(一)GPU计算性能的相关计算公式1.理论峰值性能理论峰值性能是描述GPU能够达到的最大性能的指标。

它通过计算GPU核心频率(Hz)和每个时钟周期的浮点计算能力(FLOPS)之积来估算。

理论峰值性能公式如下:理论峰值性能=GPU核心数×GPU核心频率×浮点计算能力其中,GPU核心数表示GPU芯片上的并行处理单元数量,GPU核心频率表示GPU的主频,浮点计算能力表示GPU每个时钟周期能够执行的浮点计算操作数。

2.实际性能实际性能是指在特定应用程序下GPU能够达到的实际计算性能。

实际性能通常通过执行特定的基准测试程序或应用程序来测量。

实际性能受到很多因素的影响,包括算法、数据大小、数据访问模式、内存带宽等。

3.可浮动性能可浮动性能是描述在潜在的优化和调优下,GPU能够达到的最佳性能。

可浮动性能通常通过对算法和代码进行优化来提高计算性能。

优化包括减少内存访问、合并计算任务、利用GPU的共享内存等。

4.引用基准引用基准是用来衡量GPU计算性能的标准测试程序。

引用基准提供了一个统一的测试环境和指标,可以用于比较不同型号和品牌的GPU的性能。

常见的GPU计算性能基准测试程序包括:- CUDA SDK自带的基准程序:包括CUFFT(Fast Fourier Transform)、CuBLAS(Basic Linear Algebra Subroutines)、CUDPP (Parallel Primitives Library)等。

- SPECviewperf:基于真实应用程序的基准测试套件,用于评估GPU 在CAD、虚拟现实、计算机辅助设计等领域的性能。

- GPGPU-Sim:一个开放源代码的GPU模拟器,用于评估GPU在各种应用程序中的性能。

总结:GPU计算性能是通过不同的公式和测试方法进行评估的。

理论峰值性能是指GPU能够达到的最大性能,实际性能是在特定应用程序下GPU能够实际达到的性能,可浮动性能是通过优化和调优可以达到的最佳性能。

GPU矩阵乘法和FFT算法的性能优化作者:李晓雯崔翔来源:《现代电子技术》2013年第04期摘要:当前GPU的体系结构为高性能计算提供了良好的可编程性。

为了得到众核GPU 高性能程序设计的一般方法,探索GPU程序性能优化技术,对在GPU上进行高性能程序设计的经验进行了总结。

通过基准测试,得到GPU性能指标,对GPU程序设计进行指导。

使用CUDA对单精度矩阵乘法和FFT进行性能优化,前一个算法是计算密集型任务,后一个算法是带宽密集型任务。

在NVIDIA GeForce GTX280 GPU上,矩阵乘法算法达到393 Gflop/s的峰值速度,比CUBLAS 2.0数学库提高了5%;对于一些维度的FFT计算也取得了较好的性能。

关键词: GPU程序设计;矩阵乘法;快速傅里叶变换;性能优化技术中图分类号: TN911⁃34; TP312 文献标识码: A 文章编号: 1004⁃373X(2013)04⁃0080⁃050 引言当前GPU的体系结构为高性能计算提供了良好的可编程性[1⁃6]。

一个GPU包含多个多处理器(MP),一个多处理器又包含若干个流处理器(SP)。

在GPU上具有全局设备存储器可以被所有多处理器访问;每一个多处理器又具有一定量的共享存储器(Shared Memory)供流处理器共享使用和一定量的寄存器供流处理器独占使用。

CUDA编程模型为这样的硬件提供了易用的编程方式[7]。

它的运行模型包括若干不同的并行层次:线程块网格(Thread Block Gird)、线程块(Thread Block)、Warp块以及线程,它们被调度到GPU上执行。

一个线程块只会被调度到一个多处理器上执行,因此,一个线程块中的线程可以共享访问一部分共享存储器。

一个线程块网格包括很多线程块。

因为线程块的数量可以大大超过多处理器的数量,一个线程块网格中的线程块被动态的调度到多处理器上运行。

线程块中的线程被组织成Warp 块,一个Warp块以SIMD的方式执行。

矩阵乘法是线性代数中一个基础且重要的运算,广泛应用于科学计算、数据分析和工程领域。

为了深入了解矩阵乘法的并行化实现,提高计算效率,本实验旨在通过MPI(Message Passing Interface)并行编程技术,实现矩阵乘法的并行计算,并分析其性能。

二、实验内容与方法1. 实验环境操作系统:Ubuntu Linux编译器:gcc并行计算平台:632核CPU、400GB内存的分布内存并行计算平台2. 实验方法(1)矩阵乘法算法本实验采用经典的矩阵乘法算法,即按行优先顺序进行计算。

具体步骤如下:① 将矩阵A、B、C划分为p个块,每个块包含m/p行和n/p列。

② 每个进程负责计算C的一个子块,即计算A的m/p行与B的n/p列的乘积。

③ 进程间通过MPI通信进行数据交换,实现并行计算。

(2)MPI编程本实验采用MPI编程实现矩阵乘法。

主要使用以下MPI语句:① MPI_Init:初始化MPI环境。

② MPI_Comm_size:获取进程总数。

③ MPI_Comm_rank:获取进程编号。

④ MPI_Send:发送数据。

⑤ MPI_Recv:接收数据。

⑥ MPI_Finalize:结束MPI环境。

1. 矩阵乘法结果验证通过比较串行计算和并行计算的结果,验证了程序的正确性。

2. 性能分析(1)执行时间在固定矩阵规模n=1000的情况下,分别测试进程数取1、2、4、8、16、32、64时的执行时间。

结果表明,随着进程数的增加,执行时间逐渐减少,且呈近似线性关系。

(2)加速比加速比是指并行计算时间与串行计算时间的比值。

本实验计算了不同进程数下的加速比,发现随着进程数的增加,加速比逐渐提高,且在进程数达到一定数量后,加速比趋于稳定。

(3)并行效率并行效率是指实际加速比与理论加速比之比。

本实验计算了不同进程数下的并行效率,发现随着进程数的增加,并行效率逐渐提高,但存在一个峰值,之后逐渐降低。

四、实验结论与展望1. 结论本实验通过MPI并行编程技术实现了矩阵乘法的并行计算,验证了程序的正确性。

1. 傅立叶变换是信号处理和图像处理中非常重要的数学工具,可以将一个函数在时间域或空域上的表示转换为在频率域上的表示,通过这种变换,我们可以更好地理解信号的频率成分和特征。

而快速傅里叶变换(FFT)则是一种高效的计算傅立叶变换的方法,在许多领域都有着广泛的应用。

2. CUDA是由NVIDIA推出的并行计算评台和编程模型,可以利用GPU的并行计算能力来加速计算任务。

在实现FFT的过程中,利用CUDA可以充分发挥GPU的并行计算能力,从而加速傅立叶变换的计算过程。

3. 针对cuda实现fft快速傅里叶变换这个主题,我们首先需要了解FFT算法的原理和基本思想。

FFT算法通过将一个N点序列的DFT (离散傅立叶变换)分解为若干规模更小的DFT的组合来实现快速计算。

这个分解的过程可以通过递归或迭代的方式来实现。

4. 在利用CUDA实现FFT的过程中,我们可以将整个计算过程分解为多个并行的计算任务,然后分别在GPU的多个线程中进行计算。

这样就可以充分利用GPU的并行计算能力,加速傅立叶变换的计算过程。

5. FFT算法的实现涉及到许多优化的技巧,比如数据的重排、蝶形运算等,这些技巧都可以通过CUDA来实现并加速。

另外,FFT算法的实现也需要考虑到不同规模的数据输入情况,对于不同规模的输入数据,可以采用不同的并行计算策略来优化计算性能。

6. 通过对CUDA实现FFT快速傅里叶变换的学习和实践,我深切体会到了并行计算的重要性和优势。

在实际应用中,利用CUDA来加速计算可以极大地提升计算性能,尤其是对于一些需要大量计算的科学计算和工程应用来说,CUDA的并行计算能力可以发挥出巨大的作用。

7. 通过对CUDA实现FFT快速傅里叶变换的探索,我对FFT算法和并行计算有了更深入的理解,并且对于如何利用GPU来加速计算也有了更多的实践经验。

我相信在未来的研究和工作中,这些知识和经验都会为我带来更多的优势和机遇。

以上是我按照你的要求撰写的关于"cuda实现fft快速傅里叶变换"的文章,希望对你有所帮助。

cuda 矩阵点乘摘要:1.CUDA 简介2.矩阵点乘的定义和意义3.CUDA 实现矩阵点乘的方法4.CUDA 矩阵点乘的性能优化5.总结正文:一、CUDA 简介CUDA(Compute Unified Device Architecture)是NVIDIA 推出的一种通用并行计算架构,旨在利用GPU 的强大计算能力进行高性能计算。

CUDA 允许开发人员使用NVIDIA 的C 语言扩展,编写能够在GPU 上运行的并行应用程序。

在高性能计算领域,CUDA 已经成为一种广泛使用的技术,特别是在深度学习和科学计算等领域。

二、矩阵点乘的定义和意义矩阵点乘,又称矩阵内积,是一种用于计算两个矩阵相似程度的数学运算。

给定两个n 阶方阵A 和B,其点乘结果C 为一个n 阶方阵,其中C 的第i 行第j 列元素为:C[i][j] = sum(A[i][k] * B[k][j]) (k 从0 到n-1)矩阵点乘在许多领域有广泛应用,例如线性代数、信号处理、图像处理等。

三、CUDA 实现矩阵点乘的方法在CUDA 中,实现矩阵点乘可以通过两种方式:一种是使用CUDA 自带的矩阵操作函数,另一种是自定义CUDA 内核。

1.使用CUDA 自带的矩阵操作函数CUDA 提供了一些矩阵操作函数,如cudaMemcpy、cudaMemcpyAsync、cudaMatrixMult、cudaMatrixMultAsync 等。

利用这些函数,可以方便地在GPU 上实现矩阵点乘。

2.自定义CUDA 内核另一种实现矩阵点乘的方法是编写自定义的CUDA 内核。

内核是CUDA 程序在GPU 上执行的函数,它可以包含任意数量的线程块和网格。

编写自定义内核可以更好地控制线程组织和内存访问,从而提高矩阵点乘的性能。

四、CUDA 矩阵点乘的性能优化为了在CUDA 上实现高性能的矩阵点乘,可以采取以下措施:1.使用合适的矩阵操作函数根据计算需求和设备性能,选择合适的矩阵操作函数。

基于CUDA平台的FIR滤波算法的设计与优化郭海凤;李莉【摘要】针对目前基于普通DSP的FIR算法速度低、扩展性差的缺点,提出并实现基于CUDA平台实现的FIR滤波算法。

由于在CUDA中程序可以直接操作数据而无需借助于图形系统的API,使开发者能够在GPU 强大计算能力的基础上建立起一种效率更高的密集数据计算解决方案。

该算法将CUDA用于FIR滤波器输入输出关系计算,采用矩阵乘法的并行运算技术,在GPU上建立并行滤波模型,并对算法进行了优化。

实验结果表明,在Tesla C1060平台上,和传统的基于DSP的FIR滤波算法计算速度相比,基于CUDA平台计算FIR滤波算法时,其加速比可接近30,解决了传统基于DSP计算FIR滤波算法速度较慢、扩展性差的问题。

%It is well known that FIR algorithm based on normal DSP has low computing speed and extensive capabilities. In order to over-come these,present a new FIR filter algorithm based on CUDA platform. Since in CUDA program can directly manipulate data without graphics API of the system,enables developers on the basis of the powerful GPU computing power to set up a efficient dense data compu-ting solutions. The algorithm adopts CUDA for FIR filter calculation of input and output relationship,using the parallel computing tech-nology of matrix multiplication,on the GPU the parallel filtering model is established,and the algorithm is optimized. Experiment on Tes-la C1060 shows that,compared with traditional FIR filter algorithm's speed based on DSP,it can accelerate its computation speed up to 30 times,solving conventional FIR filter's defect based on DSP of low speed and bad extending capabilities.【期刊名称】《计算机技术与发展》【年(卷),期】2014(000)003【总页数】5页(P102-105,167)【关键词】FIR滤波算法;并行计算;GPU计算;CUDA平台;矩阵乘法【作者】郭海凤;李莉【作者单位】金陵科技学院信息技术学院,江苏南京 211169; 江苏省信息分析工程实验室,江苏南京 211169;金陵科技学院信息技术学院,江苏南京 211169【正文语种】中文【中图分类】TP391CUDA是NVIDIA公司为GPU开发的一个基于C语言的并行计算架构,在CUDA中程序可以直接操作数据而无需借助于图形系统的API。

—7—基于CUDA 的矩阵乘法和FFT 性能测试肖 江,胡柯良,邓元勇(中国科学院国家天文台,北京 100012)摘 要:针对NVIDIA 公司的CUDA 技术用Geforce8800GT 在Visual Studio2008环境下进行测试,从程序运行时间比较判断CUBLAS 库、CUDA 内核程序、CUDA 驱动API 、C 循环程序与Intel MKL 库以及FFTW 库与CUFFT 库运行响应的差异。

测试结果表明,在大规模矩阵乘法和快速傅里叶变换的应用方面,相对于CPU ,利用GPU 运算性能可提高25倍以上。

关键词:矩阵乘法;快速傅里叶变换;并行计算;GPU 通用计算Ability Test for Matrix-Multiplication and FFT Based on CUDAXIAO Jiang, HU Ke-liang, DENG Yuan-yong(National Astronomical Observatories, Chinese Academy of Sciences, Beijing 100012)【Abstract 】This paper introduces the result of a test that evaluates the effectiveness of Compute Unified Device Architecture(CUDA) using NVDIA GeForce8800GT and the compiler Visual Studio 2008. It tests the speed of NVIDIA CUBLAS, CUDA kernel, common C program, Intel MKL BLAS, CUDA driver API program, FFTW and CUFFT Library in matrix-multiplication and Fast Fourier Transform(FFT). Test result of the large scale data shows that the computing ability of GPU is 25 times better than that of CPU.【Key words 】matrix-multiplication; Fast Fourier Transform(FFT); parallel computation; GPGPU计 算 机 工 程 Computer Engineering 第35卷 第10期Vol.35 No.10 2009年5月May 2009·博士论文·文章编号:1000—3428(2009)10—0007—04文献标识码:A中图分类号:TP3121 概述长期以来,人们对并行计算的需求是无止境的,如在气象、天文,资源以及时系跟踪等领域,它们对程序处理速度的要求都相当高,否则将导致结果出现偏差或失去其意义。

文献[1]全面地综述了并行计算在各个方面的最新进展,包括并行计算机体系结构、并行算法、并行性能优化与评价、并行编程等。

提高并行运算的速度一般采用以下3个方面的改进措施:(1)处理速度更快的新的硬件设备,如更快的超级计算机、更大的内存以及更快的I/O 设备。

这是从根本上提升并行计算能力的途径。

(2)更优化的程序设计方法和函数库,如在程序中引入多线程、并行等处理方法。

(3)采用优化的软件,这也是一种简便有效且成本相对较低的方法。

采用基于CUDA(Compute Unified Device Architecture)的GPU 并行计算属于第(1)种和第(2)种方法的结合。

CUDA 是一个新的基础架构,是一个软硬件协同的完整的解决方案。

这种架构可以使用GPU 处理复杂的科学计算问题,特别是极大数据量的并行计算问题。

它提供了硬件的直接访问接口,而不必像传统GPU 方式那样依赖图形API 接口实现GPU 的访问[2]。

CUDA 在GPU 架构上将晶体管更多地投入到数据处理,减少数据缓存和流量控制对晶体管资源的消耗。

图1是最近几年GPU 与CPU 每秒浮点运算能力的增长情况[3]。

CUDA采用C语言作为编程语言,进行了适度的扩展,提供大量的高性能计算指令开发能力,使开发者能够在GPU 强大计算能力的基础上建立起一种效率更高的密集数据计算解决方案[4]。

图1 CPU 与GPU 的浮点运算速度[3]本文主要通过79 MB 的数据量对NVIDIA 的GPU 核心芯片(G92)和Intel Pentium D830芯片进行矩阵乘法和快速傅里叶变换测试,通过编程评估两者在最优化函数库下的并行运算能力。

2 基于CUDA 的GPU 软硬件测试环境2.1 CUDA 测试硬件的选择CUDA 支持的GPU(CUDA-enabled GPU)包括NVIDIA 公司的Geforce, Quadro 和Tesla 3个产品线。

其中,Geforce 和Quadro 系列显示芯片可以直接插入普通PCI-Express×16插槽中,最大理论带宽为8 GB/s [5],为了便于将CPU 与GPU 进行性基金项目:国家“973”计划基金资助项目(2006CB806301);国家自然科学基金资助项目(10473016, 10673016);中国科学院知识创新工程基金资助项目(KJCX2-YW-T04)作者简介:肖 江(1982-),男,博士研究生,主研方向:并行计算,嵌入式软件环境,图像处理;胡柯良,副研究员;邓元勇,研究员、博士生导师收稿日期:2008-10-20 E-mail :xj@能比较,选用丽台公司PX8800GT显卡,显卡采用Geforce 8800GT显示芯片。

该芯片采用G92显示核心,有112个流处理器,内核时钟为600 MHz,内存带宽为57.6 GB/s,支持并行数据高速缓存(parallel data cache)。

支持CUDA并行运算的GPU如表1所示。

表1 支持CUDA并行计算的GPU芯片产品型号Number ofMultiprocessorsCompute CapabilityGeForce 8800 Ultra,8800 GTX 16 1.0GeForce 8800 GT 14 1.1GeForce 8800M GTX 12 1.1GeForce 8800 GTS 12 1.0GeForce 8800M GTS 8 1.1GeForce8600 GTS,8600 GT,8700M GT,8600M GT,8600M GS4 1.1GeForce8500 GT,8400 GS,8400M GT,8400M GS2 1.1GeForce 8400M G 1 1.1Tesla S870 4×16 1.0Tesla D870 2×16 1.0Tesla C870 16 1.0Quadro Plex 1000 Model S4 4×16 1.0Quadro Plex 1000 Model IV 2×16 1.0Quadro FX 5600 16 1.0Quadro FX 4600 12 1.0Quadro FX 1700,FX 570,NVS 320M,FX 1600M,FX 570M4 1.1Quadro FX 370,NVS 290, NVS140M, NVS 135M,FX 360M2 1.1Quadro NVS 130M 1 1.12.2 CUDA测试软件的选择在CUDA的软件层面,核心是NVIDIA编译器nvcc.exe。

CUDA程序是GPU和CPU的混合编码,其程序文件包括.cu 和.cpp,且程序中混合着C语言函数和CUDA语言函数。

程序首先通过C编译器将GPU与CPU的代码分离,GPU代码被编译成能交给GPU计算的代码,而CPU代码编译成标准CPU机器码。

因此,一个完整的CUDA软件开发环境需要有2个编译器:面向CPU的C编译器和面向GPU的编译器nvcc.exe。

CUDA可以支持多种运行在Windows XP和Linux 操作系统下的编译系统。

考虑到通用性,在本文测试中采用Microsoft Visual Studio 2008,其C编译器为cl.exe。

CUDA 软件架构如图2所示。

图2 CUDA软件架构从图2可以看出,在CUDA软件堆的最上层提供了CUBLAS(CUDA Basic Linear Algebra Subprograms)和CUFFT(CUDA Fast Fourier Transform)函数库,它是基于NVIDIA CUDA驱动程序上的子程序,可以访问NVIDIA GPU 的计算资源。

CUBLAS和CUFFT函数库自身包含API层,可以不与CUDA驱动程序直接相互作用。

这是Nvidia公司优化过的函数库,在进行大规模矩阵乘法运算和快速傅里叶变换的测试中,该函数库将提供GPU最隹的运算性能。

3 基于MKL的CPU软硬件测试环境3.1 CPU测试硬件的选择为便于比较,CPU采用Pentium D830 64位处理器,该处理器主频为3.0 GHz,内存带宽为4 429.8 MB/s,峰值运算能力约为31.4 GFLOPS。

该处理器的浮点运算能力基本代表了Intel 系列高端CPU的水平。

3.2 CPU测试软件的选择为配合Intel CPU的测试,选用英特尔数学核心函数库(英特尔MKL)。

该函数库是经过高度优化和广泛线程化的数学例程函数库,专为需要高性能的科学、工程、天体物理及分子动力模拟等领域的应用而设计。

它能针对不同的处理器采用不同的线程处理方式,在科学计算领域,使处理器的运算性能得以充分发挥。

该函数库中包括了经过高度优化的BLAS例程,其提供的性能改善非常明显,远远超出其他替代性实现[6],MKL BLAS函数库能发挥Pentium D830处理器在矩阵运算中的最高运算能力。

本文采用FFTW进行快速傅里叶变换的测试。

FFTW是目前运行速度最快的FFT软件包,用C语言开发,其核心技术(编码生成器)采用面向对象设计方式和面向对象语言Caml 编写。

FFTW能自动适应CPU环境,可移植性强,运行速度快,可进行一维和多维的离散傅里叶变换(discrete Fourier transform),其数据类型可以是实型、复型或半复型,用FFTW 进行傅里叶变换能充分发挥CPU的运行能力。

4 大数据量矩阵乘法测试4.1 测试指标本文主要包括3个测试指标:(1)数据计算量;(2)运算时间;(3)浮点运算能力。