SCA规范下FPGA的硬件抽象层设计

- 格式:pdf

- 大小:268.65 KB

- 文档页数:4

2018 年 8 月第 4 期现代导航·295·基于 SCA 的硬件抽象层设计石磊(中国电子科技集团公司第二十研究所,西安 710068)摘 要:基于软件通信架构(SCA)硬件抽象层(HAL)的概念,将系统波形开发与硬件平台研制分开, 硬件抽象层通过屏蔽硬件平台相关的底层通信机制、驱动,封装标准的通信接口,实现波形组件间数据通信方式与具体硬件平台的分离,保持波形组件底层通信访问接口的一致性,提高了波形应用的跨平台可移植性。

本文详细介绍硬件抽象层的功能以及应用接口(API),描述了在FPGA 上实现硬件抽象层(HAL)的方法,通过测试波形对 HAL 的实时性能进行了测试。

关键词:SDR; SCA; HAL; FPGA中图分类号:TN925文献标识码:A文章编号:1674-7976-(2018)04-295-05Design of Hardware Abstract Layer Based on Software Communication ArchitectureSHI LeiAbstract:The waveform development is separated from the hardware platform based on Software CommunicationArchitecture (SCA) Hardware Abstract Layer (HAL).HAL can separate data communication mode between waveform components from the hardware platform by shielding drive of the hardware platform and using the standard communication interface, the consistency of the communication interface at waveform component is maintained and the portability of waveform application is improved. This paper introduces the function and application interface of HAL, describes the method of realizing HAL on FPGA,and HAL’s real-time response performance was tested by the test waveform. Key words:SDR; SCA; HAL; FPGA0 引言软件无线电(Software Defined Radio)是指用软 件定义的、能实现多种功能的无线电通信系统。

工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的。

逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。

在逻辑方面,我觉得比较重要的规范有这些:1.设计必须文档化。

要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。

这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间,且这种做法可以使项目处于可控、可实现的状态。

2.代码规范。

a.设计要参数化。

比如一开始的设计时钟周期是30ns,复位周期是5个时钟周期,我们可以这么写:parameter CLK_PERIOD = 30;parameter RST_MUL_TIME = 5;parameter RST_TIME = RST_MUL_TIME * CLK_PERIOD;...rst_n = 1'b0;# RST_TIME rst_n = 1'b1;...# CLK_PERIOD/2 clk <= ~clk;如果在另一个设计中的时钟是40ns,复位周期不变,我们只需对CLK_PERIOD进行重新例化就行了,从而使得代码更加易于重用。

b.信号命名要规范化。

1) 信号名一律小写,参数用大写。

2) 对于低电平有效的信号结尾要用_n标记,如rst_n。

3) 端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪个模块去的关系排列,这样在后期仿真验证找错时后方便很多。

如:module a(//inputclk,rst_n, //globle signalwren,rden,avalon_din, //related to avalon bussdi, //related to serial port input//outputdata_ready,avalon_dout, //related to avalon bus...);4) 一个模块尽量只用一个时钟,这里的一个模块是指一个module或者是一个entity。

1 FPGA硬件系统设计1.1 功能要求1.2 FPGA硬件系统组成(先给出系统组成框图,然后用文字描述框图上的每一部分功能)FPGA是整个系统的核心构成系统控制器波形数据生成器加法器运算/译码分频器等电路系统控制器:控制系统的每个部分状态及之间的协调。

加法器:是10位的。

当只选择1种波形时,加法器等效于传输线,不对波形数据做处理;当选择2种或2种以上波形时,加法器先把送进来的数据进行叠加,把最后的数据的最低2位舍去,把剩下位送到波形DAC中。

运算/译码:正弦波、三角波、锯齿波和叠加的波形的幅值算法都是相同的。

方波A和方波B的波形的幅值算法是相同的。

分频:分频系数有的固定不变,也有可改变的。

具体见程序部分。

存储器1:用来存储正弦波波形数据。

存储器2:用来存储任意波波形数据。

1.3 FPGA最小系统简介(FPGA最小系统板、下载接口等)1.4 FPGA外围电路设计1.4.1 拨码开关电路设计(先给出电路图,然后分析工作原理,并计算上拉电阻。

)1.4.2 显示驱动电路设计(先给出电路图,然后分析工作原理,并计算限流电阻。

)1.4.3 DAC0832电路设计(先给出电路图,然后分析工作原理。

)FPGA与DAC0832接口电路原理图DAC0832是采用CMOS/Si-Cr工艺实现的8位D/A转换器。

该芯片包含8位输入寄存器、8位DAC寄存器、8位D/A转换器。

DAC0832中有两级锁存器,第一级即输入寄存器,第二级即DAC寄存器,可以工作在双缓冲方式下。

DAC0832 输出控制时序图1.4.4 发光二极管指示电路设计(先给出电路图,然后分析工作原理,并计算限流电阻。

) 1.5 硬件电路调试及结果分析2基于DDS 技术的信号发生器设计 2.1 功能要求要求用FPGA 设计一个信号发生器,根据输入信号的选择可以输出锯齿波、三角波、方波、正弦波这四种信号,且设置两种不同频率的信号输出。

用示波器测试D/A 转换器的输出,观测四种波形。

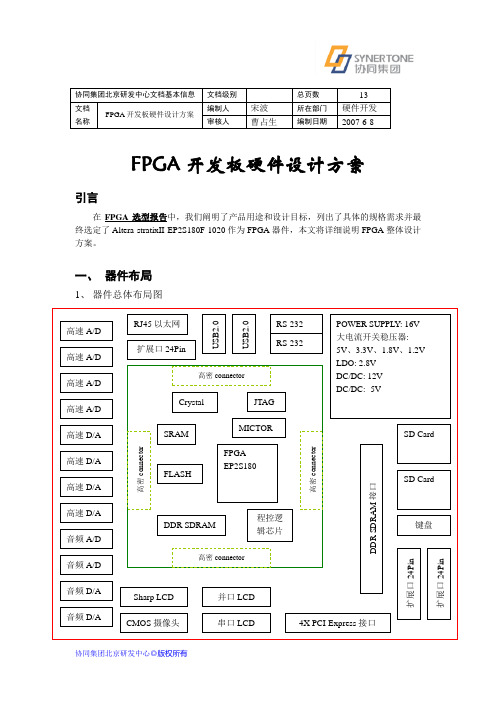

FPGA 开发板硬件设计方案引言在FPGA 选型报告中,我们阐明了产品用途和设计目标,列出了具体的规格需求并最终选定了Altera stratixII EP2S180F-1020作为FPGA 器件,本文将详细说明FPGA 整体设计方案。

一、 器件布局1、 器件总体布局图协同集团北京研发中心文档基本信息 文档级别 总页数 13 文档 名称FPGA 开发板硬件设计方案编制人 宋波 所在部门 硬件开发 审核人曹占生编制日期2007-6-8高速A/D 高速A/D 高速A/D 高速D/A U S B 2.0RS-232 扩展口24P i n扩展口24PinPOWER SUPPL Y: 16V大电流开关稳压器: 5V 、3.3V 、1.8V 、1.2V LDO: 2.8V DC/DC: 12V DC/DC: -5V高速A/D 高速D/A 高速D/A 高速D/A RJ45以太网 键盘音频A/D 音频A/D 音频D/A 音频D/ACMOS 摄像头串口LCDSD Card4X PCI-Express 接口D D R S D R A M 接口并口LCD FPGA EP2S180SRAMFLASHDDR SDRAMJTAG MICTOR 程控逻辑芯片Crystal U S B 2.0RS-232高密connector高密connector高密c o n n e c t o r高密c o n n e c t o rSD CardSharp LCD 扩展口24P i n2、器件总体布局考虑因素➢实用性:将各种应用接口布置在板边方便使用,包括高速A/D D/A的SMA端子、音频A/D D/A的RCA端子、摄像头Connector、LCD Connector、键盘接口、RJ-45接口、RS-232接口、USB2.0 OTG接口、CF Card(可选)、SD Card、Power supply端子、扩展口;PCI-e和DDR存储器接口可放置于板内。

简谈FPGA研发设计相关规范(企业中很实用)大家好!又到了每日学习的时间了,今天我们聊一聊FPGA做开发的时候,有哪些设计规范,从文档到工程建立等,聊一聊也许你会学到很多东西,少走很多弯路哦!在团队项目开发中,为了使开发的高效性、一致性、正确性,团队应当要有一个规范的设计流程。

按照规范来完成项目的设计开发工作,归类清晰明了的工程文件夹级别;项目应拥有良好风格和完整的文档,如设计思路与调试记录及器件选型等;代码书写高效,即统一的书写规范,文件头包含的信息完整,无论自己还是团队他人阅读便一目了然。

一、文档命名: 清晰的文档命名能够让我们思路非常的清晰,所以FPGA工程文件夹的目录要求层次鲜明,归类清晰。

一个工程必须要有一个严整的框架结构,用来存放相关的文档、设计,不仅方便自己查看,也提高了项目的团队工作效率。

下面我们来举例说明: 一级文件夹为工程名二级文件夹多个:用以存放源文件用以存放Testbench文件用来存放设计思路相关类的文件用来存放IP 核的文件等等…二、设计文档化:将自己对设计的思路和调试记录在文档中,有利于以后对模块功能的添加和维护,并且在项目联调时方便项目组其他人员读代码。

也方便不同厂家的FPGA之间移植,以及FPGA到ASIC的移植。

如下图就是设计文档化的举例说明,文档介绍清晰,功能分析明确,有利于以后对模块功能的添加和维护。

设计思路:按照项目的要求,自顶向下的分成若干模块,分别编写功能。

顶层尽量只做行为描述,逻辑描述在底层编写。

模块的编写要有硬件电路思维方式,每一个模块的设计都应考虑是否存在该硬件电路,尽量采用同步设计。

三、编程风格:每个module应存在于单独的源文件中,源文件名应与其所包含的模块名相同。

每个设计都应该有一个完善的文件头,包含公司名称、设计者、设计时间、文件名、所属项目、模块名称及功能、修改记录及版本信息等内容。

代码中的标识符采用传统C语言的命名方法,在单词之间用下划线分开,采用有意义,能反应对象特征、作用和性质的单词命名标识符,以此来增强程序的可读性。

基于VPX架构的软件无线电通信平台设计作者:崔霞霞王少飞来源:《计算机与网络》2020年第11期摘要:针对目前通信装备型谱复杂、通用性差、维护难度高等情况,分析了VPX架构与软件无线电技术的特点,提出了一种基于VPX架构的多体制软件无线电基型通信平台的设计思路,并介绍了平台硬件体系结构、软件体系结构与健康管理系统设计,构建了具有开放性、标准化、模块化特点的无线通信通用硬件平台。

同时搭建测试环境,对设计的软件无线电通信平台数据通路、波形控制等基本功能进行了验证。

关键词:软件无线电;VPX;通信平台中图分类号:TN925文献标志码:A文章编号:1008-1739(2020)11-56-40引言在全球信息网络快速发展与不断变化的高强度军事对抗电磁环境背景下,对传统军事无线通信设备的标准化、软件定义化和应用手段的综合化提出了更高的要求。

美军于20世纪末启动了联合战术无线电系统项目,该项目旨在利用软件无线电技术,联合工业部门共同制定开放的体系结构标准,按照该标准研制一个具有开放体系结构、可灵活配置和可升级的战术电台系列[1]。

通信频谱覆盖美军现役大部分的HF频段、所有的VHF频段和大部分的UHF频段,支持战斗网电台(CNR)、数据链和有关军用战斗通信卫星系统等戰术通信波形,取代原有的数十种型号和数十万部战术电台,最终为全球信息栅格(GIG)提供一个无缝的战术通信网络基础设施。

目前,我国对软件无线电技术在军用无线通信装备综合化设计方面的应用尚处于起步阶段,主要工作是总体架构、硬件、软件标准的研究以及软件无线电原理样机的研制。

大部分已装备的通信设备根据特定用途设计,功能单一、型谱复杂、装备通用性差及维护难度高,极大地限制了不同装备的互连、互通和互操作能力。

为了解决以上问题,通过分析VPX架构与软件无线电技术特点,提出了一种基于VPX架构的多体制软件无线电基型通信平台的设计思路,构造具有开放性、标准化、模块化的通用硬件平台,为实现通信装备的架构统一、波形共用和互联互通提供硬件基础。

基于软件通信体系结构的DSP硬件抽象层研究与设计石贱弟;赵小璞【摘要】Software communications architecture is the only standard of software radio system architecture, which was approved by JPO of the department of defense in USA. At Present, the waveform development based on SCA can not create good portability and reusable components.In this paper, it presents a method for implement DSP HAL-C based on SCA after study on SCA SHS and HAL-C. The result of the test demonstrates the method is flexible in implementing and can create few resource depend and good portability components. This method also accords with the idea of SCA HAL-C.%软件通信体系结构是美国国防部的联合计划办公室JPO发布的关于软件无线电体系架构的唯一标准,当前基于软件通信体系结构的波形组件的开发存在可移植性差、重用性低等问题。

论文在对软件通信体系结构专用硬件补充规范中的硬件抽象层连通性HAL-C内容进行了深入研究的基础上,提出了一种基于软件通信体系结构的DSP硬件抽象层连通性的实现方法。

实践证明,该方法符合软件通信体系结构的硬件抽象层连通性设计思想,并具有实现方便、组件可移植性好、占用资源少等特点。

68M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第4期w w w .m e s n e t .c o m .c nMH A L 硬件抽象层数据流的分级调度设计路小超(中国西南电子技术研究所,成都610036)摘要:分析MH A L 硬件抽象层的技术规范,针对MH A L 硬件抽象层在数据调度方面的局限性,结合数据帧的优先级业务属性设计了具有实时数据传输保障的调度㊂按照优先级将数据帧进行队列管理,完成硬件抽象层数据流的分级调度㊂测试结果表明,该设计能够实现MH A L 硬件抽象层数据流的分级调度,提高了MH A L 硬件抽象层数据调度的灵活性,对推进S C A 软件通信体系架构在嵌入式系统中的应用研究具有积极意义㊂关键词:MH A L ;优先级;队列管理;分级调度;S C A中图分类号:T N 802;T N 923 文献标识码:AD e s i g n o f H i e r a r c h i c a l S c h e d u l i n g M e c h a n i s m f o r H a r d w a r e A b s t r a c t i o n L a ye r D a t a S t r e a m L u X i a o c h a o(S o u t h w e s t C h i n a I n s t i t u t e o f E l e c t r o n i c T e c h n o l o g y ,C h e n gd u 610036,C h i n a )A b s t r a c t :A s c he d u l i n g d e s i g n w i t h r e a l -t i m e d a t a t r a n s m i s s i o n g u a r a n t e e i s d e s i gn e d f o r t h e l i m i t a t i o n o f m o d e m h a r d w a r e a b s t r a c t i o n l a y e r (MHA L )i n d a t a s c h e d u l i n g b y a n a l y z i n g t h e t e c h n i c a l s p e c i f i c a t i o n o f MHA L h a r d w a r e a b s t r a c t i o n l a y e r a n d c o m b i n g wi t h t h e p r i -o r i t y b u s i n e s s a t t r i b u t e o f d a t a f r a m e .Q u e u e m a n a g e m e n t i s a p p l i e d t o d a t a f r a m e s a c c o r d i n g t o t h e p r i o r i t y t o c o m pl e t e t h e h i e r a r c h i c a l s c h e d u l i n g o f t h e d a t a f l o w i n t h e h a r d w a r e a b s t r a c t i o n l a y e r .T h e t e s t r e s u l t s s h o w t h a t t h i s d e s i g n c a n r e a l i z e t h e h i e r a r c h i c a l s c h e d u l i n go f MHA L h a r d w a r e a b s t r a c t i o n l a y e r d a t a f l o w ,i m p r o v e t h e f l e x i b i l i t y o f MHA L h a r d w a r e a b s t r a c t i o n l a y e r d a t a s c h e d u l i n g ,a n d h a v e p o s i t i v e s i g n i f i c a n c e f o r p r o m o t i n g t h e a p p l i c a t i o n r e s e a r c h o f s o f t w a r e c o mm u n i c a t i o n a r c h i t e c t u r e (S C A )i n e m b e d d e d s ys t e m.K e yw o r d s :MHA L ;p r i o r i t y ;q u e u e m a n a g e m e n t ;h i e r a r c h i c a l s c h e d u l i n g ;S C A 0 引 言软件通信体系架构(S o f t w a r e C o mm u n i c a t i o n s A r -c h i t e c u r e ,S C A )为软件无线电的实现提供了一种开放式㊁标准化和通用性强的软件体系架构,由美军联合战术无线电系统(J o i n t T a c t i c a l R a d i o S ys t e m ,J T R S )项目的联合管理办公室制定[1-2]㊂为了实现不同计算单元(如D S P ㊁F PG A )上组件间管理的统一性和通信的标准化,适应部分难以部署S C A 架构的硬件平台,S C A 规范提出了硬件抽象层(MH A L )的概念,规范了A P I 接口[3]㊂近年来,G P P ㊁F P G A 和D S P 等芯片技术发展迅速[4],其丰富的处理资源㊁高度的设计灵活性,使得嵌入式系统正以前所未有的速度向前发展,嵌入式系统中功能软件的规模和复杂性也随之不断提高㊂MH A L 屏蔽了硬件平台底层的通信机制㊁封装标准的通信接口,实现了系统开发过程中软件设计和通用硬件平台相分离,提高了功能软件跨平台的可移植性,显著降低了功能软件的开发成本㊂这些优势使MH A L 在嵌入式系统的应用也越来越广泛㊂MH A L 协议本身未对数据的调度做出明确的规定,MH A L 在实现过程中,特别是在F P G A 等硬件相关性强的器件上部署时,如何快速响应波形数据的传输请求,实现数据的合理高效调度,是架构设计时需要解决的关键问题之一㊂参考文献[5]将所有请求传输的数据缓存在一个队列中,按照 先入先出 的原则发送数据,该调度方法固然保证了公平性,但无法保证部分关键数据的实时调度㊂参考文献[6]为波形组件各逻辑端口配置不同的优先级,高优先级逻辑端口的传输请求得到优先处理,虽然实现了波形组件端口间数据传输请求的差别处理,但无法解决同一个逻辑端口内部不同优先级数据的分级调度问题㊂本文提出了一种新的硬件抽象层分级调度设计,以数据自身的优先级属性为依据,进行队列化管理,保证实时性数据优先处理,一般数据按其优先级进行分级处理,以实现高效的调度策略㊂1 M H A L 硬件抽象层平台MH A L 在嵌入式系统部署时通常使用G P P ㊁F P G A和D S P 三类典型的处理器㊂如图1所示,MH A L 为波形组件封装标准的通信接口,实现波形组件间通信方式与具敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第4期69图1 硬件抽象层平台模型体硬件平台的分离,保持波形组件底层通信访问接口的一致性,从而易于在异构硬件平台间移植波形组件,提高了波形应用的跨平台可移植性[7]㊂波形组件是指为完成无线通信双方信息间的传输而对信息采取的一系列变化过程,其封装的是具体的功能实现,通过MH A L 硬件抽象层提供的用户接口与外界通信,完成用户输入㊁射频信号处理等功能[8]㊂图2为波形组件划分示意图,图中R F 表示射频设备㊁I F 表示中频设备㊁B C P 表示基带协处理组件㊁MA C 表示媒体接入组件㊁L L C 表示逻辑链路组件㊁N E T 表示网络组件㊁S a f e 表示安全/密码设备㊂波形组件的用户接口一般包括控制接口和数据接口,控制接口实现对组件的初始化㊁启动㊁停止㊁状态查询等功能,实现系统对组件的统一管理;数据接口是组件实际通信功能的体现㊂波形组件在硬件上具体实现时,一个波形组件可占用多个组件的逻辑端口㊂功能用户不用关心底层差异,只需要专注于功能算法的研究,使上层波形应用的实现从复杂的底层硬件通信机制中解脱出来㊂图2波形组件划分示意图平台传输方式主要实现系统总线对MH A L 硬件抽象层的接口适配,打通各节点MH A L 硬件抽象层之间的信息交互,支持系统控制管理对MH A L 硬件抽象层的配置和状态监控㊂各节点波形组件之间的通信采用MH A L 硬件抽象层封装的统一数据报文格式,数据报文内容包括流控位(I U )㊁逻辑地址(L o gi c a l D e s t i n a t i o n ,L D )㊁帧长字段(L e n g t h )和数据净荷(P a y l o a d )字段等,每个波形组件的逻辑地址全局唯一,以便数据路由㊂嵌入式系统平台内各节点上部署的波形组件可通过MH A L 进行数据交互㊂对各类处理器的MH A L 而言,与其互换的波形组件通常不止一个㊂当这些波形组件同时有数据发送请求时,MH A L 需具备合理的调度设计,及时响应波形数据的发送请求,实现数据的合理高效调度㊂2 M H A L 硬件抽象层分级调度设计2.1 M H A L 硬件抽象层消息结构设计MH A L 消息从最低有效位到最高有效位以流控位㊁逻辑地址㊁帧长字段和数据净荷字段等顺序排列㊂为了获取每个数据帧的优先级属性,本文对MH A L 标准中的消息结构进行了修改和扩充,添加了优先级字段和保留字段,其消息结构如图3所示,其他字段与MH A L 标准中的消息结构一样㊂图3 M H A L 消息结构图优先级(P r i)占用了5位,最多可支持32种优先级㊂最高优先级定义为00000 ,分配给实时数据业务,一般数据业务可根据项目需求将优先级从高到低依次排序㊂此外,还增加了11位预留位,这样就可根据MH A L 的消息结构获取不同数据帧的优先级属性,方便后续依据数据帧的优先级属性开展分级调度设计㊂2.2 M H A L 分级调度的设计方法通过图3所示的MH A L 消息结构,可获取数据帧的优先级业务属性,依据此优先级业务属性,设计了硬件抽象层具有实时数据传输保障的分级调度设计㊂设计中将波形组件的数据分为实时数据与一般数据,一般数据又可按优先级高低进一步细分,按照优先级的高低将待传输的设计进行队列化管理㊂MH A L 硬件抽象层分级调度设计处理流程如图4所示,分级调度设计的核心是队列管理,为每一种优先级分配一个缓存队列㊂波形组件待发送的数据经入队控制进行分流,按照优先级属性完成数据帧的入队操作,入队控制实现了各波形组件端口数据与不同优先级队列的选通㊂在出队操作时,优先处理实时数据的队列,对于紧急程度最高的数据帧给予更快的队列响应速度;当实时数据对应的队列清空后,再完成一般数据的出队操作,给予高优先级的数据更快的出队响应㊂实时数据的最大排队时间出现在被考察实时数据帧i 准备好发送时,恰好有一个一般数据的最长数据帧λm a x 刚70M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第4期w w w .m e s n e t .c o m .c n图4 M H A L 硬件抽象层分级调度设计处理流程刚开始传输㊂设R 为平台对外传输速率,则实时数据帧的最大排队时间为:d q ue u e =λ m a x +ðij =1λj )/R 波形组件接收数据的流程是图4的逆过程,这里不再赘述㊂分级调度设计优先保证了实时数据传输,但实时数据毕竟是少量的,平台主要还是传输大量的一般业务数据㊂如此,在保证了实时数据快速响应的同时,按照优先级对一般数据提供尽力而为的服务㊂2.3 M H A L 分级调度的队列配置MH A L 分级调度设计最多支持32种优先级,理论上每个节点的硬件抽象层最多应管理32个缓存队列,但在图5 M H A L 控制报文结构实际通信过程中,各节点所需求的优先级队列数量一般极为有限㊂为了避免内存资源的浪费,提高各节点内存的使用效率,可采用动态配置的方式,完成各节点缓存队列的初始化㊁配置与释放等控制㊂缓存队列的动态配置通过标准的控制报文实现,各节点MH A L 硬件抽象层解析接收到的控制报文,实现对队列的动态管理㊂控制报文消息结构如图5所示㊂MH A L 控制报文结构中,控制报文L D 为系统分配的特定L D ,指示当前数据为控制报文;控制指令(C o m -m a n d )通过编码表示不同的控制指令,如队列的初始化㊁新增㊁修改以及删除等指令;配置参数1(P a r a _1)和配置参数2(P a r a _2)表示控制指令的配置信息㊂队列控制报文示例如表1所列㊂MH A L 硬件抽象层在工作过程中,首先收到系统下发的队列初始化指令,指示其应分配的队列数量和队列长度,按照通信数据的优先级注册这些队列,使得每一种优先级的数据都有一个队列与之绑定㊂在MH A L 初始化完成之后,根据系统下发的控制报文指令,可以新增队列㊁开辟新的优先级队列存储空间,也可以修改某个优先级队列的长度,或者完成队列的删除操作㊂3 运行示例以某工程嵌入式系统的F P G A 节点为测试对象,F P G A 型号为X C 7K 325T ,平台通过R a pi d I O 总线进行传输,该总线有效传输速率约为1G b ps ㊂MH A L 硬件抽象层所有波形组件的实时数据传输带宽需求为150M b ps ,高优先级的一般数据传输带宽需求为750M b -p s ,低有效级的一般数据传输带宽需求为150M b p s ,各类数据均匀生成㊂上电配置队列为3个,队列长度设置为12K B ,测试结果如表2所列㊂表1 队列控制报文指令示例序号控制指令配置参数1配置参数21初始化队列队列数量队列长度2新增队列队列优先级队列长度3修改队列队列优先级队列长度4删除队列队列优先级表2 采用分级调度设计的实验测试数据业务类型平均传输时延/μs 有效传输带宽/M b ps 实时数据1.3150高优先级一般数据5.1750低优先级一般数据17.698.6经过实例测试发现,传输时延方面,实时数据传输时延最小,高优先级的一般数据传输时延次之,低优先级的一般数据传输时延最大,数据帧优先级越高,平均传输时延越小㊂因为总线传输带宽受限,分级调度优先保证了高优先级数据的传输,为低优先级的一般数据提供了尽力而为的服务㊂4 结 语基于MH A L 硬件抽象层数据帧的优先级属性,提出了一种分级调度设计,按照优先级对传输数据进行队列化管理,保证了实时数据的优先传输,完成MH A L 硬件抽象层数据流的分级调度㊂仿真结果证明了该分级调度的有效性,对软件无线电系统在嵌入式系统的应用提供了一种设计参考,具有一定的实用价值㊂80M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第4期w w w .m e s n e t .c o m .c n[2]史蒂芬㊃山德,阿明㊃达曼,克里斯汀㊃门兴.无线通信系统中的定位技术与应用[M ].郎为民,译.北京:机械工业出版社,2015.[3]张国家,徐东冬,吴巍,等.一种基于红外线的室内导航设备[P ].江苏:C N 106371438A ,20170201.[4]李冰.超声波室内定位导航装置的设计与实现[D ].哈尔滨:哈尔滨理工大学,2017.[5]谢俐,黄泽伟,周燕.基于R F 射频通信的室内定位导航系统[P ].北京:C N 207440277U ,20180601.[6]张子明,彭惠,刘良勇,等.R O S 系统的无人小车自动跟随方案研究[J ].单片机与嵌入式系统应用,2020,20(2):4651.张子明(工程师),主要研究方向为嵌入式系统开发应用㊂通信作者:张子明,934773134@q q.c o m ㊂(责任编辑:薛士然 收稿日期:2020-11-16)参考文献[1]赵蕾.R a p i d I O 串行总线的硬件抽象层设计与应用[J ].单片机与嵌入式系统应用,2020(5):1113.[2]J O I N T P R O G R AM E X E C U T I V E O F F I C E .S o f t w a r e c o m -m u n i c a t i o n a r c h i t e c t u r e s pe c if i c a t i o n ,v e r s i o n 4.0,2012.[3]J P O J .M o d e m h a r d w a r e a b s t r a c t i o n l a ye r A P I 2.13[M ].S a n D i e go :J T R S S t a n d a r d ,2010.[4]董胜.信号处理平台中F P G A 的组件化运行环境的设计与实现[D ].郑州:解放军信息工程大学,2017.[5]羿昌宇,沈聪,李裕.基于R a pi d I O 的F P G A 硬件抽象层设计[J ].航空电子技术,2015,46(3):610.[6]乌力更,王德刚,黄圣春,等.F P G A 硬件抽象层的路由配置设计与实现[J ].无线电通信技术,2013,39(5):6871.[7]袁扬,谭月辉,孙慧贤,等.基于Z e d B o a r d 的S C A 架构的设计与实现[J ].电子技术应用,2015,41(11):3133,37.[8]余晓玫,高飞.基于软件通信体系结构的波形F P G A 软件设计方法[J ].现代电子技术,2017,40(1):1012.路小超(工程师),主要研究方向为交换式总线和机载通信中间件㊂通信作者:路小超,807342113@q q.c o m ㊂(责任编辑:薛士然 收稿日期:2020-12-18) [8]A n d e r s e n N ,G r a n h a u g K ,M i c h a e l s e n J A ,e t a l .7.7A 118mW 23.3G S /s d u a l b a n d 7.3G H z a n d 8.7G H z i m -p u l s e b a s e d d i r e c t R F s a m p l i n g ra d a r S o C i n 55n m C MO S [C ]//S o l i d s t a t e C i r c u i t s C o n f e r e n c e .I E E E ,2017.[9]E S P 32技术参考手册[E B /O L ].[202010].h t t ps ://w w w.e s p r e s s i f .c o m /z h h a n s /p r o d u c t s /s o c s /e s p32/r e s o u r c e s .[10]C h o i J W ,Y i m D H ,C h o S H.P e o p l e C o u n t i n g Ba s e d o n a n I R UW B R a d a r S e n s o r [J ].I E E E S e n s o r s J o u r n a l ,2017(17):1.[11]C h o i J W ,Q u a n X ,C h o S H.B i D i r e c t i o n a l P a s s i n g P e o pl e C o u n t i n g S ys t e m b a s e d o n I R UW B R a d a r S e n s o r s [J ].I E E E I n t e r n e t o f T h i n gs J o u r n a l ,2017:512522.[12]C h o i J H ,K i m J E ,K i m K T.L e a r n i n g B a s e d P e o pl e C o u n t i n g S y s t e m U s i n g an I R UW B R a d a r S e n s o r [J ].T h e J o u r n a l o f K o r e a n I n s t i t u t e o f E l e c t r o m a g n e t i c E n g i n e e r i n ga n d e n c e ,2019,30(1):2837.[13]K i m Y ,M o o n T.H u m a n D e t e c t i o n a n d A c t i v i t y Cl a s s i f i c a -t i o n B a s e d o n M i c r o D o p p l e r S i g n a t u r e s U s i n g D e e p Co n v -o l u t i o n a l N e u r a l N e t w o r k s [J ].I E E E G e o s c i e n c e &R e m o t eS e n s i n g Le t t e r s ,2016,13(1):812.[14]C h e n Z ,L i G ,F i o r a n e l l i F ,e t a l .P e r s o n n e l R e c o gn i t i o n a n d G a i t C l a s s i f i c a t i o n B a s e d o n M u l t i s t a t i c M i c r oD o p pl e r S i g n a t u r e s U s i n g D e e p Co n v o l u t i o n a l N e u r a l N e t w o r k s [J ].I E E E G e o s c i e n c e &R e m o t e S e n s i n g Le t t e r s ,2018(99):15.鲍润晗(硕士研究生),主要研究方向为雷达信号处理㊁目标区域感知与跟踪;阳召成(副教授),主要研究方向为雷达信号处理㊁区域感知与智能信息处理㊁阵列信号处理㊁机器学习等;赖佳磊(硕士研究生),主要研究方向为雷达信号处理㊁目标跟踪与目标活动识别;周建华(讲师),主要研究方向为嵌入式系统设计㊁智能穿戴产品设计㊁生物电信号处理等㊂通信作者:阳召成,y a n g z h a o c h e n g@s z u .e d u .c n ㊂(责任编辑:薛士然 收稿日期:2020-10-09)研华与A D V A 共创开放式远程实验室研华与A D V A 宣布推出联合T e s t D r i v e 门户计划㊂该计划基于A D V A E n s e m b l e 套件及研华边缘设备,可对u C P E 的S DWA N 和安全解决方案进行远程评估,为需远程工作的网络工程师和架构师提供各种S D WA N u C P E 预集成平台的免费访问权限,从而简化评估流程,不仅满足他们识别软硬件配置选项的要求,还克服了远程评估在物流方面的挑战,例如测试许可㊁把设备运输至分布式团队等㊂A D V A A d v a n t e c h u C P E T e s t D r i v e P o r t a l 的在线流量生成工具,可协助注册用户模拟各种网络服务链和基准应用吞吐量㊂同时,研华与A D V A 联手推出的优化u C P E 平台可满足市场上的各种性价比要求,支持从小型办公室到企业总部和边缘云等各种应用㊂这款解决方案提供全球供应链网络支持,并可通过出厂前预集成实现无缝部署㊂。