DDS模块板布局图

- 格式:pdf

- 大小:27.34 KB

- 文档页数:1

AD9852的引脚说明:D7—D0: Pin1—8,并行编程模式下的8位并行数据I/O口.A0-A5: Pin14—19,并行编程模式下的6位并行地址口.其中,Pin 17与串行通信的复位端复用,Pin18与串行数据输出口复用(3线模式),Pin19与串行数据I/O 口复用((2线模式)。

DVDD: Pin9,10,23,24,25,73,74,79,80,数字电路电源端,相对于数字地3.3V供电,3.135V-3.465V可保证设计指标。

DGND:Pinll,12,26,27,28,72,75,76,77,78,数字地。

AVDD: Pin31,32,37,38,44,50,54,60,65,模拟电路电源端,相对于模拟地3.3V供电,3。

135V—3.465V可保证设计指标。

电路设计时,应加强DVDD和AVDD 之间的去藕,以防噪声相互串扰。

AGND:Pin33,34,39,40,41,45,46,47,53,59,62,66,67,模拟地.NC:Pin13,35,57,58,63,内部无连接的引脚,布线时可以悬空。

I/O UD: Pin20,频率更新端口。

要向AD9852寄存器内写数据,先是写到端口的缓冲器里,等工作模式所需的数据写完后,再在此引脚上加一持续至少8个系统时钟周期的高电平,使DDS芯片按照所设置的方式运行.频率更新也可以设置成内部更新模式,这时DDS按照UDC寄存器设置的值定时自动更新频率,同时输出持续8个系统时钟周期高电平的同步信号。

WRB/SCLK:Pin21,并行模式下的读控制端,与串行模式时钟信号输入端复用.RDB/CSB:Pin22,并行模式下的写控制端,与串行模式片选端复用.FSK/BPSK/HOLD:Pin29,多功能复用引脚.FSK工作模式下,低电平选择频率F1,高电平选F2;BPSK模式时,低电平选相位1,高电平选相位2 ;Chirp 模式时,高电平使DDS输出保持当前频率.SHAPED KEYING:Pin30,高电平使DDS输出有一个调幅过程,若电路设计为低电平,DDS将没有输出。

verilog轻松实现高分辨率DDS

DDS广泛应用于雷达系统、数字通信、电子对抗、电子测量等民用军用设备中。

它的优点:

➀工作频率范围很宽

➁极高的频率分辨率

➂极短的频率转换时间

➃数字调制性能好

➄频率转换连续

DDS基本原理

1.原理框图

图1. FPGA产生DDS框图

上图就是DDS的的FPGA实现框图,完整的DDS还应该在外面有DAC和低通滤波器的,然而很多时候我们是不需要这两个的,因为上图的DDS输出的信号就在数字域,凡是数学域的信号都可以用它参与处理了,所以正弦ROM查找表出来后的信号可以直接给到其他的逻辑使用。

只有要在模拟域参与处理才会把DDS的数字信号用DAC和低通滤波变换成模拟信号。

2.DDS正弦波产生原理

正弦ROM查找表里面就是按地址存放的一个周期的正弦波,可以根据幅值精度要求分成256,1024,等点数,点数越多,波形越精细,越接近真实的模拟正弦波。

但是由于FPGA 资源有限,选择一个能够满足要求的点数就足够了。

相位调整器是控制输出波形的初相位,也就是波形输出起点从哪里开始。

相位累加器是控制ROM地址跳变的。

相位累加器在每个时钟脉冲输入时,把频率控制字累加一次,相位累加器的输出数据就是信号的相位,也就是ROM的地址。

由于相位累加。

4 DDS模块板DDS模块板的主芯片是AD9854芯片作为主芯片,它是ADI公司推出的高性能、高集成度DDS芯片。

AD9854芯片主要性能为:●最高300MHz的系统时钟频率(本模块支持的最高频率为200MHz);●4-20倍可编程参考时钟倍频器;●双路48位可编程频率寄存器;●双路14位可编程相位偏移寄存器;●12位可编程幅度调制以及可编程Shape On/off Keying功能;●超高速、低抖动比较器;●SIN(x)/x校正。

本模块不仅能够产生标准正弦波,在MCU的配合下,还能够实现多种数字载波调制,用途非常广泛。

模块板的硬件布局如图4.1所示,跳线孔对应连线如表4.1所示。

为使AD9854输出高稳定的、低抖动的信号,模块为AD9854提供了相应的硬件滤波电路。

使用AD9854时,一定要注意如下两点:(1)芯片复位。

MCU程序要对AD9854进行上电复位操作;复位操作一定要符合使用要求。

(2)AD9854的内部寄存器一定要配置正确。

图4.1 DDS模块板硬件资源布局附带的参考文档提供了电路原理图、AD8954的Datasheet和中文使用说明。

Demo程序说明如下:●位置:fpga/ demo_project/ test_parallel_dds。

●功能说明:提供了DDS模块板的演示程序。

该程序能够使模块输出频率为156.25KHz的正弦波。

程序的顶层文件提供了更为详细的工程说明,ucf文件提供了模块的连线方法。

●连线方法:(1)跳线连接底板跳线孔模块板跳线孔TP140 TP17TP136 TP9TP139 TP11TP200 TP22TP207 TP23TP206 TP24TP214 TP15TP208 TP13TP212 TP10TP213 TP19TP216 TP16TP222 TP20(2)排线连接底板排插J4 模块板排插J3J4.1 J3.1J4.2 J3.2J4.3 J3.3J4.4 J3.4J4.5 J3.5J4.6 J3.6J4.7 J3.7J4.8 J3.8J4.9 J3.9J4.10 J3.10J4.11 J3.11J4.12 J3.12。

---------------------------------------------------------------范文最新推荐------------------------------------------------------ 基于DSP的DDS信号发生器硬件设计+电路图摘要在21世纪的今天,基于DSP的信号发生器以其编程的高度灵活性,波形的高精度与高稳定性等特点而脱颖而出,具有极大的应用价值和广泛的应用前景。

本文利用高性能DSP芯片加上合理的外围控制电路构成基于DSP的DDS信号发生器,完成电压监测电路的硬件设计工作。

通过对DDS的相应介绍采用查表法实现正弦波的产生,采用高速微处理器实现DDS。

然后完成硬件芯片的选型(TMS320LF2407)和硬件电路的设计工作。

硬件设计主要有核心控制模块电路、片选电路、串行通信电路、AD转换电路及信号采集电路,以此实现硬件电路完成接收上位机的控制信号,采集外部电压信号处理后送给上位机,实现对电压的监控。

关键词:信号发生器,DDS,电压监控,硬件设计11870毕业设计说明书(论文)外文摘要1 / 10TitleDDS signal generator hardware design based on DSPAbstractIn the 21st century,the DSP signal generator stand out for its high degree of flexibility of the programming waveforms, high precision and high stability characteristics, shows great value and broad application prospects.This article takes use of high performance DSP chip with peripheral control circuit DSP-based DDS signal generator,complete the hardware design of the voltage monitoring circuit.Achieve the generation of sine wave with look-up table method corresponding introduction of DDS.Then complete selection of hardware chip(TMS320LF2407)and hardware design.The hardware design mainly consists of core control module circuit, chip select circuit, the serial communication circuit, AD converter circuit and the signal acquisition circuit,In order to achieve the hardware circuit to complete the PC to receive the control signal.The acquisition of an external---------------------------------------------------------------范文最新推荐------------------------------------------------------voltage signal processing to give the host computer,in order to monitoring the voltage.Key words: signal generator,DDS,voltage monitoring,hardware design4.4 PC机与DSP的点对点的串行通信接口244.5 输入输出接口254.5.1A/D的接口254.5.2电压信号采样电路265电路设计中注意的问题28致谢30参考文献313 / 10附录硬件电路原理图321 绪论1.1 信号发生器简介信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

DDS1.模块功能:DDS模块主要采用AD9850、AD812、125MHz有源晶振等器件,DDS是新一代的信号产生方式,它把一系列数字量形式的信号通过DAC转换成模拟量形式的信息。

它的工作方式是利用高速存储器作查询表,然后通过高速DAC产生已经用数字形式存入的波形。

与其他频率合成方法相比,DDS具有频率转换时间短、频率分辨率高、输出相位连续、可编程、全数字化仪与集成等突出优点。

本模块原理图见图1。

图 12.主要器件:(1) AD9850:(a)器件功能:AD9850是AD公司生产的采用先进的CMOS技术的直接频率合成器,主要由可编程DDS系统、高性能模数变换器(DAC)和高速比较器三部分构成,能实现全数字编程控制的频率合成,并且有时钟产生功能,能产生最高125MHZ 的时钟频率,功耗低。

它采用32位的相位累加器将信号截断成14位输入到正弦查询表,查询表的输出再被截断成10位后输入到DAC,DAC再输出两个互补的电流。

DAC满量程输出电流通过一个外接电阻REST调节,调节关系为Iset=32/(1.248V/RSET)。

(b) 器件引脚:AD9850引脚图如图2所示。

D0—D7:8比特数据输入端。

这是一个用于重复输入32比特频率和8比特相位/控制字的8比特数据输入端,D7是最高位,它还是40比特串行数据输入端口。

DGND:数字电路地。

DVDD:数字电路电源。

W_CLK:控制字输入时钟。

此时钟用来控制并行或串行输入频率/相位控制字。

FQ_UD:频率更新时钟。

在此时钟的上升沿,DDS将刷新已输入到数据输入寄存器中的频率(或相位)字,是输入数据寄存器归。

CLKIN:参考时钟输入。

AGND:模拟电路地。

A VDD:模拟电路电源。

Rset:DAC外部电阻Rset连接处。

QOUTB:输出为补充,是比较器的补充输出。

图2QOUT:输出为真。

是比较器的真正输出。

RESET:重新设置。

IOUT:DAC的模拟电源输出。

DDS_BOARD 模块使用说明书V1.0 - 2009.3文档版本 1.0.0文档日期2009年3月第1章概述 1.1 DDS_BOARD 模块概述DDS_BOARD模块包括DA转换、驱动等电路组成。

该模块输入端有两组DA数据,一路数据经DA转换后成作为信号输出,另一路数据经DA转换后成作为输出信号的幅度调节。

经合EDA-SOPC核心板的DDS技术可实现任意波形,一定频率、一定幅度范围的信号输出。

该模块可分别通过14针和16针两条数据线连接到EDA-SOPC核心板上,使用方便。

图1.1 DDS_BOARD模块实物图1.2模块规格工作电压: DC 5V,外接正负5V电源模块尺寸: 60mm×70mm1.3配件清单DDS_BOARD模块 1块16针接口线 1根14针接口线 1根模块说明书及相关资料 1份第2章模块说明2.1 电路原理DDS_BOARD模块包括DA转换、驱动等电路组成。

2.1.1 与EDA-SOPC核心板接口该接口采用14针和16针两条数据线分别与核心板PORT10-DA和PORT12-IO接口相连。

具体如下:2.1.2 信号DA转换及驱动电路由DDS_DA1输入的8位数据通过DAC908转换为模拟信号,再通过AD8058运放驱动后,作为信号输出,该信号在电路图上网络标号为AIN。

2.1.3 幅度控制DA及驱动电路由电阻网络及模拟开关构成的12位DA转换电路,用于输出信号的幅度控制。

1K注意:本模块使用时需要外接正负5V电源,用于模拟部分供电。

2.2 软件原理该模块实际相当于两路DA输出,一路使用D/A芯片完成,即在时钟的作用下,将8BIT的数据送到输出端即在DA的模拟输出相应模拟电压。

另一路DA使用电阻网络完成,12BIT数据控制。

第3章快速上手3.1 电路连接将模块两个接口采用14针和16针两条数据线分别与核心板PORT10-DA和PORT12-IO接口相连。

核心板JTAG通过下载线与计算机相连,连接好处接正负5V电源,打开核心板电源。

DDS,什么是DDS,DDS的结构DDS,什么是DDS,DDS的结构DDS概述直接数字式频率综合器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。

DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit 或者更高),频率分辨率高。

DDS工作原理Error! Reference source not found. 是DDS 的内部结构图,它主要分成3 部分:相位累加器,相位幅度转换,数模转换器(DAC)。

图 1,DDS的结构相位累加器一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS 正是利用了这一特点来产生正弦信号。

如图 2,根据DDS 的频率控制字的位数N,把360° 平均分成了2的N次等份。

图2,相位累加器原理假设系统时钟为Fc,输出频率为Fout。

每次转动一个角度360°/2N,则可以产生一个频率为Fc/2N 的正弦波的相位递增量。

那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,Fout = Fc*M / 2N,相位幅度转换通过相位累加器,我们已经得到了合成Fout 频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。

比如当DDS 选择为2V p-p 的输出时,45°对应的幅度值为0.707V,这个数值以二进制的形式被送入DAC。

这个相位到幅度的转换是通过查表完成的。

DAC 输出代表幅度的二进制数字信号被送入DAC 中,并转换成为模拟信号输出。

注意DAC 的位数并不影响输出频率的分辨率。

输出频率的分辨率是由频率控制字的位数决定的。

基于FPGA的DDS信号发⽣器的设计与实现⼀、实现环境 软件:Quartus II 13.0 硬件:MP801⼆、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是⼀种新型的频率合成技术,具有相对带宽⼤,频率转换时间短,分辨率⾼和相位连续性好等优点。

较容易实现频率、相位及幅度的数控调制,⼴泛应⽤于通信领域。

DDS的实现⽰意图如下图所⽰: 1、将需要合成的信号的数据存储在rom中,合成待输出信号的⽅法请参考: 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照⼀定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。

(1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定⼀个波形的起始时刻在哪个点; (2)频率累加器⽤来控制每隔⼏个点从rom中取⼀个数据,决定⼀个波形的频率; (3)若DDS的时钟频率为F clk ,频率控制字fword = 1,则输出频率为 F out = F clk/2N,这个频率相当于“基频”,若fword = B,则输出频率 F out = B * F clk/2N。

因此理论上由以上三个参数就可以得出任意的 f o 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。

当参考时钟频率越⾼,累加器位数越⾼,输出频率分辨率就越⾼。

3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯⽚来将数字信号转换为模拟信号,这样将dac芯⽚输出的信号接⼊到⽰波器中,才能看到波形; 4、举例说明频率控制和相位控制: 如上图所⽰,这个是⼀个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为dds_control ⽣成的地址信号。

DDS 电路设计摘要本文介绍了DDS的原理,给出了用Altera Cyclone 1 EP1CQ240C8 FPGA芯片实现直接数字频率合成器的工作原理、设计思路、电路结构和仿真结果以及频谱纯度分析。

关键词:直接数字频率合成(DDS);现场可编程门阵列(FPGA);相位累加器一、DDS原理概述1、DDS在基本原理框图如图所示。

它主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。

其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。

DDS的实质是对相位进行可控等间隔的采样。

为实现全数字化的频率可调的频率合成器,本系统基于FPGA采用Verilog HDL设计而成直接数字频率合成器(DDS)。

系统由加法器、累加寄存器、波形存储器、D/A转换器、低通滤波器构成。

在FPGA 里面做到的是D/A转换器之前的部分。

图一DDS原理图DDS系统的核心是相位累加器,它由一个N位累加器与N位相位寄存器构成。

时钟脉冲每触发一次,累加器便将频率控制数据与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位寄存器的数据输入端。

相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使加法器在下一个时钟的作用下继续与频率控制数据相加。

这样,相位累加器在参考时钟的作用下将进行线性相位累加,当相位累加器累加满时,就会产生一次溢出,以完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,相位累加器的溢出频率就是DDS输出的信号频率。

2、DDS参数计算相位寄存器每经过2N/M 个f c 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波频率:2NC outff M •=本设计中,N=10,M 为位宽为32的频率控制字,fc=20Mhz二、DDS 电路结构设计1、电路描述接口信号名称 位宽 方向 描述 备注 freq 32 输入 输入频率字reset 1 输入 复位 高电平异步复位 clock 1 输入 时钟 上升沿有效 sinout 8输出输出波形2补码格式2、电路结构DDS 模块RTL Viewer累加器ACC模块RTL ViewerROM模块RTL Viewer三、DDS电路仿真结果1、Quartus时序仿真设定时序分析工具为Class timing analyzer tool,观察电路最大运行频率fMAX用二补码格式观察2、Modelsim时序仿真参考时钟fc=20Mhz(1)当freq =32'b0000_0001_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 78Khz(2)当freq =32'b0000_0010_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 156Khz(3)当freq =32'b0000_0100_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo =(4)当freq =32'b0000_1000_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 625Khz四、频谱纯度分析(原始信号)频率控制字为32'h08000000时间012345678910x 106X: 6.25e+005Y: 89.17(幅度-频率曲线)频率控制字为32'h08000000频率/Hz幅度/d B(原始信号)频率控制字为32'h04000000时间x 106(幅度-频率曲线)频率控制字为32'h04000000频率/Hz幅度/d B20040060080010001200(原始信号)频率控制字为32'h02000000时间x 106(幅度-频率曲线)频率控制字为32'h02000000频率/Hz幅度/d B(原始信号)频率控制字为32'h01000000时间012345678910x 106(幅度-频率曲线)频率控制字为32'h01000000频率/Hz幅度/d B可见,随着频率控制字的减小,频谱的杂散现象越来越严重。

4 DDS模块板DDS模块板的主芯片是AD9854芯片作为主芯片,它是ADI公司推出的高性能、高集成度DDS芯片。

AD9854芯片主要性能为:●最高300MHz的系统时钟频率(本模块支持的最高频率为200MHz);●4-20倍可编程参考时钟倍频器;●双路48位可编程频率寄存器;●双路14位可编程相位偏移寄存器;●12位可编程幅度调制以及可编程Shape On/off Keying功能;●超高速、低抖动比较器;●SIN(x)/x校正。

本模块不仅能够产生标准正弦波,在MCU的配合下,还能够实现多种数字载波调制,用途非常广泛。

模块板的硬件布局如图4.1所示,跳线孔对应连线如表4.1所示。

为使AD9854输出高稳定的、低抖动的信号,模块为AD9854提供了相应的硬件滤波电路。

使用AD9854时,一定要注意如下两点:(1)芯片复位。

MCU程序要对AD9854进行上电复位操作;复位操作一定要符合使用要求。

(2)AD9854的内部寄存器一定要配置正确。

图4.1 DDS模块板硬件资源布局附带的参考文档提供了电路原理图、AD8954的Datasheet和中文使用说明。

Demo程序说明如下:●位置:fpga/ demo_project/ test_parallel_dds。

●功能说明:提供了DDS模块板的演示程序。

该程序能够使模块输出频率为156.25KHz的正弦波。

程序的顶层文件提供了更为详细的工程说明,ucf文件提供了模块的连线方法。

●连线方法:(1)跳线连接底板跳线孔模块板跳线孔TP140 TP17TP136 TP9TP139 TP11TP200 TP22TP207 TP23TP206 TP24TP214 TP15TP208 TP13TP212 TP10TP213 TP19TP216 TP16TP222 TP20(2)排线连接底板排插J4 模块板排插J3J4.1 J3.1J4.2 J3.2J4.3 J3.3J4.4 J3.4J4.5 J3.5J4.6 J3.6J4.7 J3.7J4.8 J3.8J4.9 J3.9J4.10 J3.10J4.11 J3.11J4.12 J3.12。

1.设计概述(述一下你的设计,如:设计意图,适用范围以及针对用户群。

同时请简要阐述一下你选用本款 Altera 器件来进行设计的原因。

) 为了能拥有一个操作简单,输出频率精度高且稳定,并且拥有足够宽的输出频率范围,所以本项目设计了基于FPGA的任意波形发生器。

本项目的设计由以下几个模块组成:PS/2键盘,FPGA-ER4CE6F17C8开发板,高速D/A模块,TFT 显示屏。

PS/2键盘主要功能是选择任意波形任意2.功能概述(说明你作品的功能以及如何实现该功能)本次设计的100M-DDS波形发生器外设有PS/2键盘输入,TFT彩屏输出。

本波形发生器有2路输出,第1路为固定零点相位输出,第2路可以选择相位位移。

使用者首先在PS/2键盘输入所需输出的波形选择,按确认键,然后选择相位位移度,按确认键,再输入输出频率,再按确认键,则可以看到TFT彩屏输出要求的波形频率,显示屏同时将波形的相关信息显示出来。

3.性能参数(说明你的设计的性能参数。

如果可能,请再比较一下设计参数和该性能实际的实现情况,并评价一下您所使用的 Altera 器件在设计中的功能。

)在设计中使用了IP核中的PLL功能,使得原本50M的时钟频率上升至100M,并且使用了IP核中的ROM功能,在使用ROM功能时将设置ROM中每位数据的位宽为8以及数据量深度位32,所以此设计的输出波形频率可以达到20M,频率精度能达到100M/2^32=0.02HZ。

4.设计结构(设计框图,或同时给出硬件设计框图和软件流程图)5.设计方法(阐述设计的实现方法和设计实现的步骤,并着重描述如何使用SOPC 概念来实现你的设计)通过PS/2键盘的输入,可以选择输出波形,调节相位输出,调节频率输出。

按键信息发送到FPGA中经过FPGA的处理。

FPGA将需要输出的频率通过公式:K=(2^N)*f0/f1计算,其中K为频率控制字,f0为输出频率,f1位输入频率,得出频率控制字K,FPGA再将频率控制字K通过相位累加器得出一系列数据,这些数据就是ROM中的地址,再将ROM中的地址输出,得出输出数字信号,此数字信号则为输出波形的数字信号,再由D/A模块将数字信号转成模拟信号,将模拟信号通过滤波器得出平滑的曲线信号,同时通过TFT彩屏显示输出波形的各项信息。

DDS 信号源设计原理DDS 引言 DDS 原理 DDS 结构 DDS 设计 DDS 描述 DDS 仿真 DDS 实现一、DDS 引言频率合成技术是将一个(或多个)基准频率变换成另一个(或多个)合乎质量要求的所需频率的技术。

在通信、雷达、导航、电子侦察、干扰与抗干扰等众多领域都有应用。

随着各种频率合成器和频率合成方案的出现,频率合成技术得到了不断的发展。

1971年3月美国学者J.Tierncy ,C.M.Rader 和B.Gold 首次提出了直接数字频率合成(DDS__Direct Digital Synthesis )技术。

这是一种从相位概念出发直接合成所需要的波形的新的全数字频率合成技术。

同传统的频率合成技术相比,DDS 技术具有极高的频率分辨率、极快的变频速度,变频相位连续、相位噪声低,易于功能扩展和全数字化便于集成,容易实现对输出信号的多种调制等优点,满足了现代电子系统的许多要求,因此得到了迅速的发展。

目前市面上的DDS 芯片,价格昂贵、功能固定单一,应用受到限制。

本综合实验项目采用基于FPGA 的EDA 技术设计实现DDS 芯片,并可以根据实际需要对其功能进行灵活地修改,配置。

二、DDS 工作原理一个纯净的单频信号可表示为:()()o o t f U t u θπ+=2sin (2-1)只要它的幅度U 和初始相位o θ不变,它的频谱就是位于o f 的一条谱线。

为了分析简化起见,可令U=1,o θ=0,这将不会影响对频率的研究。

即: ()()()t t f t u o θπsin 2sin == (2-2)如果对(2-2)的信号进行采样,采样周期为c T (即采样频率为c f ),则可得到离散的波形序列:()()c o nT f n u π2sin = ()...2,1,0=n (2-3)相应的离散相位序列为:()n nT f n c o ∙∆==θπθ2 ()...2,1,0=n (2-4)式中:c oc o f f T f ππθ22==∆ (2-5)是连续两次采样之间的相位增量。

直接数字频率合成(Direct Digital Frequency Synthesis,DDS)技术是一种新的全数字的频率合成原理,它直接从相位出发合成所需的波形。

其建立在采样定理的基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后再通过查表将数据读出,经过D/A转换器转换成模拟量,把存入的波形重新合成出来。

它具有频率切换速度快、频率分辨率高、相位可连续线性变化、生成的正弦/余弦信号正交特性等特点,并且其数字压控振荡器NCO的相位、幅度均得以数字化。

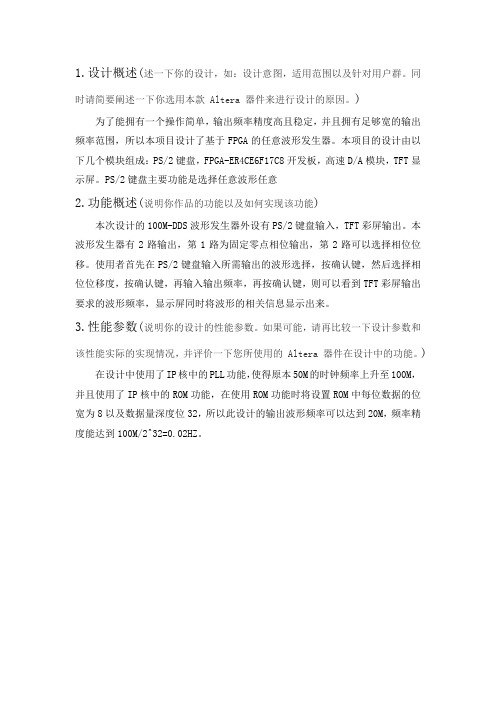

1 DDS基本工作原理DDS主要由相位累加器、波形存储器、数模转换器、低通滤波器构成,如图1所示。

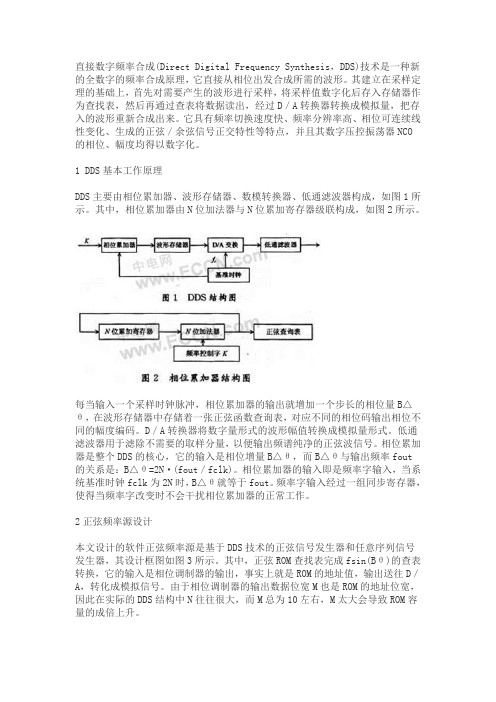

其中,相位累加器由N位加法器与N位累加寄存器级联构成,如图2所示。

每当输入一个采样时钟脉冲,相位累加器的输出就增加一个步长的相位量B△θ,在波形存储器中存储着一张正弦函数查询表,对应不同的相位码输出相位不同的幅度编码。

D/A转换器将数字量形式的波形幅值转换成模拟量形式。

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

相位累加器是整个DDS的核心,它的输入是相位增量B△θ,而B△θ与输出频率fout的关系是:B△θ=2N·(fout/fclk)。

相位累加器的输入即是频率字输入,当系统基准时钟fclk为2N时,B△θ就等于fout。

频率字输入经过一组同步寄存器,使得当频率字改变时不会干扰相位累加器的正常工作。

2正弦频率源设计本文设计的软件正弦频率源是基于DDS技术的正弦信号发生器和任意序列信号发生器,其设计框图如图3所示。

其中,正弦ROM查找表完成fsin(Bθ)的查表转换,它的输入是相位调制器的输出,事实上就是ROM的地址值,输出送往D/A,转化成模拟信号。

由于相位调制器的输出数据位宽M也是ROM的地址位宽,因此在实际的DDS结构中N往往很大,而M总为10左右,M太大会导致ROM容量的成倍上升。

3任意序列信号发生器设计要实现数字调制,正弦频率源模块还需要产生序列信号,如伪随机序列,其在扩频通信系统中起着十分关键的作用。