电子技术课程设计IC管脚分配图

- 格式:doc

- 大小:253.00 KB

- 文档页数:5

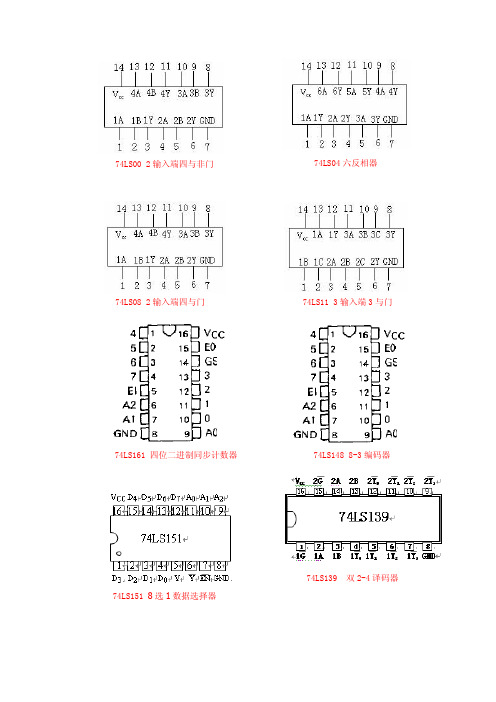

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

交直流调速器电路常用IC引脚功能图说明:从应用的维修的角度,掌握一些IC器件的引脚功能,便于测量部分引脚的电压(电平)状态,判断IC是否处于正常工作状态就够了。

IC内部,具体是个什么电路,是来不及也无须去管它的。

比如单片机电路,重点检测供电、复位、晶振、控制信号、输入信号几个端子的电压(电平)状态,就可以了。

对于数字(包括光耦合器)电路,一般情况下,知道器件引脚功能,便可根据输入、输出端的逻辑关系,测量判断IC的好坏了。

而模拟电路,在变频器电路中,一半是用于处理开关量信号的,如电压比较器等,检测判断上,同数字电路是一样方便的。

部分处理模拟信号的模拟电路,可据动、静态电压的明显变化,测其好坏,也不是太难的事。

因而,只要知晓两点,1:IC是个什么类型的芯片,数字或模拟电路?2:引脚功能,该脚为输入、输出或供电脚?便能实施测量了。

将变频器常用IC引脚功能图,集中附录于后,就不必花费大量时间再去查阅相关的手册了。

一、CPU(微控制器)芯片及外围IC电路引脚功能图:1、CPU芯片-MB90F562B 贴片封装64引脚,应用广泛:2、CPU芯片-S87C196MH贴片封装80引脚,应用广泛:3、CPU芯片-MN18992MDY-6 塑封双列直插,64引脚,用于松下早期DV551、DV561机型:4、CPU芯片-HD6404733037F 贴片封装80引脚,应用广泛:5、存储器引脚功能图:93C56 24C04A 93C66 6、RS485通讯模块引脚功能图:ADM485 SN75179B二、常用运算放大器引脚功能图:LF347四运放电路 LM324四运放电路 LM339四运放(开路集电极输出)LF353 双运放电路 LM393 双运放(开路集电极输出) TL072四运放电路运算放大器多用于电流、电压检测电路,用于处理模拟信号和将模拟信号转换为开关量信号——报警、停机保护信号。

开路集电极输出型多用于电压比较器电路。

实验电路结构图及芯片引脚对应表NO.0实验电路结构图HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8S P E A K E R扬声器译码器译码器译码器译码器译码器译码器译码器译码器FPGA/CPLD PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片附图2-2 实验电路结构图NO.0附图2-3 实验电路结构图NO.1附图2-4 实验电路结构图NO.2ʵÑéµç·½á¹¹Í¼NO.3ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E RÑïÉùÆ÷12345678Ä¿±êоƬFPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2-5 实验电路结构图NO.3附图2-6 实验电路结构图NO.4GNDPIO45PIO46513PS/2接口VCCJ74接PC 机串行通讯接口接口电路单片机接口电路235RS-232B412MHZA键复位P34P33P32X1X2P31P30P35RST GND12345678910VCCPIO11PIO12PIO13PIO14AT89C2051EU3P37P10P11P12P13P14P15P16P17VCC 11121314151617181920PIO15PIO24PIO25PIO26PIO27PIO28PIO29PIO30PIO317.2K P29->A14)27512(PIN30->VCC,PIN3->A15,PIN29->WE)628128(PIN30->VCC,PIN3->A14,RAM/ROMP29->WE)62256(PIN30->VCC,PIN3->A14,6264(PIN30->VCC,PIN29->WR)PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN29->A14)27020(PIN30->A17,PIN3->A15,P29->A14)27010(PIN30->VCC,PIN3->A15,PIO40PIO41PIO42PIO43PIO44R78 200R77 200R76 20010548761413321 视频接口VGA J6A18/A19A18/A15/WE PIO49VCC SLA17RAM_ENVCC GND SLRAMPIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO8PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCC A17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GND D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A1610K VCCVR1PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+5JP251pFC27JP2(COMP)COMP LM311VCC10K -12+124823TL082/1AIN0AOUT1021035.1KR72765TL082/2841+12-12滤波0滤波1FITCOMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CS WR2XFER A GND D GNDVREF8VCC 20VCCJP2(1/2,3/4)D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8P I O 8J P 2(5/6)P I O 8(23)(24)1216272610C L O C K 750K H Z A F I T102C 30103C 29P I O 37P I O 35C O M MC O M PA D E O C A D E NJ P 22018161412108642191715131197531021+5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T附图2-7 实验电路结构图NO.5附图2-8 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图2-9 实验电路结构图NO.7附图2-10 实验电路结构图NO.8附图2-11 实验电路结构图NO.9附图2-12 实验电路结构图NO.BD22D21D20D19D18D17VCC87654321SDA (PIO79)SCL (PIO78)24C01GNDVCCPIO77PIO766PS/254321GNDVCCD-(PIO76)D+(PIO77)SLAVEUSB GND键12键11键9键1010K X 4PIO75PIO74PIO72PIO73VCCP I O 71P I O 76P I O 77P I O 70P I O 69P I O 68数码14数码13数码12数码11数码10数码9PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60hg f e d c b a 888888附图2-13 实验电路结构图COM万能接插口与结构图信号/与芯片引脚对照表附录二:《EDA技术》部分实验参考源程序一、8位硬件加法器设计程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8 ISPORT ( CIN : IN STD_LOGIC;A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER8;ARCHITECTURE behav OF ADDER8 ISSIGNAL SINT : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINSINT <= ('0'& A) + B + CIN ;S <= SINT(7 DOWNTO 0); COUT <= SINT(8);END behav;选择实验电路NO.1验证此加法器的功能。

常用电子管管脚接线图(1)管脚图例管子型号管子型号(1) 管子型号(2)A 6AQ8 ECC85A 6BQ7A ECC180A 6BZ7AA 6CG7A 6FQ7(第9脚为NC)A 6DJ8 ECC88A 6922 E88CCA 7308 E188CCA 8223 E288CCA CcaA 6N1 6н1пA 6N2 6н2пA 6N6 6н6пA 6N11 6н23пA 6240G(第9脚为IC)A 6н30пA1 2C51A1 5670A1 6N3 6н3п常用电子管管脚接线图(2)管脚图例管子型号管子型号(1) 管子型号(2)B 12AT7 ECC81B 12AU7 ECC82B 12AX7 ECC83B 12BH7B 5751B 5814AB 6201 E81CCB 6189 E82CCB 6681 E83CCB 7025B 12AY7 6н4пB ECC99B E80CCB 6N4B 6N10B 2025B1 5687B1 7119 E182CC常用电子管管脚接线图(3)管脚图例管子型号管子型号(1) 管子型号(2)C 6SL7GTC 5691C 6SN7GTC 5692C 6N8P 6н8сC 6N9P 6н9сC ECC33C 6AS7GC 6080C 6N5P 6н5сC 6N13P 6н13сC 6BX7GTC 6BL7GTAD 6BQ5 EL84D 7189D 6P14 6п14п常用电子管管脚接线图(4)管脚图例管子型号管子型号(1) 管子型号(2)E 6F6GTE 6L6GE 6L6GCE 6V6GTE 5881E 6550AE KT88(第1脚为BC)E KT66E 1614E 7581AE 6P3P 6п3сE 6P6P 6п6сE 6G-B8F 2A3F 2c4cF 45F 50F 300BF 4300B常用电子管管脚接线图(5)管脚图例管子型号管子型号(1) 管子型号(2)G 211G 845H EL34 6CA7常用电子管管脚接线图(6)管脚图例管子型号管子型号(1) 管子型号(2)I 7027AK 7868常用电子管管脚接线图(7)管脚图例管子型号管子型号(1) 管子型号(2) L 807L FU-7 г-807M 6AU6 EF94M 6BA6 EF93M 6BD6M 6J4 6ж4пM 6J5 6ж5п常用电子管管脚接线图(8)管脚图例管子型号管子型号(1) 管子型号(2) M1 6AG5 EF96M1 6AK5 EF95M1 6BC5M1 6J1 6ж1пM1 6J3 6ж3пN 6267 EF86N 6J8 6ж32п常用电子管管脚接线图(9)管脚图例管子型号管子型号(1) 管子型号(2) N1 6BX6 EF80N1 6EJ7 EF184O 6SJ7GTO 5693O 6J8P 6ж8с常用电子管管脚接线图(10)管脚图例管子型号管子型号(1) 管子型号(2) P 5AR4 GZ34P 5V4GP 5Z4GT GZ30P GZ32P GZ33P GZ37P U54P 5Z4P 5ц4сQ 5U4GQ 5U4GBQ 5Z3P 5ц3с常用电子管管脚接线图(11)管脚图例管子型号管子型号(1) 管子型号(2) R 5R4GYR 5Y3GTR 274BR 5Z2PS 5Z3S 80常用电子管管脚接线图(12)管脚图例管子型号管子型号(1) 管子型号(2) T 6CA4 EZ81T EZ80U 6X4 EZ90常用电子管管脚接线图(13)管脚图例管子型号管子型号(1) 管子型号(2) U1 6Z4 6ц4пV 7591常用电子管管脚接线图(14)管脚图例管子型号管子型号(1) 管子型号(2) W 6AN8X 6BL8 ECF80X 6U8A ECF82常用电子管管脚接线图(15)管脚图例管子型号管子型号(1) 管子型号(2) Y 7199注:F----灯丝 G----栅极 G1----控制栅 G2----帘栅极 G3----抑制栅极或集射屏 H----热丝 K----阴极 P----屏极IC----管内没有电极连接的空脚,但管座上的焊片不能作中继连接端子用。

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

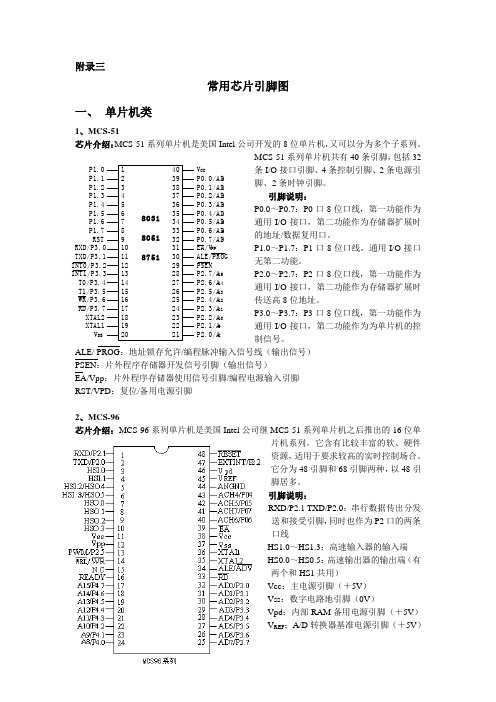

附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751AGND:A/D转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

数字电路实验芯片引脚图数字电路实验一、芯片引脚图真值表:二、组合逻辑电路实验设计题1.举重比赛有3个裁判,一个主裁判A和两个辅裁判B和C,杠铃完全举上的裁决由每个裁判按下自己的按键来决定。

当3个裁判判为成功或两个裁判(其中一个为主裁判)判为成功则成功绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

2.设输入数据为4位二进制数,当该数据能被3整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

3.设输入数据为4位二进制数,当该数据能被5整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

4.试设计一个四人表决器,当四个人中有3个人或4个人赞成时绿灯亮表示建议被通过,否则红灯亮表示建议被否决。

试用74LS151设计此逻辑电路。

5.设输入数据为4位二进制数,设计由此二进制数决定的偶校验逻辑电路,即当此二进制数中有偶数个1时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

6.某楼道内住着A、B、C、D 四户人家,楼道顶上有一盏路灯。

请设计一个控制电路,要求A、B、C、D 都能在自己的家中独立地控制这盏路灯。

试用74LS151设计此逻辑电路。

7.用74LS151实现一个函数发生器,其功能是:当S1S0=00时,Y=AB;当S1S0=01时,Y=A+B;当S1S0=10时,Y=A B;当S1S0=11时,Y=。

试用74LS151设计此逻辑电路。

8.试用两片74LS151实现16选1数据选择器。

三、时序逻辑电路实验设计题1.用十进制计数-译码器CC4017设计一个8盏灯的流水灯电路。

2.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0000→0001→0010→…→1011循环。

每循环一次产生一个进位脉冲。

3.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0100→0101→0110→…→1111循环。

常用电子管管脚接线图(1)管脚图例管子型号管子型号(1) 管子型号(2)A 6AQ8 ECC85A 6BQ7A ECC180A 6BZ7AA 6CG7A 6FQ7(第9脚为NC)A 6DJ8 ECC88A 6922 E88CCA 7308 E188CCA 8223 E288CCA CcaA 6N1 6н1пA 6N2 6н2пA 6N6 6н6пA 6N11 6н23пA 6240G(第9脚为IC)A 6н30пA1 2C51A1 5670A1 6N3 6н3п常用电子管管脚接线图(2)管脚图例管子型号管子型号(1) 管子型号(2)B 12AT7 ECC81B 12AU7 ECC82B 12AX7 ECC83B 12BH7B 5751B 5814AB 6201 E81CCB 6189 E82CCB 6681 E83CCB 7025B 12AY7 6н4пB ECC99B E80CCB 6N4B 6N10B 2025B1 5687B1 7119 E182CC常用电子管管脚接线图(3)管脚图例管子型号管子型号(1) 管子型号(2)C 6SL7GTC 5691C 6SN7GTC 5692C 6N8P 6н8сC 6N9P 6н9сC ECC33C 6AS7GC 6080C 6N5P 6н5сC 6N13P 6н13сC 6BX7GTC 6BL7GTAD 6BQ5 EL84D 7189D 6P14 6п14п常用电子管管脚接线图(4)管脚图例管子型号管子型号(1) 管子型号(2)E 6F6GTE 6L6GE 6L6GCE 6V6GTE 5881E 6550AE KT88(第1脚为BC)E KT66E 1614E 7581AE 6P3P 6п3сE 6P6P 6п6сE 6G-B8F 2A3F 2c4cF 45F 50F 300BF 4300B常用电子管管脚接线图(5)管脚图例管子型号管子型号(1) 管子型号(2)G 211G 845H EL34 6CA7常用电子管管脚接线图(6)管脚图例管子型号管子型号(1) 管子型号(2)I 7027AK 7868常用电子管管脚接线图(7)管脚图例管子型号管子型号(1) 管子型号(2) L 807L FU-7 г-807M 6AU6 EF94M 6BA6 EF93M 6BD6M 6J4 6ж4пM 6J5 6ж5п常用电子管管脚接线图(8)管脚图例管子型号管子型号(1) 管子型号(2) M1 6AG5 EF96M1 6AK5 EF95M1 6BC5M1 6J1 6ж1пM1 6J3 6ж3пN 6267 EF86N 6J8 6ж32п常用电子管管脚接线图(9)管脚图例管子型号管子型号(1) 管子型号(2) N1 6BX6 EF80N1 6EJ7 EF184O 6SJ7GTO 5693O 6J8P 6ж8с常用电子管管脚接线图(10)管脚图例管子型号管子型号(1) 管子型号(2) P 5AR4 GZ34P 5V4GP 5Z4GT GZ30P GZ32P GZ33P GZ37P U54P 5Z4P 5ц4сQ 5U4GQ 5U4GBQ 5Z3P 5ц3с常用电子管管脚接线图(11)管脚图例管子型号管子型号(1) 管子型号(2) R 5R4GYR 5Y3GTR 274BR 5Z2PS 5Z3S 80常用电子管管脚接线图(12)管脚图例管子型号管子型号(1) 管子型号(2) T 6CA4 EZ81T EZ80U 6X4 EZ90常用电子管管脚接线图(13)管脚图例管子型号管子型号(1) 管子型号(2) U1 6Z4 6ц4пV 7591常用电子管管脚接线图(14)管脚图例管子型号管子型号(1) 管子型号(2) W 6AN8X 6BL8 ECF80X 6U8A ECF82常用电子管管脚接线图(15)管脚图例管子型号管子型号(1) 管子型号(2) Y 7199注:F----灯丝 G----栅极 G1----控制栅 G2----帘栅极 G3----抑制栅极或集射屏 H----热丝 K----阴极 P----屏极IC----管内没有电极连接的空脚,但管座上的焊片不能作中继连接端子用。

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC 390为例)附录2 集成电路1. 集成电路命名方法 集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍 集成电路I C 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有L M (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与C M OS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

附录图 2.1双列直插式集成电路的引脚排使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于和V 5.5+低于的低内V 5.0-阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

芯片引脚图及引脚描述文档编制序号:[KKIDT-LLE0828-LLETD298-POI08]555芯片引脚图及引脚描述555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。

1脚为地。

2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。

当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平;2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。

6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。

3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。

4脚是复位端,当4脚电位小于时,不管2、6脚状态如何,输出端3脚都输出低电平。

5脚是控制端。

7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。

555集成电路管脚,工作原理,特点及典型应用电路介绍.1 555集成电路的框图及工作原理555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。

但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。

此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。

由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。