关于解码芯片SAA7115及TVP5150的配置

- 格式:pdf

- 大小:260.85 KB

- 文档页数:5

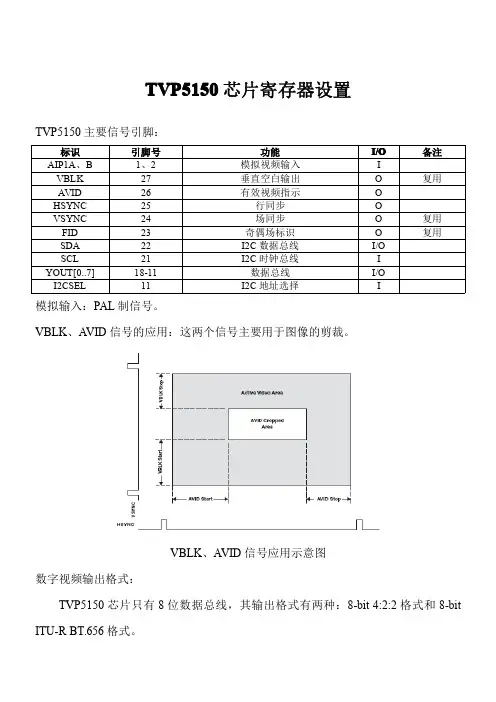

ICETEK-TVP5150-E板使用说明一.TVP5150芯片简介TVP5150A是一款由美国德克萨斯仪器公司(TI)开发生产的低功耗视频解码芯片,它可以将输入的NTSC,PAL,和SECAM视频信号转换成8位ITU-R BT.656格式的数字码流,同时还能输出分离的视频同步信号。

TVP5150A芯片采用32芯TQFP封装,标准工作状态下功耗为115mW,待机状态I2总线进行配置编程。

功耗低于1mW,它采用1.8V供电,I/O采用3.3V。

可以采用CTVP5150A解码芯片提供的主要功能:-超强的同步检测-带模拟处理功能的AD转换器-亮度和彩色信号分别采用4行的梳状滤波器处理-色度处理-亮度处理-视频时序处理和低功耗模式-多种输出格式控制I2总线接口-C-VBI数据处理-复合视频和S端子输入I2总线进行配置和控制,它使用一套内部的寄存器设置运行参数。

TVP5150A解码芯片可以通过C这些寄存器的配置及参数选择,请查阅相关文档。

二.ICETEK-TVP5150板ICETEK-TVP5150板采用TI的TVP5150A芯片实现视频图象的采集、存储和传输。

它采用背板设计,可以安装在ICETEK的A板上使用。

1.原理框图2.ICETEK-TVP5150-E板系统组成(1)视频解码芯片:TVP5150完成对模拟视频信号的解码,形成8位ITU-R BT.656格式的数字码流,供后续模块使用。

(2)逻辑控制芯片:XC95144完成对BT.656格式的数字码流解码,并顺序存储到存储区。

包括提取码流中的同步信号、行起始和结束信号、取出亮度(Y)信息、去除色度信息等。

产生必要的逻辑控制和时序,将解码得到的亮度数据发送到存储区存储。

I2总线接口。

实现C在DSP需要读取状态和图象数据时,产生必要的逻辑控制和时序,将数据从存储区读取并发送给DSP。

在DSP写ICETEK-TV5150-E板的状态寄存器时,将状态信息存储到相应控制寄存器。

MP3内芯你懂吗?主流解码芯片详解MP3内芯你懂吗?主流解码芯片详解点击此处查看全部新闻图片如今购买MP3,理性的消费者一般不只关注外观以及功能,最主要还是机器本身的品质。

MP3的解码芯片已经为越来越多的消费者所关注,不过市场中几千款MP3,到底有哪些解码芯片为其提供良好的品质呢?那就请关注以下这篇文章吧!一、飞利浦芯片产地:荷兰如果一定要评出目前市场上最好的MP3解码芯片的话,那么无疑就是飞利浦芯片了。

飞利浦家族的解码芯片在业界一直以其“功能全,音质好,价格高”而著称。

飞利浦的解码芯片一般都采用的是BGA封装工艺,而国内的这方面技术相当有限,此外,由于飞利浦的解码芯片需要搭配另外的控制芯片电路协同工作,所以产品成本较高。

所以采用飞利浦解码芯片的厂商往往都定位于中高价位,如MPIO和IRIVER这两家韩国的MP3专业厂商。

这两个品牌一个最主要的共同特点就是在产品中全面采用了飞利浦的解码芯片。

因此,他们的产品拥有很高的音质和品质,成为全球MP3爱好者追逐的对象。

1、飞利浦SAA775X系列(SAA7750/7751/7752/7753)飞利浦SAA775x芯片是目前市场上MP3播放器解码芯片组中功能最全(支持CD直录),效果最好的解码芯片之一。

该解码芯片的音质表现为:低音下沉较深、中音表现出色、而相比之下高音则显得一般。

MP3内芯你懂吗?主流解码芯片详解点击此处查看全部新闻图片因为SAA775x中内含DSP(Digital Signal Processing,数字信号处理)和32位ARM RISC处理器,所以能用超高集成度的单颗芯片,音频解码和语音编码等工作,并且可以加入SDMI(Secure Digital Music Initiative,安全式数字音乐)保护其中SAA7750内含DSP和32位ARM RISC处理器,信噪比为90dB。

该芯片兼容多段多档位EQ智能音效,支持以AD PC M格式保存语音记录、同步显示歌名和歌曲信息、Line-in直录,此外还支持USB 1。

基于FPGA的视频编解码系统设计作者:肖飞陈立新来源:《科技资讯》2014年第22期摘要:结合Altera公司Cyclone II 器件中Nios II 嵌入式CPU内核开发板,进行视频编码、解码的硬、软件设计,制作成实物模块。

讨论了视频编码、解码原理,对FPGA、CPLD 逻辑器件进行深入学习和研究,设计了一套视频编码解码简易系统。

关键词:Altera Cyclone II Nios II 视频编解码中图分类号:TP274 文献标识码:A 文章编号:1672-3791(2014)08(a)-0025-02Abstract:The Nios II embedded CPU core develop board based on Altera Cyclone II can apply in video encode, design of hardware and software decoding, making objects units. This paper discussed video encode and decoding principles, carrying on through analysis and exploration to FPGA, CPLD logic devices, and designing a simple system of video encode and decode.Key Words:Altera Cyclone II;Nios II;Video CodecAltera公司是可编程逻辑解决方案的倡导者,Cyclone II FPGA以低于ASIC的成本实现了高性能和低功耗,单独使用Cyclone II FPGA,可以把它用作数字信号处理(DSP)解决方案,实现Nios II处理器时,Cyclone?II FPGA提供高性价比嵌入式处理解决方案[1]。

电子技术DM642嵌入式图像融合处理系统硬件设计研究郝雅婷,马立新(中国矿业大学,北京,100083)摘要:时代的进步使得嵌入式系统朝着更为智能的方向发展,DSP被人们广泛的应用到信号高速处理领域,特别是在图像处理加工领域能够为图像处理提供精准的数据支持。

为此,文章以图像融合硬件系统打造和技术实现为研究对象,将TMS320DM642芯片(以下简称DM642)作为核心处理器,就DM642嵌入式图像融合处理系统的架构、处理器内部配置、硬件设计问题进行探究。

关键词:DM642;嵌入式图像;融合处理系统;硬件设计在工业监督控制、机器视觉、医学影像处理领域会应用一些复杂的算法来进行多图像处理数据,基于这样的要求传统的图像处理系统很难满足系统处理要求。

文章面向实时图像处理,采用模块化的设计思想以新一代高性能多媒体专用DSP芯片DM642为核心,打造了体积小、能耗低、应用性强的嵌入式实时图像处理可拓展硬件平台。

1DM642嵌入式图像融合处理系统的总体架构设计DM642嵌入式图像融合处理系统是基于专用数字媒体应用的高性能32位定点芯片DM642进行设计开发的,系统以DM642为核心,由图像采集模块、图像处理模块、图像存储模块以及电源模块等构成。

系统的具体工作原理如下所示:在系统通电之后从FLASH加载程序,完成对DM642的初始化并通过FC总线来实现对视频编解码芯片的参数设定。

在设定好参数之后开展进行图像信息的采集整理,从四路图像传感器采集到的模拟图像信号经过解码转换成数字图像信号后会通过DM642视频接口传送到DSP 中,再经由内部图像处理后,通过DM642视频接口解码传出显ZBoDM642嵌入式图像融合处理系统总体架构如图1所示。

图1DM642嵌入式图像融合处理系统架构2DM642嵌入式图像融合处理系统的内部配置■2.1系统存储空间DM642嵌入式图像融合处理系统程序或者数据存储空间地址以字节为基本单位进行统一编写,整个寻址空间的大小为4G,片上存储器、片上外设、外部的储存器都能够映射到4G的字节空间中。

最近因为在做视频处理,所以和解码芯片打交道很多,根据DM642的例程总了一些应该配置的东西.注:以下的配置均是指AV信号输入,PAL制式输出的条件(一)关于SAA7115(基于TI的驱动)结构体定义如下:typedef struct {Int cmode; /* capture mode settings */Int fldOp; /* field & frame operation *//* bit 8-15 */Int scale; /* indicate whether to enable 1/2 scaling */Int resmpl; /* indicate whether to enable choroma *//* sub-sampling */Int bpk10Bit; /* 10-bit bit-pack mode *//* bit 16-23 */Int hCtRst; /* horizontal counter reset mode */Int vCtRst; /* vertical counter reset mode */Int fldDect; /* enable whether to use FID input or field *//* detection logic based on the timing *//* relation of hsync and vsync */Int extCtl; /* enable external timing control */Int fldInv; /* enable inversion of the detected fid */Uint16 fldXStrt1; /* field 1 X start */Uint16 fldYStrt1; /* field 1 Y start */Uint16 fldXStrt2; /* field 2 X start */Uint16 fldYStrt2; /* field 2 Y start */Uint16 fldXStop1; /* field 1 X stop */Uint16 fldYStop1; /* field 1 Y stop */Uint16 fldXStop2; /* field 2 X stop */Uint16 fldYStop2; /* field 2 Y stop */Uint16 thrld; /* video FIFO threshold *//* frame buffer settings */Int numFrmBufs; /* number of frame buffers that the driver allocates */ Int alignment; /* frame buffer alignment */Int mergeFlds; /* indicate to interleave data of the two fields in memory *//* or just store them seperated */Int segId; /* memory segment ID, used by MEM_alloc() to allocate *//* video frame buffer *//* EDMA priority */Int edmaPri; /* channel EDMA priority */Int irqId;} VPORTCAP_Params;现在对其中一些关键信息进行注释:Cmode 为vport数据输入格式的选择,如下所示:? VPORT_MODE_BT656_8BIT? VPORT_MODE_BT656_10BIT? VPORT_MODE_RAW_8BIT? VPORT_MODE_RAW_10BIT? VPORT_MODE_YC_8BIT? VPORT_MODE_YC_10BIT? VPORT_MODE_RAW_16BIT? VPORT_MODE_RAW_20BITInt fldOp :帧和场的操作模式,在vport.h中定义,参考选择如下:? VPORT_FLDOP_FLD1? VPORT_FLDOP_FLD2? VPORT_FLDOP_FRAME? VPORT_FLDOP_PROGRESSIVEScale和resample的设置(具体操作见spru629 66页):Int bpk10Bit; /* 10-bit bit-pack mode */10bit数据打包成64bit数据包的方式,包括:? VPORTCAP_BPK_10BIT_ZERO_EXTENDED? VPORTCAP_BPK_10BIT_SIGN_EXTENDED? VPORTCAP_BPK_10BIT_DENSEHOUNT=0,VOUNT=1Xstart~Xstop定义图像的宽度Ystart~Ystop定义图像的高度以上4个参数决定了捕获的图像帧的窗口中的位置Uint16 thrld; /* video FIFO threshold */指示FIFO的门限值,当捕获的数据达到门限值则出发DMA操作Int extCtl; /* enable external timing control */Int vCtRst; /* vertical counter reset mode */Exc和vrst定义了图象捕获中垂直计数器的复位点Int hCtRst; /* horizontal counter reset mode */Exc和hrst定义了水平采样计数器的复位点:当EXC=0,VRST=0:VCOUNT在场消隐开始时复位当EXC=0,VRST=1:VCOUNT在有效行开始时复位当EXC=0,HRST=0:HCOUNT在EAV代码结束时复位当EXC=0,HRST=1:HCOUNT在SAV代码结束时复位当EXC=1,VRST=0,HRST=0时,VCOUNT和HCOUNT都是在VCTL0控制信号的上升沿进行复位;VRST=1,HRST=1时,VCOUNT和HCOUNT都是VCTL0控制信号的下降沿复位Int fldDect; 场检测使能定义FID:FID=0,指场一的开始;FID=1指示场2的开始;使用FID输入判断场的方法适合Y/C图像数据流;SAA7115_ConfParams EVMDM642_vCapParamsSAA7115 = {SAA7115_MODE_NTSC720,SAA7115_MODE_USER,SAA7115_AFMT_COMPOSITE,TRUE,TRUE,INV,LINE_SZ,NUM_LINES*2,TRUE,};typedef struct {SAA7115_Mode inMode;SAA7115_Mode outMode;SAA7115_AnalogFormat aFmt;Bool enableBT656Sync;Bool enableIPortOutput;I2C_Handle hI2C;/* optional parameters for inMode == SAA7115_MODE_USER */Int hSize;Int vSize;Bool interlaced;} SAA7115_ConfParams; (saa7115.h)SAA7115_Mode的inMode和outMode可以是下面结构体定义的其中之一;typedef enum SAA7115_Mode{SAA7115_MODE_NTSC640,SAA7115_MODE_NTSC720,SAA7115_MODE_PAL720,SAA7115_MODE_PAL768,SAA7115_MODE_CIF,SAA7115_MODE_QCIF,SAA7115_MODE_SQCIF,SAA7115_MODE_SIFSAA7115_MODE_USER}SAA7115_Mode;SAA7115_AnalogFormat aFmt;(saa7115.h)指定编码器的模拟输出模式typedef enum SAA7115_AnalogFormat {SAA7115_AFMT_SVIDEO,SAA7115_AFMT_COMPOSITE} SAA7115_AnalogFormat;Bool enableBT656Sync; 把ITU-R BT.656中定义的SAV/EAV代码插入到输出图像数据流Bool enableIPortOutput; 选择图像数据的输出端口为I-PORT还是X-PORTInt hSize; & Int vSize; 分别定义图像的水平宽度和垂直高度Bool interlaced; 指定用户定义的图像采用interlaced(隔行扫描)模式或者progressive(逐行扫描)模式在TI的例程里有一个结构体,里面有对7115需要配置的项目SAA7115_ConfParams EVMDM642_vCapParamsSAA7115 = {SAA7115_MODE_PAL720,SAA7115_MODE_PAL720,SAA7115_AFMT_COMPOSITE,TRUE,TRUE,INV, /*handleI2C */};这个结构体的原形在头文件saa7115.h中定义typedef struct {SAA7115_Mode inMode;SAA7115_Mode outMode;SAA7115_AnalogFormat aFmt;Bool enableBT656Sync;Bool enableIPortOutput;I2C_Handle hI2C;/* optional parameters for inMode == SAA7115_MODE_USER */Int hSize;Int vSize;Bool interlaced;} SAA7115_ConfParams;(1)inMode 定义为视频输出格式(在saa7115.h中定义)typedef enum SAA7115_Mode {SAA7115_MODE_NTSC640,SAA7115_MODE_NTSC720,SAA7115_MODE_PAL720,SAA7115_MODE_PAL768,SAA7115_MODE_CIF,SAA7115_MODE_QCIF,SAA7115_MODE_SQCIF,SAA7115_MODE_SIF,SAA7115_MODE_USER}SAA7115_Mode;(2)outMode 定义为输出视频格式,值同上(3) aFmt 定义为视频输出设备的模拟信号格式(值在saa7105.h)中定义typedef enum SAA7115_AnalogFormat {SAA7115_AFMT_SVIDEO,SAA7115_AFMT_COMPOSITE} SAA7115_AnalogFormat;(4)enableBT656Sync 定义为在输出视频数据流中允许插入ITU-R BT.656定义的SAV/EAV码(5)enableIPortOutput:用I-PORT口代替X-PORT口输出视频流(6)hI2C DM642的I2C控制器的句柄当inMode = SAA7115_MODE_USER时,下面的参数可选(7)hSize 用户定义图画水平大小(8)vSize用户自定义图画垂直大小(9)interlaced 定义用户图像是隔行扫描还是逐行扫描模式由上面我们可以看出,一般在PAL制式采集视频时,需要配置的东西主要是: 输入输出模式、是否有同步信号、使能数据输出口(二).EVMDM642_vDisParamsSAA7105配置VPORTDIS_Params EVMDM642_vDisParamsChan = {VPORT_MODE_BT656_8BIT, /* dmode:3 */VPORT_FLDOP_FRAME, /* fldOp:3 */VPORT_SCALING_DISABLE, /* scale:1 */VPORT_RESMPL_DISABLE, /* resmpl:1 */VPORTDIS_DEFVAL_ENABLE,/* defValEn:1 */VPORTDIS_BPK_10BIT_NORMAL, /*bpk10Bit:1 */VPORTDIS_VCTL1_HSYNC, /* vctl1Config:2 */VPORTDIS_VCTL2_VSYNC, /* vctl2Config:2 */VPORTDIS_VCTL3_FLD, /* vctl3Config:1 */VPORTDIS_EXC_DISABLE, /* extCtl:3 */864, /* frmHSize */625, /* frmVSize */0, /* imgHOffsetFld1 */0, /* imgVOffsetFld1 */LINE_SZ, /* imgHSizeFld1 */NUM_LINES, /* imgVSizeFld1 */0, /* imgHOffsetFld2 */0, /* imgVOffsetFld2 */LINE_SZ, /* imgHSizeFld2 */NUM_LINES, /* imgVSizeFld2 */720, /* hBlnkStart */ 862, /* hBlnkStop */720, /* vBlnkXStartFld1 */ 624, /* vBlnkYStartFld1 */ 720, /* vBlnkXStopFld1 */ 23, /* vBlnkYStopFld1 */360, /* vBlnkXStartFld2 */ 311, /* vBlnkYStartFld2 */ 360, /* vBlnkXStopFld2 */ 336, /* vBlnkYStopFld2 */720, /* xStartFld1 */1, /* yStartFld1 */360, /* xStartFld2 */ 313, /* yStartFld2 */752, /* hSyncStart */ 782, /* hSyncStop */752, /* vSyncXStartFld1 */ 1, /* vSyncYStartFld1 */ 752, /* vSyncXStopFld1 */3, /* vSyncYStopFld1 */320, /* vSyncXStartFld2 */313, /* vSyncYStartFld2 */ 320, /* vSyncXStopFld2 */ 316, /* vSyncYStopFld2 */16, /* yClipLow */235, /* yClipHigh */16, /* cClipLow */240, /* cClipHigh */0x10,0x80,0x80,VPORTDIS_RGBX_DISABLE, /* RGB extract disable */ 0, /* incPix, for raw mode only */(LINE_SZ>>3), /*thrld */3, /*numFrmBufs*/128, /*alignment */VPORT_FLDS_MERGED, /*mergeFlds */NULL, /*segId */EDMA_OPT_PRI_HIGH, /*edmaPri */8 /* irqId */};Display1EVMDM642_vDisParamsChan 参数说明1.dmode:当前值:VPORT_MODE_BT656_8BIT,作用:co-sited luma and chroma data multiplexed into a single data stream因当前位数为8bit,VDOUT9~ VDOUT2脚输出8位数据图1:BT.656 Output Sequence图2:模式选择2.fldOp:field and frame operation mode.当前值:VPORT_FLDOP_FRAME类似于如下3. Scale: horizontal 2x scaling enable。

SAA7111是Philips公司推出的可编程视频输入处理芯片,它利用复合电视信号频谱交错的特点,采用数字式梳状滤波器实现高精度亮色信号分离。

基于离散时间振荡器DTO(DiscreteTime Oscillator)的PLL技术能方便的提供各种频率的高精度锁相。

视频信号中除了包含图像信号以外,还包括了行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前后均衡脉冲等。

因此对视频信号进行A/D转换的电路也非常复杂,SAA7111将这些非常复杂的视频A/D转换电路集成到一块芯片内,为视频信号的数字化应用提供了极大的方便。

SAA7111采用CMOS工艺,SAA7111通过简洁的I2C总线与其他器件(如计算机和嵌入式芯片)连接可方便的构成图像采集的开发系统。

SAA7111内部包含两路模拟处理通道,可以选择视频源(如CVBS,Y/C)并可抗混叠滤波,同时还可以进行模数变换、自动嵌位、自动增益控制、时钟产生、多制式解码等,另外还可以对模拟输入控制、亮度、对比度和饱和度和数据输出格式进行控制。

SAA7111芯片内的场同步信号VREF,行同步信号HREF、时钟参考输出LLC2、像素时钟信号CREF都由芯片引脚直接引出,从而省去了时钟同步电路的设计,系统内部锁相环技术的集成使得可靠性有了很大的提高,并极大的降低了设计的复杂度。

除此之外在价格上相比其它公司的产品也占有很大的优势,所以在本系统中采用SAA7111作为视频采集芯片。

特性:四个模拟输入,内部模拟源选择器,e.g. 4 × CVBS or 2 × Y/C or (1 × Y/C and 2 × CVBS)两个模拟预处理通道主要通道的完全可编程静态增益或选定CVBS或Y/ C通道自动增益控制切换白峰控制两个内置的模拟抗混叠滤波器两个8位视频CMOS模拟- 数字转换器(ADCs)片上的时钟发生器行锁定系统时钟频率H -同步处理和时钟产生数字锁相环需要所有的标准只有一个晶体(24.576 MHz的)水平和垂直同步检测50/60赫兹场频与PAL和NTSC标准之间自动切换的自动检测对于不同制式亮度和色度信号处理PAL BGHI,PALN,PAL M,NTSC M,NTSC N和NTSC 4.43用户可编程的亮度峰值或光圈校正通过色度梳装过滤跨色彩还原NTSCPAL纠正PAL相位误差延迟线实时状态信息输出(RTCO)亮度对比度饱和度(BCS)的控制芯片YUV(CCIR- 601)总线支持的数据传输速率:- 864×FH =13.5兆赫625线源- 858 ×FH =13.5兆赫为525线源。

ICETEK-TVP5150-EM板使用说明ICETEK-DM642-PCI板是一个集视频输入输出、音频编解码、网络传输、PCI接口等功能于一身的嵌入式应用开发平台,可用于软、硬件的评估。

为了在此平台上评估更多的硬件与DM642的连接应用,板上留出了3个扩展插座,即DCP1-3(这些扩展插座的定义,请参考ICETEK-DM642-PCI板附带的说明文档“TMS320DM642评估板背板规范.pdf”),它们提供了EMIF、Vport口的接口以及电源和地等信号。

一.背板设计设计目的:由于ICETEK-DM642-PCI板上视频输入部分的组成为:视频解码芯片SAA7115(A,B)->DM642Vport(0,1),其中的视频解码芯片可供两路活动视频信号同时输入,还支持Y/C分离信号的输入。

如果在实际应用中,我们不满足此输入配置,而需要单路输入或更多路的输入,或者需要采用其他的视频解码芯片取代SAA7115,比如构造数字信号的输入模块以连接数字摄像输入设备,就可以通过设计一个插在DCP1-3上的扩展背板来实现硬件和软件的评估。

ICETEK-TVP5150-EM背板就是一个直接接到DM642的Vport0上的视频解码芯片,构成TVP5150->DM642 Vport0的视频输入通路。

通过软件设置,DM642采用此此背板上的复合视频插座输入,从而绕开了ICETEK-DM642-PCI板上提供的视频输入通路。

TI TVP5150A芯片简介:TVP5150是一款视频解码芯片,它有1个9bit的AD转换器,可进行N 制和PAL制复合视频信号及Y/C信号的解码和输出,可产生8bit4:2:2格式或ITU-R BT656格式的输出,由一个标准的I2C总线接口进行控制。

具体的控制和输出方法请参见TVP5150A芯片的数据手册。

设计思路:电源:背板的供电采用3.3V,考虑功耗因素,背板可以由ICETEK-DM642-PCI板驱动,所以从ICETEK-DM642-PCI板上的DC_P1接口直接取电。

COMB FILTER • Universal VBI Slicer • Macrovision ®P h i l i p s S e m i c o n d u c t o r sw w w .s e m i c o n d u c t o r s .p h i l i p s .c o mThe SAA7115 provides the front-end digitization and processing of analog video inputs for next-generation set-top boxes,digital televisions,video projectors,personal video,and DVD recorders.A single-chip 9-bit video decoder with 2x-oversampling,the SAA7115provides video capture for a range of applications including advanced large-screen devices such as LCD projectors and HDTVs.Decoding NTSC,PAL and SECAM signals using fully automatic standarddetection,the SAA7115 also includes a pixel accurate H/V scaler,a frame accurate audio clock and an optional square pixel output rate.Designed with service providers in mind the SAA7115complies with Macrovision’s Copy Protection Detect Specification Revision 1.00 and is also well suited for video surveillance systems requiring ultra-fast frame switching.In addition,it is fully pin-to-pin compatible with Philips’ highly successful SAA7114 Video Decoder,making it the ideal solution for a multitude of applications.Product highlightsThe SAA7115 from Philips Semiconductors is a feature-packed video-capture device,offering these major benefits:• Dual 9-bit low noise analog-to-digital converters with 2x-oversampling• Worldwide NTSC/PAL/SECAM decoding with full auto-detection• 6 analog inputs allow flexible combinations of CVBS and S-Video • Best-in-class dynamically adaptive worldwide 4-line comb filter • High performance,pixel-accurate,horizontal and vertical scaler • Automatic VCR detection and optimization • Optional square pixel output rate• Universal VBI data slicer including WST 525/625 T eletext,VPS,US/European Close Captioning (CC),WSS 525/625 (CGMS),US NABTS,VITC 525/625,Gemstar ®1x/2x and Moji Japanese T eletext• Flexible VBI read back via industry standard I 2C-bus• Comprehensive three-level hardware Macrovision ®detection certification• Ultra fast field-lock for advanced video surveillance and security applications• Patented real-time control (RTC) for video editing and time-shift applications• LQFP100 package,pin-to-pin compatible with Philips highly successful SAA7114.T argeting next generation digital video applications For superior performance in today’s PC and consumer video products,as well as tomorrow’s hot new digital video applications,check out the SAA7115 for the following:• PC video capture and editing• Personal Video Recorders (time shifting)• Cable,terrestrial,and satellite set-top boxes • Video projectors • Flat Panel Displays • DVD recorders • Digital televisions• Line doublers and scan converters • Video surveillance and security • Video editing and post production • Video conferencing • Digital VCRs.Multistandard video decoding,scaling,and data processing on one ICWhen a video application demands high quality decoding – flexible scaling and robust data processing – look to the SAA7115 video decoder.Highly integrated and supporting worldwide video standards,the SAA7115 is designed to provide a digital video stream for any video-input application.This includes input to the image port of a VGA controller,for capture to system memory,or to provide digital baseband video to any MPEG encoder,LCD scaler or picture-improvement processor.The SAA7115 features a two-channel analog preprocessing circuit,dual Clock Generation Circuits (CGCs),a digital multistandard decoder and a high-performance pixel-accurate scaler.It accurately decodes all variations of PAL,SECAM,and NTSC signals intostandard ITU-601 compatible component colour values.It accepts CVBS or S-Video (Y+C) from TV or VCR sources as analog inputs – including weak and distorted signals – as well as digital video via an integrated bi-directional expansion port (X Port).At its image port (I Port),the SAA7115 supports scaled 8- or 16-bit output data with auxiliary reference data for interfacing to VGA controllers.For capturing serially coded data in the vertical blanking interval (VBI data),the SAA7115 can use its scaler for interpolating raw video samples to the required data output.Programmable on a line-by-line basis to one of 15 data types,the versatile data slicer can also output through the image port or via the industry standard I 2C-bus.The SAA7115 incorporates frame-locked audio clock generation,to ensure the same number of audio samples is always associated with a frame,or a set of fields.This prevents loss of synchronization between video and audio during capture or playback.Furthermore the second,integrated CGC can be optionally used to enhance this audio clock for an ultra low jitter frame-locked audio clock.Controlled via the I 2C-bus,the SAA7115 offers full write-read capability for all programming registers,at up to 400 kbits/s.RTC OUTPUT RTSx6 ANALOG INPUTS ALLOW FLEXIBLE COMBINATIONS OF CVBS AND S-VIDEOCONTROLPOWER-ON CONTROL AUX PULSE CONTROL XTAL AND VIDEO CLOCKS CHROMAPROCESSINGLUMINANCE PROCESSINGINPUT DATA CONTROLANALOG INPUT PROCESSINGCbCrCDYNAMIC COMBING ENGINESYNCHRONIZATIONSAA7115 VCVBSYADC1ADC2SSSYVideo acquisition and clock generation featuresThe analog pre-processing circuit incorporates source selection,anti-aliasing filters and two low-noise analog-to-digital converters.This sub-system includes input clamps,white-peak control and user-selectable automatic or fully programmable gain control to match specific signal properties.The 9-bit low-noise CMOS analog-to-digital converters provide high performance with oversampling at 27 MHz – twice the ITU-601 standard.On-chip line-locked clock generation also complies with ITU-601and offers free-running capability with horizontal and vertical synchronization generation.• Six analog inputs with internal analog source selectors,e.g.6x CVBS or (2 x YC and 2 x CVBS) or (1 x YC and 4 x CVBS)• T wo built in analog anti-aliasing filters• Dual 9-bit low noise analog-to-digital converters with 2x-oversampling• Fully programmable static gain or automatic gain control (AGC) for the selected CVBS or Y/C channel• Automatic Clamp Control (ACC) for CVBS,Y and C • Switchable white peak control• Requires only one crystal (32.11 MHz or 24.576 MHz) for all standards• Independent gain and offset adjustment for raw data path • On-chip line locked clock generation according to ITU-601• Generation of a frame locked audio master clock to support a constant number of audio clocks per video field • Second onboard analog PLL can be used for:- on-chip line-locked square pixel clock generation for PAL and NTSC square pixel video output or- optional generation of a low jitter frame-locked audio clock from the audio master clock,through reuse of the analog square pixel PLL.Supports audio clock frequencies of 256*fs,384*fs and 512*fs (fs = 32 kHz,44.1 kHz or 48 kHz).• Versatile universal VBI-data decoder,slicer,clock regeneration and byte synchronization for:- WST 525/625 T eletext - VPS- US/European Close Captioning (CC)- WSS 525/625 (CGMS)- US NABTS - VI TC 525/625- Gemstar ®1x/2x- Moji Japanese T eletext.• Flexible VBI read back via industry standard I 2C-bus of the following decoded data types:- US/European Close Captioning (CC)- WSS 525/625 (CGMS)- Gemstar ®1x/2x.Video decoder featuresThe decoder in the SAA7115 is based on the principle ofline-locked clock decoding,yielding the highest quality video with maximum discrimination and automation.The decoder features advanced two-dimensional chrominance/luminance separation using a dynamically adaptive comb filter.• Digital PLL for synchronization and clock generation for all stan-dards and from non-standard video sources,e.g.consumer grade VCR• Automatic detection of 50 Hz / 60 Hz field frequency,and auto-matic recognition of all common broadcast standards • Enhanced horizontal and vertical sync detection• Luminance and chrominance signal processing for PAL BGDHIN,combination-PAL N,PAL M,NTSC M,NTSC-Japan,NTSC 4.43and SECAM (50 Hz / 60 Hz)• High performance 2/4-line comb filter for two-dimensional chrominance/luminance-separation operating with dynamically adaptive comb filter parameters• Independent Brightness Contrast Saturation (BCS) adjustment • User programmable sharpness control • Automatic TV/VCR detection • X-port video output as:- noise shaped 8-bit ITU-656 video or- full 10-bit ITU-656 interface (DC-performance 9-bit).• Certification for detection of copy protected input signals:- according to Macrovision’s Copy Protection Detect Specification Revision 1.00- indicating level of protection.8- or 16-BIT SCALED DATAI 2S CLOCKSI 2CX PORT DATA AND SYNCX PORT I 2C PORTAUDIO CLOCKSMSD805BOUNDARY SCANDECODER OUTPUT CONTROLI PORT OUTPUT FORMATTERAND VIDEO FIFOY Cb CrY Cb Cr SY Cb Cr SUNIVERSAL VBI ENGINEHORIZONTAL PROCESSINGH PORT VIDEO DECODERTASK AND EVENT CONTROLLERBCS CONTROLVERTICAL PROCESSINGSCALER FIR-PREFILTER SAA7115Leading CompetitorSAA7115Leading CompetitorPhilipsSemiconductorsP h i l i p s S e m i c o n d u c t o Additional featuresThe SAA7115 provides flexibility for easy,cost-effective design of today’s video applications.• Generation of an audio serial and left/right (channel) clock signal• Real-time signal port includes continuous line-locked reference clock and real-time status information to support RTC level 3.1 standard • Power-on control• CMOS 3.3 V device with 5 V tolerant digital inputs and I/O ports• Software controlled power-saving standby modes• Programming via serial I 2C-bus;full read-back by an external controller,at a rate of up to 400 kbits/s• Boundary-scan test circuit conforming to IEEE-1149.b1-1994• Available in LQFP100 (SOT407-CD5) package• Pin-to-Pin compatible with Philips Semiconductors SAA7114video decoder.Video scaler featuresThe versatile scaler provides variable horizontal and vertical up- and down-scaling to randomly sized windows and has independent brightness,contrast and saturation control for scaled outputs.Vertical scaling offers linear phase interpolation;6-bit phase accuracy and an accumulating filter for anti-aliasing.Horizontal phase-correct up- and down-scaling means improved signal quality of scaled data,especially for compression and video conferencing applications.This scaling,at 6-bit phase accuracy (1.2 ns step width),uses an anti-aliasing and accumulating filter.• Horizontal and vertical down-scaling and up-scaling to randomly sized windows• Horizontal and vertical scaling range:variable zoom to 1/64(icon) (Note:H and V zoom are restricted by the transfer data rates)• Vertical scaling with linear phase interpolation andaccumulating filter for anti-aliasing (6 bit phase accuracy)• Conversion to square pixel format• Generation of a video output stream with improved synchronization grid at the I-Port• T wo independent programming sets (tasks) for scaler,which define two “ranges” per field or two sequences over frames • Fieldwise switching between decoder and expansion port (X-port) input• Brightness,contrast and saturation controls for scaled outputs.SCB 73November 2001 9397 750 09016The Netherlands。

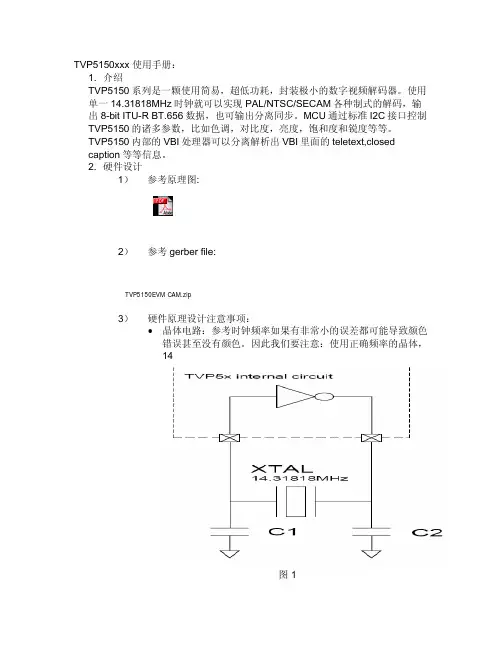

TVP5150xxx 使用手册:1. 介绍TVP5150系列是一颗使用简易,超低功耗,封装极小的数字视频解码器。

使用单一14.31818MHz时钟就可以实现PAL/NTSC/SECAM各种制式的解码,输出8-bit ITU-R BT.656数据,也可输出分离同步。

MCU通过标准I2C接口控制TVP5150的诸多参数,比如色调,对比度,亮度,饱和度和锐度等等。

TVP5150内部的VBI处理器可以分离解析出VBI里面的teletext,closedcaption等等信息。

2. 硬件设计1)参考原理图:2)参考gerber file:TVP5150EVM CAM.zip3)硬件原理设计注意事项:•晶体电路:参考时钟频率如果有非常小的误差都可能导致颜色错误甚至没有颜色。

因此我们要注意:使用正确频率的晶体,14图114.31818MHz,误差在50ppm内为佳;C1,C2的选择应该根据晶体的负载电容,,其中Cstray一般取3-8pF。

•上电时序:由于TVP5150AM1内部有多种电压,为了保障系统的正常工作,我们建议1.8v电压先上,然后上3.3v电压,最后相隔100ms后给系统复位。

•视频输入管脚及增益设置:在匹配电阻为75欧姆情况下,最大的峰峰值为1.24v,如下图:图2这时候就超过了TVP5150允许的最大输入值0.75v,我们通常采用电阻分压网路来解决该问题。

图3• Anti-aliasing滤波器设计:为了防止频带外的杂讯干扰,通常在模拟前端加入低通滤波器。

如图4,是给CVBS信号、S-Video的滤波器,它们不同主要是因为TVP5150对这两种信号的采样频率不同。

图4图5.幅频特性,频响特性4)PCB layout注意事项:•地的分割:建议分模拟地和数字地,并使它们在相应的电源层下。

•不要将任何信号放在电源层或地层上。

•确保电源层等于或小于相应地层的大小。

•不要使模拟信号靠近时钟信号。

•不要将数字信号放在模拟区域。

TVP5150调试报告1.引言2.调试环境我们在一台Ubuntu 20.04 LTS操作系统的电脑上进行了TVP5150的调试。

该计算机配备了Intel Core i7处理器和8 GB内存。

我们采用了TVP5150的评估板,连接到计算机的PCI-Express插槽。

为了完成调试和测试,我们使用了TVP5150的软件开发工具包。

3.调试步骤在开始调试之前,我们首先通过在设备管理器中检查PCI设备列表,确认TVP5150评估板已正确连接到计算机。

然后,我们安装了TVP5150的软件开发工具包,并按照用户手册中的指示进行设置和配置。

接下来,我们打开了TVP5150软件开发工具包提供的示例应用程序,并按照用户手册中的说明进行了配置。

我们设置采样频率为25 fps,并选择了适当的视频输入源。

然后,我们启动了应用程序,并观察到TVP5150成功将视频信号输入到计算机中。

为了进一步测试TVP5150的性能,我们使用了一段来自摄像头的实时视频流,并将其通过TVP5150进行采集和处理。

我们观察到TVP5150的图像质量非常出色,并且没有明显的失真或噪声。

此外,TVP5150的处理速度也非常快,几乎即时将视频流显示在计算机屏幕上。

最后,我们进行了一些附加的测试,以验证TVP5150的其他功能。

我们测试了TVP5150的视频捕捉能力,并成功捕获了一幅单帧图像。

我们还测试了TVP5150的音频处理功能,并将音频信号输入到计算机的扬声器中。

4.结论通过对TVP5150的详细调试,我们发现它具有优秀的视频采集和处理性能。

TVP5150的图像质量非常出色,并且其处理速度快且稳定。

此外,TVP5150还具有其他功能,如视频捕捉和音频处理,使其成为一款功能齐全的视频处理器。

尽管我们在本次调试中没有遇到明显的问题或故障,但我们仍建议在实际应用中进行更加细致的测试和调试。

这将有助于确保TVP5150在各种情况下都能正常工作,并满足用户的需求。

SAA7115视频解码芯片寄存器的配置与应用摘要:为确保视频传输过程中传输数据的正确性,设计了一个简单的视频信号传输系统。

在该系统中,对视频解码芯片的配置很关键。

与其它普通视频解码芯片相比,SAA7115 解码芯片内有自适应的NTSC/PAL/SECAM 制式的梳状滤波器,具有高性能图像缩放及I2C 总线Read back 技术、适用范围广,因此视频解码芯片选用SAA7115。

并对SAA7115 视频解码芯片中的一些关键寄存器进行了特殊配置,对采集的数据进行了实时显示。

结果表明,在该配置下保证了解码数据的正确性,并实现了实时传输。

关键词:视频传输;SAA7115;寄存器配置;实时传输SAA7115 是飞利浦半导体公司推出的9 位视频解码芯片。

可提供双9 位低噪音、2x 过抽样模拟到数字转换,其信噪比仅为10~15 dB,是同类产品中解码性能最高的解码芯片,主要特点有:1)6 通道模拟信号的输入,内有源选择器;2)2 个改进的9-bit COMS 模数转换器;3)可实现对CVBS、Y、C、信号的自动控制;4)加强型行、场同步检测,自动延迟矫正PAL 制式相位误差;5)TV/VCR 信号源自动检寻。

1 引脚说明SAA7115 内部框图如图1 所示。

其主要管脚及其功能如下:45 脚(ICLK):图像主时钟输出;46 脚(IDQ):图像数据限制;47 脚(ITRI):图像端口控制信号;52 脚(IGPV):多目标场基准信号;53 脚(IGPH):多目标行基准信号;54~57,59~62 脚(IPD0 一IPD7)图像数据输出端口;64~67,69~62 脚(HPD0-HPD7):主端口数据输入/输出;81~82,84~87,89~90(XPD7- XPD0):扩展端口视频输出数据。

其中模拟输入管脚由20(AI11)、18(AI12)、16(AI21)、14(AI22)、12(AI23)、10(AI24)6 个视频输入管脚的不同组合来控制,具体由SA02 寄存器的位。

TVP5150黑白转彩色异常调试TVP5150(目前已升级为TVP5150AM1)是TI生产的超低功耗、支持NTSC/PAL/SECAM 等格式的高性能视频解码器,在正常工作时,它的功耗仅115 mW,并且具有超小封装(32脚的TQFP),因此非常适用于便携、批量大、高质量和高性能的视频产品。

它可以接收2路复合视频信号(CVBS)或1路S-Video信号。

通过I2C总线设置内部寄存器,可以输出8位4:2:2的ITU-R BT.656信号(同步信号内嵌),以及8位4:2:2的ITU-R BT.601信号(同步信号分离,单独引脚输出)。

可以说TVP5150是最稳定、使用最广的一颗视频AD芯片之一,在很多产品上有广泛的应用。

但就这样一颗芯片,也不是完美无缺的。

在此和大家分享一下调试解决TVP5150 bug的经历。

我公司的主要产品是网络摄像机。

前端是CCD板机(或其它摄像机)送出模拟CVBS 信号,经TVP5150AM1变换为BT.656信号,送给后端的主控CPU实现图像的H.264压缩和网传。

有一款前端的摄像机具有低噪度转黑白功能,在光线不足时,会输出黑白图像,光线充足时,会自动输出彩色图像。

在连接这款摄像机时出现一个问题。

摄像机图像从黑白转为彩色时,后端得到的依然是黑白图像(我公司仅在这款摄像机上发现这个问题,在其它具有低噪度转黑白功能的摄像机上没有发现)。

针对这个问题,我们软件、硬件齐下手,狠狠的调了一阵子,能想到的方法全用上了。

无奈现象依旧,只能求救于TI了。

把问题现象给TI描述清楚后,TI回复的倒挺快:需要给TVP5150AM打个补丁,并把补丁包发了过来。

(TI也太可恶了,明知有这么个Bug,既不在芯片中修正,也不出文档告知大家,折磨了兄弟一个多星期)。

,这个就是TI的补丁包,下面和大家分享下补丁包的使用。

首先,确认你用的TVP5150AM1 ROM版本是v4.00 。

通过IIC 读TVP5150AM1寄存器0x82 0x83值应该是0x04 0x00;第二步,启动TVP5150AM1内部的微处理器。

omap3530+tvp5150调试小结在网上搜了不少帖,都是问怎么做怎么调才行,就没有出来分享一下调试成功的经验的,于是写下这篇小结,记录下自己的调试过程,希望对从事相关工作的朋友有所启发。

开发板是实验室自己做的,tvp5150连接到omap3530的i2c2口上,i2csel接上拉电阻,所以tvp5150的地址为0xBA。

笔者使用Mini板提供的kernel(2.6.28)和Uboot,使用mini板的配置编译后,发现无法检测到tvp5150,/dev/下只找到i2c-1和i2c-3的设备文件,直接编程打开/dev/i2c-1或/dev/i2c-3,设置从机地址为tvp5150的地址,也没有找到设备。

开始还以为是硬件有问题,用示波器检测,发现tvp5150上电后有时钟信号,27M,但数据输出都为0,查数据手册才发现,要设置0x03寄存器为0x09后,才会有数据信号输出。

后来修改board-omap3mini.c,注册i2c-2,如下://#ifdef CONFIG_I2C2_OMAP_MINIomap_register_i2c_bus(2, 400, NULL, 0);//#endif重新编译内核后,/dev/下出现i2c-2设备文件,但还是无法检测到tvp5150。

听别的工程师说,tvp5150的检测和i2c无关,主要是看数据端口有没有被检测到。

但是使用/dev/i2c-2可访问到tvp5150,可以对tvp5150的寄存器进行操作。

设置0x03寄存器为0x09后,果然有数据信号输出。

至此,笔者终于确定问题是出在瑞泰Mini-V3板提供的kernel上,估计是视频输入输出这方面没做好。

接下来笔者将尝试移植2.6.32的kernel,此kernel是从DVSDK里析出来的,多媒体驱动比较全。

附上笔者设置tvp5150的代码:#include <stdio.h>#include <stdlib.h>#include <linux/i2c-dev.h>#include <fcntl.h>#define TVP5150_SLAVE_ADDRESS 0xBA>>1#define TVP5150_MISC_CTL 0x03 /*Miscellaneous controls register address*/int main (int argc, char *argv[]){int tmp = 0, i;int file;int adapter_nr = 2;char filename[20];unsigned char tvp5150_init[2] = {TVP5150_MISC_CTL,0x09};snprintf(filename, 19, "/dev/i2c-%d", adapter_nr);file = open(filename, O_RDWR);if (file < 0) {printf("%s not found.\n",filename);exit(1);}else {printf("open %s success.\n",filename);}if (ioctl(file, I2C_SLAVE, TVP5150_SLAVE_ADDRESS) < 0) {printf("TVP5150 not found.\n");exit(1);}else {printf("set slave address = %X success.\n",TVP5150_SLAVE_ADDRESS);}if (write(file, tvp5150_init, 2) != 2) {printf("i2c write failed: address = 0x%02X\n", tvp5150_init[0]);}else {printf("set 0x%02X = 0x%02X success\n", tvp5150_init[0], tvp5150_init[1]);};//printf("TVP5150 has set to enable 8-bit ITU-R BT.656 with embedded syncs output"); close(file);}TVP5150调试心得最近有客户要求用ccd的sensor,而自己也考虑到用模拟摄像头灵活,而且现在有些模块的价格已经卖得非常便宜,昨天去华强北采购了一些样,还真不贵。

刚开始用TVP5150,寄存器的设置参照网友的设置如下:IIC_Write(TVP5150,0x00,0x00);II C_Write(TVP5150,0x03,0x09); //8-bit ITU-R BT.656 with embedded syncsIIC_ Write(TVP5150,0x07,0x40);IIC_Write(TVP5150,0x0d,0x07);数据输出和数据时钟接到驱动芯片上,主要现象:PAL制时,彩色会一闪一闪,好像是一幅有彩一幅黑白的图像,将彩色关闭,图像就不闪了,NTSC制时,图像会自动变色,红,绿,蓝的不断变化;彩色关闭,也很正常,请问对TVP5150只要上面的寄存器设置就可以吗,请有做过的朋友帮忙一下,谢谢!TVP5150的低功耗视频解码模块0 引言随着便携式多媒体终端需求量迅速增加,在视频解码等方面对芯片低功耗的要求也越来越高。

因此,只有将模拟视频信号转换成为符合ITU-R BT.656标准的数字信号,才可方便地利用FPGA或者DSP甚至PC机来进行信号处理。

本模块就是利用TI公司的超低功耗T VP5150芯片对视频信号A/D解码,由单片机通过I2C总线控制,预留地址数据等接口,作为模块验证以及后续数字信号处理之用。

1模块硬件构成1.1系统基本构成系统总体构成框图如图1所示。

TVP5150是超低功耗、支持NTSC/PAL/SECAM等格式的高性能视频解码器,在正常工作时,它的功耗仅115 mW,并且具有超小封装(32脚的TQFP),因此非常适用于便携、批量大、高质量和高性能的视频产品。

它可以接收2路复合视频信号(CVBS)或1路S-Video信号。

通过单片机I2C总线设置内部寄存器,可以输出8位4:2:2的ITU-R BT. 656信号(同步信号内嵌),以及8位4:2:2的ITU-R BT.601信号(同步信号分离,单独引脚输出)。

单片机选用TI公司的MSP430F2013,超低功耗,有2 kB+256 B Flash存储器和12 8 B RAM,14脚超小封装(TSSOP)。

关于解码芯片SAA7115及TVP5150的配置

最近因为在做视频处理,所以和解码芯片打交道很多,但因为解码芯片的datasheet很多内容(又是英文的,汗),所以根据DM642的例程总了一些应该配置的东西.

注:以下的配置均是指AV信号输入,PAL制式输出的条件

(一)关于SAA7115(基于TI的驱动)

在TI的例程里有一个结构体,里面有对7115需要配置的项目

SAA7115_ConfParams EVMDM642_vCapParamsSAA7115={

SAA7115_MODE_PAL720,

SAA7115_MODE_PAL720,

SAA7115_AFMT_COMPOSITE,

TRUE,

TRUE,

INV,/*handleI2C*/

};

这个结构体的原形在头文件saa7115.h中定义

typedef struct{

SAA7115_Mode inMode;

SAA7115_Mode outMode;

SAA7115_AnalogFormat aFmt;

Bool enableBT656Sync;

Bool enableIPortOutput;

I2C_Handle hI2C;

/*optional parameters for inMode==SAA7115_MODE_USER*/

Int hSize;

Int vSize;

Bool interlaced;

}SAA7115_ConfParams;

(1)inMode定义为视频输出格式(在saa7115.h中定义)

typedef enum SAA7115_Mode{

SAA7115_MODE_NTSC640,

SAA7115_MODE_NTSC720,

SAA7115_MODE_PAL720,

SAA7115_MODE_PAL768,

SAA7115_MODE_CIF,

SAA7115_MODE_QCIF,

SAA7115_MODE_SQCIF,

SAA7115_MODE_SIF,

SAA7115_MODE_USER

}SAA7115_Mode;

(2)outMode定义为输出视频格式,值同上

(3)aFmt定义为视频输出设备的模拟信号格式(值在saa7105.h)中定义

typedef enum SAA7115_AnalogFormat{

SAA7115_AFMT_SVIDEO,

SAA7115_AFMT_COMPOSITE

}SAA7115_AnalogFormat;

(4)enableBT656Sync定义为在输出视频数据流中允许插入ITU-R BT.656定义的SAV/EAV码

(5)enableIPortOutput:用I-PORT口代替X-PORT口输出视频流

(6)hI2C DM642的I2C控制器的句柄

当inMode=SAA7115_MODE_USER时,下面的参数可选

(7)hSize用户定义图画水平大小

(8)vSize用户自定义图画垂直大小

(9)interlaced定义用户图像是隔行扫描还是逐行扫描模式

由上面我们可以看出,一般在PAL制式采集视频时,需要配置的东西主要是:

输入输出模式、是否有同步信号、使能数据输出口

(二)关于TVP5150

在合众达提供的loop2例程中,有一个_tvp51xx.c的文件,里面包括了所有关于TVP5150寄存器的配置参数,但好像是没有用,因为根本没有调用这个文件的,而只是用下面的几条语句进行几项配置:

_IIC_write(hSeeddm642i2c,addrI2C,0x00,input_sel);

_IIC_write(hSeeddm642i2c,addrI2C,0x03,misc_ctrl);

_IIC_write(hSeeddm642i2c,addrI2C,0x0D,output_format);

_IIC_write(hSeeddm642i2c,addrI2C,0x0F,pin_cfg);

_IIC_write(hSeeddm642i2c,addrI2C,0x1B,chro_ctrl_2);

根据地址,我们可以知道是对以下寄存器进行了设置,(由于人懒了一点,直接把PDF的东西粘贴过来了)

但在我逐条的检查_tvp51xx.c中的参数,发现还有一些寄存器可能要修改,只是在例程里没有用到,这一点等我确认后才能再贴出来,今天晚上与别人讨论一下吧。