CMOS静态特性

- 格式:doc

- 大小:601.00 KB

- 文档页数:7

CMOS电路特性与参数CMOS(Complementary Metal-Oxide-Semiconductor,互补式金属氧化物半导体)是一种常见的集成电路技术。

它由一对互补的MOSFET (金属氧化物半导体场效应晶体管)构成,具有高集成度、低功耗和高噪声抑制等优点。

在本文中,我们将探讨CMOS电路的特性和参数。

一、CMOS电路的基本特性CMOS电路采用了互补的nMOS和pMOS晶体管,使得在非导通状态下电流基本为零,从而实现了极低的静态功耗。

此外,由于nMOS和pMOS晶体管的互补作用,CMOS电路还具有较高的抗噪声性能和较宽的工作电压范围。

这些特性使得CMOS电路成为了现代集成电路设计的重要选择。

二、CMOS电路的关键参数1. 高电平(High Level,或简称"High")和低电平(Low Level,或简称"Low")电压:这两个参数定义了CMOS电路中表示逻辑状态的电压范围。

通常情况下,高电平电压应接近于供电电压(VDD),低电平电压应接近于地(GND)。

2. 阈值电压:阈值电压(Threshold Voltage)是指晶体管切换电流的参考电压。

对于nMOS晶体管,阈值电压为正值;对于pMOS晶体管,阈值电压为负值。

阈值电压决定了晶体管的导通和截止的条件。

3. 驱动能力:驱动能力(Drive Capability)是指CMOS电路对外部负载的驱动能力。

它通常由晶体管的截止电压和饱和电压确定。

高驱动能力可以保证信号在电路中的传输质量和速度。

4. 功耗:CMOS电路的功耗主要包括静态功耗和动态功耗。

静态功耗是指电路在静止状态下的功耗,主要由漏电流引起;动态功耗是指电路在切换状态时的功耗,主要由充电和放电电流引起。

降低功耗是CMOS电路设计的一个重要目标。

5. 速度:CMOS电路的速度取决于晶体管的开关速度和电路中的延迟。

晶体管的开关速度主要由其驱动能力和晶体管的尺寸确定;电路中的延迟主要由线路长度、传输门的个数等因素决定。

CMOS集成电路的性能及特点1、功耗低CMOS集成电路采用场效应管,而且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。

实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。

单个门电路的功耗典型值仅为20uW,动态功耗(在1MHz工作频率时)也仅为几个mW。

2、工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

国产CC4000系列的集成电路,可在3~18V电压下正常工作。

3、逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电源低电位VSS。

当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。

因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

4、抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。

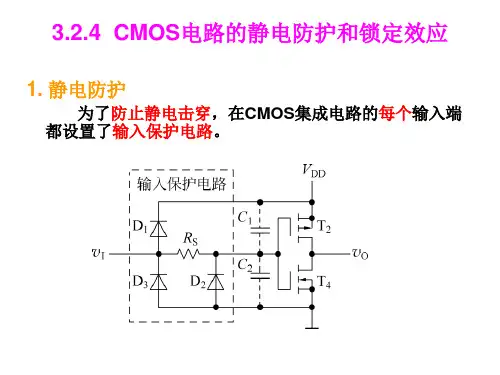

5、输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄荷电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

6、温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

一般陶瓷金属封装的电路,工作温度为-55 ~ +125℃;塑料封装的电路工作温度范围为-45 ~ +85℃。

7、扇出能力强扇出能力是用电路输出端所能带动的输入端数来表示的。

由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

CMOS反相器的静态特性z噪声容限

z反相器VTC线性近似

CMOS反相器寄生电容

CMOS 反相器的动态特性

z

减少CMOS 门传播延时的设计技术

z

电源电压V DD 对延时的影响

30.690.52

4(/)(/2)

L DD

L DD pHL

DSATn n n DSATn DD Tn DSATn C V C V t I W L k V V V V ==′−−0.52

(/)L

pHL

n n

DSATn C t W L k V =′/2

DD Tn DSATn V V V − 如果忽略沟道调制系数λ

CMOS 反相器的动态特性

z

反相器链的尺寸优化

z

反相器的输入电容C g 与本征输出电容之间的关系

z 反相器链

g

C C γ=000111g ext p p p p g g fC C f t t t t C C γγγ⎛⎞

⎛⎞⎛⎞=+=+=+⎜⎟⎜⎟⎜⎟⎜⎟⎜⎟⎝⎠⎝⎠⎝

⎠

,1,00,11g j j p j

p p g j C f t t t C γγ+⎛⎞⎛

⎞=+=+⎜⎟⎜⎟⎜⎟⎝⎠⎝

⎠ext g

C fC =

4,opt

N f F f >=<t opt /t p0与F 的关系

延时

z为减少能耗的尺寸优化

z改变器件尺寸并降低电源电压时减小逻辑电路能好的有效办法z在最优值之外过多加大晶体管尺寸会消耗更多能量

I t I t

小电容负载。

CMOS电路主要特性的教学与研究作者:何金儿蔡京玫来源:《电子世界》2012年第15期【摘要】对CMOS数字电路静态和动态中的的几个关键的重要特性进行了探讨,并对因CMOS数字电路内部结构而引发的闩锁效应进行了分析。

给出了CMOS数字电路的使用方法及注意事项。

【关键词】基本结构;静态特性;动态特性;功耗计算;闩锁效应;CMOS集成电路特性;闩锁效应动态功耗1.引言CMOS数字集成电路是目前大规模和超大规模数字集成电路中广泛应用的一种电路结构,与NMOS和PMOS数字电路相比较,CMOS数字电路在功耗、噪声抑制、抗干扰能力等方面具有明显的优势。

并且由于CMOS数字电路的集成度可以做的非常高,在总体性能上已经超出了TTL电路,因此得到了迅速而广泛地运用。

目前CMOS电路占据了99%的市场份额。

特别是CMOS电路的制造工艺已经达到了深亚微米范围后,器件特性的变化带来了一系列需要重视的问题。

但是在高校传统的数字电路课程的教材中,对TTL电路的原理和特性讲述的比较详细,对CMOS电路的原理和特性却介绍过于简单。

特别是对CMOS电路的关键的几个电气特性讲述的更少。

因此揭示CMOS数字电路的构成,研究CMOS电路电气特性以及CMOS 电路在设计数字系统中一些注意事项,是数字电路课程的教学和正确设计数字系统的一个需要引起注意的环节。

2.反相器的静态特性在CMOS数字电路中,反相器是所有数字电路设计的核心。

几乎所有的CMOS电路的电气特性都可以从反相器得到的结果中推断出来。

Nmos管的开关特性如图1a所示,UT是Nmos管的开启电压,当电压│UGS│≥│UT│时,Nmos管呈现出导通的状态,导通电阻的阻值与UGS的大小呈非线性变化,如图1a所示,输出电阻的典型值在Kῼ范围内。

当电压│UGS│≤│UT│时Nmos管呈现出截止的状态,其电阻非常大。

在Pmos管的开关特性中如图1b所示,PMOS管和NMOS管成对偶性在CMOS电路中,推荐的逻辑高电平为VDD,低电平为VSS。

分类号TP309 学号GS******** U D C 密级公开工程硕士学位论文基于LBDL逻辑的抗DPA攻击安全芯片的设计与实现硕士生姓名夏璐工程领域集成电路工程研究方向微电子技术指导教师李少青研究员国防科学技术大学研究生院二〇一二年三月基于LBDL 逻辑的抗DPA 攻击安全芯片的设计与实现国防科学技术大学研究生院Design and Implementation ofDPA-Resistant Chip Based on LBDL LogicCandidate:Xia LuAdvisor:Prof. Li ShaoqingA dissertationSubmitted in partial fulfillment of the requirements for the degree of Master of Engineeringin Integrated Circuit EngineeringGraduate School of National University of Defense Technology Changsha,Hunan,P.R.ChinaMarch,2012目录摘要 (i)ABSTRACT ......................................................................................................... i i 第一章绪论 (1)1.1 研究背景 (1)1.2 国内外研究现状 (2)1.3 研究内容 (3)1.4 论文结构 (4)第二章功耗分析攻击及DPA防护技术 (6)2.1 旁路攻击 (6)2.2 功耗分析攻击 (8)2.2.1 静态互补CMOS电路的工作特性 (9)2.2.2 提前传播效应 (11)2.2.3 功耗分析攻击的种类 (12)2.3 DPA防护技术 (13)2.3.1 DPA防护技术概论 (13)2.3.2 掩码(Masking)技术 (14)2.3.3 解相关(Decorrelation)技术 (14)2.4 本章小结 (15)第三章基于动态差分逻辑的芯片设计流程 (16)3.1 动态差分逻辑 (16)3.1.1 SABL (17)3.1.2 WDDL (18)3.1.3 LBDL (20)3.1.4 三种动态差分逻辑对比 (21)3.2 差分布线方法 (24)3.2.1 差分布线方法 (24)3.2.2 三种差分布线方法对比 (26)3.2.3 差分布线流程设计 (26)3.3 支持差分布线的半定制设计流程 (27)3.4.1 数字集成电路设计方法 (28)3.4.2 总体流程设计思路 (29)3.4.1 逻辑单元信号跳变分析 (30)3.4.2 总体时序分析思路 (31)3.4 本章小结 (32)第四章抗DPA攻击DES算法芯片设计与实现 (33)4.1 DES算法概述 (33)4.1.1 DES算法 (33)4.1.2 针对DES算法的DPA攻击方法 (36)4.2 支持差分布线的抗DPA攻击芯片半定制设计 (37)4.2.1 具体设计流程 (37)4.2.2 部分Perl脚本代码 (39)4.3 支持差分布线的抗DPA攻击芯片时序分析 (40)4.3.1 逻辑单元延迟信息分析 (40)4.3.2 延迟信息替换 (41)4.4 芯片实现 (42)4.5 本章小结 (42)第五章实现结果分析验证 (44)5.1 差分布线结果验证 (44)5.2 时序分析 (45)5.3 抗DPA攻击性能分析 (46)5.3.1 基于普通静态逻辑的DES芯片实现 (46)5.3.2 实验数据分析对比 (47)5.4 本章小结 (49)第六章结束语 (50)6.1 工作总结 (50)6.2 研究展望 (51)致谢 (52)参考文献 (54)作者在学期间取得的学术成果 (58)附录A 部分Perl脚本代码 (59)表目录表2.1 静态互补CMOS逻辑反相器的功耗行为 (10)表2.2 受提前传播效应影响的路径延迟情况 (11)表3.1 三种动态差分逻辑对比 (23)表3.2 三种差分布线方法对比 (26)表3.3 静态CMOS逻辑与动态差分逻辑信号关系 (31)表3.4 静态CMOS逻辑与动态差分逻辑信号跳变关系 (31)表4.1 静态标准逻辑单元与动态差分逻辑单元信号跳变关系 (40)表4.2 AND单元由输入导致输出跳变的延迟信息关系 (41)表4.3 负跳变逻辑替换策略 (41)表5.1 SPICE模拟与PrimeTime所得延迟路径结果比较 (45)表5.2 普通静态逻辑的DES芯片延迟路径结果 (46)表5.3 两种不同逻辑DES芯片性能参数对比 (47)表5.4 两种不同逻辑DES芯片的抗DPA攻击性能 (48)图目录图2.1 旁路攻击外部模型 (7)图2.2 旁路攻击内部模型 (7)图2.3 静态互补CMOS逻辑结构 (9)图2.4 静态互补CMOS逻辑反相器结构 (9)图2.5 输入信号存在路径延迟差异的模型电路 (11)图3.1 n输入SABL逻辑门结构图 (17)图3.2 WDDL逻辑单元 (18)图3.3 WDDL行波预充思想的电路实例 (19)图3.4 2输入AND LBDL单元 (20)图3.5 LBDL单元的CELL (21)图3.6 SABL-NOR实例 (22)图3.7 WDDL-NOR实例 (22)图3.8 LBDL-NOR实例 (22)图3.9 双轨信号平行布线原理 (26)图3.10 基于双轨信号平行布线的差分布线流程 (27)图3.11 典型的半定制设计流程 (28)图3.12 支持差分布线的半定制设计流程总体思路 (29)图4.1 DES加密算法整体流程 (34)图4.2 DES的轮函数F (35)图4.3 支持差分布线的半定制实现具体设计流程 (38)图4.4 基于LBDL逻辑的DES芯片版图 (42)图5.1 差分布线结果电路局部视图对比 (45)图5.2 基于普通静态逻辑的DES芯片版图 (46)图5.3 两种不同逻辑芯片动态电流曲线 (48)摘要随着信息化的高速发展,安全芯片在人们的生活中得到了越来越广泛的应用。

数字集成电路学习总结5CMOS反相器今天开始总结数字集成电路。

这本书其实算是本科最难的⼀本了,细节过多⽆法卒读,涉及到的知识也⾮常全⾯。

实际上本科课程安排中并为将其作为重点,我们的课⾮常⽔,不知道讲了什么。

今天详细总结⼀下。

当时然由于内容过多,⽆法全部涵盖,只能⼤致总结,并着重记录定性的结论。

涉及到计算之类的问题,就只能略过了。

第五章 COMS反相器5.1 引⾔为什么从第五章开始,原因是这章⽐较基础,详细学习CMOS反相器后,才能继续看组合电路和时序电路等等。

研究的对象有如下⼏个指标:成本(复杂性和⾯积)、完整性和稳定性(静态特性)、性能(动态特性)、能量效率(功耗)。

5.2 静态CMOS反相器——直观综述课本上的描述:晶体管只不过是⼀个具有⽆限关断电阻和有限导通电阻的开关。

以开关来理解,可以推导出其他重要特性:1、输出⾼电平和低电平分别为VDD和GND,换⾔之,电压摆幅等于电源电压。

因此噪声容限很⼤。

2、逻辑电平与器件的相对尺⼨⽆关,所以晶体管可以采⽤最⼩尺⼨。

这⾥有⼀个概念叫⽆⽐逻辑3、稳态时,输出和VDD或GND之间总存在有限电阻的通路。

因此⼀个设计良好的CMOS反相器具有低输出阻抗,这使得它对噪声和⼲扰不敏感。

4、输⼊电阻极⾼。

理论上,单个反相器可以驱动⽆穷个门,或者说有⽆穷⼤的扇出。

但很快我们发现增加扇出也会增加传播延时。

因此扇出不会影响稳态特性,会影响瞬态特性。

5、忽略漏电流的话,意味着⽆静态功耗。

之前常⽤的是NMOS电路,静态功耗不为0,限制了集成度。

后来必须转向CMOS。

电压传输特性(VTC)的性质和形状可以通过图解法迭加两管的图像得到。

结果是观察到VTC具有⾮常窄的过渡区。

我们可以把开关特性简化为RC电路,⼀个快速门的设计是通过减⼩输出电容或者减⼩晶体管的导通电阻(增⼤宽长⽐)实现的。

5.3 CMOS反相器稳定性的评估——静态特性5.3.1 开关阈值开关阈值VM定义是Vin=Vout的点,利⽤图解法可以看出。

MOS器件的静态分析

院系:电子工程学院

专业班级:集电0903

姓名:郑燕燕

学号:04096096(26)

日期:2012年5月7日

摘要 (2)

一、实验目的 (4)

二、实验内容 (4)

三、实验过程 (4)

3.1 NMOS器件原理图设计 (4)

3.2 CMOS器件的静态分析与模拟 (5)

3.3 MOS器件的输出结果显示 (6)

四、实验小结 (6)

摘要

一、实验目的

1、熟悉并掌握Tanner Pro仿真工具的使用,能够进行较简单

的器件仿真。

2、分析MOS器件的工作原理并进行单个MOS器件的静态分析。

二、实验内容

熟悉了Tanner Pro软件的使用方法后,在S_Edit中画出单个CMOS器件(NMOS或PMOS),然后在T-Spice中生成对应的网表并对输入及输出进行处理,最终获得其静态特性曲线再加以分析。

三、实验过程

3.1 NMOS器件原理图设计

CMOS器件是一个四端器件,夹在栅端的电压决定了源端与漏端之间有多少电路流过。

从最浅显的观点看,可以把MOS器件看成是一个开关。

当栅压大于阈值电压时,在漏端和源端之间就形成了一导电沟道。

当漏端和源端之间存在电压差时,电流就会在它们之间流动。

其电路图如下:

其原理图编辑如下:

3.2 CMOS器件的静态分析与模拟

在S_Edit中只需画出待测MOS器件即可,然后在T_Spice 中生成对应的网表,这时,一些待测量的值的设定十分重要。

主要包括:栅源电压Vgs的线性变化以及漏源电压Vds的线性变换。

由于CMOS静态分析主要是观察器件电流随电压值的变化曲线,所以,需对器件电流进行波形的仿真。

仿真程序如下:

3.3 MOS器件的输出结果显示

横坐标为Vds,横坐标为器件电流Ids:

四、实验小结。