《数字逻辑电路》复习资料

- 格式:doc

- 大小:1.80 MB

- 文档页数:23

《数字逻辑》复习题一选择题1.逻辑表达式Y=AB可以用 ( C ) 实现。

A.正或门B.正非门C.正与门D.负或门2.在( A )的情况下,“或非”运算的结果是逻辑 1 。

A.全部输入是0 B.全部输入是1C.任一输入为0,其他输入为1D.任一输入为13.CMOS数字集成电路与TTL数字集成电路相比突出的优点是( A )。

A. 微功耗B. 高速度C. 高抗干扰能力D. 电源范围宽4.在下列逻辑电路中,不是组合逻辑电路的有( D )。

A. 译码器B. 编码器C. 全加器D. 寄存器5.一块数据选择器有三个地址输入端,则它的数据输出端最多应有( D )。

A.3B.6C.7D.86.组合逻辑电路的特点是( B )。

A. 输出与以前输入有关B. 输出只由当时输入决定C. 输出与原来输出有关D. 输出由当时和以前输入共同决定7.若在编码器中有90个编码对象,则要求输出二进制代码位数为( C )位。

A.5B.6C.7D.88.数据选择器,某瞬间在选择变量作用下,从多路信号中选出( C )。

A.2路B.全部C.1路D. 4路9.八路数据分配器,其地址输入端有( C )个。

A.1B.2C.3D.4E.810.同步计数器和异步计数器比较,同步计数器的显著优点是( A )。

A.工作速度高 B.触发器利用率高 C.电路简单 D.不受时钟CP控制11.8 位移位寄存器,串行输入时经( D )个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.812.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容( D )。

A.全部改变B.全部为0C.不可预料D.保持不变13.基本的逻辑运算是( C )。

A. 异或B. 与非C. 与、或、非D. 或非14.格雷码的特点是位置相邻的数码中只有( A )。

A. 一位不同B. 二位不同C. 高位相同,其他全不同D. 各位全不同15.函数F= <!--[if !vml]--><!--[endif]-->的反函数是( A )。

_、单选题1、十进制整数转换为二进制数一般采用()。

A.除2取整法B.除10取余法C.除2取余法D.除10取整法正确答案:C2、将十进制小数转换为二进制数一般采用()。

A.乘2取整法B.乘10取余法C.乘2取余法D.乘10取整法正确答案:A3、十进制数"13",用三进制表示为()。

A.211B.111C.112D.101正确答案:B4、将十进制数18转换成八进制是().A.20B.24C.22D.21正确答案:C5、十进制数25用8421 BCD码表示为()A.10 010100B.0010 0101C.10 101D.10 000101正确答案:B6、以下代码中为恒权码的是()。

A.余3循坏码B右移码C.5211 码D.余3码正确答案:C7、T立八进制数可以用()位二进制数来表示。

A.4B.3C.1D.2正确答案:B&十进制数43用8421BCD码表示为()。

A.10011B.0100 0011C.101011D.1000011正确答案:B9、A+BC=()A.AB+ACB.BCC・(A+B)(A+C)正确答案:C10、4变量逻辑函数的真值表,表中的输入变量的取值应有()种。

A.4B.2C.16D.8正确答案:C11、f 16选1的数据选择器,其选择控制(地址)输入端有()个,数据输入端有16个,输出端有1个。

A.4B.16C.1D.2正确答案:A12、一个译码器若有100个译码输出端,则译码输入端至少有()个。

A.5B.8C.7D.6正确答案:C13、能实现并-串转换的是()。

A.数据选择器B.数据分配器C.译码器D.数值比较器正确答案:A14、欲设计一个3位无符号数乘法器(即3x3),需要6位输入及()位输出信号。

B.6C.4D.5正确答案:B15、4位输入的二逬制译码器,其输出应有()位。

A.4B.1C.8D.16正确答案:D16、对于8线一3线优先编码器,下面说法正确的是()A.有8根输入线,8根输出线B.有8根输入线,3根输出线C.有3根输入线,8根输出线D.有3根输入线,3根输出线正确答案:B17、3线-8线译码电路是()译码器A.八进制B.三进制C.三位二进制D.H-A进制正确答案:C18、实现多输入、单输出逻辑函数,应选()。

《数字逻辑电路》在线作业参考资料一、单选题1. 一位8421BCD计数器,至少需要(B)个触发器A 3B 4C 5D 102. 在(A)的情况下,函数运算的结果是逻辑“1”A全部输入是“0” B任一输入是“0” C任一输入是“1” D全部输入是“1”3. 表示两个相邻脉冲重复出现的时间间隔的参数叫(A )A.脉冲周期B.脉冲宽度C.脉冲前沿D.脉冲后沿4. 只能读出不能写入,但信息可永久保存的存储器是(A)A.ROMB.RAMC.RPROMD.PROM5. 在(D)的情况下,函数Y=AB运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”6. 下列哪些信号一定不属于数字信号(A)A.正弦波信号B.时钟脉冲信号C.音频信号D.视频图像信号7. 在(B)的情况下,函数Y=/(AB)运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”8. 符合六变量m5的相邻最小项,有下列(C )说法成立A. 共有5 个相邻最小项B. m0、m4、m7、m13是它的相邻项C. 共有6 个相邻最小项D. m4、m21、m13、m38是它的相邻项9. 下列器件中,属于时序部件的是(A)A.计数器B.译码器C.加法器D.多路选择器10. 在n变量的逻辑函数F中,有(C )A. 若mi为1,则Mi也为1B. 若F所有mi为0,则F为1C. 若F所有Mi为1,则F为1D. F的任一最小项标记为mni( i = 1~2n )11. 半加器的逻辑功能是(A)A. 两个同位的二进制数相加B. 两个二进制数相加C. 两个同位的二进制数及来自低位的进位三者相加D. 两个二进制数的和的一半12. 1路—4路数据分配器有(A)A.一个数据输入端,两个选择控制端,四个数据输出端B.四个数据输入端,两个选择控制端,一个数据输出端C.一个数据输入端,一个选择控制端,四个数据输出端D.四个数据输入端,一个选择控制端,一个数据输出端13. 全部的最小项之和恒为(B)A.0B.1C.0或1D.非0非114. 对于四变量逻辑函数,最小项有(D)个A.0B.1C.4D.1615. 逻辑表达式A+BC=( C )A. ABB. A+CC. (A+B)(A+C)D. B+C16.在(A)的情况下,函数运算的结果不是逻辑“1”A全部输入是“0” B 任一输入是“0”C任一输入是“1” D全部输入是“1”17. 十进制数25用8421BCD码表示为(B )。

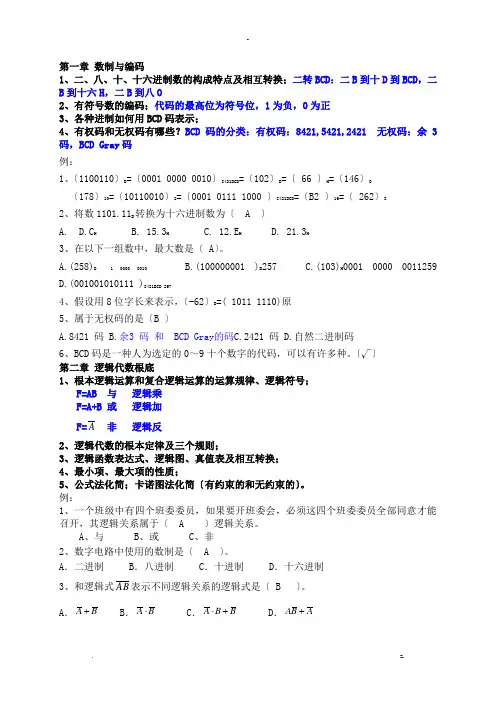

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

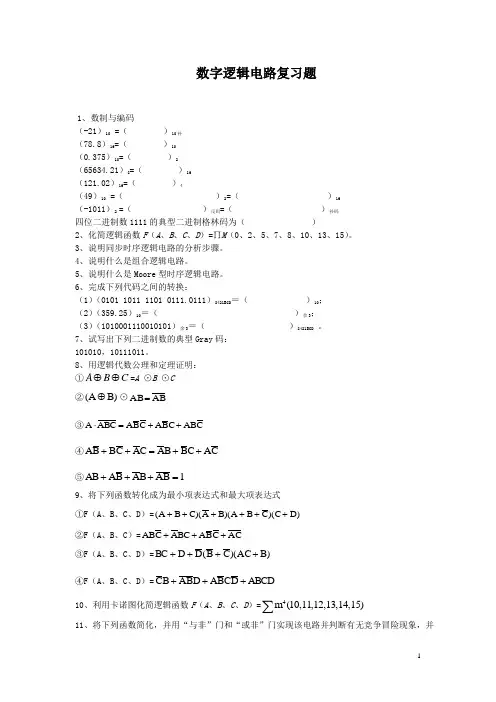

数字逻辑电路复习题1、数制与编码(-21)10 =( )10补(78.8)16=( )10(0.375)10=( )2(65634.21)8=( )16(121.02)16=( )4(49)10 =( )2=( )16(-1011)2 =( )反码=( )补码四位二进制数1111的典型二进制格林码为( )2、化简逻辑函数F (A 、B 、C 、D )=∏M (0、2、5、7、8、10、13、15)。

3、说明同步时序逻辑电路的分析步骤。

4、说明什么是组合逻辑电路。

5、说明什么是Moore 型时序逻辑电路。

6、完成下列代码之间的转换:(1)(0101 1011 1101 0111.0111)8421BCD =( )10;(2)(359.25)10=( )余3;(3)(1010001110010101)余3=( )8421BCD 。

7、试写出下列二进制数的典型Gray 码:101010,10111011。

8、用逻辑代数公理和定理证明:①C B A ⊕⊕=A ⊙B ⊙C②)B A (⊕⊙B A AB = ③C AB C B A C B A ABC A ++=⋅ ④C A C B B A C A C B B A ++=++ ⑤1B A B A B A AB =+++9、将下列函数转化成为最小项表达式和最大项表达式①F (A 、B 、C 、D )=)D C )(C B A )(B A )(C B A (++++++②F (A 、B 、C )=C A C B A BC A C AB +++③F (A 、B 、C 、D )=)B AC )(C B (D D BC ++++④F (A 、B 、C 、D )=ABCD D C B A D B A B C +++10、利用卡诺图化简逻辑函数F (A 、B 、C 、D )=4m (10,11,12,13,14,15)∑ 11、将下列函数简化,并用“与非”门和“或非”门实现该电路并判断有无竞争冒险现象,并予以消除。

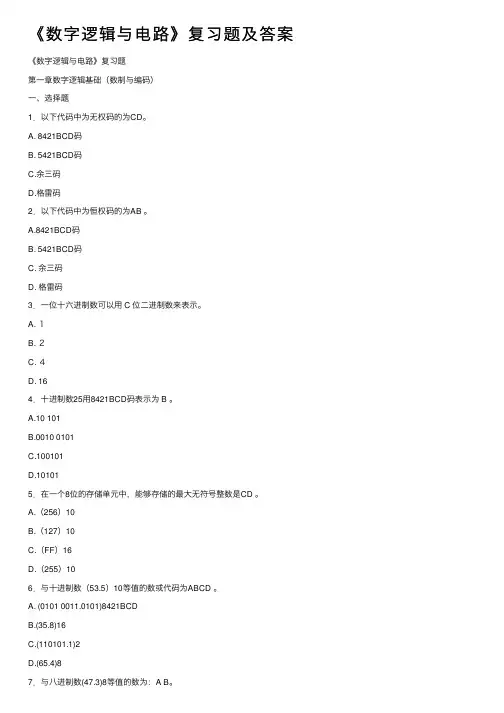

《数字逻辑与电路》复习题及答案《数字逻辑与电路》复习题第⼀章数字逻辑基础(数制与编码)⼀、选择题1.以下代码中为⽆权码的为CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.⼀位⼗六进制数可以⽤ C 位⼆进制数来表⽰。

A. 1B. 2C. 4D. 164.⼗进制数25⽤8421BCD码表⽰为 B 。

A.10 101B.0010 0101C.100101D.101015.在⼀个8位的存储单元中,能够存储的最⼤⽆符号整数是CD 。

A.(256)10B.(127)10C.(FF)16D.(255)106.与⼗进制数(53.5)10等值的数或代码为ABCD 。

A. (0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与⼋进制数(47.3)8等值的数为:A B。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常⽤的B C D码有C D。

A.奇偶校验码B.格雷码C.8421码D.余三码⼆、判断题(正确打√,错误的打×)1. ⽅波的占空⽐为0.5。

(√)2. 8421码1001⽐0001⼤。

(×)3. 数字电路中⽤“1”和“0”分别表⽰两种状态,⼆者⽆⼤⼩之分。

(√)4.格雷码具有任何相邻码只有⼀位码元不同的特性。

(√)5.⼋进制数(17)8⽐⼗进制数(17)10⼩。

(√)6.当传送⼗进制数5时,在8421奇校验码的校验位上值应为1。

(√)7.⼗进制数(9)10⽐⼗六进制数(9)16⼩。

(×)8.当8421奇校验码在传送⼗进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

(√)三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其⾼电平和低电平常⽤1和0来表⽰。

1.连续异或1985个1的结果是( B )A,0 B,1C,不确定D,逻辑概念错误2.在二进制逻辑运算中,1+1=(A)A, 0; B,1C,2 D,103.连续异或1986个1的结果是(A)A,0 B,1C,不确定D,逻辑概念错误4.给48个字符编码,至少需要( B )位二进制数;A,5; B,6C,7 D,85.符合逻辑“或”运算规则的是( D )。

A、1×1=1B、1+0=0C、1+1=10D、1+1=16.逻辑函数F=AB +A经过化简所得的结果是( A)。

A、AB、BC、CD、AB7.下列哪种逻辑表达式化简结果是错误的( C )A, A+1=1; B,AA=A;C,A+0=0 D;A+AB=A8.三位二进制编码器,其输入端共有( A)位;A,3;B,4;C,8;D,16 9.下列各门电路中,哪个电路输出端可以直接相连,实现线与功能。

( B )A,TTL与非门;B,TTL集电极开路门;C,CMOS与非门;D,TTL传输门10.组合逻辑电路的特点是输出状态只决定于同一时刻的( B )状态。

A、输出B、输入C、输入与输出D、前三者都不对11.十进制数6用8421BCD码表示为:( B )A,110; B,0110;C,0111;D;11;12.下列选项中,哪个是变量A,B,C,D的最小项( B )A,A+B+C+D; B,ABCD;C,ABC;D;A+B+C;13.十进制数5用8421BCD码表示为:( B )A,101; B,0101;C,1010;D;011;14.一个三输入端与非门,使其输出为0的输入端的组合有( C )种。

A,7; B,8;C,1 D;4=+=(A)15.逻辑函数F A ABC+;D, A+C;A, A+BC; B,A;C,A C16.下列哪种逻辑表达式化简结果是错误的( C )A, A+1=1; B,AA=A;C,A+0=0 D;A+AB=A17.下列选项中,哪个是变量A,B,C的最小项( C )A,A+B+C+D; B,ABCD;C,ABC;D;A+B+C;18. 逻辑函数F A A C =+=( A )A,A+C; B ,A ; C ,A C +; D, C ;19. 一个三输入端或非门,使其输出为1的输入端的组合有( C )种。

1 / 22 单选题(3分)正确答案C我的答案C单选2、将二进制、八进制和十六进制数转换为十进制数的共同规则是( )。

A除n取余Bn位转1位C按权展开D乘n取整2 / 22 单选题(3分)正确答案B我的答案B根据最小项与最大项的性质,任意两个不同的最小项之积为0 ,任意两个不同的最大项之和为。

B1.0C2.0D不确定3 / 22 单选题(3分)正确答案D我的答案D我们可以用逻辑函数来表示逻辑关系,任何一个逻辑关系都可以表示为逻辑函数的与或表达式,也可表示为逻辑函数的表达式。

A与B或C与或非D或与4 / 22 单选题(3分)正确答案C我的答案CABCD5 / 22 单选题(3分)正确答案C我的答案C单选36、若4位同步二进制加法计数器当前的状态是0111,下一个输入时钟脉冲后,其内容变为()。

A0111B0110C1000D00116 / 22 单选题(3分)正确答案B我的答案BABCD7 / 22 单选题(3分)正确答案B我的答案B、当现态时,具 J=1,K=0时,时钟动作后的 J - K 触发器次态应为()。

A置0B置1C保持D不确定8 / 22 单选题(3分)正确答案C我的答案CABABCA+BDB9 / 22 单选题(3分)正确答案C我的答案C单选18 、能够存储0 、 1 二进制信息的器件是()。

ATTL门BCMOS门C触发器D译码器10 / 22 单选题(3分)正确答案D我的答案D单选31 、用n级触发器组成计数器,其最大计数模是()。

AnB2nCn2D2n11 / 22 多选题(4分)正确答案CD我的答案CD多选3 、计算机中的所有信息均以二进制形式表示,但有时为了书写与阅读的方便,也使用()表示。

A四进制B六进制C八进制D十六进制12 / 22 多选题(4分)正确答案ACD我的答案ACD多选13 、求一个逻辑函数F的对偶式,可将F中的()。

A“·”换成“+”,“+”换成“·”B原变量换成反变量,反变量换成原变量C变量不变D常数中“0”换成“1”,“1”换成“0”13 / 22 多选题(4分)正确答案BD我的答案BD下列乘积项中,()是四变量ABCD函数的最小项。

数字逻辑复习题《数字逻辑》复习资料⼀.选择题:1.下列数码均代表⼗进制数6,其中按余3码编码的是()。

A)0110 B)1100 C)1001 D)01012.已知逻辑函数Y=AB+A?B+?A?B,则Y的最简与或表达式为()。

A)A B)A+?A?B C)A+?B D)A+B3.对于J-K触发器,若J=K,则可完成()触发器的逻辑功能。

A)R-S B)D C)T;D)J-K4.下列四个数中,最⼤的数是()。

A)(AF)16 B)(001010000010)8421BCDC)(10100000)2 D)(198)105.逻辑变量的取值1和0可以表⽰()。

A)开关的闭合、断开B)电位的⾼、低C)真与假D)电流的有、⽆6.在何种输⼊情况下,“或⾮”运算的结果是逻辑0。

()A)全部输⼊是0 B)全部输⼊是1C)任⼀输⼊为0,其他输⼊为1 D)任⼀输⼊为17.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输⼊T=()。

A)0 B)1 C)Q D)不确定8.下列触发器中,克服了空翻现象的有()。

A)边沿D触发器B)]主从RS触发器;C)同步RS触发器D)主从JK触发器;9.卡诺图上变量的取值顺序是采⽤()的形式,以便能够⽤⼏何上的相邻关系表⽰逻辑上的相邻。

A)⼆进制码B)循环码C)ASCII码D)⼗进制码10.表⽰任意两位⽆符号⼗进制数需要()⼆进制数。

A)6 B)7 C)8 D)911.余3码10001000对应的2421码为()。

A)01010101 B)10000101 C)10111011 D)1110101112.补码1.1000的真值是()。

A)+1.0111 B)-1.0111 C)-0.1001 D)-0. 100013.标准或-与式是由()构成的逻辑表达式。

A)与项相或B)最⼩项相或C)最⼤项相与D)或项相与14.下列四种类型的逻辑门中,可以⽤()实现三种基本运算。

A)与门B)或门C)⾮门D)与⾮门15.实现两个四位⼆进制数相乘的组合电路,应有()个输出函数。

数字逻辑课程知识点第一章数字逻辑概论1.计算机中常见的几种数制及其转换方法(十进制、二进制、十六进制)2.有符号数的补码表示方法(要求会求符号数的补码或从补码求实际的有符号数)3.掌握ASCII码概念。

知道常用字符(空格、数字0-9和字母A – Z,a- z等)的ASCII 码。

4.掌握8421BCD码的概念,会用BCD码表示十进制数5.掌握基本逻辑运算(“与”、“或”、“非”、“与非”、“或非”、“异或”以及“同或”等运算)及其逻辑符号。

6.掌握逻辑函数的5种表示方法(真值表表示法、逻辑表达式表示法、逻辑图表示法、波形图表示法、卡诺图表示法)第二章逻辑代数1.逻辑代数的基本定律和恒等式(摩根定理)2.逻辑代数的基本规则(代入规则、反演规则、对偶规则)3.把“与---或”表达式变换为“与非---与非”和“或非---或非”表达式的方法4.逻辑函数的代数化简方法:并项法(A+/A=1)吸收法(A+AB=A)消去法(A+/AB=A+B)配项法(A=A*(B+/B))5.卡诺图的特点:每个小方格都惟一对应于一个不同的变量组合(一个最小项),而且,上、下、左、右在几何上相邻的方格内只有一个因子有差别。

任何一个函数都等于其卡诺图中为1的方格所对应的最小项之和。

6.掌握用卡诺图化简逻辑函数的方法7.理解无关项的概念:即实际应用中,在真值表内对应于变量的某些取值,函数的值是可以任意的,或者这些变量的取值根本不会出现,这些变量取值对应的最小项即称为无关项或任意项,每个无关项的值既可以取0,也可以取1,具体的取值以得到最简的函数表达式为准。

第三章MOS逻辑门电路1.数字集成电路的分类:从集成度方面分:小规模(SSI)、中规模(MSI)、大规模(LSI)、超大规模(VLSI)和甚大规模(ULSI)。

从制造工艺方面分:CMOS、TTL、ECL以及BiCMOS等2.CMOS的特点:(功耗低、抗干扰能力强、电源范围宽)3.理解集成电路各种参数的意义:(1)V IL(max)、V IH(min)、V OH(min)、V OL(max)、I IH(max)、I IL(max)、I OH(max)、I OL(max)(2)高电平噪声容限期VNH = V OH(min) —V IH(min)(3)低电平噪声容限期VNL = V IL(max)—V OL(max)(4)传输延迟时间t PLH、t pHL以及tpd = (t PLH + t pHL)/2(5)功耗(动态功耗和静态功耗)。

1、正逻辑体系中,用表示周电平,用表示低电平。

2.在逻辑电路中,用0来表示高电平,用1来表示低电平,称为体制。

3.作为数据分配使用的译码器必须具有,且该端要作为使用,而译码器的输入端要作为分配器的,译码器的输出端就是分配器的。

4.将247转换为二进制数为o5、86的8421BCD码为。

余3码为。

若1101是2421BCD码的一组代码,则它对应的十进制数是-十进制数(165) io转换成8421 BCD码是。

6、(11.25)何的二进制数为,十六进制数为o7、写出Y=AB+CD的反函数,对偶函数o8、三态输出门(TS门)的输出有三种可能的状态,分别是高电平、、o9、触发器的特性方程为o对于触发器,若J = K ,则可完成触发器的逻辑功能;若J = K,则可完成——触发器的逻辑功能10、一个五位的二进制加法计数器,由00000状态开始,经过75个计数脉冲,此计数器的状态为=11、为构成1024X8位的RAM,需要片256X4位的RAM,并且需要位地址译码器完成寻址操作。

12、一个8位D/A转换器的最小输出电压增量为0. 02V,当输入代码为01001101时,输出电压V。

为13、某台计算机的内存储器设置有32位地址线,16位并行数据输入/输出端,这台计算机的最大存储容量是o14、n位触发器构成的环形计数器,也是一个分频电路。

15.T触发器的特征方程是。

16.一个三位扭环形计数器的模为o17.由555定时器构成的施密特触发器,设V CC=12V,外接控制端未接电压,则其回差AV=。

18.( 35.4)s =()2 =()10=)16=()8421 BCD19.逻辑代数的三个重要规则是、、o20.数字电路按照是否有记忆功能通常可分为两类:、21.集电极开路门的英文缩写为门,工作时必须外加和o22.随机存取存储器具有功能。

23 .常见的脉冲产生电路有,常见的脉冲整形电路有、=24.五个D触发器构成环形计数器,其计数长度为-25.N个触发器可以构成最大计数长度(进制数)为的计数器。

数字逻辑电路-题库1、当决定一件事情的所有条件全部具备时,这件事情才发生,这样的逻辑关系称为非。

答案:错误2、逻辑变量取值的0和1表示事物相互独立而又联系的两个方面。

答案:正确3、在变量A、B取值相异时,其逻辑函数值为1,相同时为0,称为异或运算。

答案:正确解析:异或:不同为1,相同为04、最基本的三种逻辑运算是________、________、________。

答案:与;或;非;5、答案: B6、有三个输入端的或非门电路,要求输出高电平,其输入端应是。

A、全为高电平B、至少一个端为低电平C、全为低电平D、至少一个端为高电平答案: C7、十进制数(42)10对应的十六进制数为。

答案:2A;8、在下列逻辑运算中,错误的是:。

A、若A+B=B+C,则A=CB、若1+A=B,则1+A+AB=BC、若A=B,则AB=AD、若A=C,则AB=BC答案: A9、若两个函数相等,则它们的真值表一定相同;反之,若两个函数的真值表完全相同,则这两个函数未必相等。

答案:错误10、逻辑函数两次求反后可以还原,而逻辑函数的对偶式再作对偶变换也可以还原为它本身。

答案:正确11、若逻辑函数AB=AC,则B=C答案:错误解析:若A等于0,AB=AC,B可以不等于C12、若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等答案:错误解析:不同的逻辑函数式可以相等。

13、逻辑表达式A+BC= ()A、 ABB、 A+CC、 (A+B)(A+C)D、 B+C答案: C14、。

A、B、C、D、答案: A15、逻辑函数F=AB+CD的对偶式=__ ____,反函数=____ ____。

答案:(A+B)(C+D),16、n个变量的逻辑函数,其全部最小项共有n个。

答案:错误解析:共有2的N次方个17、在逻辑函数表达式中,如果一个乘积项包含的输入变量最少,那么该乘积项叫做最小项。

答案:错误解析:所谓最小项,必须包含所有逻辑函数,函数必须以原变量或者反变量的形式出现,且只出现一次。

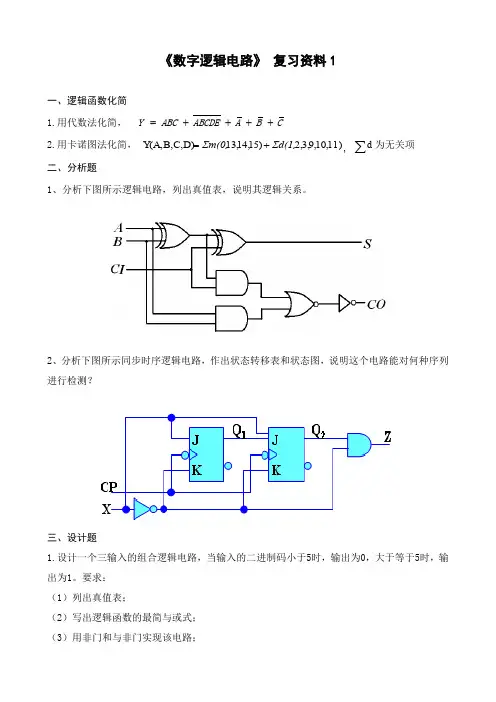

成考复习资料《数字逻辑电路》 复习资料1一、逻辑函数化简1.用代数法化简, C B A ABCDE ABC Y ++++=2.用卡诺图法化简, ),,Σd(1,5)4,,Σm(0,Y(A,B,C,D)11,10,9321113+=, ∑d 为无关项 二、分析题1、分析下图所示逻辑电路,列出真值表,说明其逻辑关系。

2、分析下图所示同步时序逻辑电路,作出状态转移表和状态图,说明这个电路能对何种序列进行检测?三、设计题1.设计一个三输入的组合逻辑电路,当输入的二进制码小于5时,输出为0,大于等于5时,输出为1。

要求: (1)列出真值表;(2)写出逻辑函数的最简与或式; (3)用非门和与非门实现该电路;(4)用74LS138实现该电路。

74LS138功能表2、设计一个按自然顺序变化的7进制加法计数器,计数规则为逢7进位,产生一个进位输出。

要求:选用边沿JK触发器设计实现该功能的同步时序逻辑电路,并画出逻辑电路图。

成考复习资料答案一、逻辑函数化简1. ABC+(ABC)+(ABCDE)=1''2.AC AD B A Y ++=二、分析题1. 逻辑表达式:1Y A B CI =⊕⊕2((()))()Y A B CI AB A B CI AB ''=⊕+=⊕+由逻辑表达式计算出真值表:A B C Y Y 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 11 1这是一个全加器电路。

2. 答:电路的状态方程和输出方程为:状态表和状态转移图如下:凡在输入序列中出现两个或两个以上“1” 之后再出现一个 “0” ,输出就为“1” ; 否则,输出为“0” 。

由电路图可得输出方程为:10Y XQ Q =驱动方程为:01100110()()()J X Q J X Q K XQ K X Q ⎧⎧''''==⎪⎪⎨⎨'''''==⎪⎪⎩⎩将驱动方程代入JK 触发器的特性方程中可得状态方程为:*01010*10101()Q X Q Q XQ Q Q X Q Q X Q Q ⎧''=++⎪⎨''''=+⎪⎩成考复习资料1001检测器,能够自启动三、设计题1. 解:(1)真值表:设输入A、B、C,输出FABC F0 0 0 00 0 1 00 1 0 00 1 1 01 0 0 01 0 1 11 1 0 11 1 1 1(2)逻辑函数的最简与或式;ACABABCCABCBAF+=++=(3)用非门和与非门实现ACABACABF⋅=+=用非门和与非门实现该电路的逻辑图如下图(a)所示(4)用74HC138实现A、B、C从A2、A1、A输入,令,1123===EEE765765765YYYmmmmmmABCCABCBAF⋅⋅=⋅⋅=++=++=用74HC138实现该电路的逻辑图见下图(b)图(a ) 图(b )2. (1)、解:状态转换图如下:由状态转换图可画出电路的次态卡诺图 Q 2Q 1Q 3 00 01 11 10 0 1 Q 2Q 1Q 3 00 01 11 10 0 1Q 3卡诺图 Q 2Q 1Q 3 00 01 11 10 0 1Q 2卡诺图 Q 2Q 1Q 3 00 01 11 10001 010 100 011 101 110 XXX 0000 0 1 0 1 1 X 00 1 0 1 0 1 X 0001 000010 011100101 110 111 Q 3Q 2Q 11Q1卡诺图画出分解的次态卡诺图,并化简求出电路的状态方程Q 3*=Q3Q2’+Q3’Q2Q1=(Q2Q1)Q3’+(Q2)’Q3Q 2*=Q1Q2’+Q3’Q2Q1’=(Q1)Q2’+(Q3’Q1’)Q2Q 1*=Q2’Q1’+Q3’Q1’=(Q2Q3)’Q1’+(1’)Q1与JK触发器特性方程比较得出驱动方程:J 3=Q2Q1; K3=Q2J 2=Q1; K2=(Q3’Q1’)’J 1=(Q2Q3)’; K1=1输出方程为:根据驱动方程画出电路图如图:Q 3Q1Q1=111 时,代入状态方程得:Q3*Q1*Q1*=000,所以该电路能自启动.1 0 0 11 0 X 032QQY⋅=复习资料2一、单选题1. 一个8选一数据选择器的数据输入端有个。

A. 1B. 2C. 3D. 4E. 82. 以下表达式中符合逻辑运算法则的是。

A. C·C=C2B. 1+1=10C. 0<1D. A+1=13. 欲使D触发器按Qn+1=Qn工作,应使输入D=________________。

A. 0B. 1C. QD.4. 在下列逻辑电路中,不是组合逻辑电路的有。

A. 译码器B. 编码器C. 全加器D. 寄存器5. 某存储器具有8根地址线和8根双向数据线,则该存储器的容量为__________。

A. 8×3B. 8K×8C. 256×8D. 256×2566. 一个16选1的数据选择器,其地址输入(选择控制输入)端有个。

A. 1B. 2成考复习资料C. 4D. 167. 用二进制码表示指定离散电平的过程称为_________。

A. 采样B. 量化C. 保持D. 编码8. 4位倒T型电阻网络DAC的电阻网络的电阻取值有_________种。

A. 1B. 2C. 4D. 89. 将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为_________。

A. 采样B. 量化C. 保持D. 编码10. 当逻辑函数有n个变量时,共有个变量取值组合?A. nB. 2nC. n2D. 2 n11. 要构成容量为4K×8的RAM,需要__________片容量为256×4的RAM。

A. 2B. 4C. 8D. 3212. 对于JK触发器,若J=K,则可完成__________触发器的逻辑功能。

A. RSB. DC. TD. Tˊ13. 以下电路中常用于总线应用的有________________。

A. TSL门B. OC门C. 漏极开路门D. CMOS与非门14. A+BC = 。

A. A+BB. A+CC. (A+B)(A+C)D. B+C15. 以下四种转换器,_________是A/D转换器且转换速度最高。

A. 并联比较型B. 逐次逼近型C. 双积分型D. 施密特触发器二、判断题1 权电阻网络D/A转换器的电路简单且便于集成工艺制造,因此被广泛使用。

()2 主从JK触发器、边沿JK触发器和同步JK触发器的逻辑功能完全相同。

()3 PROM的或阵列(存储矩阵)是可编程阵列。

()4 RS触发器的约束条件RS=0表示不允许出现R=S=1的输入。

()5若要实现一个可暂停的一位二进制计数器,控制信号A=0计数,A=1保持,可选用T触发器,且令T=A。

()三、问答题1. 分析下图所示电路,试问输入信号A、B、C不同组合时,电路中P点和输出端F的状态。

2 门电路输出波形四、设计题成考复习资料1. 设计一个四人表决电路,当四人中有三人或三人以上赞成时表决通过,否则表决失败。

要求:(1)写出逻辑函数的最小项之和的形式,并利用卡诺图化简法写出最简与或式;(2)画出利用与非门实现该逻辑问题的电路图。

(3)利用8选1数据选择器74HC151来实现四人表决电路。

输入输出D A2A1A0S'Y Y'×××× 1D0 0 0 0 0D1 0 0 1 0D2 0 1 0 0D3 0 1 1 0D4 1 0 0 0D5 1 0 1 0D6 1 1 0 0D7 1 1 1 00 1D0D'D11D'D22D'D33D'D44D'D55D'D66D'D77D'74HC151功能表 74HC151逻辑功能示意图2. 设计一个按自然顺序变化的6进制加法计数器,计数规则为逢6进位,产生一个进位输出。

要求:(1)选用边沿JK触发器设计实现该功能的同步时序逻辑电路,并画出逻辑电路图。

(2)利用二-五-十进制异步计数器进行设计,画出逻辑电路图。

74LS290的功能表 74LS290的逻辑示意图答案一、 1-5 EDDDC 6-10 CDBBD 11-15 DCACA二、判断题1-5 FTTTF三、问答题1解:当C=1时,三态门输出为高阻状态。

从TTL与非门电路可知,输入为高阻态(等同于悬空)时,相当于输入为高电平2解:设与门的输出为F1,或门的输出为F2。

对于与门:“有低出低,全高出高”;对于或门:“有高出高,全低出低”。

它们的输出波形如下图所示。

四、设计题1. 解:(1)真值表:设输入A、B、C、D,取值为0表示不同意,取值为1表示同意,输出Y=0表示表决不通过,Y=1表示表决通过。

由题意可列出真值表:A B C D Y0 0 0 0 00 0 1 0 00 0 1 1 00 1 0 0 00 1 0 1 00 1 1 0 00 1 1 1 11 0 0 0 01 0 0 1 01 0 1 0 0 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1标准与或表达式:Y A BCD AB CD ABC D ABCD ABCD ''''=++++ 卡诺图逻辑函数的最简与或式;Y BCD ACD ABD ABC =+++(3)用非门和与非门实现(()()()())Y BCD ACD ABD ABCBCD ACD ABD ABC =+++'''''=用非门和与非门实现该电路的逻辑图如下图(a )所示,利用74HC151实现该电路的逻辑图如下图(b )所示。

(a ) (b )2. (1)解:状态转换图如下:Q 3Q 2Q 1由状态转换图可画出电路的卡诺图*2102010202Q Q Q Q Q Q Q Q Q Q'''=+=+001000 010 011100101111 110成考复习资料*11021020101Q Q Q Q Q Q Q Q Q Q Q''''''=+=+*00Q Q'=20C Q Q=与JK触发器特性方程比较得出驱动方程:21011202011011J Q Q JJ Q QK Q KK Q⎧'==⎧⎧⎪=⎨⎨⎨===⎩⎩⎪⎩根据驱动方程以及输出方程画出电路图如图所示:001000 010 011100101111Q3Q2Q1110由状态图可知该电路能自启动(2)74LS290具有异步清零和异步置九的功能。