内插滤波器及其FPGA实现

- 格式:pdf

- 大小:131.49 KB

- 文档页数:3

cic滤波器的FPGA实现发布时间:2016-01-26 15:07:21技术类别:CPLD/FPGA一、关于多采样率数字滤波器很明显从字面意思上可以理解,多采样率嘛,就是有多个采样率呗。

前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号,具体例子我也不解释了,我们大学课本上多速率数字信号处理这一章也都举了不少的例子。

按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。

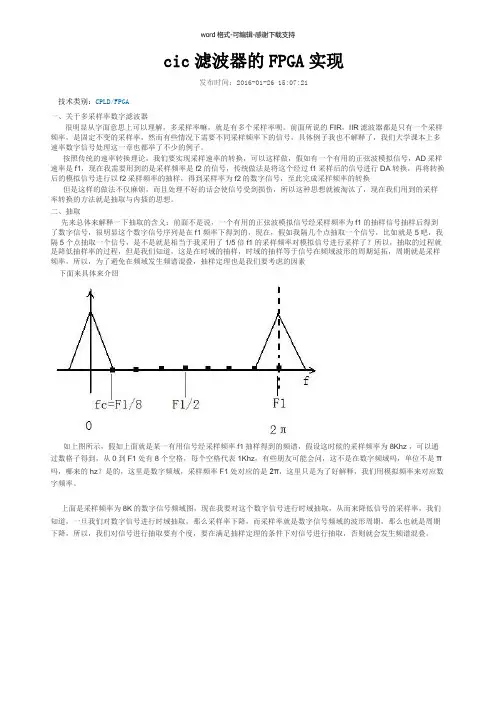

二、抽取先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素下面来具体来介绍如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8Khz ,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。

DVB-S中可变插值率CIC滤波器设计及其FPGA实现作者:张文坡常亮史丽荣来源:《现代电子技术》2008年第11期摘要:在数字上变频中常用的CIC滤波器的基础上,提出了一种适用于DVB-S系统的可变插值率CIC滤波器的实现结构,首先实现一个内插因子为2的CIC滤波器单元,然后根据不同的内插因子要求,来重复地调用这些内插因子为2的基本滤波器模块,这种CIC滤波器的实现结构符合结构化的设计思想。

通过Verilog HDL语言在FPGA上对其进行了仿真、综合给出了相应的仿真结果,并成功应用于DVB-S系统中。

关键词:积分梳状滤波器;FPGA;插值;数字上变频;数字视频广播中图分类号:TN911.73 文献标识码:B文章编号:1004-373X(2008)11-103-Design of Variable Interpolated Filter CIC in DVB-S and Its FPGA RealizationZHANG We,,(1.Jiazai Telecommunication Equipment Co.Ltd.,Xi′an,710075,China;2.Satellite Application System Department of China Academy of SpaceTechnology,Beijing,100086,China;3.Xi′an Node Science Technology Co.Ltd.,Xi′an,710075,China)Abstract:In this paper,a new variable interpolated filter in DVB-S(Digital Vidoe Broadcast by Satellite) is introduced based on the common filter of cascaded integrator comb.Firstly a CIC filter module with interpolation factor 2 is designed,then we could reuse the basic module according to the interpolation factor.Based on the theory of CIC filter,the filter with FPGA is simulated and synthesized,the results is given,and realizes it in the system of DVB-S.Keywords:CIC;FPGA;interpolation;digital up converter;DVBCIC(Cascaded Integrator Comb)滤波器是现代数字上变频的核心技术,具有简单而高效的结构。

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

基于FPGA的中值滤波算法的实现1.背景知识中值滤波法是⼀种⾮线性平滑技术,它将每⼀像素点的灰度值设置为该点某邻域窗⼝内的所有像素点灰度值的中值.中值滤波是基于排序统计理论的⼀种能有效抑制噪声的⾮线性信号处理技术,中值滤波的基本原理是把数字图像或数字序列中⼀点的值⽤该点的⼀个邻域中各点值的中值代替,让周围的像素值接近的真实值,从⽽消除孤⽴的噪声点。

⽅法是⽤某种结构的⼆维滑动模板,将板内像素按照像素值的⼤⼩进⾏排序,⽣成单调上升(或下降)的为⼆维数据序列。

⼆维中值滤波输出为g(x,y)=med{f(x-k,y-l),(k,l∈W)} ,其中,f(x,y),g(x,y)分别为原始图像和处理后图像。

W为⼆维模板,通常为3*3,5*5区域,也可以是不同的的形状,如线状,圆形,⼗字形,圆环形等。

中值滤波法对消除椒盐噪声⾮常有效,在光学测量条纹图象的相位分析处理⽅法中有特殊作⽤,但在条纹中⼼分析⽅法中作⽤不⼤.中值滤波在图像处理中,常⽤于保护边缘信息,是经典的平滑噪声的⽅法。

2.中值滤波理论中值滤波是⼀种⾮线性滤波,在数字图像处理中,对于 N X N (N 为奇数) 中值滤波器,可以滤除⼩于或等于邻域中(N 2- 1)/2 个像素的噪声并且较好地保持图像的边缘[3]。

对图像进⾏中值滤波处理⾸先要确定⼀个模板 N ×N ,⼀般选取 3X 3 或 5 ×5。

中问位置的图像数据的表达式为f (x ,y ) = med{f (x ± k,Y ± Z) , (K≤ (N -1) /2,Z≤ (N-1) /2) }要得到模板中数据的中间值,⾸先要将数据按⼤⼩排序,然后根据有序的数字序列来找中问值。

中值滤波排序的过程有很多成熟的算法,如冒泡排序、⼆分排序等,⼤多是基于微机平台的软件算法,⽽适合硬件平台的排序算法则⽐较少。

3.FPGA硬件实现⽅法L(1,1) L(1,2) L(1,3)L(2,1) L(2,2) L(2,3)L(3,1) L(3,2) L(3,3)如上所⽰,为⼀个3x3的图像模板,第⼀步:分别对三⾏像素进⾏排序(例:由L11,L12,L13得到L1max,L1mid,L1min);第⼆步:分别对三⾏像素中的最⼤,中间和最⼩分别进⾏排序(例:由L1max,L2max,L3max得到Lmax_max,Lmax_mid,Lmax_min);第三步:对最⼤的最⼩,中间的中间以及最⼩的最⼤进⾏排序(例:由Lmax_min,Lmid_mid,Lmin_max得到midian);FPGA的算法实现步骤基本如此。

基于FPGA的数字滤波器设计与实现数字滤波器是信号处理中常用的工具,可以通过滤除不需要的频率成分或者增强需要的频率成分对信号进行处理。

在数字信号处理领域,基于FPGA的数字滤波器设计与实现是一项重要的研究课题。

本文将介绍FPGA数字滤波器的设计原理、实现方法和应用领域。

首先,我们来了解一下FPGA(可编程逻辑门阵列)是什么。

FPGA是一种可重构的硬件平台,它由大量的可编程逻辑门电路构成。

相比于传统的ASIC(专用集成电路)设计,FPGA具有更高的灵活性和可重构性,可以实现多种不同的电路功能。

在数字滤波器设计中,FPGA可以用来实现各种类型的滤波器,如低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

FPGA数字滤波器的设计通常包括以下几个步骤:1. 规格定义:确定滤波器的工作频率范围、滤波器类型(如FIR滤波器或IIR滤波器)、滤波器阶数和滤波器的性能指标等。

2. 滤波器设计:根据规格定义,选择适合的滤波器结构和滤波器系数设计方法,如窗函数法、频率采样法或者最小二乘法等。

设计好的滤波器可以通过MATLAB等工具进行模拟验证。

3. 滤波器实现:将滤波器设计转化为可在FPGA上实现的硬件描述语言(如VHDL或Verilog)。

在这个步骤中,需要将滤波器结构转化为逻辑电路,并根据具体的FPGA平台选择适合的资源分配和布局策略。

4. 仿真验证:使用EDA(电子设计自动化)工具对滤波器进行仿真验证,确保其在FPGA上的功能和性能与设计规格一致。

5. 实际实现:将经过仿真验证的滤波器设计烧录到FPGA 芯片中,并进行实际的性能测试。

测试结果可以与仿真结果进行比较,来评估滤波器的实现质量。

FPGA数字滤波器的设计和实现具有以下几个优势:1. 高性能:FPGA提供了大量的逻辑资源和高速IO接口,可以实现复杂的滤波器结构和算法,并能够处理高速数据流。

2. 低功耗:相比于通用处理器,FPGA的功耗较低,可以在不牺牲性能的情况下降低系统的功耗。

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。

一种基于fpga的farrow滤波器及其实现方法随着数字信号处理技术的飞速发展,FPGA(现场可编程门阵列)因其在并行处理和实时性方面的优势,被广泛应用于通信、雷达等领域。

Farrow滤波器作为一种高效的多速率信号处理工具,也在FPGA上得到了广泛实现。

本文将详细介绍一种基于FPGA的Farrow滤波器及其实现方法。

一、FPGA简介FPGA是一种高度集成的可编程数字逻辑器件,用户可以根据需求对其进行编程,实现各种数字信号处理算法。

FPGA具有灵活性强、开发周期短、并行处理能力强等特点,使其在数字信号处理领域具有广泛的应用前景。

二、Farrow滤波器原理Farrow滤波器是一种基于多项式插值的滤波器,可以实现多速率信号处理。

其核心思想是通过调整插值多项式的系数,实现对信号采样率的转换。

Farrow滤波器具有线性相位、低延迟、低复杂度等优点,适用于通信系统中的多速率信号处理。

三、基于FPGA的Farrow滤波器实现方法1.设计原理基于FPGA的Farrow滤波器实现方法主要包括三个部分:滤波器系数计算、插值操作和滤波操作。

首先,根据所需的插值倍数和滤波器阶数,计算滤波器系数;其次,通过插值操作对输入信号进行上采样;最后,利用计算出的滤波器系数对上采样后的信号进行滤波处理。

2.滤波器系数计算Farrow滤波器的系数计算可以通过多种方法,如最小二乘法、矩阵求逆等。

在实际应用中,可以根据滤波器性能要求和FPGA的资源限制,选择合适的计算方法。

计算得到的滤波器系数需要存储在FPGA的BRAM(块随机存储器)中,以供后续插值和滤波操作使用。

3.插值操作插值操作是Farrow滤波器的核心部分,其主要作用是将输入信号的采样率提高。

在FPGA中,插值操作可以通过流水线技术实现,提高处理速度。

插值倍数可以根据实际需求进行设置,如2倍、4倍等。

4.滤波操作滤波操作是对插值后的信号进行处理,以消除混叠效应和降低噪声。

在FPGA中,滤波操作通常采用分布式算法(DA)实现,以减少资源消耗和功耗。

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的工具,用于去除信号中的噪声或不需要的频率成分。

在数字信号处理中,滤波器可以通过软件算法实现,但随着现代电子技术的发展,使用基于FPGA的滤波器可以实现更高效、实时的信号处理。

本文将介绍基于FPGA的滤波器设计与实现的方法和步骤。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,由大量的逻辑门、存储单元和可编程连接组成。

FPGA的特点是可重构性强,可以根据需要编程实现各种逻辑功能。

在数字信号处理中,可以将滤波器的算法实现在FPGA中,利用其并行处理的能力来提高处理速度和效率。

三、滤波器的基本原理滤波器可以根据其频率响应的特点分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

滤波器的设计目标是在保留需要的信号成分的同时,去除不需要的噪声或频率成分。

常用的滤波器设计方法有FIR滤波器和IIR滤波器。

四、基于FPGA的滤波器设计步骤1. 确定滤波器的类型和设计要求:根据信号处理的需求,确定滤波器的类型(低通、高通等)和性能指标(截止频率、通带衰减等)。

2. 确定滤波器的结构:选择合适的滤波器结构,如直接形式、级联形式等。

3. 设计滤波器的传递函数:根据滤波器的类型和设计要求,设计出满足要求的传递函数。

4. 将传递函数转化为差分方程:根据所选滤波器结构,将传递函数转化为差分方程。

5. 实现差分方程的计算:将差分方程转化为FPGA可以计算的形式,使用硬件描述语言(如Verilog、VHDL)编写计算模块。

6. 将计算模块综合到FPGA中:使用相应的工具将计算模块综合到FPGA中,生成比特流文件。

7. 下载比特流文件到FPGA:将生成的比特流文件下载到FPGA中,使其开始工作。

8. 测试和优化:对设计的滤波器进行测试,并根据测试结果进行优化,以满足设计要求。

FPGA四阶IIR数字滤波器实现常用的数字滤波器有FIR数字滤波器和IIR数字滤波器。FIR数字滤波器具有精确的线性相位特性,在信号处理方面应用极为广泛,而且可以采用事先设计调试好的FIR数字滤波器IPCore来完成设计,例如Altera公司提供的针对Altera系列可编程器件的MegaCore,但是需要向Altera公司购买或申请试用版。另外,对于相同的设计指标,FIR滤波器所要求的阶数比IIR滤波器高5~10倍,成本较高,而且信号的延迟也较大。IIR滤波器所要求的阶数不仅比FIR 滤波器低,而且可以利用模拟滤波器的设计成果,设计工作量相对较小,采用FPGA实现的IIR 滤波器同样具有多种优越性。IIR滤波器主要有巴特沃斯滤波器、切比雪夫滤波器和椭圆滤波器几种。给出了以上三种滤波器实现同样性能指标所需的阶数及阻带衰减的比较,如表1所示。由表1可见,椭圆滤波器给出的设计阶数比前两种低,而且频率特性较好,过渡带较窄,但是椭圆滤波器在通带上的非线性相位响应最明显。本系统选用椭圆函数滤波器进行设计。1 原理分析数字滤波器实际上是一个采用有限精度算法实现的线性非时变离散系统,它的设计步骤为:首先根据实际需要确定其性能指标,再求得系统函数H(z),最后采用有限精度算法实现。根据需要,本系统的设计指标为:模拟信号采样频率为2MHz,每周期最少采样20点,即模拟信号的通带边缘频率为fp=100kHz,阻带边缘频率fs=1MHz,通带波动Rp不大于0.1dB(通带误差不大于5%),阻带衰减As不小于32dB。换算为数字域指标为:Wp=0.1π,Ws=0.2π, Rp=0.1dB,As=32dB。系统函数H(z)的计算采用Matlab软件比较方便,其中有两个现成的函数可以使用:ellipord(wp/pi,ws/pi,Rp,As)函数用来计算数字椭圆滤波器的阶次N和3dB截止频率wn,而ellip(N,Rp,As,wn)函数可以求得直接型椭圆IIR滤波器的各个系数。通过调用以上两个函数计算得到的系统函数H(z)为:这是一个四阶IIR系统,Matlab计算出该系统的频率响应如图1所示,可见满足设计要求。如果采用直接型结构实现,需用的乘法器和延迟单元相对较多,而且分子和分母的系数相差较大,需要较多的二进制位数才能实现相应的精度要求。如果采用二阶节级联实现,一来各基本节的零点、极点可以很方便地单独进行调整,二来可以降低对二进制数位数的要求。给出了一个直接型结构转为级联型结构的dir2cas.m文件,利用该函数求得系统函数的级联表达形式为:H(z)=H1(z)×H2(z)=(0.11-0.1041z -1+0.11z -2)/(1-1.58z -1+0.6469z -2)×(0.2464-0.426z -1+0.2464z -2)/(1-1.7753z -1+0.892z -2)由上式可以看出,每个二阶节的分子、分母系数差异减少了。值得注意的是,在分配二阶节的增益时,要保证每个节不会发生运算溢出,可以先用Matlab软件分析计算来合理安排各节的增益。经过计算,本文采用第一级分配0.11,第二级分配0.2464,可以保证在要求的输入范围,没有数据溢出发生。2 系统实现将第一个二阶节的系统函数表示为差分方程:y1(n)=a0x(n)-a1x(n-1)+a2x(n)+b0y(n-1)-b1y(n-2)=0.11x(n)-0.1041x(n-1)+0.11x(n)+1.58y(n-1)-0.6469y(n-2)可以看出,一个二阶节的实现需要五次乘法运算、四次加法运算(采用二进制补码将减法运算变为加法运算)。两个二阶节共需要十次乘法运算。虽然现在已有上千万门的FPGA产品可供选用,但是一般应用时全部采用硬件阵列乘法器毕竟不太合适,而如果采用串行乘法器进行分时复用,其工作速度也不太理想。本文采用一个折中的方法实现,即乘加单元(MAC)的乘法器采用阵列乘法器,而不使用串行乘法器,以提高运算速度。需要注意的是,MAX+plusⅡ的LPM库中乘法运算为无符号数的阵列乘法,所以使用时需要先将两个补码乘数转换为无符号数相乘后,再将乘积转换为补码乘积输出。每个二阶节完成一次运算共需要6个时钟周期,而且需采用各自独立的MAC实现两级流水线结构,即每个数据经过两个二阶节输出只需要6个时钟周期。2.1 系统原理框图系统原理框图如图2所示,模拟信号经过TLC5510转换为00H~FFH的二进制数后,送入四阶IIR低通滤波器,处理后输出10位二进制数送AD7520得到双极性的模拟电压输出。2.2 顶层IIR模块顶层IIR模块如图3所示。主要由一个时序控制模块IIRC、两个IIR二阶节模块(IIR1和IIR2)构成。IIR模块设计为10位二进制补码输入,最高位ad9为补码符号位,次高位ad8用于防止运算时的溢出。可见该IIR模块实际可以输入9位二进制补码数,但TLC5510的输出数据为8位,输入到IIR模块时,将ad9和ad8引脚均接地,即输入为正极性电压。clr输入端为异步清零端,高电平有效。当输入时钟clk为12MHz时,IIR模块产生一个频率为2MHz的clk_ad输出时钟提供给TLC5510。输出数据dout为10位二进制补码。IIR1和IIR2模块构成级联结构。2.3 IIR1和IIR2模块IIR1、IIR2模块主要由两个模块构成,一个是数据移位模块,在CLK_R时钟作用下将差分方程的各x、y值延迟一个时钟;另一个模块是补码乘加单元,用VHDL语言编写,两个乘数先取补后再进行阵列乘法,在CLK_B时钟控制下完成一次乘加运算,乘积取补后输出,共需要6个时钟。差分方程的各系数如表2所示,采用10位定点纯小数补码表示。表2 二阶差分方程的系数另外模块中的五个系数定义为常数,以节省硬件资源,并且采用0舍1入法进行数据处理,尽量提高数据运算精度。VHDL程序如下:entity smultadd1 isport (clk_regbt,clk_reg: in std_logic:x0,x1,x2,y0,y1:in std_logic_vector(9 downto 0);yout: out std_logic_vector(9 downto 0));end smultadd1;architecture behav of smultadd1 issignal tan,tbn,tp2n:std_logic;signal cnt: std_logic_vector(2 downto 0);signal ta,tb,taa,tbb:std_logic_vector(8 downto 0);signal tmpa,tmpb:std_logic_vector(9 downto 0);signal tp:std_logic_vector(18 downto 0);signal tpp:std_logic_vector,22 downto 0);signal ytmp,p:std_logic_vector(23 downto 0);constant a0:std_logic_vector(9 downto 0:=“0000011100”(其余常数说明略)begintp2n<=tan xor tbn;--求补后送阵列乘法器taa<=not ta +…1‟ when (tan=…1‟) else ta;tbb<=not tb +…1‟ when (tbn=…1‟) else tb;tpp<=…1‟&…1‟&…1‟&…1‟& not tp +…1‟ when(tp2n=…1‟) else tp; tmpa<=a0 when cnt=0 elsea1 when cnt=1 elsea2 when cnt=2 elseb0 when cnt=3 elseb1 when cnt=4 else (others=>…0‟);tmpb<=x0 when cnt=0 elsex1 when cnt=1 elsex2 when cnt=2 elsey0 when cnt=3 elsey1 when cnt=4 else (others=>…0‟);ta<=tmpa(8 downto 0);tb<=tmpb(8 downto 0);tan<=tmpa(9);tbn<=tmpb(9);tp<=taa*tbb;p<=(others=>…0‟) when (tmpb=“0000000000”) elsetp2n & tpp;process (clk_reg,clk_regbt)beginif clk_reg=…1‟ then cnt<=“000”;ytmp<=(others=>…0‟);elsif (clk_regbt‟event and clk_regbt=…1‟) thenif cnt<5 then cnt<=cnt+1;ytmp<=ytmp+p;elsif (cnt=5) thenif ytmp(7)=…1‟ thenyout(8 downto 0)<=ytmp(16 downto 8)+1;yout(9)<=ytmp(23);else yout(8 downto 0)<=ytmp(16 downto 8);yout(9)<=ytmp(23); end if;end if;end if;end process;end behav;IIR2模块的输出数据采用将补码最高符号位直接取反转换为移码后,就可以送到DAC7520实现双极性信号输出。3 系统性能测试系统性能的测试采用单极性方波周期信号作为输入信号。信号的频率为100kHz,在采样频率为2MHz时,每个周期采样20个点,换算成数字域频率为0.1π,其二次谐波的数字频率为0.2π。输入到TLC5510的信号电压幅度为0~2V,则经过A/D转换后的输出为00H~FFH。由于低通滤波器的阻带截止频率选在200kHz,衰减32dB,由信号理论分析可知,周期方波信号没有二次谐波,所以对三次谐波的衰减经过IIR滤波器后输出有直流分量的基波(频率为100kHz)正弦信号。理论计算给出的方波周期信号基波幅度为:2E/π=(2×255)/π=162.34输入一个周期的数据,Matlab的计算值与MAX+plusⅡ的仿真值如表3所示。由表3可见,仿真输出值为补码,谷点输出值993换算成符号数为993-1024=-31。Matlab软件计算的满度输出值为286.9,其基波幅度为[286.9-(-34.9)]/2=160.9,与理论值的误差为:(160.9-162.34)/162.34=-0.87%四阶IIR滤波器实现的满度输出值为[282-(-31)]/2=156.5,与理论值的误差为:(156.5-162.34)/162.34=-3.6%这是由于有限精度算法所引起的误差,可以通过增加二进制位数来提高系统的运算精度。图4给出单极性方波信号的前三个周期经过滤波后得到的含直流分量的输出波形,其中实线为Matlab的计算值,“*”为MAX+plusⅡ的仿真输出。可见,该四阶级联IIR滤波器达到了设计要求。如果改变滤波器的输入时钟频率,则可以改变滤波器的截止频率。另外如果输入无直流分量的周期信号,而且其频率为采样频率的1/20,则该低通滤波器可以直接得到基波分量输出。其实,要将TLC5510输出的直流分量滤出很容易,只需利用FPGA做一个减法运算即可。。

(34条消息)FIR滤波器的MATLAB与FPGA的设计实现引言数字滤波器是数字信号系统里面最常用、最重要、最基本的元件之一。

有限脉冲响应(Finite Impulse Response,FIR)滤波器可以设计成任意幅频特性,同时保证精确,严格的线性相位特性。

因此在电子通信、图像处理、模式识别等领域,FIR数字滤波器被广泛应用。

本文主要通过以低通滤波器的MATLAB与FPGA的设计实现来介绍FIR滤波器的原理介绍,架构研究,设计实现等。

原理介绍FIR滤波器的方程表达式为:y(n)=∑x(k)h(n-k) k=0,1…N-1;0≦n≦N-1;其方程分解式为:y(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+…+h(k)x(n-k);根据FIR滤波器的幅频特性可知,FIR滤波器为奇对称和偶对称两种形式。

例如当滤波器阶数为偶数n=3时,根据线性相位跟对称法则可得:h(0)=h(3),h(1)=h(2);可得到方程式为:y(n)=h(0){x(n-1)+x(0)}+h(1){x(n-2)+x(1)};当滤波器阶数为奇数n=4时,根据线性相位跟对称法则可得:h(0)=h(4),h(1)=h(3),h(2)独立一个;可得到方程式为:y(n)=h(0){x(n-1)+x(0)}+h(1){x(n-2)+x(n-3)}+h(2)x(n-2);故其系统函数为从其系统函数可以看得出FIR系统是线性时不变系统,只在原点上存在极点,这使得FIR系统具有全局稳定性。

从FIR系统函数也可以看得出FIR滤波器其实是由一个抽头延迟线加法器和乘法器的集合构成的。

每个乘法器的操作系数为FIR滤波器系数。

因此这种抽头延迟线结构的架构实现图可如下所示:MATLAB设计实现在matlab里面设计数字滤波器既可以通过窗函数自己编写程序来设计FIR滤波器,也可以通过调用工具箱来设计FIR滤波器。

通过编写程序来设计FIR滤波器比较普遍,滤波器的参数等改动也比较方便,与FPGA做联合功能仿真验证也方便。