半导体芯片测试成本降低方案

- 格式:pdf

- 大小:2.84 MB

- 文档页数:2

TEST SOLUTIONSTEST SYSTEMS• 节省时间和成本-解放您的内部资源• 加快产品面世速度-迅速完成测试系统开发和部署• 解决下一代的难题-提供创新的解决方案来解决最新的测试难题 • 提高效率-通过各种解决方案来实现运营效率的最大化• 量身定制的解决方案-设计完全从您的需求出发• 从各方面完善解决方案-从设计概念直至安装和技术支持半导体行业的好伙伴如果一成不变的测试设备无法满足您的需要,或者您的工程团队有力所不及的地方,尽管来找我们。

我们会用创新、灵巧的测试解决方案来帮您解决最棘手的半导体测试难题。

我们的团队会与您紧密配合,创建全新的测试解决方案,这些方案不仅能够满足您的实际要求,还能帮您实现降低测试成本、提高效益和完善测试流程的商业目标。

20 多年来,我们的设备已经为全世界的各大半导体企业测试过数十亿颗芯片。

现在,您可以随时享用这些深厚的技术积淀。

雄厚的实力Astronics T est Systems 可以通过交钥匙设计和各种生产服务来打造出色的半导体测试解决方案,以满足您对生产和测试成本的要求,提高运转效率。

由各具专长的半导体测试人员组成的综合性团队将根据您的各项具体目标,为您量身定制一套完备的系统,其中包括:• 测试策略• 硬件设计• 软件开发与集成• 制造• 安装• 项目管理• 后续技术支持我们的团队采用垂直整合架构,电气设计、机械设计、软件设计、车间和测试工程等都聚集在一个厂房内。

创新的半导体测试解决方案为您而设计©2018 Astronics Test Systems ATS 定制半导体解决方案 2.0马上开始行动。

若需了解详情或安排系统演示时间,请联系Astronics T est Systems 。

4 Goodyear, Irvine, CA 92618 电话: (800) 722.2528 电话: (949) 859-8999 SemiTest@astronics .com丰富的半导体行业经验。

芯片测试方案一、引言芯片测试是电子产品制造过程中的重要环节之一,通过对芯片进行全面、准确的测试,可以保证产品的质量和性能。

本文将介绍芯片测试的意义、测试方案的设计和实施过程。

二、芯片测试的意义1. 提高产品质量:芯片是电子产品的核心部件,其质量直接影响整个产品的性能和稳定性。

通过对芯片进行全面的测试,可以及早发现和解决潜在问题,提高产品的质量。

2. 降低成本:及早发现和解决芯片问题可以避免后期的重大故障和召回事件,降低维修成本和售后成本。

3. 提高生产效率:芯片测试可以帮助生产线实现自动化生产,提高生产效率和产能。

三、芯片测试方案的设计1. 确定测试目标:根据产品的特性和需求,确定芯片测试的主要目标,如性能测试、可靠性测试、功耗测试等。

2. 测试环境的搭建:根据测试目标和产品的特性,搭建适合的测试环境,包括测试设备、测试软件和测试工具的选择和配置。

3. 测试用例的设计:根据产品的功能和性能要求,设计一系列测试用例,覆盖产品的各个方面。

测试用例应该具有代表性,能够全面测试芯片的功能和性能。

4. 测试流程的制定:根据测试用例,制定详细的测试流程,包括测试的顺序、测试的步骤以及测试结果的记录和分析。

5. 数据分析和问题解决:对测试结果进行数据分析和问题解决,查找问题的原因并给出解决方案。

四、芯片测试方案的实施过程1. 准备工作:包括测试环境的搭建、测试设备的准备和测试用例的编写。

2. 测试执行:按照测试流程执行测试用例,记录测试结果和问题。

3. 数据分析:对测试结果进行数据分析,包括统计数据、图表分析和问题的归类。

4. 问题解决:根据数据分析的结果,找出问题的原因并给出解决方案。

5. 结果验证:对解决方案进行验证,确保问题得到解决。

五、常见的芯片测试方法1. 功能测试:测试芯片的各个功能模块是否正常工作,包括输入输出、通信接口等。

2. 性能测试:测试芯片的性能指标,如速度、响应时间、功耗等。

3. 安全测试:测试芯片的安全性能,包括防火墙、加密算法等。

半导体制造成本优化探索降低半导体制造成本的最佳实践和策略随着科技的不断发展和半导体市场的不断扩大,半导体制造成本优化成为半导体企业关注的焦点。

降低半导体制造成本可以提高企业的竞争力,增强市场份额,并最终实现可持续发展。

本文将探讨降低半导体制造成本的最佳实践和策略,从供应链管理、工艺优化和设备更新等多个角度进行分析。

一、供应链管理供应链管理在降低半导体制造成本方面起着重要作用。

通过合理的供应链布局和有效的库存管理,可以降低原材料和零部件的采购成本。

企业可以选择与可靠、价格合理的供应商建立长期合作关系,从而获得更好的价格和服务。

此外,供应链中的物流和仓储也需要进行优化。

通过合理规划运输路线、提高运输效率和减少仓储费用,可以有效控制供应链成本。

同时,信息技术的应用也是提高供应链效率的重要手段,企业可以借助物联网、大数据分析等技术手段,实现供应链的数字化和智能化管理。

二、工艺优化工艺优化是降低半导体制造成本的关键。

在半导体制造过程中,不断优化工艺流程和制造技术,可以提高生产效率、降低废品率,并减少生产周期和能源耗费。

首先,企业可以引入先进的制造技术和设备,以提高制造效率和产品质量。

例如,采用更先进的光刻技术和薄膜沉积技术,可以实现更高精度的芯片制造。

此外,优化工艺流程和生产线布局,合理安排设备的使用和作业顺序,也可以提高生产效率。

另外,企业还可以通过精细化管理来降低成本。

通过实施精益生产和六西格玛等管理方法,减少浪费和不合格品数量。

此外,进行全面质量管理、精确的生产计划和优化的设备维护,也可以有效降低制造成本。

三、设备更新随着科技的不断进步,半导体制造设备也在不断更新换代。

及时更新设备可以提高生产效率、降低能耗和维护成本,从而实现半导体制造成本的降低。

企业应密切关注最新的设备技术和市场动态,选择适合自身需求的先进设备。

同时,对老旧设备进行合理淘汰和更新,以提高生产效率和产品质量。

此外,企业还可以考虑采用租赁设备的方式,避免高额购买成本,降低资金压力。

晶圆可接受度测试(WAT)晶圆⽣产出来后,在出晶圆⼚之前,要经过⼀道电性测试,称为晶圆可接受度测试(WAT)。

这个测试是测试在切割道(Scribe Line)上的测试键(TestKey)的电性能。

测试键通常设计有各种原件,例如不同尺⼨的NMOS、PMOS、电阻、电容以及其他⼯艺相关的特性。

这⼀道可以当做是初选。

那些有严重⽣产问题从⽽使得测试键的电性能超出规格之外的晶圆会在这⼀道被筛选出来,报废掉。

这⼀道报废掉的晶圆,因为还没有出货到客户⼿⾥,所以是不收取客户钱的,由晶圆⼚⾃⼰吸收。

WAT测试结束后,晶圆⼯艺就算完成。

下⼀步就是来到测试⼚这⾥进⾏测试。

第⼀道晶圆切割前的测试我们称为CP (Chip Probing), 因为这⼀道测试是在完整的晶圆上测的,⽤到的机台,我们称作Prober。

每⼀个产品,都会有针对⾃⼰设计的Prober Card, 上⾯根据芯⽚的测试焊盘(Pad)的位置装有对应的测试探针及电路与测试台连接。

每次测的时候,测试头从上⾯压下来,探针就会扎到Pad上,然后供电进⾏测试。

两期我们聊了芯⽚的封装和测试问题,包括CP测试,FT测试和系统级测试(没看过的朋友可以点击这⾥你不知道的那些芯⽚测试和测试⿊幕和你了解芯⽚封装技术吗?)。

这⼀次我们聊⼀下半导体中良率的问题。

良率是个啥?有什么⽤?良率是什么?准确的说,就是总共的芯⽚(可以是⼀⽚wafer,可以是⼀个批次,可以是⼀个产品,或者是⼀段时间内有多少芯⽚等等)。

在这些芯⽚测试完成后,有哪些芯⽚是通过测试的,两者相除就是良率,为了聊起来⽅便,我们就拿晶圆级测试(CP)来做例⼦。

下⾯是⼀⽚foundry寄给测试⼚的wafer,现在要进⾏CP测试了。

现在我们假设这⽚wafer总共有100颗芯⽚,在完成CP1,CP2,CP3之后,只有92颗芯⽚是通过的。

所以说,我们把这⼀⽚的良率称作是92%(92/100)。

那你可能会问,那⼜怎么了,有92颗芯⽚能⽤,我就⽤92颗呗,可不是这样哦。

半导体芯片项目运营管理方案目录一、项目概况 (2)二、发展规划 (3)三、市场营销管理 (6)四、财务管理 (8)五、人力资源管理 (11)六、运营管理保障措施 (14)七、质量管理 (16)八、主要经济指标一览表 (19)声明:本文内容信息来源于公开渠道,对文中内容的准确性、完整性、及时性或可靠性不作任何保证。

本文内容仅供参考与学习交流使用,不构成相关领域的建议和依据。

半导体芯片行业在近年来持续快速发展,得益于技术创新和全球需求的增长。

当前,随着人工智能、物联网和5G技术的普及,对高性能半导体芯片的需求不断上升。

行业主要集中在几个技术前沿的领域,如小型化、集成度提升和功耗优化。

尽管面临供应链挑战和国际贸易摩擦,半导体芯片依然是推动现代科技进步的核心驱动力,未来的技术突破将进一步影响各行各业的变革。

一、项目概况(一)项目名称半导体芯片项目(二)建设单位1、项目建设单位:xx2、项目选址:xx(三)项目投资估算1、总投资:24135.19万元2、建设投资18395.56万元3、建设期利息:490.79万元4、流动资金:5248.84万元(三)盈利能力1、年产值:33823.35万元2、总成本:29418.76万元3、净利润:3303.44万元4、财务内部收益率:12.17%5、财务净现值:15220.51万元6、回收期:4.86年(含建设期24个月)。

二、发展规划在半导体芯片项目和运营管理领域的研究中,发展规划是一个至关重要的环节。

一个完善的发展规划可以为企业未来的发展方向和目标提供清晰的指引,帮助企业在竞争激烈的市场中取得优势地位。

(一)市场分析与前景预测1、市场分析对目标市场进行全面细致的调研和分析,包括市场需求、竞争格局、行业趋势、政策法规等方面。

通过市场分析,可以深入了解市场环境,为后续决策提供依据。

2、前景预测基于市场分析结果,对未来市场发展进行预测,包括市场规模、增长速度、机会与挑战等方面。

芯片制造中的成本分析与降低策略芯片制造是现代科技领域中不可或缺的重要环节,它们广泛应用于电子设备、计算机、通信等各个领域。

然而,芯片制造的成本一直是制约其发展的重要因素之一。

本文将对芯片制造中的成本进行分析,并提出一些降低成本的策略。

一、直接成本分析芯片制造的直接成本主要包括材料成本、人工成本以及设备成本。

1. 材料成本材料成本占芯片制造总成本的很大比重。

在材料选择上,我们应该根据产品的要求和预算来选择合适的材料。

更高质量的材料通常会增加成本,但它们能提供更好的性能和稳定性。

因此,在选择材料时应该综合考虑性能和成本之间的平衡。

2. 人工成本芯片制造过程需要大量的人工操作,因此人工成本也是一个重要因素。

降低人工成本的策略可以是增加自动化程度,减少人工操作的需求。

引入先进的自动化设备和智能机器人可以有效提高生产效率,降低人力成本。

3. 设备成本芯片制造过程中需要采用各种设备,这些设备的成本也占据一定比例。

为了降低设备成本,可以考虑与设备供应商进行合作,租赁设备而不是购买,或在设备的使用寿命结束后进行二手设备的购买。

二、间接成本分析芯片制造中的间接成本包括能源消耗、维护费用、环境成本等。

1. 能源消耗芯片制造过程中需要大量的能源供应,包括电力、水等。

对于能源的合理利用可以帮助降低成本。

通过优化生产流程,降低能源消耗的浪费,如使用能效更高的设备和节能技术,可以有效降低能源成本。

2. 维护费用芯片制造中的设备需要定期的维护和保养。

定期维护可以延长设备寿命,减少故障率,降低维修和更换设备的费用。

另外,采用可靠的设备和材料也能够降低维护费用。

3. 环境成本芯片制造对环境的影响不可忽视,包括废水、废气等的处理和排放。

环境成本的降低可以通过优化环保设备、合理处理废弃物等方式来实现。

节约使用化学物品和减少污染物排放也是降低环境成本的有效途径。

三、降低成本的策略除了直接成本和间接成本的优化外,还有一些其他策略可以帮助降低芯片制造的成本。

ATE低成本解决方案迎接市场复苏

佚名

【期刊名称】《电子产品世界》

【年(卷),期】2003(000)07B

【摘要】随着半导体工艺的改进和集成度的进一步提高,无论是工业系统,还是半导体芯片的设计、制造,对于测试设备的需求都在急剧增长,但过去几年半导体工业经历了一个前所未有的严冬,产业链的各个环节不无例外地受到冲击。

由于各个厂商不断压缩开支,自动测试设备(ATE)厂商近几年多半是愁云满目,很少有开心。

倒是中国电子制造、以及半导体设计市场的红火,他这些厂商寄予很大希望。

【总页数】2页(P18,26)

【正文语种】中文

【中图分类】TN302

【相关文献】

1.定颖资本支出7亿新台币迎接PCB市场复苏 [J],

2.ATE低成本解决方案迎接市场复苏 [J],

3.ATE射频测试板低成本解决方案 [J], 孙佳焱

4.高安多手准备迎接市场复苏 [J], 邓小亮

5.迎接市场复苏推进数字化加工 [J], Jean—Louis MACEY

因版权原因,仅展示原文概要,查看原文内容请购买。

芯片样品成本管控方案1. 前言在半导体设计行业,产品样品是新产品推广的重要手段,同时也是开展业务的有力工具。

然而,样品制作所需要的材料和人力成本非常高昂,因此,如何管控样品成本,一直是半导体企业亟需解决的问题。

2. 成本分析要管控样品成本,首先需要对样品成本进行分析。

一般来说,芯片样品的成本由以下几部分组成:2.1 芯片设计费用芯片设计费用包括基础开发费用和难度系数费用,这部分成本在所有样品中是最大的。

2.2 材料成本芯片制造需要原材料,例如晶圆、掩膜、光刻胶等。

不同类型的芯片需要的原材料种类和数量不一样,因此,材料成本是根据不同类型的芯片而定的。

2.3 工艺费用芯片制造需要进行一系列工艺,如晶圆切割、芯片测试等,这些过程需要使用大量的设备和人力,因此同样是非常高昂的成本。

2.4 运输费用样品需要从设计厂商运到客户处,这部分成本包括物流费用和保险费用等。

3. 成本管控方案如何降低样品成本,将成本控制在需要的范围内?下面就针对以上成本分析,提出一些有效的管控方案。

3.1 设计费用控制设计费用是样品成本的主要组成部分之一,如果控制好设计费用,就可以有效地降低样品成本。

以下是几种可以控制设计费用的方案:•设计重复使用:对于已经设计好的芯片,可以重复使用设计方案,而不是重新设计,这可以节省很多设计费用。

•开发者合作:与开发者合作,建立长期合作关系,可以获得更优惠的设计报价。

3.2 材料成本控制材料成本通常是样品成本的第二大组成部分。

以下是几种可以控制材料成本的方案:•选取适当的材料:在芯片设计过程中,应当尽可能选取价格低廉的材料,这样可以降低材料成本。

•与供应商合作:与原材料供应商合作,可以获得更优惠的价格,并可以保证材料的质量。

3.3 工艺费用控制芯片制造的工艺费用是样品成本的第三大组成部分。

以下是几种可以控制工艺费用的方案:•自备测试系统:企业可以自己采购测试设备,这样可以在大规模生产之前对芯片进行测试,减少测试费用。

半导体封测建设内容一、半导体封测建设的必要性1.1 提高芯片可靠性半导体芯片在制造过程中可能会受到各种外界环境因素的影响,导致芯片内部存在着一些潜在隐患,如封装材料不良、焊接问题、线路接触不良等。

通过封测工艺,可以对芯片进行包装封装,同时对芯片进行严格测试,发现隐患并予以排除,从而提高芯片的可靠性和稳定性。

1.2 降低生产成本半导体芯片的封装和测试是整个芯片制造中的重要环节,它直接影响到芯片的成本和性能。

通过封测建设,可以将芯片的成本控制在合理范围内,同时提高生产效率和产品质量,降低生产成本。

1.3 提高产品竞争力随着半导体技术的不断进步,芯片制造技术也在不断更新换代,尤其在芯片封装和测试方面,新的技术和设备不断涌现。

通过封测建设,可以及时引进先进的封装和测试技术,提高产品的竞争力,满足市场需求。

1.4 促进产业升级半导体封测建设是半导体产业链上的一个重要环节,其发展水平直接影响到整个半导体产业的发展。

通过封测建设,可以促进产业升级,推动半导体产业向高端发展,提升国内半导体产业的整体水平。

二、半导体封测建设的主要技术和设备2.1 封测技术封测技术是指将半导体芯片进行封装,并对封装后的芯片进行功能测试和可靠性测试的技术。

封测技术的主要内容包括封装设计、封装材料、封装工艺、封装测试等。

封测技术的发展水平直接影响到芯片的性能和可靠性。

2.2 封测设备封测设备是指用于半导体芯片封装和测试的设备和工具。

封测设备的种类繁多,主要包括封装机、焊接机、测试机、打标机等。

这些设备的功能各不相同,但共同作用是对芯片进行封装和测试,确保芯片的正常工作。

2.3 封测工艺封测工艺是指封测过程中的具体步骤和操作规程。

封测工艺包括封装工艺、测试工艺、封测工艺流程等。

封测工艺的稳定性和可靠性对于芯片的成本和性能至关重要。

2.4 封测质量控制封测质量控制是指对封测过程中的各项指标和关键环节进行严格控制,确保封测产品符合质量标准。

半导体测试与可靠性深入了解半导体测试和可靠性方面的挑战和解决方案半导体技术在现代电子行业中起着至关重要的作用。

无论是我们日常生活中使用的各种电子设备,还是工业生产过程中所需的高性能芯片,都离不开半导体的应用。

而半导体的可靠性和测试是保证其正常运行的关键因素。

本文将深入探讨半导体测试和可靠性方面的挑战和解决方案。

一、半导体测试的挑战1.1 复杂多样的半导体器件半导体器件的种类繁多,每一种器件都有不同的测试需求。

例如,存储器、处理器、模拟器件等,它们的内部结构和功能不尽相同,需要不同的测试方法和设备来进行验证。

因此,针对每种器件的测试策略需要具体分析和设计,需求的多样性给测试带来了挑战。

1.2 高稳定性和高精度的测试环境半导体器件的测试要求在高稳定性和高精度的环境下进行。

温度、电压和湿度等因素会对测试结果产生影响,而这些因素的控制需要高精度的测试设备和稳定的测试环境。

在确保这些测试条件的前提下,获取精确可靠的测试结果也成为了挑战。

1.3 测试成本的压力半导体测试通常需要大量的人力、物力和设备投入,这导致测试成本居高不下。

特别是在新型半导体器件的测试过程中,由于其设计和制造都处于不断更新迭代的状态,测试技术的更新迭代也需要跟上步伐,这给测试成本带来了更大的压力。

二、半导体测试的解决方案2.1 先进的测试设备和技术应用随着科技的进步,半导体测试设备和技术不断更新迭代。

先进的测试设备能够满足更多样化的测试需求,同时提供更高精度和更稳定的测试环境。

例如,出现了多通道测试设备、高温高频测试设备等,它们能够更好地适应不同器件的测试需求。

此外,自动化测试技术的应用也提高了测试效率和可靠性。

2.2 优化测试流程和策略为了降低测试成本和提高测试效率,可以对测试流程和策略进行优化。

通过分析不同器件的特点和需求,制定合理的测试流程和策略,避免不必要的测试环节,从而提高测试效率。

同时,可以采用并行测试技术,同时测试多个器件,以减少测试时间和人力资源的浪费。

测试过程优化如何减少测试时间和成本测试是软件开发过程中至关重要的环节,它旨在确保软件的可靠性、质量和功能完善性。

然而,传统的测试方法存在一些问题,如测试时间长、成本高等。

因此,为了提高测试效率和减少测试成本,我们需要对测试过程进行优化。

本文将探讨几种测试过程优化的方法,旨在帮助软件开发者和测试人员更好地利用测试资源。

一、测试计划优化测试计划是测试过程中的关键一步,它规划了测试策略、测试范围和测试资源的分配。

优化测试计划可以减少测试时间和成本。

1.确定测试目标和优先级:在制定测试计划时,应明确测试的目标和重要性,并根据软件的功能、稳定性和安全性等方面确定测试的优先级。

通过合理设置测试目标和优先级,可以确保在有限的时间内优先测试最关键的功能和风险点,减少不必要的测试工作。

2.合理分配测试资源:根据测试目标和优先级,合理分配测试资源,包括测试人员、测试工具和测试环境等。

通过合理分配测试资源,可以避免资源浪费和测试冗余,提高测试效率和成本效益。

二、自动化测试工具的应用自动化测试工具可以大大提高测试效率和减少测试时间和成本。

三、测试用例优化测试用例是测试过程中的核心,它决定了测试的覆盖率和测试效果。

通过优化测试用例,可以减少测试时间和成本。

1.精简冗余测试用例:对于重复和相似的测试用例,可以通过合并或删除部分测试用例来减少测试时间和成本。

同时,应根据软件的功能和风险进行有效的测试用例设计,确保高覆盖率和高效率的测试。

2.有效选择测试数据:测试数据的选择对测试结果的准确性和测试时间的长短都有一定的影响。

因此,应根据软件的功能和风险选择合适的测试数据,并确保测试数据的全面性和多样性。

四、持续集成和自动化部署持续集成和自动化部署是测试过程优化的重要手段,它可以提高测试效率和减少测试时间和成本。

1.持续集成:通过使用持续集成工具,将开发人员的代码集成到共享代码库,并自动触发自动化测试。

持续集成可以及时发现和解决代码集成导致的问题,减少测试时间和成本。

芯片测试方案第1篇芯片测试方案一、前言随着半导体技术的飞速发展,芯片在各个领域的应用日益广泛。

为确保芯片产品的质量与可靠性,满足客户及市场需求,特制定本测试方案。

二、测试目标1. 确保芯片产品符合设计规范和功能要求。

2. 评估芯片在不同环境条件下的性能指标。

3. 发现并排除芯片在设计、制造过程中的潜在缺陷。

4. 为产品优化和改进提供依据。

三、测试范围1. 功能测试:验证芯片的基本功能是否正确。

2. 性能测试:评估芯片的性能指标是否符合设计要求。

3. 可靠性测试:检验芯片在规定条件下的可靠性。

4. 兼容性测试:验证芯片与其他相关设备的兼容性。

四、测试方法1. 功能测试:采用白盒测试和黑盒测试相结合的方法,对芯片进行全面的测试。

2. 性能测试:通过对比分析、模拟实验等方法,评估芯片性能指标。

3. 可靠性测试:采用高低温、振动、冲击等环境应力,检验芯片的可靠性。

4. 兼容性测试:通过与各类设备对接,验证芯片的兼容性。

五、测试流程1. 测试准备:收集相关资料,制定测试计划,搭建测试环境。

2. 测试执行:按照测试用例进行测试,记录测试结果。

3. 缺陷跟踪:对发现的缺陷进行分类、跟踪和反馈。

4. 测试报告:整理测试数据,编写测试报告。

5. 测试总结:分析测试结果,提出改进建议。

六、测试用例1. 功能测试用例:包括基本功能、边界条件、异常情况等。

2. 性能测试用例:包括处理速度、功耗、频率响应等。

3. 可靠性测试用例:包括高温、低温、振动、冲击等。

4. 兼容性测试用例:包括与其他设备接口、协议、驱动等的兼容性。

七、测试环境1. 硬件环境:提供符合测试需求的硬件设备。

2. 软件环境:搭建合适的操作系统、工具软件等。

3. 网络环境:确保测试过程中网络畅通。

八、测试人员1. 测试组长:负责测试方案的制定、测试任务的分配和监控。

2. 测试工程师:负责执行测试用例,记录和反馈测试结果。

3. 开发人员:协助解决测试过程中遇到的技术问题。

-32-

/2012.06/

是三元催化器堵塞或气门、活塞顶面有积

炭。

建议驾驶员进行喷油器、进气道、三元催化器免拆清洗。

经过清洗,用VAS5052测试,前氧传感器显示值和以前一样,怠速时后氧传感器显示值在0.12-0.7V之间变化,说明后氧传感器已经恢复正常。

清除故障码,OBD警告灯熄灭。

四、结束语

通过以上分析我们得出造成该车故障的主要原因是三元催化器堵塞,气门、活塞顶

面积炭,进行“二清”(即免拆清洗燃油系统、燃烧室与三元催化器,手工清洗节气门与进气道)后,清除故障码,此车行车过程中OBD警告灯点亮,同时出现发动机加速无力的故障便解决了。

通过排除此故障,我们得出今后再遇到行车时排气质量恶化或发动机缺火损坏三元催化器,导致OBD警告灯点亮或闪亮的情况,应利用OBD系统故障码和数据流进行诊断,对症修理,以提高维修效率并为顾客降低维修成本。

参考文献

[1]王永军.轿车车载诊断(OBD)系统核心技术研究[D].吉林大学,2007.

[2]陈鲁训,陈萍.第二代随车电脑诊断系统OBD II[J].汽车技术,1996(9):47-50.

[3]袁双宏.汽车OBD技术浅析[J].科技信息,2009(35).[4]徐建平.美国第二代及欧洲汽车微机故障诊断系统[J].汽车电器,2003(6):45-48.

[5]郭庆庆.上海大众帕萨特领驭OBD警告灯报警[J].汽车维修与保养,2012(2).

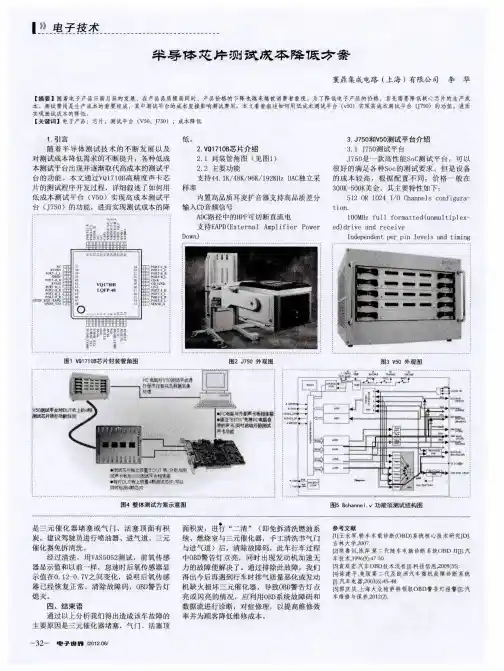

半导体芯片测试成本降低方案寰鼎集成电路(上海)有限公司 李 华

【摘要】随着电子产品日新月异的发展,在产品品质提高同时,产品价格的下降也越来越被消费者重视。

为了降低电子产品的价格,首先需要降低核心芯片的生产成本。

测试费用是生产成本的重要组成,其中测试平台的成本直接影响测试费用。

本文着重叙述如何用低成本测试平台(v50)实现高成本测试平台(J750)的功能,进而实现测试成本的降低。

【关键词】电子产品;芯片;测试平台(V50,J750);成本降低

1.引言

随着半导体测试技术的不断发展以及对测试成本降低需求的不断提升,各种低成本测试平台出现并逐渐取代高成本的测试平台的功能。

本文通过VQ1710B高精度声卡芯片的测试程序开发过程,详细叙述了如何用低成本测试平台(V50)实现高成本测试平台(J750)的功能,进而实现测试成本的降

低。

2.VQ1710B芯片介绍

2.1 封装管角图(见图1)2.2 主要功能

支持44.1K/48K/96K/192KHz DAC独立采样率

内置高品质耳麦扩音器支持高品质差分输入CD音频信号

ADC路径中的HPF可切断直流电

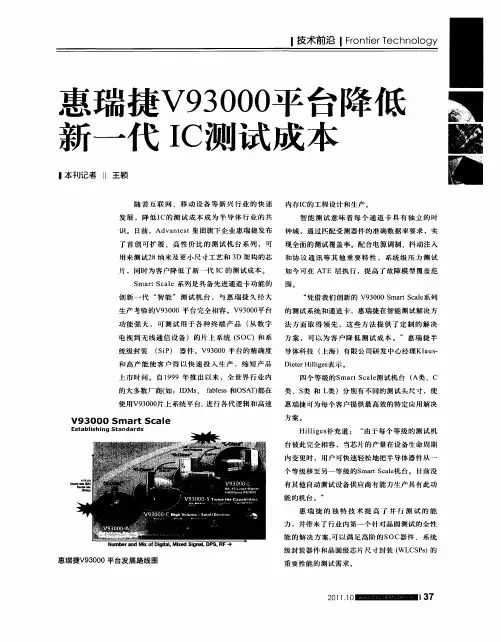

支持EAPD(External Amplifier Power Down) 3.J750和V50测试平台介绍3.1 J750测试平台

J750是一款高性能SoC测试平台,可以很好的满足各种Soc的测试要求。

但是设备的成本较高,根据配置不同,价格一般在300K-500K美金。

其主要特性如下:

512 OR 1024 I/O Channels configura-tion.

100MHz full formatted(unmultiplex-ed)drive and receive

Independent per pin levels and timing

图1 VQ1710B芯片封装管角图

图2 J750 外观图图3 V50 外观图

图4 整体测试方案示意图图5 8channel.v 功能项测试结构图

-33-

/2012.06

256 global time sets,32 per pin edge sets

6 edges per pin up to 50MHz,and 4 edges per pin up to 100MHz

3.2 V50测试平台介绍

V50是惠瑞杰旗下的一款多功能测试平台,可以测试数字类产品(测试频率低于50HZ),模拟类产品以及混合信号类产品,是中低端测试平台中性价比非常高的一款测试机,根据配置不同,价格一般在70K-150K 美金。

其主要特性如下:

Channel count:64 channels per logic board

Maximum 256 channels for one system Parallelism:maximum 8-site

Scalability:different kinds of the board can

Signal Docking:256 channel cable mount

4.芯片功能测试项

判断一颗芯片是良品还是不良品,都是

透过检测其功能项来进行判断。

如果所有的功能项均测试合格,则该芯片为良品。

若有一项不通过,则为不良品。

该芯片的功能测试项见表1。

由于文章篇幅的关系,以下着重介绍V50如何实现DA_PATH下的8Channel.v功能项(表一中的第10项)的测试。

该功能测试项主要是检测该声卡芯片8个音频输入输出通道通道是否正常。

5.V50测试方案

5.1 整体测试方案示意图(见图4)5.2 DA_PATH之8channel.v功能项测试结构图(见图5)

在测试该功能项之前,V50测试平台会通过测试程序将芯片上Poat A–H 8个音频输入输出通道通道打开,并且输入频率为1KHZ,振幅为±2V的正弦波,然后对输出波形进行采集,比较。

6.软件实现

6.1 软件流程图(见图6)6.2 软件程序(C语言)

***********以下为检测PortA通道的子程序***************

@@PLAN DA_PORT_A

SITE_SEQUENCE=OFF;

DISABLE_BY_MARK_NO=NULL; S_SETUP_FILE=c:\set.dat; REMARK=DA_PORT_A; DC_INIT(); CLEAR_CONT();

LOGIC_CLOSE_DPS_OUTPUT_RELAY(1,ON);

LOGIC_CLOSE_DPS_OUTPUT_RELAY(2,ON);// V50初始化

LOGIC_FORCE_DPS(1,2.97V,100MA,-100MA,E1,I7,VI_MODE);

LOGIC_FORCE_DPS(2,4.5V,100MA, -100MA,E1,I7,VI_MODE);// 开启芯片工作电压

LOGIC_CLOSE_PE_RELAY(DIGITAL_PINS); LOGIC_SET_DRV_LEVEL(DIGITAL_PINS, 3.3V, 0.0V, VR0);

LOGIC_SET_CMP_LEVEL(DIGITAL_PINS, 1.485V, 1.485V, VR0);// V50测试管角设置

LOGIC_CLOSE_USER_RELAY("29,24");// 开通PortA通道

WAIT(1MS); V50MesgToClient(DA_PORT_A);

RUN_PATTERN(B1_8CH_1121:start,B1_8CH_1121:end,1,5);//设置芯片工作模式并启动测试

V50MesgToClient(MSG_START_RE-CORD);// 记录,处理测试数据

WAIT(10MS);Sleep(1);

int R1 = V50GetViaResult( ); GB[1] = R1;

PRINT_LOG(GB2,GB2);// 调用比较软件,输出测试结果(Pass or Fail)

CONDITION IF_FAIL

REJECT_BIN=14;//根据测试结果,进行好坏品归类

@@END_PLAN

****************************************

7.结束语

通过本案的方案,测试平台的购置成本至少降低50%以上,大大缩减了测试成本。

同时希望更多的低成本平台可以实现更多高成本平台的功能,通过测试设备成本降低的方式缩减测试费用,从而降低产品成本,最终惠及终端用户。

参考文献

[1]刘恩科,朱秉升.半导体物理学[M].西安:西安交通大学出版社,1998.

[2]朱正涌.半导体集成电路[M].北京:清华大学出版社,2001.

[3]李亚伯.数字电路与系统[M].北京:电子工业出版社,2001.

[4]王毓银.数字电路逻辑设计[M].北京:高等教育出版社,1999.

[5]曹培栋,亢宝位.微电子技术基础[M].北京:电子工业出版社,2001

.

表1 芯片功能测试项列表

图6 软件流程图

图6 软件流程图。