电子科技大学集成电路原理实验集成电路图识别与提取王向展完整版

- 格式:docx

- 大小:1.18 MB

- 文档页数:8

数字集成电路版图设计与验证实验指导书电子科技大学微电子与固体电子学院实验名称数字集成电路版图设计与验证一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

该实验是正向设计中电路仿真完成之后、工艺制版之前的必须环节,与其他实验相结合,可以使学生对当前国际主流的IC设计技术流程有较完整的认识。

本实验是基于微电子技术应用背景和《微电子集成电路》课程设置及其特点而设置,为IC设计性实验。

其目的在于:•根据实验任务要求,综合运用课程所学知识自主完成相应的数字集成电路版图设计,掌握基本的IC版图布局布线技巧。

•学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的自动布局布线设计与验证。

通过该实验,使学生掌握数字专用集成电路版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力,掌握自主进行数字集成电路版图设计与验证的基本方法,进而为今后从事科研、开发工作打下良好基础。

二、实验原理2. 1 Cadence 环境的调入1、在UNIX 操作系统的Terminal窗口下→ cd user/userxxx/studname/Project→ icms& 或icfb&2、出现CIW(command Interpreter window)命令解释画面3、点选在CIW窗口的上面工具列Tools→Library Manager,会出现LM窗口LM(Library Manager)2. 2 建立新的Library1.点选LM窗口上面的工具列File→New→Library2.会产生New Library画面3.出现下图画面1.在name填上Library名称2.点选下面的OK4.出现Load Technology File窗口,添加工艺文件2.3 电路版图的自动布局布线2.3.1 启动Automatic Layout Tool1.打开已经设计完成的电路图Schemic2.点选 Tools --> Design Synthesis --> Device-Level Editor ,将弹出对话框,定义版图名,最好取与前面cell view 相同的名字。

实验报告课程名称:集成电路原理实验名称: CMOS模拟集成电路设计与仿真小组成员:实验地点:科技实验大楼606 实验时间: 2017年6月12日2017年6月12日微电子与固体电子学院一、实验名称:CMOS模拟集成电路设计与仿真二、实验学时:4三、实验原理1、转换速率(SR):也称压摆率,单位是V/μs。

运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。

2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。

3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。

4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。

5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

6、输出电压摆幅:一般指输出电压最大值和最小值的差。

图 1两级共源CMOS运放电路图实验所用原理图如图1所示。

图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。

M6、M7为二级放大电路,Cc为引入的米勒补偿电容。

其中主要技术指标与电路的电气参数及几何尺寸的关系:转换速率:SR=I5I I第一级增益:I I1=−I I2I II2+I II4=−2I I1I5(I2+I3)第二级增益:I I2=−I I6I II6+I II7=−2I I6I6(I6+I7)单位增益带宽:GB=I I2I I输出级极点:I2=−I I6I I零点:I1=I I6I I正CMR:I II,III=I II−√5I3−|I II3|(III)+I II1,III负CMR:I II,III=√I5I1+III5,饱和+I II1,III+I II饱和电压:III,饱和=√2I III功耗:I IIII=(I8+I5+I7)(I II+I II)四、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

实验报告课程名称:集成电路原理实验名称:模拟集成电路版图设计与验证小组成员:实验地点:科技实验大楼606实验时间:2017年6月19日2017年6月19日微电子与固体电子学院一、实验名称:模拟集成电路版图设计与验证二、实验学时:4三、实验原理1、电路设计与仿真实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。

2、工艺设计根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。

3、版图设计按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。

并优化版图结构。

四、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。

通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。

五、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。

3、整理版图生成文件,总结、撰写并提交实验报告。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、根据实验指导书掌握Cadence EDA仿真环境的调用。

熟悉版图编辑器Layout Editor的使用。

了解基本的布局布线方法及元器件的画法。

2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。

实验报告一、实验名称:集成电路版图识别与提取二、实验学时:4三、实验原理本实验重点放在版图识别、电路拓扑提取、电路功能分析三大模块,1、仔细观察芯片图形总体的布局布线,找出电源线、地线、输入端、输出端及其对应的压焊点。

2、判定此IC采用P阱还是N阱工艺;进行版图中元器件的辨认,要求分出MOS管、多晶硅电阻和MOS电容。

3、根据以上的判别依据,提取芯片上图形所表示的电路连接拓扑结构;复查,加以修正;完成电路的提取,并分析电路功能,应用Visio 或Cadence等软件对电路进行复原。

六、实验仪器设备(1)工作站或微机终端 1台(2)芯片显微图片 1张图11、观察芯片布局明确V DD、GND、V in1、V in2、V out、Test的压焊点。

2、根据V DD连接的有源区可以判断为PMOS管,根据比较环数推测出此IC采用了P阱工艺。

3、确定P阱工艺后,从输入端开始逐一对元器件及其连线进行辨认。

从输入端出来,直接看到在输入压焊点到输入管之间有一段多晶硅,但又无连线的“交叉”出现,排除了“过桥”的可能,初步判断为电阻,再根据其后的二极管可以判定为是与二极管组成保护电路最终与输入管相接,可断定是输入端起限流作用的电阻。

其中绿色圈标识有大片的多晶硅覆盖扩散区的区域判断为MOS电容。

图22、可见,实验图片为一个采用CMOS P阱工艺制造的放大器电路,该电路为典型的差分放大输入级。

由电路图可以看出,器件连接方式正确,逻辑上能完成确定的功能,说明提取结果是正确的。

3、整个实验过程是对IC逆向设计的尝试,IC逆向设计是IC设计的一条关键技术之一,一方面可借鉴并消化吸收先进、富有创意的版图步提取;由将二者提取的电路结合所学知识修改、完善,并最终确定电路;由用Cadence 软件搭建出所提取的电路,并完善布局;最后,由二者共同完成该实验报告。

报告评分:指导教师签字:。

电路识图9-集成电路的识图方法随着微电子技术的不断发展,各种无线电电子设备越来越多的使用了集成电路,集成电路符号也就越来越多的出现在各种电路图中。

由于电路图中一般不画出集成电路的内部电路,使得用集成电路构成的电路图不像分立元件电路图那样直观易读,因此,看懂含有集成电路的电路图需要掌握一些特殊的看图方法。

一、了解集成电路的基本功能集成电路往往都是电路图中各单元电路的核心,在单元电路中起着主要的作用。

从图面上看,某些单元电路就是由一块或几块集成电路再配以必须的外围元器件构成的。

要看懂这样的电路图,关键是了解和掌握处于核心地位的集成电路的基本功能,以此为突破口分析整个电路的工作原理。

集成电路的品种繁多,功能各异,特别是对于缺少资料和经验的电子爱好者来说,了解电路图中集成电路的功能并非易事。

但是,我们可以通过了解电路作用、查找资料、分析接口情况等方法,来搞清楚集成电路的基本功能。

1、根据单元电路所承担的任务,判断集成电路的基本功能一般而言,集成电路是单元电路的核心,单元电路的作用主要是依靠该集成电路来实现和完成的。

所以,根据单元电路所承担的任务和所起的作用,即可大致判断出在单元电路中起核心作用的集成电路的基本功能。

下面举例作进一步的说明,下图所示是以集成电路IC1为核心构成的一个单元电路,下图所示是某扩音机电路原理方框图,由图中可知该单元电路的作用和任务是对音频信号进行功率放大,因此,作为核心器件的集成电路IC1的基本功能是功率放大,IC1应该是一个集成功率放大器。

2、通过查找资料,了解集成电路的基本功能一般在较完整的电路图中,均会标注有各个集成电路的型号。

我们可以根据电路图提供的型号,通过查阅集成电路手册等技术资料,搞清楚这些集成电路的基本功能以及其它相关数据,这对于看懂集成电路电路图会有极大的帮助。

在上面介绍的功率放大单元电路中,集成电路IC1的型号是LM3886,通过查阅手册可以很清楚的了解到:LM3886是高性能集成功率放大器,频率响应范围5Hz~100kHz,输出功率50W,总谐波失真0.03%,具有过压、过载、超温保护功能和静噪功能,以LM3886为核心构成的音频功放单元电路具有很好的技术性能。

电子科技大学实验报告学生姓名:鄢传宗,梁成豪学号:2011031030010,2011031030009 指导教师:王向展实验地点:211楼307 实验时间:2014.5.28一、实验室名称:微电子技术实验室二、实验项目名称:逻辑IC功能和参数测试三、实验学时:4四、实验原理:1.MOSIC静态功耗(也称维持功耗)P DDMOSIC的静态功耗是:当输入端为固定的逻辑电乎,输出端空载,输出状态固定不变时电路所消耗的能量。

静态功耗是温度的函数。

由于静态时从电源到地没有直流通路,MOSIC静态功耗很小,它只取决于漏电情况。

2.输出高电平V OH(低电平V OL),输入高电平V IH(低电平V IL)(1)当输入端为固定的V CC或V SS,输出端空载时,所输出的固定电平称为输出高电平V OH及输出低电平V OL。

(2)当输出端维持应有的V OH和V OL时,输入端所能输入的最小高电平V IH或最大低电平V IL。

V OH(V OL)越接近V CC(V SS),V IH(V IL)越远离V CC(V SS),其电路性能越好。

3.逻辑功能和最高工作频率f MAX(1)先根据被测的IC应有的逻辑功能确定输入波形的时序,搭一个相应的测试电路产生这些输入波形并把共送入被测IC的输入端,用示波器或逻辑分析仪测试输入输出波形所对应的时序关系。

(2)最高工作频率f MAX取决于电路各级在动态工作中的充放电速度。

在额定的负载下,保持正确的逻辑关系和额定的波形幅度,电路所能承受的输入脉冲的频率为f MAX。

4.工作功耗P W静态功耗和动态功耗的总和为电路的工作功耗。

(1)动态功耗包括瞬态功耗P T和交变功耗P A。

其中P T是在动态工作中电源对电容(包括级间栅电容、pn结电容和输出级负载电容等)的充放电所消耗的能量。

(2)P A是由于在交变时波形的上升沿和下降沿使得电路从V CC到V SS有直流通路而消耗的能量。

(3)动态功耗是无法单独测试的,而对于CMOS电路由于P DD很小,因此(4)在固定负载情况下它与工作频率成正比,在固定工作频率时,它与负载电容成正比。

实验33 模拟集成电路版图的反向提取模拟集成电路具有设计难度大、应用范围宽等优点,早已成为了集成电路设计领域的重要研究热点,引起了研究者的广泛关注。

模拟集成电路版图的反向提取关乎电路设计的成败,是设计过程中的重要关键环节之一。

本实验要求学生能够独立对标准CMOS模拟集成电路版图单元,完成电路的反向提取、绘制整理和功能分析等工作。

通过对CMOS模拟集成电路版图单元的反向提取实践,锻炼和提高学生对集成半导体器件和模拟集成电路版图的认知能力和对电路整理与结构优化技能,培养学生对模拟集成电路反向设计思想的理解,加强学生灵活运用所学《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等理论知识的能力。

一、实验原理1. 模拟集成电路中的集成器件在标准CMOS工艺下,模拟集成半导体器件主要有:MOS晶体管、扩散电阻、多晶硅电阻、多晶硅电容和MOS电容等。

在P型衬底N阱CMOS工艺条件下,NMOS器件直接制作在衬底材料上,PMOS器件制作在N阱中。

在模拟集成电路中,MOS晶体管常常工作在线性区或饱和区,需要承受较大的功耗,这些晶体管具有较大的宽长比。

模拟集成电路版图常常不规则,这就要求在电路提取时要充分注意电路连接关系。

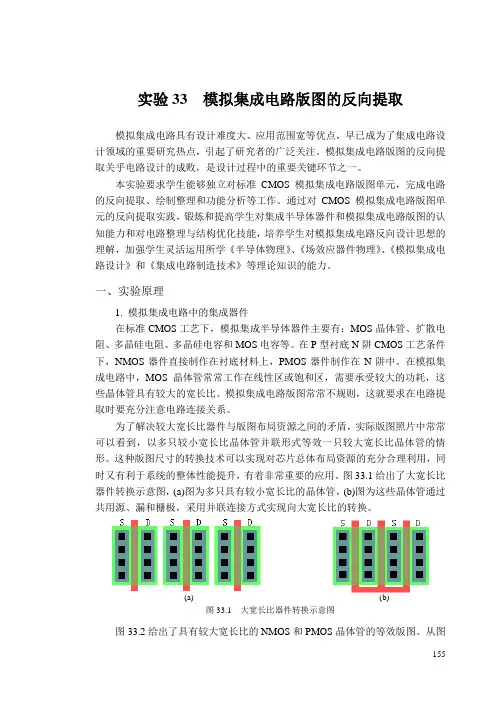

为了解决较大宽长比器件与版图布局资源之间的矛盾,实际版图照片中常常可以看到,以多只较小宽长比晶体管并联形式等效一只较大宽长比晶体管的情形。

这种版图尺寸的转换技术可以实现对芯片总体布局资源的充分合理利用,同时又有利于系统的整体性能提升,有着非常重要的应用。

图33.1给出了大宽长比器件转换示意图,(a)图为多只具有较小宽长比的晶体管,(b)图为这些晶体管通过共用源、漏和栅极,采用并联连接方式实现向大宽长比的转换。

(a) (b)图33.1 大宽长比器件转换示意图图33.2给出了具有较大宽长比的NMOS和PMOS晶体管的等效版图。

从图155中可以看出,NMOS和PMOS晶体管都是由四只晶体管并联组成的,由于源极、漏极和栅极分别接在一起,所以晶体管从漏极流向源极的电流具有四条路径,那么,作用结果相当于四倍宽长比的单只晶体管。

集成电路设计综合实验报告班级:微电子学1201班姓名:学号:日期:2016年元月13日一.实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二.实验内容1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

2. 设计一个CMOS结构的二选一选择器。

(1)根据二选一选择器功能,分析其逻辑关系。

(2)根据其逻辑关系,构建CMOS结构的电路图。

(3)利用EDA工具画出其相应版图。

(4)利用几何设计规则文件进行在线DRC验证并修改版图。

三.实验原理1. 反向提取给定电路模块方法一:直接将版图整体提取(如下图)。

其缺点:过程繁杂,所提取的电路不够直观,不易很快分析出其电路原理及实现功能。

直接提取的整体电路结构图方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。

其优点:使电路结构更简洁直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。

CMOS反相器模块CMOS反相器的symbolCMOS传输门模块 CMOS传输门的symbolCMOS三态门模块 CMOS三态门的symbolCMOS与非门模块 CMOS与非门的symbol各模块symbol按版图连接方式组合而成的整体电路经分析可知,其为一个带使能端的D锁存器,逻辑功能如下:①当A=1,CP=0时,Q=D,Q—=D—;②当A=1,CP=1时,Q、Q—保持;③当A=0,Q=0,Q—=1。

2.CMOS结构的二选一选择器二选一选择器(mux2)的电路如图所示,它的逻辑功能是:①当sel=1时,选择输入A通过,Y=A;②当sel=0时,选择输入B通过,Y=B。

二选一选择器(mux2)由三个与非门(nand)和一个反相器(inv)构成(利用实验1 的与非门和反相器symbol即可)。

电子科大集成电路原理实验报告-CMOS模拟集成电路设计与仿真标准实验报告电子科技大学微电子与固体电子学院集成电路原理与设计CMOS模拟集成电路设计与仿真电子科技大学实验报告实验地点:211楼606 实验时间:2014.6.7一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理参照实验指导书。

五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60?,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网2(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

具体计算步骤如下:(参见模拟CMOS集成电路设计)1. 通过额定功耗和片外电容C计算偏置电路电流以及流进M6,M8电流,再通过相关试验得到相关pmos,nmos的Vth和k和λ,得到m6,m8,m9宽长比并计算密勒电容Cc2. 通过cmr计算m4和m0的宽长比3. 通过GB和Cc求出m2和m5宽长比4. 由m6,m8的Ids电流计算m7宽长比5. 进行电路仿真,观察电路是否符合各方面要求。

title电子技术实验基础(一:电路分析)(电子科技大学)中国大学mooc答案100分最新版content实验1-1 常用电子测量仪器的使用——数字示波器的使用数字示波器的使用单元测试题1、如图所示示波器的面板旋钮中,标出哪个按键是垂直通道的菜单按键A:AB:BC:CD:D答案: A2、如图所示示波器的面板旋钮中,标出哪个旋钮是水平通道的位移旋钮A:AB:BC:CD:D答案: C3、若被测试的信号是交直流叠加信号,示波器的垂直耦合方式应该选择哪一挡A:AC耦合B:DC耦合C:接低耦合D:AC、DC均可答案: DC耦合4、如图所示示波器的探头,测试信号时,探头应该与测试端应如何连接A:探勾接信号端钮,黑色鳄鱼夹接地B: 探勾接地,黑色鳄鱼夹接信号端钮C: 可以任意连接D:以上均不正确答案: 探勾接信号端钮,黑色鳄鱼夹接地5、如下图所示第四个菜单栏中,如果测量时发现该菜单栏显示不是电压1X,而是电压10X,应该调节哪个按键或旋钮使其为电压1XA:旁边的按键切换选择B:VARIABLE旋钮C:AUTOSETD:关机重启答案: VARIABLE旋钮6、下图是所示是示波器探头的手柄阻抗拨动开关细节图,若手柄放在1X端,垂直菜单栏中第四栏应怎么调节?若手柄放在10X端,又该怎样调节?A:电压1X、电压10XB:电压10X、电压1XC:电压1X、电压1XD:任意选择不影响结果答案: 电压1X、电压10X7、如图所示示波器的显示屏上,哪个标示的是通道1的零基线位置A:AB:BC:CD:D答案: C实验1-2 常用电子测量仪器的使用——函数发生器和晶体管毫伏表的使用函数发生器和晶体管毫伏表单元测验1、信号源输出周期信号时频率显示如图所示,当前输出信号的频率是多少?A:1HzB:10HzC:1KHzD:10KHz答案: 1KHz2、信号源给后级网络提供正弦信号,如果信号源幅度显示窗口显示如图所示,表明现在后级网络得到的信号电压大小是?A:不确定B:电压峰值是111mVC:电压峰峰值是111mVD:电压有效值是答案: 不确定3、下列说法正确的是?A: 数字万用表可以测量函数发生器输出信号中的直流分量B: 函数发生器只用“输出幅度调节”旋钮进行幅度调节C:函数发生器可用“直流偏移”旋钮输出直流电压信号D:函数发生器输出信号电压的最大值和最小值之间相差60dB答案: 数字万用表可以测量函数发生器输出信号中的直流分量4、列说法正确的是?A:毫伏表是用来测量包括直流电压在内的电压值的仪表B:使用毫伏表测量正弦信号的有效值时需要考虑正弦信号的频率C:毫伏表和万用表作为交流电压表都可以测量正弦信号的有效值,在没有毫伏表时,可以临时用万用表替代D:三角波信号和方波信号不能送入毫伏表测量答案: 使用毫伏表测量正弦信号的有效值时需要考虑正弦信号的频率5、某个正弦交流信号的有效值是0.8V,毫伏表应选择哪一档进行测量?A:10VB:3VC:1VD:300mV答案: 1V实验2 正弦稳态时RLC元件电压电流相位关系的测试正弦稳态时RLC元件电压电流相位关系的测试1、采用课程实验方案测量电感元件的电压电流相位关系时,为了获得近似90°的电压、电流波形相位差,信号源的频率应:A:适当增大信号源的频率;B:适当减小信号源的频率;C:调节信号源的频率不会影响相位差的测试;D:以上措施都不会改善测量结果答案: 适当增大信号源的频率;2、采用课程实验方案测量电容元件的电压电流相位关系时,示波器测量波形如图所示,下面哪种说法正确:A:CH1通道为取样电阻的电压信号, CH2通道为信号源信号;B:CH1通道为信号源信号, CH2通道为取样电阻的电压信号;C:CH2通道为电容元件的电压信号, CH1通道为取样电阻的电压信号;D:无法判断答案: CH1通道为信号源信号, CH2通道为取样电阻的电压信号;3、测量示波器相位差时显示的两路波形如图所示,为了能正确测量,应适当调节面板中哪个旋钮:A:A;B:B;C:C;D:D答案: A;4、测量示波器相位差时显示的两路波形如图所示,为了减小读数误差,需要适当应适当调节面板中哪个旋钮 :A:A;B:B;C:C;D:D答案: D5、采用课程实验方案正确测量元件的电压电流相位关系时,示波器测量波形如图所示,由此可以判断当前测试的是哪种元件:A:电感;B:电容;C:电阻;D:无法判断答案: 电阻;实验3 一阶RC电路频率特性研究一阶RC电路频率特性研究1、关于一阶RC低通滤波器的截止频率fc,如下描述中哪一项是正确的?A:电阻保持不变,减小电容值, fc降低B:电阻保持不变,增大电容值, fc降低C:截止频率处的输出电压是最大输出电压的50%D:低通滤波器的带宽是fc ~∞答案: 电阻保持不变,增大电容值, fc降低2、根据一阶RC低通滤波器的相频特性公式,随着频率从低到高,相位差的正确变化规律是:A:从0°~ -90°B:从0°~90°C:从-45°~+45°D:从0°~-180°答案: 从0°~ -90°3、测试低通滤波器的幅频特性曲线时,此处假设截止频率是大于500Hz的,如下哪种说法不正确:A: 测试过程中保持电路的输入信号幅度一致B:在大于20Hz的较低频率处找到最大输出电压后,再以此为参照开始测试C: 以输入电压为参照,调节频率至输出电压下降3dB就是截止频率D:在各个频率点测试时,应当保证测试输出电压的毫伏表的指针偏转超过刻度线的⅓答案: 以输入电压为参照,调节频率至输出电压下降3dB就是截止频率。

电子科技大学集成电路实验报告――模拟集成电路CMOS模拟集成电路设计及HSPICE使用实验学时:4学时实验一CMOS工艺参数测量一、实验目的:学习和掌握EDA仿真软件Hspice;了解CMOS工艺技术及元器件模型,掌握MOSFET工作原理及其电压电流特征;通过仿真和计算,获得CMOS中NMOS和PMOS的工艺参数kp,kn, p, n,Vtp,Vtn,为后续实验作准备。

二、实验内容:1)通过Hspice仿真,观察NMOS和PMOS管子的I-V特性曲线;2)对于给定长宽的MOSFET,通过Hspice仿真,测得几组栅-源电压、漏-源电压和漏-源电流数据,代入公式IDSn1WKn()n(VGS Vtn)2(1 nVDS),求得对应的工艺参数2Lkp,kn, p, n,Vtp,Vtn 。

三、实验结果:本实验中所测试的NMOS管、PMOS管L=1u,W由学号确定。

先确定W。

W等于学号的最后一位,若学号最后一位=0,则W=10u。

所以,本实验中所测试的NMOS管、PMOS管的尺寸为:(1)测0.5um下NMOS和PMOS管的I-V特性曲线所用工艺模型是TSMC 0.50um。

所测得的Vgs=1V时,NMOS管Vds从0V到2.5V变化时的I-V特性曲线为:所测得的Vds=1.2V时,NMOS管Vgs从0V到2.5V变化时的I-V特性曲线为:所测得的Vsg=1V时,PMOS管Vsd从0V到2.5V变化时的I-V特性曲线为:所测得的Vsd=1.2V时,PMOS管Vsg从0V到2.5V变化时的I-V特性曲线为:(2)计算TSMC 0.50um工艺库下mos管对应的工艺参数测试NMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:NOMS I-V Characteristic M1 OUT IN 0 0 CMOSn L=1U W=8U VIN IN 0 1 VOUT OUT 0 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2 .PRINT DC I(M1).LIB “C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的NMOS管电流曲线为:所测的数据如下表:根据公式IDSn1Kn()n(VGS Vtn)2(1 nVDS),计算kn, n,Vtn,分别为:2Lkn 119 10-6, n 0.028,Vtn 1.37测试PMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:POMS I-V CharacteristicM1 OUT IN Vdd Vdd CMOSP L=1U W=8UVIN Vdd IN 1 VOUT Vdd OUT 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M2).LIB "C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的PMOS管电流曲线为:所测的数据如下表:计算TSMC 0.50um 工艺中pmos 参数pptp,分别为:Kp 54.89 10-6, p 0.017,Vtp 0.927综上所述,可得:四、思考题2)不同工艺,p, n不同。

集成电路设计综合实验学院:专业:学号:姓名:日期:实验一:反向提取给定模块一、实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二、实验内容1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

图1 电路模块版图三、实验步骤1.按照(如上图1所示)提取电路图2.将提取的电路图用模块符号绘制连接起来并分析其逻辑功能3.在cadence软件创建schematic文件并绘制各子模块电路原理图4.结合原理图的功能分析仿真波形是否正确5.由schematic产生symbol6.再在cadence软件创建schematic文件并调用子模块symbol并将其各个模块连接起来构成电路原理图7.进行仿真分析其波形是否正确8.在cadence软件创建layout文件,严格按照工艺规则绘制电路版图并尽可能保证距离最小9.进行DRC验证四.实验原理经过对提取出来的电路图的分析,该电路的功能为D锁存器,输入信号A为D锁存器的CLK时钟端口,输入信号B为D锁存器的输入信号D端口,输入信号C为D锁存器的使能端E0口,输出信号Q为D锁存器的输出信号。

锁存器是一种对脉冲电平敏感的存储单元电路,他们可以在特定输入脉冲电平作用下改变状态。

当时钟信号为低时,传输管截止,数据通过三态门经反馈线和与非门后输出;当时钟信号为高时,三态门截止,输出为锁存状态,就是把信号暂存以维持某种电平状态。

该D锁存器的功能是,当使能端E0为低时,电路不工作,输出为低;当使能端E0为高时,并且CLK时钟信号为低时,输出信号与输入信号B一致;当使能端E0为低时,并且CLK时钟信号为高时,输出为锁存状态,即把上一个状态暂存起来。

D锁存器真值表五.实验结果:反向提取的schematic电路图即symbol的绘制反向器的symbol电路图和版图的绘制传输门的电路图symbol和版图的绘制与非门的电路图symbol和版图的绘制三态门的电路图symbol的绘制D锁存器的模块电路图的绘制D锁存器的模块电路图的仿真波形D锁存器DRC验证后版图的绘制实验二:二选一数字选择器一、实验内容设计一个CMOS结构的二选一选择器。

实验32 数字集成电路版图的反向提取实验32 数字集成电路版图的反向提取数字集成电路产品应用领域十分广泛,数字集成电路的设计技术日新月异。

集成电路反向设计是一种重要的集成电路设计技术,数字集成电路版图的反向提取是数字集成电路反向设计过程中的重要关键环节之一。

本实验要求学生能够独立对标准CMOS数字集成电路版图,完成电路的反向提取、绘制整理和功能分析等工作。

通过对CMOS数字集成电路版图的反向提取实践,锻炼并提高学生对集成半导体器件与数字集成电路版图的认知能力和对电路整理与结构布局的优化能力,培养学生对数字集成电路反向设计思想的理解,加强学生灵活运用所学《半导体物理》、《场效应器件物理》、《数字集成电路设计》和《集成电路制造技术》等理论知识的能力。

一、实验原理1. 标准CMOS工艺简介在现代集成电路工艺技术中,CMOS工艺技术占据重要位置,得到了广泛的应用。

P型衬底N阱CMOS工艺的主要工艺技术包括有:氧化技术、光刻技术、刻蚀技术、离子注入技术和淀积技术等。

各种工艺技术交替多次出现,达到了对半导体器件和集成电路图形的逐层加工处理。

最终形成了图形化的半导体器件和集成电路实体。

氧化技术用于生长氧化层,包括干氧、湿氧等主要方法,氧化层主要用于栅绝缘介质、杂质掩蔽和隔离保护等。

光刻技术是通过紫外光或电子束对涂有光致抗蚀剂的半导体材料进行照射,利用光致抗蚀剂在照射前后溶解性的变化,实现光刻掩膜版到半导体材料上的图形转移,为后续加工工艺开设有用窗口。

刻蚀技术是采用化学或物理的方法对一定区域的材料进行腐蚀或销蚀的技术,是实现对多余无用材质进行去除的一项技术。

离子注入是通过加速杂质离子并将杂质离子打入靶体材料的一种掺杂技术。

可以实现P型和N型杂质的掺入。

淀积技术是通过物理化学方法在基片上生长材料薄层的一种技术。

可以实现多晶硅栅等材料的生长。

2. 集成半导体器件认知标准CMOS工艺下的集成半导体器件主要有NMOS晶体管、PMOS晶体管、多晶硅电阻和多晶硅电容等。

电子科技大学集成电路原理实验集成电路图识别与提取王向展

HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

实验报告

课程名称:集成电路原理

实验名称:集成电路版图识别与提取

小组成员:

实验地点:科技实验大楼606 实验时间: 2017年5月22日

2017年5月22日

微电子与固体电子学院

一、实验名称:集成电路版图识别与提取

二、实验学时:4

三、实验原理

本实验重点放在版图识别、电路拓扑提取、电路功能分析三大模块,实验流程如下:

四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC 设计性实验。

其目的在于:

了解对塑封、陶瓷封装等不同封装形式的芯片解剖的方法及注意事项。

学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

能对提取得到的电路进行功能分析、确定,并可运用PSPICE 等ICCAD 工具展开模拟仿真。

五、实验内容

1、仔细观察芯片图形总体的布局布线,找出电源线、地线、输入端、输出端及其对应的压焊点。

2、判定此IC采用P阱还是N阱工艺;进行版图中元器件的辨认,要求分出MOS 管、多晶硅电阻和MOS电容。

3、根据以上的判别依据,提取芯片上图形所表示的电路连接拓扑结构;复查,加以修正;完成电路的提取,并分析电路功能,应用Visio或Cadence等软件对电路进行复原。

六、实验仪器设备

(1)工作站或微机终端 1台

(2)芯片显微图片 1张

(3)版图编辑软件 1套

七、实验步骤

实验所要提取的电路显微图片如图1所示。

图1

1、观察芯片布局明确V

DD 、GND、V

in1

、V

in2

、V

out

、Test的压焊点。

2、根据V

DD

连接的有源区可以判断为PMOS管,根据比较环数推测出此IC采用了P阱工艺。

3、确定P阱工艺后,从输入端开始逐一对元器件及其连线进行辨认。

从输入端出来,直接看到在输入压焊点到输入管之间有一段多晶硅,但又无连线的“交叉”出现,排除了“过桥”的可能,初步判断为电阻,再根据其后的二极管可以判定为是与二极管组成保护电路最终与输入管相接,可断定是输入端起限流作用的电阻。

其中绿色圈标识有大片的多晶硅覆盖扩散区的区域判断为MOS电容。

4、因已确定为P阱工艺,则阱和保护环内的器件为NMOS管,由图1可见,两输入管共源,且源与P阱相接,并与另一个N管的漏相接,该N管的源极与GND相接,意味着阱电位是浮动的,这是为了消除输入管衬底偏置效应采取的措施。

两输入管的漏极分别与另外两个P管的漏相接,这两个P管的源和衬底相连并与正电源连接,且其中一个P管的栅源短接,说明这两个P管构成了电流镜。

5、图1红线左边剩余电路分析得知是一个偏置电路和多级电流镜结构。

红线右边分析得出是带有偏置的具有高度对称的AB类输出级结构。

6、结合差分运放和输出级等各个基本电路结构的知识点,对电路结构进行逻辑上的排查,修正。

7、在版图编辑软件Cadence上完成电路图。

八、实验数据及结果分析

对实验所提取的电路认真分析,最终所得的电路图如图2所示。

图2

2、可见,实验图片为一个采用CMOS P阱工艺制造的放大器电路,该电路为典型的差分放大输入级。

由电路图可以看出,器件连接方式正确,逻辑上能完成确定的功能,说明提取结果是正确的。

3、整个实验过程是对IC逆向设计的尝试,IC逆向设计是IC设计的一条关键技术之一,一方面可借鉴并消化吸收先进、富有创意的版图设计思路、结构,建立自己的版图库;另一方面通过分析、优化已有版图可将原有芯片的性能加以改进提高。

目前逆向设计在通用类IC和某些低端产品的研发方面尚具有十分重要的意义。

九、实验心得与体会

在这次实验中,通过版图中元件的识别与适当的猜测,然后结合自己所学知识,还原相应电路;同时也提高了自己在绘制版图时的布局能力,为实验三“模拟集成电

路版图设计与验证”打下了基础。

最重要的是让自己见识了电路版图的艺术,虽然整个版图电路提取过程枯燥乏味,但让我们感受将来读研究生或从事相关工作时的学习、工作氛围,也给自己敲醒了警钟,将来的研究生、工作生涯将不再是本科那般简单轻松,现在就应该端正自己的学习态度,才能让自己将来即使有所失,也能有所得。

十、实验分工

版图提取过程中,两人共同讨论、分析,并同时各自完成电路的初步提取;

由将二者提取的电路结合所学知识修改、完善,并最终确定电路;

由用Cadence 软件搭建出所提取的电路,并完善布局;

最后,由二者共同完成该实验报告。

报告评分:

指导教师签字:。