设计逻辑信号电平测试器的设计

- 格式:doc

- 大小:462.00 KB

- 文档页数:17

滁州学院之宇文皓月创作课程设计陈述课程名称:数字逻辑课程设计设计题目:数字频率计的设计系别:网络与通信工程系专业:网络工程组别:第四组起止日期:2012年5月28日~ 2012年6月 22日指导教师:计算机与信息工程学院二○一二年制课程设计任务书目录1 引言12 设计要求12.1题目12.2系统结构要求12.3制作要求12.4扩展指标12.5运行环境12.6设计条件12.7元件介绍2①计数显示器2② 74160N3③ 7473N4④ XFG143 整体设计方案54 详细分析64.1单元电路设计6 4.2控制电路64.3关于JK触发器7 4.4测试85 调试与操纵说明85.1第一次仿真95.2第二次仿真95.3第三次仿真10 5.4第四次仿真106 课程设计总结117 致谢118 参考文献121 引言数字频率计是近代电子技术领域的重要丈量工具之一,同时也是其他许多领域广泛应用的丈量仪器。

数字频率计是在基准时间内把丈量的脉冲数记录下来,换算成频率并以数字的形式显示出来。

数字频率计应用于丈量信号(方波、正玄波或其他周期信号)的频率,并用十进制数显示。

它具有精度高、丈量速度快、读数直观、使用方便等优点。

2 设计要求2.1题目频率计主要用于丈量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。

其扩展功能可以丈量信号的周期和脉冲宽度。

①频率丈量范围:1HZ~10HZ。

②数字显示位数:四位静态十进制数显示被测信号的频率。

2.2系统结构要求数字频率计的整体结构要求如图所示。

图中被测信号为外部信号,送入丈量电路进行处理、丈量,档位转换用于选择测试的项目—频率、周期或脉宽,若丈量频率则进一步选择档位2.3制作要求①被测信号波形:正弦波、三角波和矩形波。

②丈量频率范围:1Hz~10kHz。

③丈量周期范围:0.1ms~1s。

④丈量脉宽范围:0.1ms~1s。

⑤丈量精度:显示4有效数字(要求分析1Hz、1kHz和10kHZ丈量误差)。

逻辑测试笔的制作与调试74LS00介绍逻辑测试笔是一种用来测试数字电路中逻辑高低电平的工具。

通过简单的电路设计和调试,我们可以使用逻辑测试笔来检测逻辑芯片的工作状态和信号传输。

在本文中,我们将讨论如何制作一个逻辑测试笔并使用它来测试74LS00芯片的逻辑电平。

材料准备•一根铜导线•一颗LED光敏二极管•一颗220欧姆电阻•一根插头•焊接工具•电线剥皮工具下面是制作逻辑测试笔的步骤:步骤1:准备工作收集所需材料,并保证工作场所清洁整齐。

步骤2:准备LED光敏二极管通过电线剥皮工具剥开LED光敏二极管的两端,将一端与导线连接,并使用焊接工具焊接在一起。

步骤3:连接电阻将220欧姆电阻与另一端的导线连接,并使用焊接工具焊接在一起。

步骤4:连接插头将导线和电阻的另一端与插头连接,并使用焊接工具进行焊接。

步骤5:固定线缆使用胶带或其他方式固定逻辑测试笔的线缆。

在制作完成逻辑测试笔后,我们需要进行调试以确保其正常工作。

下面是调试逻辑测试笔的步骤:步骤1:连接电源将逻辑测试笔的插头插入电源的负极,确保笔的LED灯亮起。

步骤2:测试高电平将逻辑测试笔的导线连接到电路板的高电平引脚上。

如果LED灯亮起,则表示该引脚处于高电平状态。

步骤3:测试低电平将逻辑测试笔的导线连接到电路板的低电平引脚上。

如果LED灯不亮,则表示该引脚处于低电平状态。

步骤4:测试未知状态将逻辑测试笔的导线连接到电路板中的未知引脚上。

如果LED灯闪烁,则表示该引脚处于未知状态。

注意事项•在使用逻辑测试笔进行测试时,务必确保电路板处于断电状态。

•在测试未知状态时,要特别注意观察LED灯的闪烁情况,并与芯片的数据手册进行对照。

结论通过制作和调试逻辑测试笔,我们可以方便地测试数字电路中的逻辑高低电平。

使用逻辑测试笔可以帮助工程师确保电路的正常运行,并进行故障诊断和调试。

制作一个逻辑测试笔不仅简单,而且成本很低,非常适合电子爱好者和工程师使用。

希望本文对你有所帮助!以上就是关于制作和调试逻辑测试笔并使用它来测试74LS00芯片的逻辑电平的说明文档。

一、实验名称逻辑电路实验二、实验目的1. 掌握基本的数字逻辑电路设计方法。

2. 理解并掌握常用的逻辑门及其组合电路。

3. 提高实验操作技能和观察能力。

4. 培养团队协作精神。

三、实验原理数字逻辑电路是构成数字系统的基本单元,主要由逻辑门、触发器等基本元件组成。

逻辑门是数字电路的基本单元,它按照一定的逻辑规则实现基本的逻辑运算。

本实验主要涉及以下逻辑门及其组合电路:1. 与门(AND):当所有输入信号都为高电平时,输出信号才为高电平。

2. 或门(OR):当至少一个输入信号为高电平时,输出信号才为高电平。

3. 非门(NOT):将输入信号取反。

4. 异或门(XOR):当输入信号不同时,输出信号为高电平。

四、实验器材1. 逻辑门实验板2. 逻辑笔3. 万用表4. 逻辑分析仪5. 示波器6. 计时器五、实验内容1. 与门、或门、非门、异或门的逻辑功能测试2. 组合逻辑电路设计3. 电路仿真与验证六、实验步骤1. 与门、或门、非门、异或门的逻辑功能测试(1)按照实验指导书,连接与门、或门、非门、异或门实验板。

(2)使用逻辑笔和万用表,测试各个逻辑门的输入、输出信号。

(3)记录测试结果,与理论值进行对比,分析实验误差。

2. 组合逻辑电路设计(1)根据设计要求,选择合适的逻辑门,绘制电路图。

(2)使用实验板,搭建组合逻辑电路。

(3)测试电路功能,验证设计是否正确。

3. 电路仿真与验证(1)使用逻辑分析仪或示波器,观察电路的输入、输出信号波形。

(2)分析波形,验证电路功能是否符合预期。

七、实验结果与分析1. 与门、或门、非门、异或门的逻辑功能测试实验结果如下:与门:当所有输入信号都为高电平时,输出信号才为高电平。

或门:当至少一个输入信号为高电平时,输出信号才为高电平。

非门:将输入信号取反。

异或门:当输入信号不同时,输出信号为高电平。

2. 组合逻辑电路设计(1)设计一个4位二进制加法器,包括两个输入端(A、B)和两个输出端(S、C)。

实验十二基于Multisim的逻辑电平测试器设计一、实验背景许多电子应用中都会用到逻辑电平测试器,它可以用来判断门电路在不同电平时状态的变化。

本文介绍如何使用Multisim软件中的电路模拟软件来设计一种逻辑电平测试器。

二、实验原理逻辑电平测试器是用来测试绝缘口路灯(IOL)的输出状态的设备。

通过输入不同的电平,可以检测出芯片与控制信号灯的输出结果。

逻辑电平测试器拥有两个输入,一个为电压信号,另一个为相应的高/低电平信号。

电压和信号电平输入到逻辑网络,通过与电压进行比较,可以从IOL得到需要的结果。

三、实验步骤1. 使用Multisim软件新建一个电路图,拖动几个重要电路元件,包括:(1)一个用于输入电压信号的源;(2)一个用于输入高/低信号的源;(3)一个用于比较信号的比较器;(4)一个用于显示输出结果的7段LED显示(或是其他形式的显示);(5)一个绝缘口路灯(IOL);(6)一个用于驱动IOL的控制信号灯。

2. 连接电路元件,完成电路连接。

注意,比较器的两个输入端与电压源及电平信号源都需要连接;比较器输出结果将用来驱动IOL及7段LED显示,因此,比较器输出端要分别连接IOL及7段LED显示。

3. 7段LED显示及IOL的输出应满足如下规则:当输入的信号电平高于设定的电压时,则7段LED显示为“1111”,IOL的电流状态为高;当输入的信号电平低于设定的电压时,则7段LED显示为“0000”,IOL的电流状态为低。

4. 在电路图上调整参数,设置信号源,同时将电压及信号源作为Simulation对象,开始对电路进行模拟,观察结果是否正确,调整参数使画得正确结果。

四、实验结果实验中,我们设计了一个逻辑电平测试器,通过输入不同的电平和信号,可以得到正确的输出结果,满足电路设计的要求。

五、结论本文介绍了如何使用Multisim软件来设计逻辑电平测试器,实验步骤清晰,且得到了正确的设计结果,可以作为使用Multisim软件设计电路的参考。

逻辑分析仪的原理及其应用1. 简介逻辑分析仪是一种专业的电子测试与测量设备,常用于逻辑信号的分析和调试。

它可以通过监视和分析信号的状态变化,帮助工程师定位和解决电子设备中的故障和问题。

本文将介绍逻辑分析仪的工作原理及其常见应用。

2. 工作原理逻辑分析仪的工作原理基于数字电路的运作方式。

它可以同时采样多个逻辑信号,并将其转换成数字形式进行分析。

逻辑分析仪通常包含以下主要组件:2.1 采样部分逻辑分析仪通过一组输入引脚来采样逻辑信号。

这些引脚可以连接到被测试设备的电路上,并将逻辑信号转换成数字电平。

通常,逻辑分析仪提供多个输入引脚,以便同时采样多个信号。

2.2 时钟为了进行精确的采样和分析,逻辑分析仪需要一个稳定的时钟信号。

该时钟信号用于控制采样过程和数据的同步性。

2.3 数字转换器逻辑分析仪使用数字转换器将模拟信号转换成数字形式。

这个过程称为模数转换。

数字转换器的精确性和分辨率直接影响到逻辑分析仪的性能。

2.4 内存逻辑分析仪使用内存来存储被采样的信号。

内存的大小决定了逻辑分析仪可以存储的信号量。

较大的内存可以存储更多的信号,提供更长时间的采样。

2.5 控制单元逻辑分析仪的控制单元通过与用户界面的交互来控制采样过程和数据分析。

它可以根据用户的设定来捕捉和分析特定的逻辑信号。

3. 应用领域逻辑分析仪在各个电子领域中有广泛的应用。

以下是几个常见的应用领域:3.1 数字电路设计与验证逻辑分析仪可以对数字电路进行快速和准确的验证。

它可以监测和分析不同信号路径上的时序关系,帮助工程师查找潜在的故障和设计错误。

3.2 嵌入式系统调试在嵌入式系统开发过程中,逻辑分析仪可以帮助工程师调试和分析系统中的逻辑问题。

它可以监视和分析各个部分之间的通信和数据传输,帮助工程师定位问题并进行修复。

3.3 协议分析逻辑分析仪可以用于协议分析,例如串行通信协议和总线协议。

它可以监视通信过程,捕捉和分析数据包的交互,并提供详细的时序和数据分析。

实验三组合逻辑电路的功能测试基本逻辑门测试:1.与门测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为1时,输出信号应为1;其他情况下,输出信号应为0。

2.或门测试:与与门测试类似,在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为0时,输出信号应为0;其他情况下,输出信号应为13.非门测试:在输入端口接入输入信号A,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号为0时,输出信号应为1;当输入信号为1时,输出信号应为0。

4.异或门测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号相同(均为0或均为1)时,输出信号应为0;当输入信号不同(一个为0,一个为1)时,输出信号应为1组合逻辑电路测试:1.与门与非门的组合测试:在输入端口分别接入两个输入信号A、B,并将输出端口接入示波器。

通过输入不同的逻辑电平(0或1),观察输出信号。

当输入信号都为1时,输出信号应为0;其他情况下,输出信号应为12.或门与非门的组合测试:与与门与非门的组合测试类似,只需将与门替换为或门,测试结果应与与门与非门的组合测试相反。

3.封装后的组合逻辑电路测试:使用封装后的组合逻辑电路实现具体的逻辑功能,如加法器、选择器等。

通过输入不同的逻辑电平(0或1),观察输出信号,验证实现的逻辑功能是否正确。

在进行功能测试时,需要注意输入信号的切换时间、输出信号的稳定时间,确保电路能够正常工作。

此外,还可以通过逻辑表或真值表对测试结果进行验证,确保组合逻辑电路的正确性。

总结:实验三组合逻辑电路的功能测试是通过对基本逻辑门和组合逻辑电路进行输入输出信号的观察和测试,验证其功能正确性。

毕业设计说明书(论文)中文摘要逻辑信号电平测试器的设计摘要本文介绍了一个逻辑信号电平测试器,它可以方便快捷的测量某一点的电位的高低,通过声音的有无和声音的频率来判定被测电位的电平范围,从而能解决平常对电路中某点的逻辑电平进行测试其高低电平时,采用很不方便的万用表或示波器等仪器仪表的麻烦。

该电路主要包括三部分电路:输入电路、逻辑状态识别电路和音响声调产生电路。

其主要应用了集成运放的非线性电路特性,开环增益很大,从而可以制作成双限比较器;用555定时器构成的多谐振荡器作为音响产生电路,利用对电容的充放电,得到一定频率的信号。

输入的逻辑信号电平大于或小于所设定的高低电平电位,则音响电路发声,如若在高低电平之间,则音响电路不发声。

利用这种方式设计电路,计算元器件参数,选择成本合适的器件,确定电路形式并进行仿真实验验证,最后做出符合全部要求的实物。

关键词逻辑信号;电平测试;高电平;低电平毕业设计说明书(论文)外文摘要Logic-level test signal designAbstractThis paper, a logic level signal tester, it can be a convenient measurement that the level of potential through the availability of voice and sound frequencies to determine the level of the measured potential range. Thus can solve common circuit at some point in the logic level test its height electricity at ordinary times, it is not convenient by the multimeter or oscillograph instrument, etc .The design of the circuit mainly includes three parts: input circuit, the logic of the state of voice recognition and audio circuits have circuit. The main application of an integrated circuit operational amplifier nonlinear characteristics of a large open-loop gain, which can limit the production of dual comparators; used consisting of 555 timer Multivibrator circuit as a sound generated by the charging and discharging of the capacitor , a certain frequency signal. The logic input signal level is greater than or less than the high-low set potential, the audible sound circuit, if in between the high-low, the sound is not audible circuit. In this way the use of circuit design, component parameters of the calculation, select the appropriate cost of the device torequirements.and circuit simulation, and finally to meet all physical requirements. Keyword:s logic signal, level testing, high, lowKeywords logic signal, level testing, high, low目录1 绪论 (1)1.1课题研究及其意义 (1)1.2国内外研究现状及发展趋势 (1)2 逻辑电平信号测试系统简介 (2)2.1 测试电路的设计思路 (2)2.2 测试电路的要求 (3)2.3 测试电路的原理介绍 (3)3 测试电路中所涉及的芯片 (3)3.1 LM311高灵活性的电压比较器芯片介绍 (4)3.1.1 典型的比较设计配置 (4)3.1.2 LM311性能参数 (5)3.2 555定时器芯片电路 (7)3.2.1 芯片简介 (7)3.2.2 电路结构和控制特性 (8)3.2.3 555定时器构成的多谐振荡器 (10)4 整体电路的设计 (12)4.1 输入电路 (13)4.2逻辑信号判断短路 (13)4.3 声响部分的电路图设计和工作原理 (14)5 电路的仿真 (15)5.1 protues仿真软件的概述 (15)5.1.1 protues的功能特点 (16)5.1.2 电路功能仿真 (16)5.2 模拟逻辑信号的仿真 (17)5.3 比较电压仿真 (17)5.4 声响波形仿真 (18)5.4.1 高电平信号输入仿真 (18)5.4.2 无电平信号输入仿真 (19)5.4.3低电平信号输入仿真 (20)5.5 仿真结论 (20)总结 (21)参考文献 (22)致谢 (23)附录:完整电路图 (24)逻辑信号电平测试器的设计1 绪论在集成电路中,存在着高电平和低电平两个概念,在数字电路中与传统的模拟电路中有很大的区别:首先,模拟电路和数字电路都属于电子电路,模拟电路要求把握对模拟量变化掌控,这点是其相对于数字电路来讲的难点。

模拟电路仿真软件实验报告篇一:模拟电路仿真实验报告一、实验目的(1)学习用multisim实现电路仿真分析的主要步骤。

(2)用仿真手段对电路性能作较深入的研究。

二、实验内容1.晶体管放大器共射极放大器(1)新建一个电路图(图1-1),步骤如下:①按图拖放元器件,信号发生器和示波器,并用导线连接好。

②依照电路图修改各个电阻与电容的参数。

③设置信号发生器的参数为Frequency1khz,Amplitude10mV,选择正弦波。

④修改晶体管参数,放大倍数为40,。

(2)电路调试,主要调节晶体管的静态工作点。

若集电极与发射极的电压差不在电压源的一半上下,就调节电位器,直到合适为止。

(3)仿真(↑图1)(↓图2)2.集成运算放大器差动放大器差动放大器的两个输入端都有信号输入,电路如图1-2所示。

信号发生器1设置成1khz、10mV的正弦波,作为ui1;信号发生器2设置成1khz、20mV的正弦波,作为ui2。

满足运算法则为:u0=(1+Rf/R1)*(R2/R2+R3)*ui2-(Rf/R1)*ui1仿真图如图3图1-2图33.波形变换电路检波电路原理为先让调幅波经过二极管,得到依调幅波包络变化的脉动电流,再经过一个低通滤波器,滤去高频部分,就得到反映调幅波包络的调制信号。

电路图如图1-4,仿真结果如图4.篇二:multisim模拟电路仿真实验报告1.2.3.一、实验目的认识并了解multisim的元器件库;学习使用multisim 绘制电路原理图;学习使用multisim里面的各种仪器分析模拟电路;二、实验内容【基本单管放大电路的仿真研究】仿真电路如图所示。

1.2.修改参数,方法如下:双击三极管,在Value选项卡下单击eDITmoDeL;修改电流放大倍数bF为60,其他参数不变;图中三极管名称变为2n2222A*;双击交流电源,改为1mV,1kz;双击Vcc,在Value选项卡下修改电压为12V;双击滑动变阻器,在Value选项卡下修改Increment值为0.1%或更小。

逻辑信号电平测试仪的设计过程,遇到的问题及解决措施逻辑信号电平测试仪是电子工程师在测试数字电路时不可或缺的测试设备。

设计一个高精度的逻辑信号电平测试仪需要考虑多个方面。

首先,需要确定测试仪的精度和可靠性指标。

我确定了该测试仪应能够测试包括TTL和CMOS逻辑电平的信号。

测试仪应能够精准地测试信号电平,以保证准确绘制数字波形。

此外,还要保证测试仪的可靠性,以避免误判和漏测。

接着,需要确定测试仪的硬件设计。

该测试仪的硬件设计有两个主要部分:信号输入和信号负载。

考虑到测试各种类型的逻辑电平,我决定在输入端添加多种测试模式。

测试仪在测试TTL电平时,应采用1.4V高电平和0.8V低电平。

在测试CMOS电平时,应采用3.3V和5V电平。

此外,我在表面贴装技术(SMT)技术下采用高精度的模拟转换器和数字信号处理器(DSP)以实现高精度测试。

在选定硬件设计后,我进行了软件设计。

在测试仪软件设计的初期阶段,我遇到了运算速度和精度之间的取舍问题。

结果,我选择了迭代运算法,以平衡速度和精度,并在测试数据中实现了高精度数字滤波算法。

这使得测试仪能够快速准确地测量逻辑电平。

在实际测试时,我遇到了一些问题。

例如,当测试CMOS高电平电平时,测试仪读取结果与实际值不相符。

经过多次检查,我发现测试仪读取的结果与实际值的差异可能是由于测试仪的参考电压发生了微小的变化。

为此,我重新校准了测试仪的参考电压,并重新测试了高电平电平。

这次测试精准度就达到了预期。

最后,我确定了测试仪的工作环境,并进行了性能测试。

测试仪在温度为16-30℃,湿度为30-70%的环境下,具有非常稳定和可靠的性能。

测试仪的精度高达15位,因此它可以满足大多数数字电路测试要求。

总之,逻辑信号电平测试仪是一个非常实用和有效的测试设备。

在设计该测试仪时,我遇到了各种问题,但通过使用高精度的硬件和软件解决方案,我能够实现高精度测试并确保测试仪的可靠性和稳定性。

实验十一时序逻辑电路的设计与测试一、实验目的1.掌握时序逻辑电路的设计原理与方法。

2.掌握时序逻辑电路的实验测试方法。

二、实验原理该实验是基于JK触发器的时序逻辑电路设计,要求设计出符合一定规律的红、绿、黄三色亮灭循环显示的电路,并且在实验板上搭建实现出来。

主要的设计和测试步骤如下:(1)根据设计的循环显示要求,列出有关Q3Q2Q1状态表;(2)根据状态表,写出各触发器的输入端J和K的状态;(3)画出各触发器的输入端J和K关于Q3Q2Q1的卡诺图;(4)确定各触发器的数软J和K的最简方程;(5)根据所得的最简方程设计相应的时序逻辑电路;(6)在实验板上,有步骤有次序的搭建实验电路,测试所设计的电路是否满足要求。

具体设计过程参见【附录二】提供的实例。

三、预习要求1.查阅附录芯片CC4027B和芯片74LS00的管脚定义。

2.阅读理论教材关于时序逻辑电路的内容,掌握实验的理论基础。

四、实验设备与仪器1.数字电路实验板(箱);2.芯片:CC4027B;74LS00;74LS20。

五、实验内容请任意选择下列一组彩灯循环显示的任务要求,设计相应的时序电路,并搭建实验线路测试之。

1.设计任务(一)2.设计任务(二)3.设计任务(三)4.设计任务(四)5.设计任务(五)6.设计任务(六)7.设计任务(七)8.设计任务(八)六、实验报告1.根据实验内容的设计要求,完成实验时序电路的设计和测试。

2.小结时序逻辑电路的设计思路与测试方法。

3.实验的心得与体会。

七、实验注意事项1.进行实验连线的过程中,注意有步骤的接线,避免多接和漏接的情况。

2.在设计好的时序逻辑电路中,若管脚没有接任何信号,处于悬空状态,注意最好给其提供高电平信号。

3.实验结束或者改接线路时,注意断开电源,保护芯片。

八、思考题1.实验要求设计的时序电路,可否设计成异步时序逻辑电路?这相对于同步时序逻辑电路有什么不同?2.能否设计一个时序逻辑电路,若初态为“000”是一个“000—〉001—〉010—〉011”循环的加法计数器,若初态为“111”是一个“111—〉110—〉101—〉100”循环的减法计数器?试设计之。

逻辑测试笔的设计与实现李晓虹【摘要】利用Proteus仿真软件设计了一款逻辑测试笔,详细介绍了该逻辑测试笔的工作原理,并经实际制作调试成功,能准确检测数字电路的逻辑信号,大大提高了电子电路设计的效率.【期刊名称】《武汉工程职业技术学院学报》【年(卷),期】2015(027)003【总页数】4页(P43-46)【关键词】仿真;调试;逻辑测试笔【作者】李晓虹【作者单位】武汉工程职业技术学院湖北武汉:430080【正文语种】中文【中图分类】TN710.9在对数字电路进行调试或维修时,通常采用万用表来检测各种芯片的输入输出状态,分析电路的工作情况,仍因数字电路测试点多而十分不便。

因此有必要设计一种逻辑测试笔专门用于检测数字电路的输入输出状态[1],方便故障的诊断和处理。

1 逻辑测试笔的组成框图图1为逻辑测试笔组成框图,该逻辑测试笔由输入电路、逻辑状态判断电路、处理输出显示电路、电源四部分组成。

图1 逻辑测试笔组成框图输入信号经输入电路送入逻辑状态判断电路进行状态分析[1],判断的结果送处理输出显示电路分类处理后驱动1只相应颜色(红、黄、绿)的发光二极管亮显示相应的逻辑状态。

采用+9V层叠电池处理后为该逻辑测试笔提供工作电压。

2 单元电路组成及工作原理2.1 单限电压比较器电压比较器的基本功能是对两个输入电压进行比较,并根据比较结果输出高电平或低电平电压[2]。

LM393集成电压比较器如图2所示。

图2(a)为同相输入单限电压比较器,其参考电压UREF接在比较器的反相端,待比较的输入电压Ui接到同相端[2]。

当Ui≥UREF时,比较器输出高电平;当 Ui<UREF时,比较器输出低电平。

由于Ui 从同相端输入且只有一个门限,故称同相输入单限电压比较器。

同理,图2(b)为反相输入单限电压比较器,当Ui≤UREF时,比较器输出低电平;当Ui>UREF 时,比较器输出高电平。

图2 LM393集成电压比较器2.2 输入及逻辑状态判断电路图3所示为输入及逻辑状态判断电路,其工作原理如下。

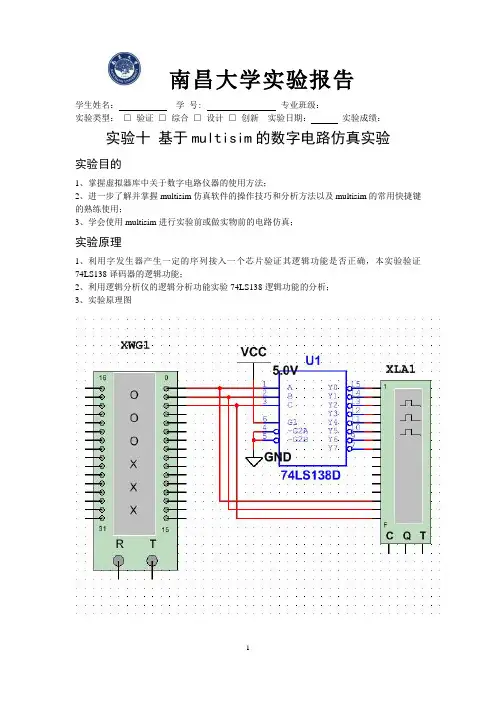

一、实验目的1. 理解译码器的原理和功能。

2. 掌握译码器的应用和实现方法。

3. 培养动手能力和团队协作精神。

二、实验原理译码器是一种将二进制编码信号转换为特定信号的电路。

在数字系统中,译码器广泛应用于地址译码、数据译码、指令译码等方面。

本实验主要研究译码器的原理、设计和实现。

三、实验设备1. 74LS138译码器芯片;2. 数字实验箱;3. 逻辑电平测试仪;4. 线路板;5. 连接线。

四、实验内容1. 译码器原理分析;2. 译码器设计;3. 译码器电路搭建;4. 译码器功能测试。

五、实验步骤1. 译码器原理分析首先,分析译码器的工作原理。

译码器由编码器、译码电路和输出电路组成。

编码器将输入信号转换为二进制编码信号,译码电路根据编码信号输出对应的信号,输出电路将译码电路输出的信号转换为所需的信号。

2. 译码器设计根据实验要求,设计译码器电路。

本实验采用74LS138译码器芯片,该芯片具有3个输入端和8个输出端。

根据输入信号的不同组合,输出对应的信号。

3. 译码器电路搭建(1)将74LS138译码器芯片插入数字实验箱的相应位置。

(2)根据译码器电路原理图,将输入端和输出端连接到实验箱的相应位置。

(3)检查电路连接是否正确,确保无短路和断路现象。

4. 译码器功能测试(1)将译码器输入端连接到逻辑电平测试仪。

(2)设置输入端信号,观察输出端信号。

(3)验证译码器输出信号是否符合预期。

六、实验结果与分析1. 实验结果实验过程中,根据译码器原理和设计,成功搭建了译码器电路。

在输入端设置不同的信号组合,输出端信号符合预期。

2. 实验分析本实验验证了译码器的原理和功能。

通过实验,我们了解到译码器在数字系统中的应用和实现方法。

在实验过程中,我们学会了如何设计译码器电路,如何搭建电路,以及如何进行功能测试。

七、实验总结1. 通过本次实验,掌握了译码器的原理和功能。

2. 学会了译码器的设计方法和实现过程。

3. 培养了动手能力和团队协作精神。

模拟电路课程设计篇一:模拟电路课程设计模拟电子技术课程设计任务书一、课程设计的任务通过理论设计和实物制作解决相应的实际问题,巩固和运用在《模拟电子技术》中所学的理论知识和实验技能,掌握常用模拟电路的一般设计方法,提高设计能力和实践动手能力,为以后从事电子电路设计、研发电子产品打下良好的基础。

二、课程设计的基本要求1、掌握电子电路分析和设计的基本方法。

包括:根据设计任务和指标初选电路;调查研究和设计计算确定电路方案;选择元件、安装电路、调试改进;分析实验结果、写出设计总结报告。

2、培养一定的自学能力、独立分析问题的能力和解决问题的能力。

包括:学会自己分析解决问题的方;对设计中遇到的问题,能通过独立思考、查询工具书和参考文献来寻找解决方案,掌握电路测试的一般规律;能通过观察、判断、实验、再判断的基本方法解决实验中出现的一般故障;能对实验结果独立地进行分析,进而做出恰当的评价。

3、掌握普通电子电路的生产流程及安装、布线、焊接等基本技能。

4、巩固常用电子仪器的正确使用方法,掌握常用电子器件的测试技能。

5、通过严格的科学训练和设计实践,逐步树立严肃认真、一丝不苟、实事求是的科学作风,并逐步建立正确的生产观、经济观和全局观。

三、课程设计任务课题4 逻辑信号电平测试器的设计(一)设计目的1、学习逻辑信号电平测试器的设计方法;2、掌握其各单元电路的设计与测试方法;3、进一步熟悉电子线路系统的装调技术。

(二)设计要求和技术指标在检修数字集成电路组成的设备时,经常需要使用万用表和示波器对电路中的故障部位的高低电平进行测量,以便分析故障原因。

使用这些仪器能较准确地测出被测点信号电平的高低和被测信号的周期,但使用者必须一面用眼睛看着万用表的表盘或者示波器的屏幕,一面寻找测试点,因此使用起来很不方便。

本课题所设计的仪器采用声音来表示被测信号的逻辑状态,高电平和低电平分别用不同声调的声音来表示,使用者无须分神去看万用表的表盘或示波器的荧光屏。

设计题目:逻辑信号电平测试器的设计1 设计要求及主要技术指标1.1 设计要求1.1.1、根据技术指标要求确定电路形式,分析工作原理,计算元件参数。

1.1.2、列出所用元器件清单并购买。

1.1.3、安装调试所设计的电路,使之达到设计要求。

1.1.4、记录实验结果。

1.1.5、撰写设计报告(含调试内容)。

1.2主要技术指标1.2.1、测量范围:低电平UL <0.8V;高电平UH>3.5V。

1.2.2、高低电平用变色发光二极管来显示,红色表示高电平,绿色表示低电平。

1.2.3、当被测信号在0.8V~3.5V之间时,发光二极管不亮。

1.2.4、输入电阻大于20kΩ。

1.2.5、工作电源为5V。

1.2.6、要求选用CW78三端集成稳压器,LM324型四运放集成电路,2EF302型三端变色发光二极管。

2 设计过程2.1题目分析逻辑信号点平测试器是将一个模拟量输入电压与一个参考电压进行比较,输出高电平低电平。

2.2 整体构思电源→输入电路→逻辑状态识别电路→显示电路.2.3 具体实现2.3.1、根据技术指标要求确定稳压器型号及电路形式.2.3.2、根据稳压器的输入电压确定电源变压器的副边电压U2.根据稳压电流的最大输出电流Imax和U2确定副边的功率P2.根据P2及效率确定电源变压器功率P1.2.3.3、确定整流二极管和滤波电容.2.3.4、根据技术指标确定输入电阻逻辑电路电阻,由2EF302型三端变色发光二极管确定显示部分保护电阻。

3 元件说明及相关计算3.1 元件说明3.1.1、电阻器固定电阻器的主要参数是标称阻值、允许误差和额定功率。

标称阻值和允许误差:电阻器上标志的阻值叫标称值,而实际值与标称值的偏差,除以标称值所得的百分数叫电阻的误差,它反映了电阻器的精度。

不同的精度有一个相应的误差,表1列出了常用电阻器的允许误差等级(精度等级)。

表1 常用电阻器允许误差的等级允许误差±0.5%±1%±2%±5%±10%±20%级别005 01 02 ⅠⅡⅢ类型精密型普通型目前固定电阻器大都为I级或II级普通电阻,而且III级很少,能满足一般应用的要求,02、01、005级的精密电阻器,一般用于测量仪器,仪表及特殊设备电路中。

国家有关部门规定了阻值系列作产品的标准,表2是普通电阻器系列表。

表中的标称值可以乘以10n,例如,4.7这个标称值,就有0.47Ω、4.7Ω、47Ω、470Ω、4.7 KΩ……。

选择阻值时必须在相应等级的系列表中进行。

表2 电阻器系列及允许误差E24 1.0 1.1 1.2 1.3 1.5 1.6 1.8 2.0 2.2 2.4 2.7 3.0 3.3 3.6 3.9 4.3 4.7 5.1 5.6 6.26.87.58.29.1E12 1.0 1.2 1.5 1.8 2.2 2.7 3.3 3.9 4.7 5.66.8 8.2E6 1.0 1.5 2.2 3.3 4.76.8各系列允许误差E24-5% E12-10% E 6-20%电阻器的额定功率:电阻器在电路中长时间连续工作不损坏,或不显著改变其性能所允许消耗的最大功率称为电阻器的额定功率。

电阻器的额定功率并不是电阻器在电路中工作时一定要消耗的功率,而是电阻器在电路工作中所允许消耗的最大功率。

不同类型的电阻具有不同系列的额定功率,如表2所示。

表2 电阻器的功率等级名称额定功率(W)实芯电阻器0.25 0.5 1 2 5 -线绕电阻器0.5251352506751010015150薄膜电阻器0.02520.0550.125100.25250.5501100电阻器的型号命名方法:第一部分:主称第二部分:材料第三部分:特征分类符号符号意义符号 意义 意义 电阻器 电位器 第四部分:序号 R 电阻器 T 碳膜 1 普通 普通对主称、材料相同,仅性能指标、尺寸大小有差别,但基本不影响互换使用的产品,给予同一序号;若性能指标、尺寸大小明显影响互换时,则在序号后面用大写字母作为区别代号。

W 电位器 H 合成膜 2 普通 普通S 有机实芯 3 超高频 ―― N 无机实芯 4 高阻 ――J 金属膜 5 高温 ――Y 氧化膜 6 ―― ―― C 沉积膜 7 精密 精密 I 玻璃釉膜 8 高压 特殊函数 P 硼碳膜 9 特殊 特殊 U 硅碳膜 G 高功率 ――X 线绕 T 可调 ――M 压敏 W ―― 微调G 光敏 D ―― 多圈R 热敏 B 温度补偿用 ――C 温度测量用 ―― P 旁热式 ―― W 稳压式 ―― Z正温度系数――示例:电阻器的标志内容及方法文字符号直标法:用阿拉伯数字和文字符号两者有规律的组合来表示标称阻值,额定功率、允许误差等级等。

符号前面的数字表示整数阻值,后面的数字依次表示第一位小数阻值和第二位小数阻值,其文字符号所表示的单位如表5所示。

如1R5表示1.5W,2K7表示2.7kW,表5文字符号R K M G T表示单位欧姆(W) 千欧姆(103W) 兆欧姆(106W) 千兆欧姆(109W) 兆兆欧姆(1012W)例如:由标号可知,它是精密金属膜电阻器,额定功率为1/8W,标称阻值为5.1kW,允许误差为±10%。

色标法:色标法是将电阻器的类别及主要技术参数的数值用颜色(色环或色点)标注在它的外表面上。

色标电阻(色环电阻)器可分为三环、四环、五环三种标法。

其含义如图1和图2所示。

三色环电阻器的色环表示标称电阻值(允许误差均为±20%)。

例如,色环为棕黑红,表示10′102=1.0kW±20%的电阻器。

四色环电阻器的色环表示标称值(二位有效数字)及精度。

例如,色环为棕绿橙金表示15′103=15kW±5%的电阻器。

五色环电阻器的色环表示标称值(三位有效数字)及精度。

例如,色环为红紫绿黄棕表示275′104=2.75MW±1%的电阻器。

一般四色环和五色环电阻器表示允许误差的色环的特点是该环离其它环的距离较远。

较标准的表示应是表示允许误差的色环的宽度是其它色环的(1.5~2)倍。

有些色环电阻器由于厂家生产不规范,无法用上面的特征判断,这时只能借助万用表判断。

3.1.2、电容器电容器的型号命名法:第一部分:主称第二部分:材料第三部分:特征、分类第四部分:序号符号意义符号意义符号意义瓷介云母玻璃电解其他电容器C 瓷介 1 圆片非密封-箔式非密封对主称、材料相同,仅尺寸、性能指标略有不同,但基本不影响互使用的产品,给予同一序号;若尺寸性能指标的差别明显;影响互换使用时,则在序号后面用大写字母作为区别Y 云母 2 管形非密封-箔式非密封I 玻璃釉 3 迭片密封-烧结粉固体密封O 玻璃膜 4 独石密封-烧结粉固体密封Z 纸介 5 穿心---穿心J 金属化纸6 支柱----B 聚苯乙7 ---无极性-代号。

烯L 涤纶8 高压高压--高压Q 漆膜9 ---特殊特殊J 金属膜S 聚碳酸脂W 微调H 复合介质D 铝A 钽N 铌G 合金T 钛E 其他示例:(1) 铝电解电容器电容器的主要技术指标:(1)电容器的耐压:常用固定式电容的直流工作电压系列为:6.3V,10V,16V,25V,40V,63V,100V,160V,250V,400V。

(2)电容器容许误差等级:常见的有七个等级如表7所示。

电容器的标志方法:有时用大于1的两位以上的数字表示单位为pF的电容,例如101表示100 pF;用小于1的数字表示单位为mF 的电容,例如0.1表示0.1mF。

(2) 数码表示法一般用三位数字来表示容量的大小,单位为pF。

前两位为有效数字,后一位表示位率。

即乘以10i,i为第三位数字,若第三位数字9,则乘10-1。

如223J 代表22′103pF=22000pF=0.22mF,允许误差为±5%;又如479K代表47′10-1pF,允许误差为±5%的电容。

这种表示方法最为常见。

(3)色码表示法这种表示法与电阻器的色环表示法类似,颜色涂于电容器的一端或从顶端向引线排列。

色码一般只有三种颜色,前两环为有效数字,第三环为位率,单位为pF。

有时色环较宽,如红红橙,两个红色环涂成一个宽的,表示22000pF。

3.1.3、变压器3.1.4、二极管3.1.5、集成运放LM324是四运放集成电路,它采用14脚双列直插塑料封装,外形如图所示。

它的内部包含四组形式完全相同的运算放大器,除电源共用外,四组运放相互独立。

每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

LM324的引脚排列见图由于LM324四运放电路具有电源电压范围宽,静态功耗小,可单电源使用,价格低廉等优点,因此被广泛应用在各种电路中。

3.1.6、集成稳压器CW7805、CW7812、CW7912、CW317集成稳压器的主要参数:参数名称/单位CW7805 CW7812 CW7912 CW317输入电压/V +10 +19 -19 £40输出电压范围/V +4.75~+5.25 +11.4~+12.6 -11.4~-12.6 +1.2~+37最小输入电压/V +7 +14 -14 +3£Vi-Vo£+40电压调整率/mV +3 +3 +3 0.02%/V最大输出电流/A 加散热片可达1A 1.53.2 相关计算3.2.1、计算集成稳压器:输出电压U0=+5V,最大电流I0=1.5A。

电容取C1=C2=0.1uf。

(作用是防止其它信号的干扰)3.2.2、计算电源变压器集成稳压器的输出电压与稳压器的输出电压相同,可得输入电压Vi的范围为Vomax+(Vi-Vo)min≤Vi≤Vomin+(Vi-Vo)max5V+3V≤Vi≤Vomin+(Vi-Vo)max8V≤Vi≤Vomin+(Vi-Vo)max副边电压V2≥Vimin/1.1=8V/1.2V,取V2=9V,副边电流I2>Iomax=0.24A,取I2=0.3A,则变压器副边输出功率P2≥I2V2=2.7W。

由表1可得变压器的效率η=0.6,则原边输入功率P1≥P2/η=4.5W。

为留有余地,选功率为8W的电源变压器。

表一、小型变压器的效率副边功率(W) 2P <10 10~30 30~80 80~200效率η0.6 0.7 0.8 0.853.2.3、计算整流二极管及滤波电容整流二极管D选1N4001,其极限参数为VRM≥50V,IF=lA。