VHDL语言的主要描述语句

- 格式:doc

- 大小:107.50 KB

- 文档页数:25

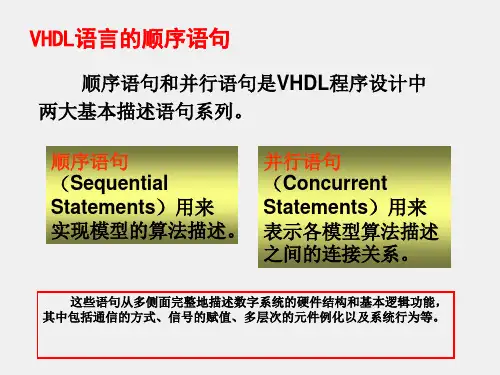

第三章VHDL的语句VHDL中的语句按其执行顺序可分为顺序描述语句和并行描述语句两大类。

顺序描述语句的执行顺序是按语句的书写顺序依次执行的,常用于实现模块的算法部分;并行描述语句的执行顺序与书写顺序无关,所有语句是并发执行的,常用于表示模块间的连接关系。

本章将详细介绍这两类VHDL语句。

3.1 VHDL语言的顺序描述语句顺序语句是建模进程、过程和函数功能的基本语句单元,它只能在进程、过程和函数中使用,其执行顺序按照书写顺序来执行,同时前面语句的执行结果会对后面语句的执行结果产生影响。

顺序描述语句按照控制方式分为条件控制语句和迭代控制语句,其中,条件控制语句有IF语句和CASE语句,迭代控制语句有循环语句和顺序断言语句。

下面对顺序描述语句进行详细介绍。

3.1.1 信号赋值语句与变量赋值语句采用VHDL描述硬件电路的过程中,数据的传递和端口界面数据的读写都是通过赋值语句来实现的,赋值语句就是将一个数值或表达式传递给某一个数据对象的语句。

VHDL 提供了两类赋值语句:信号赋值语句和变量赋值语句。

信号虽然只能在VHDL程序的并行部分进行说明,但是它在程序的顺序部分和并行部分都可使用。

信号赋值语句的语法如下:待赋值信号<=表达式;变量的说明和赋值操作都只能在程序的顺序部分进行。

变量赋值语句的语法如下:待赋值变量:=表达式;注意:不论是信号还是变量,赋值符号两边必须具备相同的数据类型和位长。

在前一章我们讲过信号与变量的区别,这里有必要重申一下:信号赋值的执行和信号值的更新之间是有一定延迟的,只有经过延迟后信号才能得到新值,否则保持原值;而变量赋值的语句执行后立即得到新值,没有延迟。

上面讲到,信号赋值会有延迟,其实,VHDL允许为信号赋值选择“延迟机制”,即:传输延迟或惯性延迟,其中,传输延迟用于表示无论输入脉冲宽度多窄都能在输出端无失真复现的延迟模型;惯性延迟用于表示输入脉冲传播时间受电路“惯性”影响的延迟模型。

vhdl语句

VHDL是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

以下是VHDL中的一些基本语句:

1.实体(Entity):用于声明一个电路或系统的接口,包括输入、输

出和输入/输出端口。

2.结构体(Architecture):用于描述电路或系统的实现,包括元件的

连接和行为描述。

3.信号赋值语句:用于在进程中给信号赋值,例如“a <= b;”。

4.条件赋值语句:用于根据条件给信号赋值,例如“IF condition THEN

a <=

b ELSE a <=

c END IF;”。

5.选择信号赋值语句:用于根据选择信号的值给信号赋值,例如

“SELECT CASE a WHEN value1 THEN b WHEN value2 THEN c WHEN OTHERS THEN d END CASE;”。

6.进程语句:用于描述电路或系统的行为,包括顺序执行和并行执

行。

7.元件例化语句:用于实例化一个元件,并将其连接到其他元件上。

8.生成语句:用于生成多个相同类型的元件实例。

9.子程序调用语句:用于调用一个子程序。

10.顺序语句:在仿真意义上具有一定顺序性,并不意味着这些语句

对于的硬件结构也有相同的顺序性。

所有门电路是并行地工作,并没有先后之分。

11.并行语句:在仿真运行中总处于两种状态:执行或者挂起。

当执

行到wait语句时,运行程序将被挂起,直到满足此语句设置的结束挂起条件后,将重新开始执行进程中的程序。

以上只是VHDL中的一些基本语句,实际上VHDL还支持更多的高级功能和描述方式。

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:并行描述语句该语句的执行与书写顺序无关,总是同时被执行顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体内可以有几个进程语句同时存在,而且并发执行。

但是进程内部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

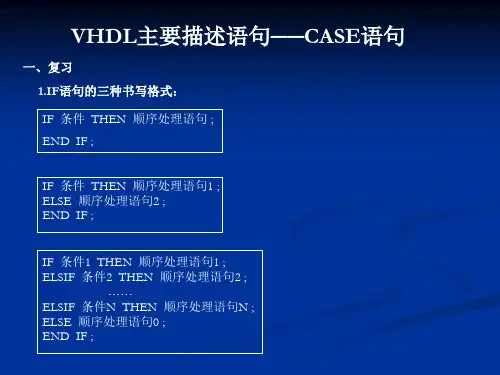

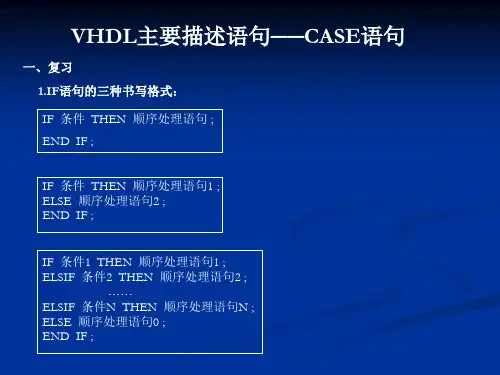

(5) 超时等待例5-3例5-42.断言语句(ASSERT)(主要用于仿真、调试)格式: ASSERT 条件[REPORT 输出信息][SEVERITY 级别]执行到断言语句时,判断条件,若条件满足就继续执行,否则输出文字串和错误级别信息.例: ASSERT (tiaojian=’1’)REPORT “some thing wrong”SEVERITY ERROR;3.信号代入语句格式: 目的信号量<=信号量表达式例: a<=b;(注意区别小于等于)4.变量赋值语句格式: 目的变量:=表达式例: c:=a+d5.IF 语句三种书写格式:1) IF的门闩控制格式:IF 条件THEN顺序执行语句;END IF;例5-5IF (a=’1’) THENc<=b;END IF;例5-62)IF 语句的二选择控制格式:IF 条件THEN顺序执行语句;ELSE顺序执行语句;END IF;例5-7ARCHITECTURE rt1 OF mux2 ISBEGINPROCESS(a,b,sel)BEGINIF(sel=’1’) THENc<=a;ELSEc<=b;END IF;END PROCESS;END rt1;3)IF 语句的多选择控制格式:IF 条件THEN顺序执行语句ELSIF 条件THEN顺序执行语句::ELSIF 条件THEN顺序执行语句ELSIF 条件THEN顺序执行语句END IF;例如:5-8LIBRARY IEEE;USE ENTITY mux4 ISPORT(input :IN STD_LOGIC_VECTOR(3 DOWNTO 0);sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0);q: OUT STD_LOGIC);END mux4;ARCHITECTURE rt1 OF mux4 ISBEGINnn: PROCESS(input,sel)BEGINIF (sel='00') THENq<=input(0);ELSIF (sel='01') THENq<=input(1);ELSIF (sel='10') THENq<=input(2);ELSEq<=input(3);ENDIF;END PROCESS nn;END rt1;注意:条件判断输出是布尔量。

6.CASE 语句常用来描述总线、编码和译码的行为。

格式:CASE 表达式ISWHEN 条件表达式=>顺序处理语句END CASE;其中WHEN的条件表达式可以有4种形式:WHEN 值=>顺序处理语句WHEN 值|值|值|…|值=>顺序处理语句WHEN 值TO 值=>顺序处理语句WHEN OTHERS=>顺序处理语句例:5-9LIBRARY IEEE;USE ENTITY mux43 ISPORT(a,b,i0,i1,i2,i3 :IN STD_LOGIC;q : OUT STD_LOGIC); END mux43;ARCHITECTURE mux4_behave OF mux43 ISSIGNAL sel: INTEGER RANGE 0 TO 3;BEGINnn: PROCESS(a,b,i0,i1,i2,i3)BEGINsel<=0;IF (a='1') THENsel<=sel+1;END IF;IF (b='1') THENEND IF;CASE sel ISWHEN 0 =>q<=i0;WHEN 1 =>q<=i1;WHEN 2 =>q<=i2;WHEN 3 =>q<=i3;END CASE;END PROCESS nn;END mux4_behave;例5-10 3-8译码器LIBRARY ieee;USE decoder38 isport(a,b,c,g1,g2a,g2b: in std_logic;y: out std_logic_vector(7 downto 0)); end decoder38;architecture behave38 OF decoder38 is signal indata: std_logic_vector(2 downto 0); beginindata<=c&b&a;process(indata,g1,g2a,g2b)beginif(g1='1' and g2a='0' and g2b='0') thenwhen "000"=>y<="11111110";when "001"=>y<="11111101";when "010"=>y<="11111011";when "011"=>y<="11110111";when "100"=>y<="11101111";when "101"=>y<="11011111";when "110"=>y<="10111111";when "111"=>y<="01111111";when others=>y<="XXXXXXXX";end case;elsey<="11111111";end if;end process;end behave38;例5-11LIBRARY ieee;USE encoder isport(input: in std_logic_vector(7 downto 0);y: out std_logic_vector(2 downto 0)); end encoder;architecture behave OF encoder isbeginprocess(input)begincase input iswhen”01111111” => y <= “111”;when”10111111” => y <= “110”;when”11011111” => y <= “101”;when”11101111” => y <= “100”;when”11110111” => y <= “011”;when”11111011” => y <= “010”;when”11111101” => y <= “001”;when”11111110” => y <= “000”;when others => y <= “xxx”;end case;end process;end behave;表5-1 优先级编码器的真值表例5-12LIBRARY ieee;USE prior isport( input: in std_logic_vector(7 downto 0);y: out std_logic_vector(2 downto 0)); end prior;architecture be_prior OF prior isbeginprocess(input)beginif(input(0)='0') theny<="111";elsif (input(1)='0') theny<="110";elsif (input(2)='0') theny<="101";elsif (input(3)='0') theny<="100";elsif (input(4)='0') theny<="011";elsif (input(5)='0') theny<="010";elsif (input(6)='0') theny<="001";elsey<="000";end if;end process;end be_prior;7. LOOP语句格式一:[标号]: FOR循环变量IN离散范围LOOP顺序处理语句;END LOOP [标号];例: ASUM: FOR i IN 1 TO 9 LOOPsum=1+sum;END LOOP ASUM;例5-13:8位奇偶校验电路LIBRARY IEEE;USE ENTITY pc ISPORT(a : IN STD_LOGIC_VECTOR(7 DOWNTO 0);y : OUT STD_LOGIC);END pc;ARCHITECTURE behave OF pc ISBEGINcbc: PROCESS(a)VARIABLE tmp: STD_LOGIC;BEGINtmp:='0';FOR i IN 0 TO 7 LOOPtmp:=tmp XOR a(i);END LOOP;y<=tmp;END PROCESS cbc;END behave;格式二:[标号]: WHILE 条件LOOP顺序处理语句;END LOOP [标号];在该语句中,如果条件为真,则进行循环,否则结束循环.例:I:=1;sum:=0abcd: WHILE (I<10) LOOPsum:=I+sum;I:=I+1;END LOOP abcd;例5-14:LIBRARY IEEE;USE ENTITY pc ISPORT(a : IN STD_LOGIC_VECTOR(7 DOWNTO 0);y : OUT STD_LOGIC);END pc;ARCHITECTURE behave OF pc ISBEGINcbc: PROCESS(a)VARIABLE tmp: STD_LOGIC;BEGINtmp:='0';i:=0;WHILE (i<8) LOOPtmp:=tmp XOR a(i);i=i+1;END LOOP;y<=tmp;END PROCESS cbc;END behave;8. NEXT语句在LOOP语句中用NEXT语句跳出循环.格式: NEXT [标号][WHEN 条件]; NEXT语句用于控制内循环的结束.例5-15:PROCESS (a,b)CONSTANT max_limit: INTEGER:=255 BEGINFOR I IN 0 TO max_limit LOOPIF (done(I)=TRUE) THENNEXT;ELSE done(I):=TRUE;END IF;q(I)<=a(I) AND b(I);END LOOP;END PROCESS;9. EXIT 语句EXIT语句用于结束LOOP循环状态.格式: EXIT [标号] [WHEN 条件]例5-16:PROCESS(a)VARIABLE int_a :INTEGER; BEGINint_a:=aFOR I=0 IN 0 TO max_limit LOOPIF (int_a<=0) THENEXIT;ELSEint_a:=int_a-1;q(I)<=REAL(a*I);END IFEND LOOP;y<=q;END PROCESS;二、并发描述语句1.进程语句在一个构造体中多个PROCESS语句可以同时并行的执行,该语句有如下特点:1)可以和其它进程语句同时执行,并可以存取构造体和实体中所定义的信号2)进程中的所有语句都按照顺序执行3)为启动进程,在进程中必须包含一个敏感信号表或WAIT语句4)进程之间的通信是通过信号量来实现的2.并发信号代入代入语句在进程中使用是顺序语句,但是在进程外即在构造体中使用就是并发语句,相当于一个进程.例:ARCHITECTURE behave OF a_var ISBEGINOutput<=a(I);END behave;可以等效于:ARCHITECTURE behave OF a_var ISBEGINss PROCESS(a,I)BEGINOutput<=a(I);END PROCESS ss;END behave;信号代入语句的右边可以是算数表达式,也可以是逻辑表达式,还可以是关系表达式,所以可以仿真加法器、乘法器、除法器、比较器和各种逻辑电路。