常见IO电平标准

- 格式:pdf

- 大小:87.40 KB

- 文档页数:2

FPGA的IO引脚电平以及驱动电流设置的影响问题FPGA IO驱动能⼒设置对设计的影响FPGA有各种逻辑电平输出标准信号,包括1.2V1.8V以及3.3V理论上⽽⾔可以通过改变IO输出电平的设置改变输出,但实际上并不能因此达到要求,需要改变电路板⼦上的跳线帽才能修改该电平,此外修改IO的驱动电流或者IO输出电平,能够达到改变驱动波形的输出。

最近调试⼀个FPGA设计,其实也是⽼的设计,以前已经调试通了,这次只是有⼀些⼩的更新。

但是在调试的过程中发现虽然⼤的功能上没有什么问题了,但是设计的可靠性⼤打折扣,经常在负荷⽐较⼤的时候就down掉了。

苦苦调试未果,因为实在是发现不了有什么问题了。

本⽂来源于,版权所有,转载请注明。

后来⽤逻辑分析仪查看IO⼝上的波形发现,原本应该是⼲净的数据波形的IO上,出现了很多⽑刺。

如图1所⽰。

图1中上⾯波形是期望的波形,⽽下⾯的波形是实际从逻辑分析仪中看到的波形。

由于波形不⼲净从⽽导致判别电路产⽣误判,导致电路失效。

分析了⼀下,可能是IO的驱动能⼒不够导致线上的电平不能马上到达期望的波形,从⽽产⽣抖动。

⼜仔细看了下以前的设计,发现原来的设计中IO的驱动能⼒设置为24mA,⽽新的设计中没有相关设置,采⽤的是默认的12mA。

尝试改了驱动能⼒,再次Implementate设计、上机试验、OK。

看来以后的设计中还是需要注意下IO的驱动能⼒啊。

后注:后来⽤⽰波器看了⼀下IO上的波形,当驱动能⼒为12mA时的近端波形如图2所⽰:从图2波形可以看到:在上升沿和下降沿的中间由于信号的反射导致电平在阈值附近震荡,从⽽出现了前⾯在逻辑分析仪中看到的波形。

后⼜看了下将驱动能⼒设为24mA时的近端波形,如图3所⽰:图3中可以看到反射虽然依然存在,但位置有所变动,已经离开了中间的敏感区域,从⽽可以在逻辑分析仪中得到⼲净的波形。

这也解释了为什么设计会受到IO驱动能⼒的影响。

想要彻底的消除近端反射,同时保证在远端可以信号的信号质量,⽬前还没想到什么办法,看来只有修改设计,避免设计在向外Drive总线时,同时直接检测IO上的波形。

一些电平标准下面总结一下各电平标准,和新手以及有需要的人共享一下^_^.现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVTTL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

3.3V LVTTL:Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

2.5V LVTTL:Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。

更低的LVTTL不常用就先不讲了。

多用在处理器等高速芯片,使用时查看芯片手册就OK了。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻; TTL电平输入脚悬空时是内部认为是高电平。

要下拉的话应用1k以下电阻下拉。

TTL输出不能驱动CMOS输入。

CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。

Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。

对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

逻辑电平高低电平标准TTL:Transistor-TransistorLogic三极管结构。

Vcc:5V;VOH=2.4V;VOL=0.5V;VIH=2V;VIL=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分"砍"掉了。

也就是后面的LVTTL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(LowVoltageTTL)。

3.3VLVTTL:Vcc:3.3V;VOH=2.4V;VOL=0.4V;VIH=2V;VIL=0.8V。

2.5VLVTTL:Vcc:2.5V;VOH=2.0V;VOL=0.2V;VIH=1.7V;VIL=0.7V。

更低的LVTTL不常用就先不讲了。

多用在处理器等高速芯片,使用时查看芯片手册就OK了。

TTL使用注意:TTL电平一般过冲都会比较严重,可在始端串22欧或33欧电阻,TTL电平输入脚悬空时内部认为是高电平。

要下拉的话应用1k以下电阻下拉。

TTL输出不能驱动CMOS输入。

CMOS:ComplementaryMetalOxideSemiconductorPMOS+NMOS。

Vcc:5V;VOH=4.45V;VOL=0.5V;VIH=3.5V;VIL=1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。

对应3.3VLVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

3.3VLVCMOS:Vcc:3.3V;VOH=3.2V;VOL=0.1V;VIH=2.0V;VIL=0.7V。

2.5VLVCMOS:Vcc:2.5V;VOH=2V;VOL=0.1V;VIH=1.7V;VIL=0.7V。

CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

FPGA的电平标准

FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,它可以通过重新编程来实现不同的逻辑功能。

在FPGA中,电平标准通常是指输入/输出端口所需的电压和电流等级。

以下是一些常见的FPGA电平标准:

1. LVDS(Low V oltage Differential Signaling):一种低电压差分信号传输标准,常用于高速串行通信和数字视频传输。

2. LVDS-25:一种低电压差分信号传输标准,常用于高速串行通信和数字视频传输。

3. LVCMOS(Low V oltage CMOS):一种低电压CMOS 信号传输标准,常用于数字电路和存储器接口。

4. DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory):一种高速存储器接口标准,常用于计算机内存接口。

5. SPI(Serial Peripheral Interface):一种串行通信协议,常用于嵌入式系统和传感器接口。

6. I2C(Inter-Integrated Circuit):一种串行通信协议,常用于嵌入式系统和传感器接口。

7. UART(Universal Asynchronous Receiver/Transmitter):一种串行通信协议,常用于嵌入式系统和计算机接口。

8. HDL(Hardware Description Language):一种硬件描述

语言,用于编写FPGA的硬件描述语言程序。

总之,不同的FPGA电平标准适用于不同的应用场景,设计者需要根据具体情况选择合适的电平标准。

电平标准分类要了解逻辑电平的内容,首先要知道以下几个概念的含义:1:输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

2:输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

3:输出高电平(V oh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此V oh。

4:输出低电平(V ol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此V ol。

5:阀值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。

它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> Vih,输入低电平<Vil,而如果输入电平在阈值上下,也就是Vil~Vih这个区域,电路的输出会处于不稳定状态。

对于一般的逻辑电平,以上参数的关系如下:V oh > Vih > Vt > Vil > V ol。

6:Ioh:逻辑门输出为高电平时的负载电流(为拉电流)。

7:Iol:逻辑门输出为低电平时的负载电流(为灌电流)。

8:Iih:逻辑门输入为高电平时的电流(为灌电流)。

9:Iil:逻辑门输入为低电平时的电流(为拉电流)。

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。

开路的TTL、CMOS、ECL门分别称为集电极开路(OC)、漏极开路(OD)、发射极开路(OE),使用时应审查是否接上拉电阻(OC、OD门)或下拉电阻(OE门),以及电阻阻值是否合适。

对于集电极开路(OC)门,其上拉电阻阻值RL应满足下面条件:(1):RL < (VCC-V oh)/(n*Ioh+m*Iih)(2):RL > (VCC-V ol)/(Iol+m*Iil)其中n:线与的开路门数;m:被驱动的输入端数。

51单片机io口输出低电平,但接了lcd后变成高电平1.引言1.1 概述概述部分的内容可以如下所示:在当前的电子设备应用中,单片机(Microcontroller)作为一种常见的电子控制器件,被广泛应用于各个领域。

而51单片机作为一种经典的单片机系列,也被广泛使用。

在使用51单片机进行控制时,IO口的控制是必不可少的一部分。

然而,在实际应用中,有时我们会遇到一些奇怪的问题。

比如,当我们将51单片机的IO口设置为输出低电平时,但是当我们接上LCD液晶显示屏之后,电平却变成了高电平,这究竟是为什么呢?本文将会对这个问题进行深入的探讨和分析。

首先,我们将介绍51单片机的IO口输出低电平的原理和应用场景。

然后,我们将会详细讨论当我们接上LCD液晶显示屏后,为什么IO口的电平会发生变化,其原因是什么。

通过本文的研究和分析,我们旨在帮助读者更好地理解51单片机的IO口输出低电平和LCD接口之间的关系,并引导读者解决此类问题时采取合适的措施。

接下来,我们将会从两个方面展开讨论。

首先,我们将介绍51单片机IO口输出低电平的基本原理和相关知识。

随后,我们将探讨当我们接上LCD液晶显示屏后,为什么IO口的电平会变为高电平。

通过本文的研究和分析,我们旨在帮助读者更好地理解这个问题,并提供一些解决方案,从而使读者能够更加顺利地进行51单片机与LCD液晶显示屏的接口设计和开发工作。

欢迎阅读本文,希望能为您带来有益的信息和启发。

1.2文章结构文章结构部分的内容可以包括以下内容:在本文中,将按照以下结构来描述和分析51单片机IO口输出低电平接上LCD后电平变高的现象。

首先,将在引言部分概述本文的主题和目的。

接下来,在正文部分,将详细介绍和解释51单片机IO口输出低电平的原理和机制,并通过实例来说明。

然后,将进一步探讨接上LCD后电平变高的原因,包括可能存在的电路连接问题和信号干扰等因素。

最后,在结论部分将总结全文的主要观点和结论,并进行结果分析和讨论。

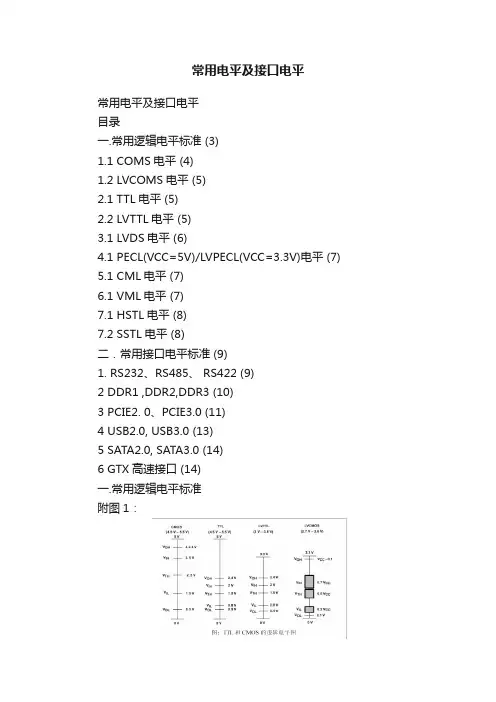

常用电平及接口电平常用电平及接口电平目录一.常用逻辑电平标准 (3)1.1 COMS电平 (4)1.2 LVCOMS电平 (5)2.1 TTL电平 (5)2.2 LVTTL电平 (5)3.1 LVDS电平 (6)4.1 PECL(VCC=5V)/LVPECL(VCC=3.3V)电平 (7)5.1 CML电平 (7)6.1 VML电平 (7)7.1 HSTL电平 (8)7.2 SSTL电平 (8)二.常用接口电平标准 (9)1. RS232、RS485、 RS422 (9)2 DDR1 ,DDR2,DDR3 (10)3 PCIE2. 0、PCIE3.0 (11)4 USB2.0, USB3.0 (13)5 SATA2.0, SATA3.0 (14)6 GTX高速接口 (14)一.常用逻辑电平标准附图1:附图2:附图3:附图4:1.1 COMS电平电平参数条件最大值典型值最小值单位备注电源电压(VCC) 5.5 5 4.5 V输入高压(VIH) 3.5 V输入低压(VIL) 1.5 V输出高压(VOH) 4.44 V输出低压(VOL)0.5 V共模电压(VT) 2.5 V传输延迟时间(25-50ns)最高速率耦合方式1.2 LVCOMS电平LVCOMS电平参数条件最大值典型值最小值单位备注电源电压(VCC) 3.6 3.3 2.7 V输入高压(VIH)0.7VCC V输入低压(VIL) 0.2VCC V输出高压(VOH) VCC-0.1 V输出低压(VOL)0.1 V共模电压(VT)0.5VCC V最高速率耦合方式2.1 TTL电平电平参数条件最大值典型值最小值单位备注电源电压(VCC) 5.5 5 4.5 V输入高压(VIH) 2 V输入低压(VIL) 0.8 V输出高压(VOH) 2.4 V输出低压(VOL)0.5 V共模电压(VT) 1.5 V传输延迟时间(5-10ns),最高速率耦合方式2.2 LVTTL电平电平参数条件最大值典型值最小值单位备注电源电压(VCC)3.6 3.3 3 V 输入高压(VIH)2 V 输入低压(VIL) 0.8 V 输出高压(VOH) 2.4 V 输出低压(VOL)0.4 V 共模电压(VT) 1.5 V 最高速率耦合方式3.1 LVDS电平最高速率:3.125Gbps耦合方式:4.1 PECL(VCC=5V)/LVPECL(VCC=3.3V)电平最高速率:LVPECL为10+Gbps耦合方式:5.1 CML电平最高速率:10+Gbps耦合方式:VCC相同时CML与CML之间采用直流耦合,VCC不同时CML与CML 之间采用交流耦合6.1 VML电平电平参数条件最大值典型值最小值单位备注电源电压(VCC)V输入高压(VIH)V输入低压(VIL) V输出高压(VOH) 1.65 V输出低压(VOL) 0.85 V共模电压(VT) 1.25 V最高速率耦合方式VML电平与LVDS电平兼容,TLK2711输出是VML 电平。

不是很明白你问的内容。

在没有任何操作的情况下,STM32通用推挽输出模式的引脚默认低电平,也就是有电的状态。

所以在配置的时候通常会先把引脚的电平设置拉高,让电路不产生电流。

有电到没电这一过程也就是引脚电平从低到高的过程。

细化到电路上,拿LED做例子,LED都是一端连在STM32引脚这边,另一端连在n 伏的电压上对吧。

有电压这边肯定是高电平的,当STM32引脚为低电平时就会与电压这边的高电平产生电流,成为有电状态。

当STM32引脚的电平由低电平改为高电平后自然就无法再与电压那边的高电平产生电流,也就变为没电状态了。

stm32复位后I/O口电平状态STM32上电复位瞬间I/O口的电平状态默认是浮空输入,因此是高阻。

做到低功耗.STM32的IO管脚配置口默认为浮空输入,把选择权留给用户,这是一个很大的优势:一方面浮空输入确保不会出现用户不希望的默认电平(此时电平取决于用户的外围电路);另一方面降低了功耗,因为不管是上拉还是下拉,都会有电流消耗。

从另一个角度来看,不管I/O管脚的默认配置如何,还是需要在输出的管脚外加上拉或下拉,这是为了保证芯片上电期间和复位时,输出的管脚始终处于已知的电平。

─ 输入浮空─ 输入上拉─ 输入下拉─ 模拟输入─ 开漏输出─ 推挽式输出─ 推挽式复用功能─ 开漏复用功能IO端口复位后处于浮空状态,也就是其电平状态由外围电路决定,这很重要,如果设计工业品的话,这是必须要确定的;IO引脚可以兼容5V电源;文案编辑词条B 添加义项?文案,原指放书的桌子,后来指在桌子上写字的人。

现在指的是公司或企业中从事文字工作的职位,就是以文字来表现已经制定的创意策略。

文案它不同于设计师用画面或其他手段的表现手法,它是一个与广告创意先后相继的表现的过程、发展的过程、深化的过程,多存在于广告公司,企业宣传,新闻策划等。

基本信息中文名称文案外文名称Copy目录1发展历程2主要工作3分类构成4基本要求5工作范围6文案写法7实际应用折叠编辑本段发展历程汉字"文案"(wén àn)是指古代官衙中掌管档案、负责起草文书的幕友,亦指官署中的公文、书信等;在现代,文案的称呼主要用在商业领域,其意义与中国古代所说的文案是有区别的。

常用电平标准:现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管逻辑。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVTTL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

3.3V LVTTL:Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

2.5V LVTTL:Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。

更低的LVTTL不常用就先不讲了。

多用在处理器等高速芯片,使用时查看芯片手册就OK了。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;TTL电平输入脚悬空时是内部认为是高电平。

要下拉的话应用1k 以下电阻下拉。

TTL输出不能驱动CMOS输入。

CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。

Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。

对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

数字信号的标准现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

一、TTL电平TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

TTL集成电路的全名是晶体管-晶体管逻辑集成电路(Transistor-Transistor Logic),主要有54/74系列标准TTL、高速型TTL(H-TTL)、低功耗型TTL(L-TTL)、肖特基型TTL(S-TTL)、低功耗肖特基型TTL(LS-TTL)五个系列。

1.标准TTL输入高电平最小2V,输出高电平最小2.4V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V(输入H>2V,输入L>0.8V;输出L=3.4V,输出L=0.2)。

2.S-TTL输入高电平最小2V,输出高电平最小Ⅰ类2.5V,Ⅱ、Ⅲ类2.7V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.5V。

3.LS-TTL输入高电平最小2V,输出高电平最小Ⅰ类2.5V,Ⅱ、Ⅲ类2.7V,典型值3.4V,输入低电平最大Ⅰ类0.7V,Ⅱ、Ⅲ类0.8V,输出低电平最大Ⅰ类0.4V,Ⅱ、Ⅲ类0.5V,典型值0.25V。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

单片机io脚电平

单片机的IO脚电平主要分为以下两种:

1. 高电平:高电平指的是IO脚的电压大于供电电压的70%。

在单片机中,高电平通常表示逻辑1,用于表示某个信号或数据的状态。

2. 低电平:低电平指的是IO脚的电压小于供电电压的30%。

在单片机中,低电平通常表示逻辑0,用于表示某个信号或数据的状态。

在单片机中,通常有一个称为GPIO(General Purpose Input/Output)的寄存器用于控制IO管脚的工作模式和电平状态。

通过对GPIO寄存器的配置,可以设置IO管脚为输入模式或输出模式,并可以设置IO管脚的电平状态为高电平(1)或低电平(0)。

对于输入模式的IO管脚,单片机会通过GPIO寄存器读取外部设备的电平状态。

当外部设备将信号引脚连接到IO管脚时,单片机可以读取该引脚的电平值,并根据需要进行相应的处理。

mcu io 默认电平MCU(Microcontroller Unit,微控制器单元)是一种集成了处理器核心、存储器和外设接口的芯片。

在MCU中,IO (Input/Output,输入/输出)是指芯片上的输入输出引脚,通过这些引脚可以实现与外部设备的数据交换和通信。

MCU IO默认电平是指在没有外部信号输入或输出时,IO引脚所处的电平状态。

默认电平可以是高电平(通常为Vcc,即芯片供电电压)或低电平(通常为0V,即接地)。

MCU IO默认电平的确定对于MCU的正常工作和外设的连接至关重要。

在MCU中,IO引脚的默认电平由芯片设计者在设计阶段决定,并通过芯片内部的电路实现。

通常,MCU的IO默认电平与芯片供电电压相关。

当MCU上电时,IO引脚会根据默认电平的设定自动处于相应的电平状态。

这种默认电平的设定可以是固定的,也可以是可编程的,以满足不同的应用需求。

MCU IO默认电平的设定对于MCU的应用和外设的连接具有重要的意义。

首先,不同的外设可能对IO引脚的默认电平有不同的要求。

如果外设要求MCU IO引脚的默认电平为高电平,而MCU的IO 引脚默认电平为低电平,就需要通过软件或硬件方式将IO引脚的默认电平进行转换。

其次,IO引脚默认电平的设定还会影响到与外设的数据交换和通信。

例如,如果IO引脚默认电平为高电平,那么与外设进行通信时,通常需要将IO引脚拉低来发送低电平信号。

为了正确使用MCU的IO引脚,默认电平的设定需要根据具体的应用需求进行调整。

在设计电路时,需要仔细考虑外设的要求,并根据外设的工作电平和信号传输方式来确定IO引脚的默认电平。

在编程时,还需要根据具体的应用逻辑来设置IO引脚的默认电平。

这样可以确保MCU与外设之间的数据交换和通信正常进行。

除了默认电平的设定,MCU的IO引脚还具有其他的功能和特性。

例如,IO引脚可以配置为输入模式或输出模式;可以设置为数字信号模式或模拟信号模式;还可以通过中断方式来处理外部事件。

fpga io电平标准

一般来讲,FPGA IO电平标准是由FPGA厂家或者模块的供应商指定的,而且可能会因为不同的设备而有所不同。

通常情况下,FPGA I/O电平标准可以有三个难度层次:18V,3.3V和2.5V。

具体标准由具体应用类型决定。

18V电平标准:

最常用的是18V电平,通常可以使用TTL电平(绿色或红色),高电平为+ 18V,低电平为- 18V。

3.3V电平标准:

使用3.3V电平标准大部分是以快速IO接口为主,如MIL-STD-1553,RS-485,ARRAY,UART,CAN,LPC接口等。

推荐使用Lvcmos 3.3V电平,通常只有高电平是+ 3.3V,没有负电平。

2.5V电平标准:

使用2.5V电平的情况比较少,主要应用在RS-232接口,CAN,TFT彩色液晶显示器等。

2.5V电平要求高电平为+ 2.5V,低电平为- 2.5V。

io电压范围

IO电压范围是指数字输入/输出(IO)接口所能接受或输出的

电压范围。

常见的IO电压范围分为两种类型:

1. TTL电平:TTL(Transistor to Transistor Logic)电平常见于

数字电路。

一般规定低电平(0)为0V至0.8V,高电平(1)为2.4V至5V。

这种电平通常适用于大多数晶体管电路。

2. CMOS电平:CMOS(Complementary Metal-Oxide-Semiconductor)电平也常见于数字电路。

一般规定低电平(0)为0V至0.3V,高电平(1)为

3.3V至5V。

这种电平通常适

用于低功耗的电路。

需要注意的是,不同的设备和接口可能有不同的电压要求和兼容性。

在使用IO接口时,应该根据设备的规格和要求来选择

合适的电平范围,以确保设备正常工作并避免损坏。

在fpga芯片中支持不同io电平标准2008-06-06 15:15:39| 分类:FPGA AND DSP | 标签:|字号大中小订阅I/O BankingSome of the I/O standards described above require VCCO and/or VREF voltages. These voltages are externally supplied and connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3). The pinout tables show the bank affiliation of eachI/O (see Pinout Tables, Module 4). Each bank has multiple VCCO pins which must be connected to the same voltage. Voltage requirements are determined by the output standards in use.In the TQ144 and PQ208 packages, the eight banks have VCCO connected together. Thus, only one VCCO level is allowed in these packages, although different VREF values are allowed in each of the eight banks.Within a bank, standards may be mixed only if they use the same VCCO. [在spartan IIE的这两种封装中,每一个bank的io电引脚是连在一起的,而参考电平引脚是在不同的bank中是独立的,也就是说在所有bank中只能有一个io电平,每一个bank可以有自己的电平。

芯片的io电压1.引言1.1 概述芯片的IO电压是指芯片内部与外部设备进行数据交互时所使用的电压水平。

在现代电子设备中,IO电压的选择和设计非常重要,因为它直接影响到芯片的性能和稳定性。

IO电压通常为芯片设计中的一个关键参数,其选择需要考虑多方面的因素。

首先,IO电压的选择要考虑到芯片的工作电压要求。

不同的芯片有不同的工作电压范围,而IO电压必须在芯片的工作电压范围内,以确保芯片正常工作。

如果IO电压过高或过低,可能导致芯片无法正常工作或损坏。

其次,IO电压的选择还要考虑到外部设备的兼容性。

外部设备和芯片之间进行数据交互时,需要保证两者的电压匹配。

如果IO电压和外部设备的电压不匹配,可能导致数据传输错误或损坏。

因此,在选择IO电压时,需要考虑与外部设备的兼容性,以确保可靠的数据传输。

此外,IO电压的选择还要考虑到功耗和信号完整性。

较高的IO电压可能导致较高的功耗,而较低的IO电压可能导致信号完整性问题。

在选择IO电压时,需要综合考虑功耗和信号完整性的要求,并进行平衡。

总之,IO电压在芯片设计中的选择要考虑到芯片的工作电压要求、外部设备的兼容性、功耗和信号完整性等多方面因素。

通过合理选择和设计IO电压,可以提高芯片的性能和稳定性,确保可靠的数据交互。

1.2文章结构文章结构部分简要介绍了整篇文章的组织方式和目录内容。

通过明确章节的标题和主要内容,读者可以对文章的结构和内容有一个整体的了解。

以下为文章结构部分的内容:在本文中,我们将围绕芯片的IO电压展开详细讨论。

首先,我们将在引言部分对文章的概述进行介绍,明确文章的背景和意义。

接下来,我们将在正文部分探讨IO电压的定义和它的重要性。

其中,我们将详细解释IO电压在芯片设计和工作中的角色和作用,以及对整个系统性能的影响。

在正文的第2.1节,我们将阐述IO电压的定义,包括其基本概念和相关参数的说明。

通过对IO电压的深入剖析,读者将更加清晰地了解IO电压在芯片电路中的具体含义。

cmos io 低电平认可电平【实用版】目录1.什么是 CMOS 电平?2.CMOS 电平与 TTL 电平的区别3.CMOS 电平的优点4.CMOS IO 口低电平认可电平的概念5.如何检测 CMOS IO 口的低电平认可电平6.总结正文一、什么是 CMOS 电平?CMOS 电平是指 CMOS(互补金属氧化物半导体)技术中,逻辑门输入和输出信号的电平标准。

CMOS 技术是一种用于制造集成电路的技术,其特点是低功耗、高噪声容限和稳定性。

二、CMOS 电平与 TTL 电平的区别CMOS 电平与 TTL(晶体管 - 晶体管逻辑)电平是两种不同的逻辑电平标准。

它们之间的主要区别在于电压范围和功耗:1.电压范围:CMOS 电平的电压范围较宽,通常为 3.5V 至 7V,而TTL 电平的电压范围为2.4V 至 5V。

2.功耗:CMOS 电路的功耗较低,因为 CMOS 晶体管的静态功耗几乎为零,而 TTL 电路的功耗相对较高。

三、CMOS 电平的优点CMOS 电平具有以下优点:1.低功耗:CMOS 晶体管的静态功耗几乎为零,因此,CMOS 电路的功耗相对较低。

2.高噪声容限:CMOS 技术具有较高的噪声容限,这意味着 CMOS 电路对噪声的容忍度更高。

3.稳定性:CMOS 技术具有较好的温度稳定性和电源电压稳定性。

4.宽电压范围:CMOS 电平的电压范围较宽,可以适应不同的电源电压环境。

四、CMOS IO 口低电平认可电平的概念CMOS IO口低电平认可电平是指CMOS输入/输出端口在低电平时,能够被其他电路识别和接受的最低电压值。

当CMOS IO 口的电压低于该值时,其他电路可以将其识别为低电平信号。

五、如何检测 CMOS IO 口的低电平认可电平要检测 CMOS IO 口的低电平认可电平,可以使用以下方法:1.使用万用表:将万用表的测量档位切换至电压档,并将红表笔连接到 IO 口的输出端,黑表笔连接到地。

常用I/O电平标准

2011-10-20

现在常用的电平标准有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。

下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

1. TTL(Transistor-Transistor Logic 三极管结构)

Vcc:5V;Voh >= 2.4V;Vol <= 0.5V;Vih >= 2V;Vil <= 0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。

所以后来就把一部分“砍”掉了。

也就是后面的LVTTL。

2. LVTTL(Low Voltage TTL)

LVTTL又分3.3V、2.5V以及更低电压的LVTTL。

l 3.3V LVTTL: Vcc:3.3V;Voh >= 2.4V;Vol <= 0.4V;Vih >= 2V;Vil <= 0.8V。

l 2.5V LVTTL: Vcc:2.5V;Voh >= 2.0V;Vol <= 0.2V;Vih >= 1.7V;Vil <= 0.7V。

更低的LVTTL不常用就先不讲了,多用在处理器等高速芯片,使用时查看芯片手册就OK 了。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻。

TTL电平输入脚悬空时内部认为是高电平。

要下拉的话应用1k以下电阻下拉。

TTL输出不能驱动CMOS输入。

3. CMOS(Complementary Metal Oxide Semiconductor MOS)

Vcc:5V;Voh >= 4.45V;Vol <= 0.5V;Vih >= 3.5V;Vil <= 1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。

对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL 直接相互驱动。

l 3.3V LVCMOS:Vcc:3.3V;Voh >= 3.2V;Vol <= 0.1V;Vih >= 2.0V;Vil <= 0.7V。

l 2.5V LVCMOS:Vcc:2.5V;Voh >= 2V;Vol <= 0.1V;Vih >= 1.7V;Vil <= 0.7V。

CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

4. ECL(Emitter Coupled Logic发射极耦合逻辑电路-差分结构)

Vcc = 0V;Vee = -5.2V;Voh = -0.88V;Vol = -1.72V;Vih = -1.24V;Vil = -1.36V。

速度快,驱动能力强,噪声小,很容易达到几百兆的应用。

但是功耗大,需要负电源。

为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL。

l PECL(Pseudo/Positive ECL)

Vcc = 5V;Voh = 4.12V;Vol = 3.28V;Vih = 3.78V;Vil = 3.64V 。

l LVPELC(Low Voltage PECL)

Vcc = 3.3V;Voh = 2.42V;Vol = 1.58V;Vih = 2.06V;Vil = 1.94V。

ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。

中间可用交流耦合、电阻网络或专用芯片进行转换。

以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。

(如多用于时钟的LVPECL:直流匹配时用130欧上拉,同时用82欧下拉;交流匹配时用82欧上拉,同时用130欧下拉。

但两种方式工作后直流电平都在1.95V左右。

)

前面的电平标准摆幅都比较大,为降低电磁辐射,同时提高开关速度又推出LVDS电平标准。

5. LVDS(Low Voltage Differential Signaling)

差分对输入输出,内部有一个恒流源3.5~4mA,在差分线上改变方向来表示0和1。

通过外部的100欧匹配电阻(并在差分线上靠近接收端)转换为±350mV的差分电平。

LVDS使用注意:可以达到600M以上,PCB要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm)。

100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。

下面的电平用的可能不是很多,由于篇幅关系,只简单做一下介绍。

如果感兴趣的话可以联系我。

6. CML

是内部做好匹配的一种电路,不需再进行匹配。

三极管结构,也是差分线,速度能达到3G以上。

只能点对点传输。

7. GTL

类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。

1.2V 电源供电。

l GTL:Vcc = 1.2V;Voh >= 1.1V;Vol <= 0.4V;Vih >= 0.85V;Vil <= 0.75V 。

l PGTL/GTL+: Vcc = 1.5V;Voh >= 1.4V;Vol <= 0.46V;Vih >= 1.2V;Vil <= 0.8V 。

8. HSTL

主要用于QDR存储器的一种电平标准:一般有V¬;CCIO = 1.8V和V¬;CCIO =1.5V。

和上面的GTL相似,输入为比较器结构,比较器一端接参考电平(VCCIO/2),另一端接输入信号。

对参考电平要求比较高(1%精度)。

9. SSTL

主要用于DDR存储器,与HSTL基本相同。

V¬;CCIO = 2.5V,输入为比较器结构,比较器一端接参考电平1.25V,另一端接输入信号。

对参考电平要求比较高(1%精度)。

HSTL和SSTL 大多用在300M以下。

10. RS232和RS485

RS232采用±12~15V供电,我们电脑后面的串口即为RS232标准。

+12V表示0,-12V表示1。

可以用MAX3232等专用芯片转换,也可以用两个三极管加一些外围电路进行反相和电压匹配。

RS485是一种差分结构,相对RS232有更高的抗干扰能力。

传输距离可以达到上千米。