LT1363CS8中文资料

- 格式:pdf

- 大小:257.24 KB

- 文档页数:12

General DescriptionThe MAX13080E–MAX13089E +5.0V, ±15kV ESD-protect-ed, RS-485/RS-422 transceivers feature one driver and one receiver. These devices include fail-safe circuitry,guaranteeing a logic-high receiver output when receiver inputs are open or shorted. The receiver outputs a logic-high if all transmitters on a terminated bus are disabled (high impedance). The MAX13080E–MAX13089E include a hot-swap capability to eliminate false transitions on the bus during power-up or hot insertion.The MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 250kbps. The MAX13083E/MAX13084E/MAX13085E also feature slew-rate-limited drivers but allow transmit speeds up to 500kbps. The MAX13086E/MAX13087E/MAX13088E driver slew rates are not limited, making transmit speeds up to 16Mbps possible. The MAX13089E slew rate is pin selectable for 250kbps,500kbps, and 16Mbps.The MAX13082E/MAX13085E/MAX13088E are intended for half-duplex communications, and the MAX13080E/MAX13081E/MAX13083E/MAX13084E/MAX13086E/MAX13087E are intended for full-duplex communica-tions. The MAX13089E is selectable for half-duplex or full-duplex operation. It also features independently programmable receiver and transmitter output phase through separate pins.The MAX13080E–MAX13089E transceivers draw 1.2mA of supply current when unloaded or when fully loaded with the drivers disabled. All devices have a 1/8-unit load receiver input impedance, allowing up to 256transceivers on the bus.The MAX13080E/MAX13083E/MAX13086E/MAX13089E are available in 14-pin PDIP and 14-pin SO packages.The MAX13081E/MAX13082E/MAX13084E/MAX13085E/MAX13087E/MAX13088E are available in 8-pin PDIP and 8-pin SO packages. The devices operate over the com-mercial, extended, and automotive temperature ranges.ApplicationsUtility Meters Lighting Systems Industrial Control Telecom Security Systems Instrumentation ProfibusFeatures♦+5.0V Operation♦Extended ESD Protection for RS-485/RS-422 I/O Pins±15kV Human Body Model ♦True Fail-Safe Receiver While Maintaining EIA/TIA-485 Compatibility ♦Hot-Swap Input Structures on DE and RE ♦Enhanced Slew-Rate Limiting Facilitates Error-Free Data Transmission(MAX13080E–MAX13085E/MAX13089E)♦Low-Current Shutdown Mode (Except MAX13081E/MAX13084E/MAX13087E)♦Pin-Selectable Full-/Half-Duplex Operation (MAX13089E)♦Phase Controls to Correct for Twisted-Pair Reversal (MAX13089E)♦Allow Up to 256 Transceivers on the Bus ♦Available in Industry-Standard 8-Pin SO PackageMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers________________________________________________________________Maxim Integrated Products 1Ordering Information19-3590; Rev 1; 4/05For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Selector Guide, Pin Configurations, and Typical Operating Circuits appear at end of data sheet.Ordering Information continued at end of data sheet.M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSDC ELECTRICAL CHARACTERISTICS(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.) (Note 1)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All Voltages Referenced to GND)Supply Voltage (V CC ).............................................................+6V Control Input Voltage (RE , DE, SLR,H/F , TXP, RXP)......................................................-0.3V to +6V Driver Input Voltage (DI)...........................................-0.3V to +6V Driver Output Voltage (Z, Y, A, B).............................-8V to +13V Receiver Input Voltage (A, B)....................................-8V to +13V Receiver Input VoltageFull Duplex (A, B)..................................................-8V to +13V Receiver Output Voltage (RO)....................-0.3V to (V CC + 0.3V)Driver Output Current.....................................................±250mAContinuous Power Dissipation (T A = +70°C)8-Pin SO (derate 5.88mW/°C above +70°C).................471mW 8-Pin Plastic DIP (derate 9.09mW/°C above +70°C).....727mW 14-Pin SO (derate 8.33mW/°C above +70°C)...............667mW 14-Pin Plastic DIP (derate 10.0mW/°C above +70°C)...800mW Operating Temperature RangesMAX1308_EC_ _.................................................0°C to +75°C MAX1308_EE_ _..............................................-40°C to +85°C MAX1308_EA_ _............................................-40°C to +125°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________3DC ELECTRICAL CHARACTERISTICS (continued)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.) (Note 1)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 4_______________________________________________________________________________________DRIVER SWITCHING CHARACTERISTICSMAX13080E/MAX13081E/MAX13082E/MAX13089E WITH SRL = UNCONNECTED (250kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13080E/MAX13081E/MAX13082E/MAX13089E WITH SRL = UNCONNECTED (250kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________5DRIVER SWITCHING CHARACTERISTICSMAX13083E/MAX13084E/MAX13085E/MAX13089E WITH SRL = V CC (500kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13083E/MAX13084E/MAX13085E/MAX13089E WITH SRL = V CC (500kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 6_______________________________________________________________________________________DRIVER SWITCHING CHARACTERISTICSMAX13086E/MAX13087E/MAX13088E/MAX13089E WITH SRL = GND (16Mbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13086E/MAX13087E/MAX13088E/MAX13089E WITH SRL = GND (16Mbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)Note 2:∆V OD and ∆V OC are the changes in V OD and V OC , respectively, when the DI input changes state.Note 3:The short-circuit output current applies to peak current just prior to foldback current limiting. The short-circuit foldback outputcurrent applies during current limiting to allow a recovery from bus contention.MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________70.800.901.501.101.001.201.301.401.60-40-10520-253550958011065125SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (m A )0201040305060021345OUTPUT CURRENTvs. RECEIVER OUTPUT-HIGH VOLTAGEM A X 13080E -89E t o c 02OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )20104030605070021345OUTPUT CURRENTvs. RECEIVER OUTPUT-LOW VOLTAGEM A X 13080E -89E t o c 03OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )4.04.44.24.84.65.25.05.4RECEIVER OUTPUT-HIGH VOLTAGEvs. TEMPERATURETEMPERATURE (°C)O U T P U T H I G H V O L T A G E (V )-40-10520-2535509580110651250.10.70.30.20.40.50.60.8RECEIVER OUTPUT-LOW VOLTAGEvs. TEMPERATURETEMPERATURE (°C)O U T P U T L O W V O L T A G E (V )-40-10520-25355095801106512502040608010012014016012345DRIVER DIFFERENTIAL OUTPUT CURRENT vs. DIFFERENTIAL OUTPUT VOLTAGEDIFFERENTIAL OUTPUT VOLTAGE (V)D I F FE R E N T I A L O U T P U T C U R R E N T (m A )2.02.82.43.63.24.44.04.8DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs. TEMPERATURED I F FE R E N T I A L O U T P U T V O L T A G E (V )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140180160200-7-5-4-6-3-2-1012354OUTPUT CURRENT vs. TRANSMITTEROUTPUT-HIGH VOLTAGEOUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )60402080100120140160180200042681012OUTPUT CURRENT vs. TRANSMITTEROUTPUT-LOW VOLTAGEOUTPUT-LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )Typical Operating Characteristics(V CC = +5.0V, T A = +25°C, unless otherwise noted.)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 8_______________________________________________________________________________________21543679810SHUTDOWN CURRENT vs. TEMPERATUREM A X 13080E -89E t o c 10S H U T D O W N C U R R E N T (µA )-40-10520-253550958011065125TEMPERATURE (°C)600800700100090011001200DRIVER PROPAGATION DELAY vs. TEMPERATURE (250kbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)300400350500450550600DRIVER PROPAGATION DELAY vs. TEMPERATURE (500kbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)1070302040506080DRIVER PROPAGATION DELAY vs. TEMPERATURE (16Mbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140160180RECEIVER PROPAGATION DELAYvs. TEMPERATURE (250kpbs AND 500kbps)R E C E I V E R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140160180RECEIVER PROPAGATION DELAYvs. TEMPERATURE (16Mbps)R EC E I V E R P R O P A G AT I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)2µs/div DRIVER PROPAGATION DELAY (250kbps)DI 2V/divV Y - V Z 5V/divR L = 100Ω200ns/divRECEIVER PROPAGATION DELAY(250kbps AND 500kbps)V A - V B 5V/divRO 2V/divTypical Operating Characteristics (continued)(V CC = +5.0V, T A = +25°C, unless otherwise noted.)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________9Test Circuits and Waveforms400ns/divDRIVER PROPAGATION DELAY (500kbps)DI 2V/divR L = 100ΩV Y - V Z 5V/div10ns/div DRIVER PROPAGATION DELAY (16Mbps)DI 2V/divR L = 100ΩV Y 2V/divV Z 2V/div40ns/divRECEIVER PROPAGATION DELAY (16Mbps)V B 2V/divR L = 100ΩRO 2V/divV A 2V/divTypical Operating Characteristics (continued)(V CC = +5.0V, T A = +25°C, unless otherwise noted.)Figure 2. Driver Timing Test CircuitM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 10______________________________________________________________________________________Test Circuits and Waveforms (continued)Figure 4. Driver Enable and Disable Times (t DHZ , t DZH , t DZH(SHDN))DZL DLZ DLZ(SHDN)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversTest Circuits and Waveforms (continued)Figure 6. Receiver Propagation Delay Test CircuitM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E/MAX13083E/MAX13086EMAX13081E/MAX13084E/MAX13086E/MAX13087EFunction TablesM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers MAX13082E/MAX13085E/MAX13088EFunction Tables (continued)MAX13089EDetailed Description The MAX13080E–MAX13089E high-speed transceivers for RS-485/RS-422 communication contain one driver and one receiver. These devices feature fail-safe circuit-ry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted, or when they are connected to a terminated transmission line with all dri-vers disabled (see the Fail-Safe section). The MAX13080E/MAX13082E/MAX13083E/MAX13085E/ MAX13086E/MAX13088E/MAX13089E also feature a hot-swap capability allowing line insertion without erroneous data transfer (see the Hot Swap Capability section). The MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflec-tions caused by improperly terminated cables, allowing error-free data transmission up to 250kbps. The MAX13083E/MAX13084E/MAX13085E also offer slew-rate limits allowing transmit speeds up to 500kbps. The MAX13086E/MAX13087E/MAX13088Es’ driver slew rates are not limited, making transmit speeds up to 16Mbps possible. The MAX13089E’s slew rate is selectable between 250kbps, 500kbps, and 16Mbps by driving a selector pin with a three-state driver.The MAX13082E/MAX13085E/MAX13088E are half-duplex transceivers, while the MAX13080E/MAX13081E/ MAX13083E/MAX13084E/MAX13086E/MAX13087E are full-duplex transceivers. The MAX13089E is selectable between half- and full-duplex communication by driving a selector pin (H/F) high or low, respectively.All devices operate from a single +5.0V supply. Drivers are output short-circuit current limited. Thermal-shutdown circuitry protects drivers against excessive power dissi-pation. When activated, the thermal-shutdown circuitry places the driver outputs into a high-impedance state.Receiver Input Filtering The receivers of the MAX13080E–MAX13085E, and the MAX13089E when operating in 250kbps or 500kbps mode, incorporate input filtering in addition to input hysteresis. This filtering enhances noise immunity with differential signals that have very slow rise and fall times. Receiver propagation delay increases by 25% due to this filtering.Fail-Safe The MAX13080E family guarantees a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver input threshold between -50mV and -200mV. If the differential receiver input voltage (A - B) is greater than or equal to -50mV, RO is logic-high. If (A - B) is less than or equal to -200mV, RO is logic-low. In the case of a terminated bus with all transmitters disabled, the receiv-er’s differential input voltage is pulled to 0V by the termi-nation. With the receiver thresholds of the MAX13080E family, this results in a logic-high with a 50mV minimumnoise margin. Unlike previous fail-safe devices, the-50mV to -200mV threshold complies with the ±200mVEIA/TIA-485 standard.Hot-Swap Capability (Except MAX13081E/MAX13084E/MAX13087E)Hot-Swap InputsWhen circuit boards are inserted into a hot or powered backplane, differential disturbances to the data buscan lead to data errors. Upon initial circuit board inser-tion, the data communication processor undergoes itsown power-up sequence. During this period, the processor’s logic-output drivers are high impedanceand are unable to drive the DE and RE inputs of these devices to a defined logic level. Leakage currents up to±10µA from the high-impedance state of the proces-sor’s logic drivers could cause standard CMOS enableinputs of a transceiver to drift to an incorrect logic level. Additionally, parasitic circuit board capacitance couldcause coupling of V CC or GND to the enable inputs. Without the hot-swap capability, these factors could improperly enable the transceiver’s driver or receiver.When V CC rises, an internal pulldown circuit holds DElow and RE high. After the initial power-up sequence,the pulldown circuit becomes transparent, resetting thehot-swap tolerable input.Hot-Swap Input CircuitryThe enable inputs feature hot-swap capability. At theinput there are two NMOS devices, M1 and M2 (Figure 9). When V CC ramps from zero, an internal 7µstimer turns on M2 and sets the SR latch, which alsoturns on M1. Transistors M2, a 1.5mA current sink, andM1, a 500µA current sink, pull DE to GND through a5kΩresistor. M2 is designed to pull DE to the disabledstate against an external parasitic capacitance up to100pF that can drive DE high. After 7µs, the timer deactivates M2 while M1 remains on, holding DE low against three-state leakages that can drive DE high. M1 remains on until an external source overcomes the required input current. At this time, the SR latch resetsand M1 turns off. When M1 turns off, DE reverts to a standard, high-impedance CMOS input. Whenever V CCdrops below 1V, the hot-swap input is reset.For RE there is a complementary circuit employing two PMOS devices pulling RE to V CC. MAX13080E–MAX13089E+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversM A X 13080E –M A X 13089EMAX13089E ProgrammingThe MAX13089E has several programmable operating modes. Transmitter rise and fall times are programma-ble, resulting in maximum data rates of 250kbps,500kbps, and 16Mbps. To select the desired data rate,drive SRL to one of three possible states by using a three-state driver: V CC , GND, or unconnected. F or 250kbps operation, set the three-state device in high-impedance mode or leave SRL unconnected. F or 500kbps operation, drive SRL high or connect it to V CC .F or 16Mbps operation, drive SRL low or connect it to GND. SRL can be changed during operation without interrupting data communications.Occasionally, twisted-pair lines are connected backward from normal orientation. The MAX13089E has two pins that invert the phase of the driver and the receiver to cor-rect this problem. F or normal operation, drive TXP and RXP low, connect them to ground, or leave them uncon-nected (internal pulldown). To invert the driver phase,drive TXP high or connect it to V CC . To invert the receiver phase, drive RXP high or connect it to V CC . Note that the receiver threshold is positive when RXP is high.The MAX13089E can operate in full- or half-duplex mode. Drive H/F low, leave it unconnected (internal pulldown), or connect it to GND for full-duplex opera-tion. Drive H/F high for half-duplex operation. In full-duplex mode, the pin configuration of the driver and receiver is the same as that of a MAX13080E. In half-duplex mode, the receiver inputs are internally connect-ed to the driver outputs through a resistor-divider. This effectively changes the function of the device’s outputs.Y becomes the noninverting driver output and receiver input, Z becomes the inverting driver output and receiver input. In half-duplex mode, A and B are still connected to ground through an internal resistor-divider but they are not internally connected to the receiver.±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electro-static discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX13080E family of devices have extra protection against static electricity. Maxim’s engineers have devel-oped state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD struc-tures withstand high ESD in all states: normal operation,shutdown, and powered down. After an ESD event, the MAX13080E–MAX13089E keep working without latchup or damage.ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX13080E–MAX13089E are characterized for protec-tion to the following limits:•±15kV using the Human Body Model•±6kV using the Contact Discharge method specified in IEC 61000-4-2ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body ModelFigure 10a shows the Human Body Model, and Figure 10b shows the current waveform it generates when dis-charged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest,which is then discharged into the test device through a 1.5k Ωresistor.IEC 61000-4-2The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX13080E family of devices helps you design equip-ment to meet IEC 61000-4-2, without the need for addi-tional ESD-protection components.+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversThe major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD with-stand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 10c shows the IEC 61000-4-2 model, and Figure 10d shows the current waveform for IEC 61000-4-2 ESD Contact Discharge test.Machine Model The machine model for ESD tests all pins using a 200pF storage capacitor and zero discharge resis-tance. The objective is to emulate the stress caused when I/O pins are contacted by handling equipment during test and assembly. Of course, all pins require this protection, not just RS-485 inputs and outputs.Applications Information256 Transceivers on the BusThe standard RS-485 receiver input impedance is 12kΩ(1-unit load), and the standard driver can drive up to 32-unit loads. The MAX13080E family of transceivers has a1/8-unit load receiver input impedance (96kΩ), allowingup to 256 transceivers to be connected in parallel on one communication line. Any combination of these devices,as well as other RS-485 transceivers with a total of 32-unit loads or fewer, can be connected to the line.Reduced EMI and ReflectionsThe MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to250kbps. The MAX13083E/MAX13084E/MAX13085Eoffer higher driver output slew-rate limits, allowing transmit speeds up to 500kbps. The MAX13089E withSRL = V CC or unconnected are slew-rate limited. WithSRL unconnected, the MAX13089E error-free data transmission is up to 250kbps. With SRL connected toV CC,the data transmit speeds up to 500kbps. MAX13080E–MAX13089E+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversM A X 13080E –M A X 13089ELow-Power Shutdown Mode (Except MAX13081E/MAX13084E/MAX13087E)Low-power shutdown mode is initiated by bringing both RE high and DE low. In shutdown, the devices typically draw only 2.8µA of supply current.RE and DE can be driven simultaneously; the devices are guaranteed not to enter shutdown if RE is high and DE is low for less than 50ns. If the inputs are in this state for at least 700ns, the devices are guaranteed to enter shutdown.Enable times t ZH and t ZL (see the Switching Characteristics section) assume the devices were not in a low-power shutdown state. Enable times t ZH(SHDN)and t ZL(SHDN)assume the devices were in shutdown state. It takes drivers and receivers longer to become enabled from low-power shutdown mode (t ZH(SHDN), t ZL(SHDN))than from driver/receiver-disable mode (t ZH , t ZL ).Driver Output ProtectionTwo mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention.The first, a foldback current limit on the output stage,provides immediate protection against short circuits over the whole common-mode voltage range (see the Typical Operating Characteristics ). The second, a thermal-shut-down circuit, forces the driver outputs into a high-imped-ance state if the die temperature exceeds +175°C (typ).Line LengthThe RS-485/RS-422 standard covers line lengths up to 4000ft. F or line lengths greater than 4000ft, use the repeater application shown in Figure 11.Typical ApplicationsThe MAX13082E/MAX13085E/MAX13088E/MAX13089E transceivers are designed for bidirectional data commu-nications on multipoint bus transmission lines. F igures 12 and 13 show typical network applications circuits. To minimize reflections, terminate the line at both ends in its characteristic impedance, and keep stub lengths off the main line as short as possible. The slew-rate-lim-ited MAX13082E/MAX13085E and the two modes of the MAX13089E are more tolerant of imperfect termination.Chip InformationTRANSISTOR COUNT: 1228PROCESS: BiCMOS+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversFigure 11. Line Repeater for MAX13080E/MAX13081E/MAX13083E/MAX13084E/MAX13086E/MAX13087E/MAX13089E in Full-Duplex Mode+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E–MAX13089EM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversPin Configurations and Typical Operating CircuitsMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers______________________________________________________________________________________21Pin Configurations and Typical Operating Circuits (continued)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 22______________________________________________________________________________________Ordering Information (continued)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers______________________________________________________________________________________23Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

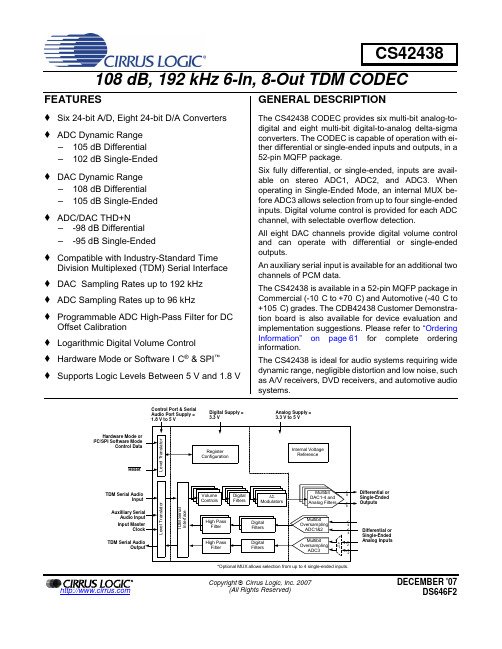

FEATURESSix 24-bit A/D, Eight 24-bit D/A Converters ADC Dynamic Range–105 dB Differential –102 dB Single-Ended DAC Dynamic Range–108 dB Differential –105 dB Single-Ended ADC/DAC THD+N–-98 dB Differential –-95 dB Single-EndedCompatible with Industry-Standard TimeDivision Multiplexed (TDM) Serial InterfaceDAC Sampling Rates up to 192 kHz ADC Sampling Rates up to 96 kHzProgrammable ADC High-Pass Filter for DCOffset CalibrationLogarithmic Digital Volume Control Hardware Mode or Software I²C ® & SPI ™ Supports Logic Levels Between 5V and 1.8VGENERAL DESCRIPTIONThe CS42438 CODEC provides six multi-bit analog-to-digital and eight multi-bit digital-to-analog delta-sigma converters. The CODEC is capable of operation with ei-ther differential or single-ended inputs and outputs, in a 52-pin MQFP package.Six fully differential, or single-ended, inputs are avail-able on stereo ADC1, ADC2, and ADC3. When operating in Single-Ended Mode, an internal MUX be-fore ADC3 allows selection from up to four single-ended inputs. Digital volume control is provided for each ADC channel, with selectable overflow detection.All eight DAC channels provide digital volume control and can operate with differential or single-ended outputs.An auxiliary serial input is available for an additional two channels of PCM data.The CS42438 is available in a 52-pin MQFP package in Commercial (-10°C to +70°C) and Automotive (-40°C to +105°C) grades. The CDB42438 Customer Demonstra-tion board is also available for device evaluation and implementation suggestions. Please refer to “Ordering Information” on page 61 for complete ordering information.The CS42438 is ideal for audio systems requiring wide dynamic range, negligible distortion and low noise, such as A/V receivers, DVD receivers, and automotive audio systems.CS42438TABLE OF CONTENTS1. PIN DESCRIPTIONS - SOFTWARE MODE (6)1.1 Digital I/O Pin Characteristics (8)2. PIN DESCRIPTIONS - HARDWARE MODE (9)3. TYPICAL CONNECTION DIAGRAMS (11)4. CHARACTERISTICS AND SPECIFICATIONS (13)RECOMMENDED OPERATING CONDITIONS (13)ABSOLUTE MAXIMUM RATINGS (13)ANALOG INPUT CHARACTERISTICS (COMMERCIAL) (14)ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE) (15)ADC DIGITAL FILTER CHARACTERISTICS (16)ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL) (17)ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE) (18)COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (20)SWITCHING SPECIFICATIONS - ADC/DAC PORT (21)SWITCHING CHARACTERISTICS - AUX PORT (22)SWITCHING SPECIFICATIONS - CONTROL PORT - I²C MODE (23)SWITCHING SPECIFICATIONS - CONTROL PORT - SPI FORMAT (24)DC ELECTRICAL CHARACTERISTICS (25)DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS (25)5. APPLICATIONS (26)5.1 Overview (26)5.2 Analog Inputs (27)5.2.1 Line-Level Inputs (27)5.2.1.1 Hardware Mode (27)5.2.1.2 Software Mode (27)5.2.2 ADC3 Analog Input (28)5.2.3 Hardware Mode (29)5.2.4 Software Mode (29)5.2.5 High-Pass Filter and DC Offset Calibration (29)5.2.5.1 Hardware Mode (29)5.2.5.2 Software Mode (29)5.3 Analog Outputs (30)5.3.1 Initialization (30)5.3.2 Line-Level Outputs and Filtering (30)5.3.3 Digital Volume Control (32)5.3.3.1 Hardware Mode (32)5.3.3.2 Software Mode (32)5.3.4 De-Emphasis Filter (32)5.4 System Clocking (33)5.4.1 Hardware Mode (33)5.4.2 Software Mode (33)5.5 CODEC Digital Interface (33)5.5.1 TDM (33)5.5.2 I/O Channel Allocation (34)5.6 AUX Port Digital Interface Formats (34)5.6.1 Hardware Mode (34)5.6.2 Software Mode (34)5.6.3 I²S (34)5.6.4 Left-Justified (35)5.7 Control Port Description and Timing (35)5.7.1 SPI Mode (35)5.7.2 I²C Mode (36)5.8 Recommended Power-Up Sequence (37)5.8.1 Hardware Mode (37)5.8.2 Software Mode (38)5.9 Reset and Power-Up (38)5.10 Power Supply, Grounding, and PCB Layout (38)6. REGISTER QUICK REFERENCE (39)7. REGISTER DESCRIPTION (41)7.1 Memory Address Pointer (MAP) (41)7.1.1 Increment (INCR) (41)7.1.2 Memory Address Pointer (MAP[6:0]) (41)7.2 Chip I.D. and Revision Register (Address 01h) (Read Only) (41)7.2.1 Chip I.D. (CHIP_ID[3:0]) (41)7.2.2 Chip Revision (REV_ID[3:0]) (41)7.3 Power Control (Address 02h) (42)7.3.1 Power Down ADC Pairs (PDN_ADCX) (42)7.3.2 Power Down DAC Pairs (PDN_DACX) (42)7.3.3 Power Down (PDN) (42)7.4 Functional Mode (Address 03h) (43)7.4.1 MCLK Frequency (MFREQ[2:0]) (43)7.5 Miscellaneous Control (Address 04h) (43)7.5.1 Freeze Controls (FREEZE) (43)7.5.2 Auxiliary Digital Interface Format (AUX_DIF) (43)7.6 ADC Control & DAC De-Emphasis (Address 05h) (44)7.6.1 ADC1-2 High-Pass Filter Freeze (ADC1-2_HPF FREEZE) (44)7.6.2 ADC3 High Pass Filter Freeze (ADC3_HPF FREEZE) (44)7.6.3 DAC De-Emphasis Control (DAC_DEM) (44)7.6.4 ADC1 Single-Ended Mode (ADC1 SINGLE) (44)7.6.5 ADC2 Single-Ended Mode (ADC2 SINGLE) (44)7.6.6 ADC3 Single-Ended Mode (ADC3 SINGLE) (45)7.6.7 Analog Input Ch. 5 Multiplexer (AIN5_MUX) (45)7.6.8 Analog Input Ch. 6 Multiplexer (AIN6_MUX) (45)7.7 Transition Control (Address 06h) (45)7.7.1 Single Volume Control (DAC_SNGVOL, ADC_SNGVOL) (45)7.7.2 Soft Ramp and Zero Cross Control (ADC_SZC[1:0], DAC_SZC[1:0]) (46)7.7.3 Auto-Mute (AMUTE) (46)7.7.4 Mute ADC Serial Port (MUTE ADC_SP) (47)7.8 DAC Channel Mute (Address 07h) (47)7.8.1 Independent Channel Mute (AOUTX_MUTE) (47)7.9 AOUTX Volume Control (Addresses 08h- 0Fh) (47)7.9.1 Volume Control (AOUTX_VOL[7:0]) (47)7.10 DAC Channel Invert (Address 10h) (48)7.10.1 Invert Signal Polarity (INV_AOUTX) (48)7.11 AINX Volume Control (Address 11h-16h) (48)7.11.1 AINX Volume Control (AINX_VOL[7:0]) (48)7.12 ADC Channel Invert (Address 17h) (49)7.12.1 Invert Signal Polarity (INV_AINX) (49)7.13 Status (Address 19h) (Read Only) (49)7.13.1 CLOCK ERROR (CLK ERROR) (49)7.13.2 ADC Overflow (ADCX_OVFL) (49)7.14 Status Mask (Address 1Ah) (49)8. EXTERNAL FILTERS (50)8.1 ADC Input Filter (50)8.1.1 Passive Input Filter (51)8.1.2 Passive Input Filter w/Attenuation (52)9. ADC FILTER PLOTS (54)10. DAC FILTER PLOTS (56)11. PARAMETER DEFINITIONS (58)12. REFERENCES (59)13. PACKAGE INFORMATION (60)13.1 Thermal Characteristics (60)14. ORDERING INFORMATION (61)15. REVISION HISTORY (61)LIST OF FIGURESFigure 1.Typical Connection Diagram (Software Mode) (11)Figure 2.Typical Connection Diagram (Hardware Mode) (12)Figure 3.Output Test Circuit for Maximum Load (19)Figure 4.Maximum Loading (19)Figure 5.TDM Serial Audio Interface Timing (21)Figure 6.Serial Audio Interface Slave Mode Timing (22)Figure 7.Control Port Timing - I²C Format (23)Figure 8.Control Port Timing - SPI Format (24)Figure 9.Full-Scale Input (28)Figure 10.ADC3 Input Topology (28)Figure 11.Audio Output Initialization Flow Chart (31)Figure 12.Full-Scale Output (32)Figure 13.De-Emphasis Curve (33)Figure 14.TDM Serial Audio Format (34)Figure 15.AUX I²S Format (34)Figure 16.AUX Left-Justified Format (35)Figure 17.Control Port Timing in SPI Mode (36)Figure 18.Control Port Timing, I²C Write (36)Figure 19.Control Port Timing, I²C Read (37)Figure 20.Single to Differential Active Input Filter (50)Figure 21.Single-Ended Active Input Filter (50)Figure 22.Passive Input Filter (51)Figure 23.Passive Input Filter w/Attenuation (52)Figure 24.Active Analog Output Filter (53)Figure 25.Passive Analog Output Filter (53)Figure 26.SSM Stopband Rejection (54)Figure 27.SSM Transition Band (54)Figure 28.SSM Transition Band (Detail) (54)Figure 29.SSM Passband Ripple (54)Figure 30.DSM Stopband Rejection (54)Figure 31.DSM Transition Band (54)Figure 32.DSM Transition Band (Detail) (55)Figure 33.DSM Passband Ripple (55)Figure 34.SSM Stopband Rejection (56)Figure 35.SSM Transition Band (56)Figure 36.SSM Transition Band (detail) (56)Figure 37.SSM Passband Ripple (56)Figure 38.DSM Stopband Rejection (56)Figure 39.DSM Transition Band (56)Figure 40.DSM Transition Band (detail) (57)Figure 41.DSM Passband Ripple (57)Figure 42.QSM Stopband Rejection (57)Figure 44.QSM Transition Band (detail) (57)Figure 45.QSM Passband Ripple (57)LIST OF TABLESTable 1. I/O Power Rails (8)Table 2. Hardware Configurable Settings (26)Table 3. AIN5 Analog Input Selection (29)Table 4. AIN6 Analog Input Selection (29)Table 5. MCLK Frequency Settings (33)Table 6. Serial Audio Interface Channel Allocations (34)Table 7. MCLK Frequency Settings (43)Table 8. Example AOUT Volume Settings (47)Table 9. Example AIN Volume Settings (48)1.PIN DESCRIPTIONS - SOFTWARE MODEPin Name#Pin DescriptionSCL/CCLK1Serial Control Port Clock (Input) - Serial clock for the control port interface.SDA/CDOUT2Serial Control Data I/O (Input/Output) - Input/Output for I²C data. Output for SPI data.AD0/CS3Address Bit [0]/ Chip Select (Input) - Chip address bit in I²C Mode. Control signal used to select the chip in SPI Mode.AD1/CDIN4Address Bit [1]/ SPI Data Input (Input) - Chip address bit in I²C Mode. Input for SPI data.RST5Reset (Input) - The device enters a low-power mode and all internal registers are reset to their default settings when low.VLC6Control Port Power (Input) - Determines the required signal level for the control port interface. See “Digital I/O Pin Characteristics” on page8.FS7Frame Sync (Input) - Signals the start of a new TDM frame in the TDM digital interface format. VD8Digital Power (Input) - Positive power supply for the digital section.DGND9,18Digital Ground (Input) -VLS10Serial Port Interface Power (Input) - Determines the required signal level for the serial port inter-faces. See “Digital I/O Pin Characteristics” on page8.SCLK11Serial Clock(Input) - Serial clock for the serial audio interface. Input frequency must be 256 x Fs. MCLK12Master Clock (Input) - Clock source for the delta-sigma modulators and digital filters.ADC_SDOUT13Serial Audio Data Output (Output) - TDM output for two’s complement serial audio data.DAC_SDIN14DAC Serial Audio Data Input (Input) - TDM Input for two’s complement serial audio data.AUX_LRCK15Auxiliary Left/Right Clock (Output) - Determines which channel, Left or Right, is currently active on the Auxiliary serial audio data line.AUX_SCLK16Auxiliary Serial Clock(Output) - Serial clock for the Auxiliary serial audio interface.AUX_SDIN17Auxiliary Serial Input (Input) - The 42438 provides an additional serial input for two’s comple-ment serial audio data.AOUT1 +,-AOUT2 +,-AOUT3 +,-AOUT4 +,-AOUT5 +,-AOUT6 +,-AOUT7 +,-AOUT8 +,-20,1921,2224,2325,2628,2729,3031,3233,34Differential Analog Output (Output) - The full-scale differential analog output level is specified in the Analog Characteristics specification table. Each positive leg of the differential outputs may also be used single-ended.AGND35,48Analog Ground (Input) - Ground reference for the analog section.VQ36Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage. VA37,46Analog Power (Input) - Positive power supply for the analog section.AIN1 +,-AIN2 +,-AIN3 +,-AIN4 +,-AIN5 +,-AIN6 +,-39,3841,4043,4245,4450,4952,51Differential Analog Input (Input) - Signals are presented differentially to the delta-sigma modula-tors. The full-scale input level is specified in the Analog Characteristics specification table. Single-ended inputs may be applied to the positive terminals when the ADCx SINGLE bit is enabled.Once in Single-Ended Mode, the negative terminal of AIN1-AIN4 must be externally driven tocommon mode. See below for a description of AIN5-AIN6 in Single-Ended Mode.AIN5 A,B AIN6 A,B 50,4952,51Single-Ended Analog Input (Input) - In Single-Ended Mode, an internal analog mux allowsselection between two channels for both analog inputs AIN5 and AIN6 (see Sections 7.6.6-7.6.8 for details). The unused leg of each input is internally connected to common mode. The full-scale input level is specified in the Analog Characteristics specification table.FILT+47Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling cir-cuits.1.1Digital I/O Pin CharacteristicsVarious pins on the CS42438 are powered from separate power supply rails. The logic level for each input should adhere to the corresponding power rail and should not exceed the maximum ratings.Power Rail Pin NameSW/(HW)I/O Driver ReceiverVLC RST Input- 1.8 V - 5.0 V, CMOS SCL/CCLK(AIN5_MUX)Input- 1.8 V - 5.0 V, CMOS, with HysteresisSDA/CDOUT (AIN6_MUX)Input/Output1.8 V - 5.0 V, CMOS/Open Drain 1.8 V - 5.0 V, CMOS, with HysteresisAD0/CS(MFREQ)Input- 1.8 V - 5.0 V, CMOS AD1/CDIN(ADC3_HPF)Input- 1.8 V - 5.0 V, CMOS VLS MCLK Input- 1.8 V - 5.0 V, CMOS LRCK Input- 1.8 V - 5.0 V, CMOSSCLK Input- 1.8 V - 5.0 V, CMOSADC_SDOUT3 (ADC3_SINGLE)Input/Output1.8 V - 5.0 V, CMOS-DAC_SDIN Input- 1.8 V - 5.0 V, CMOS AUX_LRCK Output 1.8 V - 5.0 V, CMOS-AUX_SCLK Output 1.8 V - 5.0 V, CMOS-AUX_SDIN Input- 1.8 V - 5.0 V, CMOSTable 1. I/O Power Rails2.Pin Name#Pin DescriptionAIN5_MUX AIN6_MUX 12Analog Input Multiplexer (Input) - Allows selection between the A and B single-ended inputs of ADC3.MFREQ3MCLK Frequency (Input) - Sets the required frequency range of the input Master Clock.ADC3_HPF4ADC3 High-Pass Filter Freeze (Input) - When this pin is driven high, the internal high-pass filter will be disabled for ADC3.The current DC offset value will be frozen and continue to be subtractedfrom the conversion result.RST5Reset (Input) - The device enters a low-power mode and all internal registers are reset to their default settings when low.VLC6Control Port Power (Input) - Determines the required signal level for the control port interface. See “Digital I/O Pin Characteristics” on page8.FS7Frame Sync (Input) - Signals the start of a new TDM frame in the TDM digital interface format. VD8Digital Power (Input) - Positive power supply for the digital section.DGND9,18Digital Ground (Input) - Ground reference for the digital section.VLS10Serial Port Interface Power (Input) - Determines the required signal level for the serial port inter-faces. See “Digital I/O Pin Characteristics” on page8.SCLK11Serial Clock(Input) - Serial clock for the serial audio interface. Input frequency must be 256 x Fs. MCLK12Master Clock (Input) - Clock source for the delta-sigma modulators and digital filters.ADC_SDOUT13Serial Audio Data Output (Output) - TDM output for two’s complement serial audio data.DAC_SDIN14DAC Serial Audio Data Input (Input) - TDM Input for two’s complement serial audio data.AUX_LRCK15Auxiliary Left/Right Clock (Output) - Determines which channel, Left or Right, is currently active on the Auxiliary serial audio data line.AUX_SCLK16Auxiliary Serial Clock(Output) - Serial clock for the Auxiliary serial audio interface.AUX_SDIN17Auxiliary Serial Input (Input) - The 42438 provides an additional serial input for two’s comple-ment serial audio data.AOUT1 +,-AOUT2 +,-AOUT3 +,-AOUT4 +,-AOUT5 +,-AOUT6 +,-AOUT7 +,-AOUT8 +,-20,1921,2224,2325,2628,2729,3032,31,33,34Differential Analog Output (Output) - The full-scale differential analog output level is specified in the Analog Characteristics specification table. Each positive leg of the differential outputs mayalso be used single-ended.AGND35,48Analog Ground (Input) - Ground reference for the analog section.VQ36Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage. VA37,46Analog Power (Input) - Positive power supply for the analog section.AIN1 +,-AIN2 +,-AIN3 +,-AIN4 +,-AIN5 +,-AIN6 +,-39,3841,4043,4245,4450,4952,51Differential Analog Input (Input) - Signals are presented differentially to the delta-sigma modula-tors. The full-scale input level is specified in the Analog Characteristics specification table. Single-ended inputs may be applied to the positive terminals when the ADCx SINGLE bit is enabled.Once in Single-Ended Mode, the negative terminal of AIN1-AIN4 must be externally driven tocommon mode. See below for a description of AIN5-AIN6 in Single-Ended Mode.AIN5 A,B AIN6 A,B 50,4952,51Single-Ended Analog Input (Input) - In Single-Ended Mode, an internal analog mux allowsselection between two channels for both analog inputs AIN5 and AIN6 (see Sections 7.6.6-7.6.8 for details). The unused leg of each input is internally connected to common mode. The full-scale input level is specified in the Analog Characteristics specification table.FILT+47Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling cir-cuits.3.TYPICAL CONNECTION DIAGRAMSFigure 1. Typical Connection Diagram (Software Mode)Figure 2. Typical Connection Diagram (Hardware Mode)4.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS(AGND=DGND=0 V, all voltages with respect to ground.)ABSOLUTE MAXIMUM RATINGS(AGND = DGND = 0 V; all voltages with respect to ground.)WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.Notes:1.Typical Analog input/output performance will slightly degrade at VA = 3.3 V.2.The ADC_SDOUT may not meet timing requirements in Double-Speed Mode.3.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not causeSCR latch-up.4.The maximum over/under voltage is limited by the input current.ParametersSymbol MinMax Units DC Power Supply Analog (Note 1)VA 3.14 5.25V Digital VD 3.14 3.47V Serial Audio Interface (Note 2)VLS 1.71 5.25V Control Port Interface VLC 1.71 5.25V Ambient TemperatureCommercial -CMZAutomotive -DMZT A-10-40+70+105°C °CParametersSymbol Min Max Units DC Power SupplyAnalogDigitalSerial Port Interface Control Port InterfaceVA VD VLS VLC -0.3-0.3-0.3-0.3 6.06.06.06.0V V V V Input Current(Note 3)I in -±10mA Analog Input Voltage (Note 4)V IN AGND-0.7VA+0.7V Digital Input Voltage Serial Port Interface (Note 4)Control Port InterfaceV IND-S V IND-C -0.3-0.3VLS+ 0.4VLC+ 0.4V V Ambient Operating Temperature (power applied)T A -50+125°C Storage TemperatureT stg-65+150°C(Test Conditions (unless otherwise specified): T A=-10to+70°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale input sine wave: 1 kHz through the active input filter in Figure 20 on page 50 and Figure 21 on page 50; Measurement Bandwidth is 10Hz to 20kHz.)Differential Single-EndedParameter Min Typ Max Min Typ Max Unit Fs=48 kHz, 96 kHzDynamic Range A-weightedunweighted40 kHz bandwidth unweighted 9996-10510299---96931029996---dBdBdBTotal Harmonic Distortion + Noise -1dB (Note 5) -20dB-60dB40 kHz bandwidth -1 dB -----98-82-42-90-92--------95-79-39-90-89---dBdBdBdBADC1-3 Interchannel Isolation-90--90-dB ADC3 MUX Interchannel Isolation-90--90-dB DC AccuracyInterchannel Gain Mismatch-0.1--0.1-dB Gain Drift-±100--±100-ppm/°C Analog InputFull-Scale Input Voltage 1.06*VA 1.12*VA 1.18*VA0.53*VA0.56*VA0.59*VA Vpp Differential Input Impedance (Notes 6 & 8)232932kΩSingle-Ended Input Impedance(Notes 7 & 8)---232932kΩCommon Mode Rejection Ratio (CMRR)-82----dB(Test Conditions (unless otherwise specified): T A =-40 to +85°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale input sine wave: 1 kHz through the active input filter in Figure 20 on page 50 and Figure 21 on page 50; Measurement Bandwidth is 10Hz to 20kHz.)Notes:5.Referred to the typical full-scale voltage.6.Measured between AINx+ and AINx-.7.Measured between AINxx and AGND.8.The input impedance scales inversely proportionate to the sample rate of the ADC modulatorDifferentialSingle-Ended ParameterMin Typ MaxMin Typ MaxUnitFs=48 kHz, 96 kHz Dynamic RangeA-weighted unweighted 40 kHz bandwidth unweighted 9794-10510299---9491-1029996---dB dBdBTotal Harmonic Distortion + Noise -1dB(Note 5) -20dB-60dB40 kHz bandwidth -1 dB-----98-82-42-87-90--------95-79-39-87-87---dB dB dB dB ADC1-3 Interchannel Isolation -90--90-dB ADC3 MUX Interchannel Isolation -85--85-dB DC AccuracyInterchannel Gain Mismatch -0.1--0.1-dB Gain Drift -±100--±100-ppm/°C Analog InputFull-Scale Input Voltage 1.04*VA 1.12*VA 1.20*VA 0.52*VA 0.56*VA 0.60*VA Vpp Differential Input Impedance (Notes 6 & 8)232932k ΩSingle-Ended Input Impedance(Notes 7 & 8)---232932k ΩCommon Mode Rejection Ratio (CMRR)-82----dBADC DIGITAL FILTER CHARACTERISTICSNotes:9.Filter response is guaranteed by design.10.Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 26to 33) havebeen normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.Parameter (Notes 9, 10)MinTypMaxUnitSingle-Speed Mode (Note 10)Passband (Frequency Response) to -0.1 dB corner0-0.4896Fs Passband Ripple --0.08dB Stopband0.5688--Fs Stopband Attenuation 70--dB Total Group Delay-12/Fs-sDouble-Speed Mode (Note 10)Passband (Frequency Response) to -0.1 dB corner0-0.4896Fs Passband Ripple --0.16dB Stopband0.5604--Fs Stopband Attenuation 69--dB Total Group Delay-9/Fs-sHigh-Pass Filter Characteristics Frequency Response -3.0 dB -0.13 dB -120--Hz Hz Phase Deviation @ 20Hz-10-Deg Passband Ripple --0dB Filter Settling Time -105/Fss(Test Conditions (unless otherwise specified): T A=-10 to +70°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale 997 Hz output sine wave (see Note 12) into passive filter in Figure 26 on page 54 and active filter in Fig-ure 26 on page 54; Measurement Bandwidth is 10Hz to 20kHz.)ParameterDifferentialMin Typ MaxSingle-EndedMin Typ Max UnitFs = 48 kHz, 96 kHz, 192 kHz Dynamic Range18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 10299--1081059996----9996--1051029693----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------98-85-45-93-76-36-92-----------95-82-42-90-73-33-89-----dBdBdBdBdBdBInterchannel Isolation (1 kHz)-100--100-dB Analog OutputFull-Scale Output 1.235•VA 1.300•VA 1.365•VA0.618•VA0.650•VA0.683•VA Vpp Interchannel Gain Mismatch-0.10.25-0.10.25dB Gain Drift-±100--±100-ppm/°C Output Impedance-100--100-ΩDC Current draw from an AOUT pin(Note 11)--10--10μA AC-Load Resistance (R L)(Note 13)3--3--kΩLoad Capacitance (C L)(Note 13)--100--100pF(Test Conditions (unless otherwise specified): T A =-40to +85°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale 997 Hz output sine wave (see Note 12) in Figure 26 on page 54 and Figure 26 on page 54; Measure-ment Bandwidth is 10Hz to 20kHz.)Notes:11.Guaranteed by design. The DC current draw represents the allowed current draw from the AOUT pindue to typical leakage through the electrolytic DC-blocking capacitors.12.One-half LSB of triangular PDF dither is added to data.13.Guaranteed by design. See Figure 3. R L and C L reflect the recommended minimum resistance andmaximum capacitance required for the internal op-amp's stability and signal integrity. In this circuit to-pology, C L will effectively move the dominant pole of the two-pole amp in the output stage. Increasing this value beyond the recommended 100 pF can cause the internal op-amp to become unstable. See “External Filters” on page 50 for a recommended output filter.ParameterDifferentialMin Typ MaxSingle-EndedMin Typ MaxUnitFs = 48 kHz, 96 kHz, 192 kHz Dynamic Range18 to 24-Bit A-weightedunweighted16-Bit A-weightedunweighted10097--1081059996----9794--1051029693----dB dB dB dB Total Harmonic Distortion + Noise18 to 24-Bit 0 dB-20 dB-60 dB16-Bit 0 dB-20 dB-60 dB-------98-85-45-93-76-36-90------------95-82-42-90-73-33-87-----dB dB dB dB dB dB Interchannel Isolation (1 kHz)-100--100-dBAnalog Output Full-Scale Output 1.210•VA 1.300•VA 1.392•VA 0.605•VA 0.650•VA 0.696•VA Vpp Interchannel Gain Mismatch -0.10.25-0.10.25dB Gain Drift -±100--±100-ppm/°C Output Impedance -100--100-ΩDC Current draw from an AOUT pin (Note 11)--10--10μAAC-Load Resistance (R L ) (Note 13)3--3--k ΩLoad Capacitance (C L )(Note 13)--100--100pFFigure 3. Output Test Circuit for Maximum Load Figure 4. Maximum LoadingCOMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSENotes:14.Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 34to 45) havebeen normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.15.Single- and Double-Speed Mode Measurement Bandwidth is from Stopband to 3 Fs.Quad-Speed Mode Measurement Bandwidth is from Stopband to 1.34 Fs.16.De-emphasis is only available in Single-Speed Mode.Parameter (Notes 9, 14)MinTypMaxUnitSingle-Speed ModePassband (Frequency Response)to -0.05dB corner to -3dB corner00--0.47800.4996Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.08dB StopBand0.5465--Fs StopBand Attenuation (Note 15)50--dB Group Delay-10/Fs -sDe-emphasis Error (Note 16)Fs = 32kHz Fs = 44.1 kHz Fs = 48 kHz------+1.5/+0+0.05/-0.25-0.2/-0.4dB dB dBDouble-Speed ModePassband (Frequency Response)to -0.1dB corner to -3dB corner00--0.46500.4982Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.7dB StopBand0.5770--Fs StopBand Attenuation (Note 15)55--dB Group Delay -5/Fs-sQuad-Speed ModePassband (Frequency Response)to -0.1dB corner to -3dB corner00--0.3970.476Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.05dB StopBand0.7--Fs StopBand Attenuation (Note 15)51--dB Group Delay - 2.5/Fs-sSWITCHING SPECIFICATIONS - ADC/DAC PORT(Inputs: Logic 0 = DGND, Logic 1 = VLS, ADC_SDOUT C LOAD = 15 pF.)Notes:17.After powering up the CS42438, RST should be held low after the power supplies and clocks are settled.18.See Table 7 on page 43 for suggested MCLK frequencies.19.VLS is limited to nominal 2.5 V to 5.0V operation only.20.ADC does not meet timing specification for Quad-Speed Mode.Parameters Symbol Min Max UnitsSlave ModeRST pin Low Pulse Width(Note 17)1-ms MCLK Frequency 0.51250MHz MCLK Duty Cycle(Note 18)4555%Input Sample Rate (FS pin)Single-Speed ModeDouble-Speed Mode (Note 19)Quad-Speed Mode (Note 20)F s F s F s 45010050100200kHz kHz kHz SCLK Duty Cycle 4555%SCLK High Time t sckh 8-ns SCLK Low Timet sckl 8-ns FS Rising Edge to SCLK Rising Edge t fss 5-ns SCLK Rising Edge to FS Falling Edget fsh 16-ns DAC_SDIN Setup Time Before SCLK Rising Edge t ds 3-ns DAC_SDIN Hold Time After SCLK Rising Edge t dh 5-ns DAC_SDIN Hold Time After SCLK Rising Edge t dh15-ns ADC_SDOUT Hold Time After SCLK Rising Edge t dh210-ns ADC_SDOUT Valid Before SCLK Rising Edget dval15-nsFigure 5. TDM Serial Audio Interface Timing。

W25Q64BV出版日期:2010年7月8日- 1 - 版本E64M位与串行闪存双路和四路SPIW25Q64BV- 2 -目录1,一般DESCRIPTION (5)2。

FEATURES (5)3引脚配置SOIC208-MIL.......................................... .. (6)4,焊垫配置WSON8X6-MM.......................................... . (6)5,焊垫配置PDIP300-MIL.......................................... . (7)6引脚说明SOIC208密耳,PDIP300密耳和WSON8X6-MM................................ 7......7引脚配置SOIC300mil的.......................................... .. (8)8引脚SOIC封装说明300-MIL (8)8.1包装Types (9)8.2片选(/CS) (9)8.3串行数据输入,输出和IO(DI,DO和IO0,IO1,IO2,IO3)............................. 9.......8.4写保护(/WP) (9)8.5控股(/HOLD) (9)8.6串行时钟(CLK) (9)9座DIAGRAM (10)10功能DESCRIPTION (11)10.1 SPI OPERATIONS (11)10.1.1标准SPI Instructions (11)10.1.2双SPI Instructions (11)10.1.3四路SPI Instructions (11)10.1.4保持功能 (11)10.2写保护 (12)10.2.1写保护Features (12)11,控制和状态寄存器............................................ .. (13)11.1状态REGISTER (13)11.1.1 BUSY (13)11.1.2写使能锁存(WEL) (13)11.1.3块保护位(BP2,BP1,BP0)..................................... .. (13)11.1.4顶/底块保护(TB)....................................... .................................................. ..1311.1.5部门/块保护(SEC) (13)11.1.6状态寄存器保护(SRP,SRP0)....................................... . (14)11.1.7四路启用(QE) (14)11.1.8状态寄存器内存保护........................................... .. (16)11.2 INSTRUCTIONS (17)11.2.1制造商和设备标识........................................... .. (17)11.2.2指令集表1 (18)W25Q64BV11.2.3指令表2(阅读说明书)....................................... (19)出版日期:2010年7月8日- 3 - 修订版E11.2.4写使能(06h) (20)11.2.5写禁止(04h) (20)11.2.6读状态寄存器1(05H)和读状态寄存器2(35H).............................. (21)11.2.7写状态寄存器(01H)......................................... .................................................. .. (22)11.2.8读取数据(03h) (23)11.2.9快速阅读(0Bh) (24)11.2.10快速读双输出(3BH)........................................ .................................................. 0.25 11.2.11快速读四路输出(6BH)........................................ .. (26)11.2.12快速读双I / O (BBh) (27)11.2.13快速读取四I/ O (EBh) (29)11.2.14八进制字读取四I/ O(E3H)..................................... (31)11.2.15页编程(02h) (33)11.2.16四路输入页编程(32H)........................................ . (34)11.2.17扇区擦除(20H) (35)11.2.1832KB的块擦除(52H) (36)11.2.1964KB的块擦除(D8h) (37)20年2月11日芯片擦除(C7H/ 60h) (38)21年2月11日擦除挂起(75h) (39)22年2月11日擦除恢复(7Ah) (40)23年11月2日掉电(B9h) (41)24年2月11日高性能模式(A3H)......................................... (42)25年2月11日发布掉电或高性能模式/设备ID(ABH) (42)26年2月11日读制造商/设备ID(90H)....................................... . (44)27年2月11日阅读唯一的ID号(4BH)........................................ . (45)28年2月11日读JEDEC的ID (9Fh) (46)29年2月11日连续读取模式复位(FFH或FFFFH)...................................... .. (47)12,电气特性.............................................. (48)12.1绝对最大Ratings (48)12.2操作范围 (48)12.3上电时序和写抑制阈值......................................... (49)12.4直流电气Characteristics (50)12.5 AC测量条件.............................................. .. (51)12.6 AC电气Characteristics (52)12.7 AC电气特性(续)......................................... . (53)12.8串行输出Timing (54)12.9输入Timing (54)12.10持有Timing (54)13包装SPECIFICATION (55)W25Q64BV13.18引脚SOIC208密耳(包装代号SS)..................................... .. (55)- 4 -13.28引脚PDIP300密耳(封装代码DA)..................................... (56)13.38触点WSON8x6毫米(封装代码ZE)....................................... (57)13.416引脚SOIC300密耳(封装代码SF)..................................... . (58)14订货INFORMA TION (59)14.1有效的部件号和顶端标记.......................................... (60)15版本HISTORY (61)W25Q64BV出版日期:2010年7月8日- 5 - 修订版E1概述该W25Q64BV(64M位)串行Flash存储器提供了有限的系统存储解决方案空间,引脚和电源。