CMOS模拟集成电路实训2016-Bandgap

- 格式:ppt

- 大小:1.93 MB

- 文档页数:45

模拟集成电路设计实习培训内容介绍培训目的经过本培训,学员将会学到在模拟集成电路设计过程中的绝大部分环节。

1.学会使用数模混合集成电路设计EDA工具进行简单的模拟集成电路设计的流程,包括Cadence的Virtuoso原理图输入、版图设计,Cadence的Spectre电路仿真,及Mentor Graphics 的Calibre版图规则检查(DRC)、电路图版图一致性检查(LVS)。

2.学会使用三大常用的仿真方式(DC,AC,以及Transient)来对电路进行性能的验证与设计参数的调整培训内容本培训首先设计一个运算放大器,在该放大器中采用了一个理想的电流源做偏置。

接着设计一个带隙基准源(Bandgap reference)来提供这个运算放大器中用到的电流源,然后对整个电路进行仿真验证。

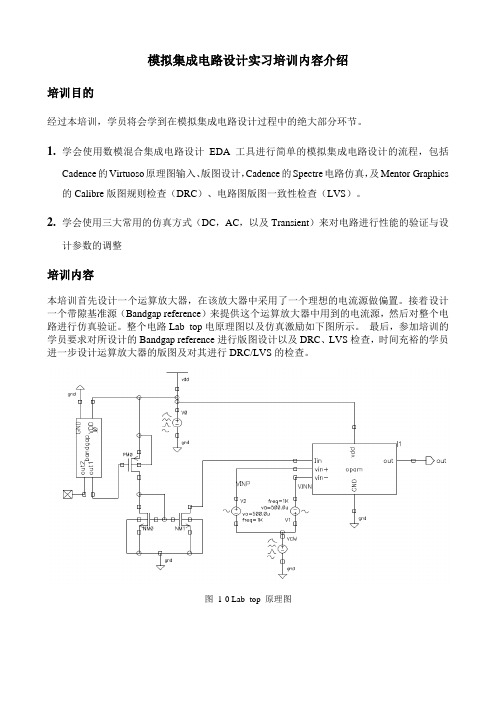

整个电路Lab_top电原理图以及仿真激励如下图所示。

最后,参加培训的学员要求对所设计的Bandgap reference进行版图设计以及DRC、LVS检查,时间充裕的学员进一步设计运算放大器的版图及对其进行DRC/LVS的检查。

图1-0 Lab_top 原理图上图中的运算放大器(opam)电路如下图所示,值得注意的是,该运算放大器需要一个current sink做偏置,该current sink由上图中的NM1来提供。

其中的bandgap电路如下图。

这里看上去好像电压源并没有和电路直接连在一起,但是由于系统中所有标记相同的点电位都相同,所以,图中的这种接法等效于直接把V4接到电路的正负极。

图1-14 加入激励源后的图二、Spectre 仿真 (opam)(1)直流分析(DC Analyses)我们在共模输入管脚接一个可以调节的电压源VCM ,使得这个电压源的电压从0升到高到3.3v 然后我们测量output 端的电压。

从图1-14中的Tools 菜单->Analog Environment 调出spectreV4AnalogLib/vsource/DCIbiasAnalogLib/isource/DCV0与V1 AnlogLib/vsinVCMAnalogLib/vsource/DC图2-1 spectre仿真界面。

电子科大集成电路原理实验报告-CMOS模拟集成电路设计与仿真标准实验报告电子科技大学微电子与固体电子学院集成电路原理与设计CMOS模拟集成电路设计与仿真电子科技大学实验报告实验地点:211楼606 实验时间:2014.6.7一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理参照实验指导书。

五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60?,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网2(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

具体计算步骤如下:(参见模拟CMOS集成电路设计)1. 通过额定功耗和片外电容C计算偏置电路电流以及流进M6,M8电流,再通过相关试验得到相关pmos,nmos的Vth和k和λ,得到m6,m8,m9宽长比并计算密勒电容Cc2. 通过cmr计算m4和m0的宽长比3. 通过GB和Cc求出m2和m5宽长比4. 由m6,m8的Ids电流计算m7宽长比5. 进行电路仿真,观察电路是否符合各方面要求。

可编辑修改精选全文完整版集成电路实习报告艰辛而又充满意义的实习生活又告一段落了,想必都收获了成长和成绩,是时候回头总结这段时间的实习生活了。

你所见过的实习报告应该是什么样的?下面是小编帮大家整理的集成电路实习报告(通用6篇),仅供参考,大家一起来看看吧。

集成电路实习报告1一:实习目的1、学习焊接电路板的有关知识,熟练焊接的具体操作。

2、看懂收音机的原理电路图,了解收音机的基本原理,学会动手组装和焊接收音机。

3、学会调试收音机,能够清晰的收到电台。

4、学习使用protel电路设计软件,动手绘制电路图。

二:焊接的技巧或注意事项焊接是安装电路的基础,我们必须重视他的技巧和注意事项。

1、焊锡之前应该先插上电烙铁的插头,给电烙铁加热。

2、焊接时,焊锡与电路板、电烙铁与电路板的夹角最好成45度,这样焊锡与电烙铁夹角成90度。

3、焊接时,焊锡与电烙铁接触时间不要太长,以免焊锡过多或是造成漏锡;也不要过短,以免造成虚焊。

4、元件的腿尽量要直,而且不要伸出太长,以1毫米为好,多余的可以剪掉。

5、焊完时,焊锡最好呈圆滑的圆锥状,而且还要有金属光泽。

三:收音机的原理本收音机由输入回路高放混频级、一级中放、二级中放、前置低放兼检波级、低放级和功放级等部分组成接收频率范围为535千赫1065千赫的中段。

1、具体原理如下原理图所示:2、安装工艺要求:动手焊接前用万用表将各元件测量一下,做到心中有数,安装时先安装低矮和耐热元件(如电阻),然后再装大一点的元件(如中周、变压器),最后装怕热的元件(如三极管)。

电阻的安装:将电阻的阻值选择好后根据两孔的距离弯曲电阻脚可采用卧式紧贴电路板安装,也可以采用立式安装,高度要统一。

瓷片电容和三极管的脚剪的长短要适中,它们不要超过中周的高度。

电解电容紧贴线路板立式焊接,太高会影响后盖的安装。

、棒线圈的四根引线头可直接用电烙铁配合松香焊锡丝来回摩擦几次即可自动上锡,四个线头对应的焊在线路板的铜泊面。

电子科技大学集成电路实验报告――模拟集成电路CMOS模拟集成电路设计及HSPICE使用实验学时:4学时实验一CMOS工艺参数测量一、实验目的:学习和掌握EDA仿真软件Hspice;了解CMOS工艺技术及元器件模型,掌握MOSFET工作原理及其电压电流特征;通过仿真和计算,获得CMOS中NMOS和PMOS的工艺参数kp,kn, p, n,Vtp,Vtn,为后续实验作准备。

二、实验内容:1)通过Hspice仿真,观察NMOS和PMOS管子的I-V特性曲线;2)对于给定长宽的MOSFET,通过Hspice仿真,测得几组栅-源电压、漏-源电压和漏-源电流数据,代入公式IDSn1WKn()n(VGS Vtn)2(1 nVDS),求得对应的工艺参数2Lkp,kn, p, n,Vtp,Vtn 。

三、实验结果:本实验中所测试的NMOS管、PMOS管L=1u,W由学号确定。

先确定W。

W等于学号的最后一位,若学号最后一位=0,则W=10u。

所以,本实验中所测试的NMOS管、PMOS管的尺寸为:(1)测0.5um下NMOS和PMOS管的I-V特性曲线所用工艺模型是TSMC 0.50um。

所测得的Vgs=1V时,NMOS管Vds从0V到2.5V变化时的I-V特性曲线为:所测得的Vds=1.2V时,NMOS管Vgs从0V到2.5V变化时的I-V特性曲线为:所测得的Vsg=1V时,PMOS管Vsd从0V到2.5V变化时的I-V特性曲线为:所测得的Vsd=1.2V时,PMOS管Vsg从0V到2.5V变化时的I-V特性曲线为:(2)计算TSMC 0.50um工艺库下mos管对应的工艺参数测试NMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:NOMS I-V Characteristic M1 OUT IN 0 0 CMOSn L=1U W=8U VIN IN 0 1 VOUT OUT 0 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2 .PRINT DC I(M1).LIB “C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的NMOS管电流曲线为:所测的数据如下表:根据公式IDSn1Kn()n(VGS Vtn)2(1 nVDS),计算kn, n,Vtn,分别为:2Lkn 119 10-6, n 0.028,Vtn 1.37测试PMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:POMS I-V CharacteristicM1 OUT IN Vdd Vdd CMOSP L=1U W=8UVIN Vdd IN 1 VOUT Vdd OUT 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M2).LIB "C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的PMOS管电流曲线为:所测的数据如下表:计算TSMC 0.50um 工艺中pmos 参数pptp,分别为:Kp 54.89 10-6, p 0.017,Vtp 0.927综上所述,可得:四、思考题2)不同工艺,p, n不同。

实验二CMOS模拟集成电路设计与仿真实验二 CMOS 模拟集成电路设计与仿真CMOS(Complementary Metal-Oxide-Semiconductor)模拟集成电路(Analog Integrated Circuits)是一种基于金属-氧化物-半导体结构的集成电路技术。

在本实验中,我们将学习并实践CMOS模拟集成电路的设计和仿真,以加深对其原理和应用的理解。

通过此实验,我们将能够熟练掌握CMOS模拟集成电路设计与仿真的基本流程与方法。

一、实验目的本实验旨在通过设计和仿真CMOS模拟集成电路,加深对其工作原理的理解,掌握电路设计与仿真的基本方法。

二、实验原理CMOS模拟集成电路是一种基于n型和p型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)的电路。

通过调节不同MOS管的工作状态,可以实现不同的电路功能。

其中,n型MOS管的主要特点是电导率高,适用于放大增益较大的部分;p型MOS管的主要特点是电导率低,适用于控制电流流动的部分。

三、实验步骤1. 电路设计:根据实际需求,确定设计所需的CMOS模拟集成电路。

在设计前,应先详细了解电路的功能、性能及工作原理,确定所需的器件数目和性能参数。

2. 电路布局:根据设计要求,将设计的各个电路模块在模拟集成电路上进行布局,合理安排电路的位置和空间,以保证电路的稳定性和性能。

3. 电路连接:按照布局图,将所需的电路模块进行连接,确保各个模块之间信号的正确传输和电路功能的正常实现。

4. 电路仿真:使用专业的仿真软件,将设计好的CMOS模拟集成电路进行仿真,验证其电路性能和功能。

在仿真过程中,应注意选择合适的仿真参数和验证方法,以保证仿真结果的准确性和可靠性。

5. 仿真分析:根据仿真结果,对电路的性能和功能进行分析和评估。

如果发现问题或改进的空间,可以根据分析结果进行相应的调整和优化。

6. 总结与展望:根据实验结果和分析,总结实验过程中的经验和教训,提出可能的改进和未来的研究方向。

实验二单级放大器的设计一、实验目的及任务1、掌握单级放大器的原理和性能。

2、设计一个采用电阻做负载的共源级放大器。

二、实验相关知识1、采用电阻做负载的共源级放大器电路的大信号分析。

如果输入电压从零开始增大,截止,(如图2.1(b))。

当接近时,开始导通,电流流经,使减小。

如果不是非常小,饱和导通,我们可以得到:这里忽略了沟道调制效应。

进一步增大,下降更多,管子继续工作在饱和区,直到(图2.1(b)中的A点)。

在A 点出满足:从上式可以计算出,并进一步计算出。

当时,工作在线性区:如果足够高以使进入深线性区,,从图2.1(b)的等效电路可以得到:2、采用电阻为负载的共源级放大器小信号特性由于在线性区跨导会下降,通常要确保,工作在图2.1(b)中A 点的左侧。

式(2.1)表征输入输出特性,并把它的斜率看作小信号增益,可以得到:此结果可以从下面的观察中直接得到:将输入电压的变化转换为漏极电流的变化,进一步转换为输入电压的变化。

从图2.1(d)的小信号等效电路也可以得到同样的结果。

V DD R DM 1V outV inV outV inV THV in1V outV inR DR onV DD V +-+-V 1outg m V 1R D(a)(c)(d)(b)图2.1 (a)共源级;(b)输入-输出特性;(c)MOS管工作在线性区的等效电路;(d)饱和区的小信号模型三、实验内容和步骤1、根据实验相关知识所述,画出采用电阻做负载的共源级放大器的原理图。

2、根据所画原理图编写电路网表。

3、调入SMIC0.35um混合信号工艺库。

4、先计算电路的直流工作点,随后进行仿真并得到电路的直流工作点,将仿真结果与计算结果进行比较。

5、在网表中加入DC分析的激励语句,做DC大信号仿真,得到放大器的直流转移特性曲线,并对的出的曲线进行分析说明。

6、在网表中加入AC分析的激励语句,做小信号仿真,得到放大器的AC频率特性和低频小信号增益,并对仿真结果给出分析和说明。

CMOS模拟集成电路设计与仿真实验指导书模拟集成电路原理实验指导书二零一二年五月实验1 集成电路版图识别与提取一、实验目的随着IT产业的迅速发展,集成电路在国民经济和国防建设中的地位日益突出。

IC设计技术尤显重要。

版图识别与提取是微电子IC逆向设计的关键技术。

一方面可借鉴并消化吸收先进、富有创意的版图设计思想、结构。

建立自己的版图库;另一方面通过分析、优化已有版图可将原有芯片的性能加以改进提高。

本实验是基于微电子技术应用背景和《模拟集成集成电路》课程设置及其特点而设置,目的在于:1增加对塑封、陶瓷封装等不同封装形式的感性认识;2 增加对硅圆片、芯片的感性认识;3 学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

4能对提取得到的电路进行功能分析、确定,并可运用EDA软件展开模拟仿真。

二、实验原理本实验重点放在版图识别、电路拓扑提取、版图编辑三大模块,实验流程如下:三、实验内容1.观察典型集成电路的封装形式;2.观察集成电路成品剖片的电路结构;3.观察硅圆片与未封装的芯片;4.在芯片上找出划片槽、测试单管、分布在芯片边缘的压焊点、对位标记,并测出有关图形的尺寸和间距。

仔细观察芯片图形的总体布局,找出电源线、地线、输入端、输出端以及相应的压焊点;6.判断集成电路的工艺类别;7.根据以上判断、提取芯片上图形所示电路图的拓扑结构;复查、修正,并进行仿真验证。

四、实验步骤1.观察典型集成电路的封装形式;2.对集成电路成品剖片的电路结构进行观察;3.观察测试单管。

仔细观察芯片的布局布线,找出电源线和地线。

4.确定芯片工艺类别,分清单个的元件结构,提取版图电路拓扑结构五、实验报告1.版图识别与提取过程总结2.绘出所提版图的电路拓扑结构六、附:版图照片(含铝线照片):金属1层去铝线照片衬底层课下思考练习: 金属1层去铝线照片衬底层实验2CMOS模拟集成电路设计与仿真一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。