FPGA 驱动触摸屏(TFT)

- 格式:doc

- 大小:130.00 KB

- 文档页数:9

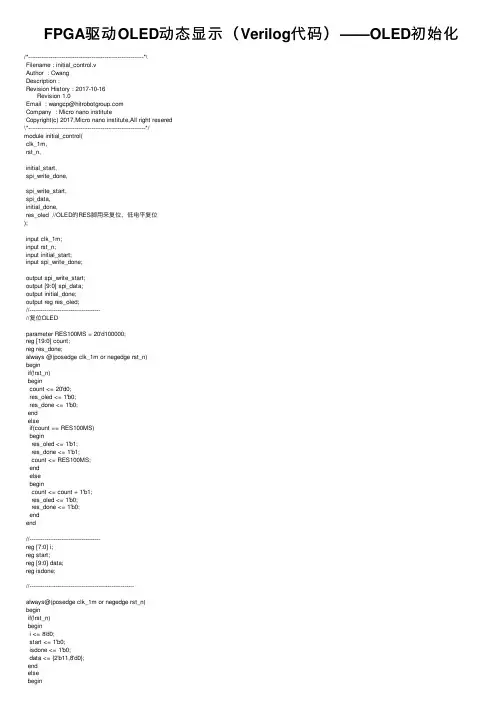

FPGA驱动OLED动态显⽰(Verilog代码)——OLED初始化/*--------------------------------------------------------------*\Filename : initial_control.vAuthor : CwangDescription :Revision History : 2017-10-16Revision 1.0Email : wangcp@Company : Micro nano instituteCopyright(c) 2017,Micro nano institute,All right resered\*---------------------------------------------------------------*/module initial_control(clk_1m,rst_n,initial_start,spi_write_done,spi_write_start,spi_data,initial_done,res_oled //OLED的RES脚⽤来复位,低电平复位);input clk_1m;input rst_n;input initial_start;input spi_write_done;output spi_write_start;output [9:0] spi_data;output initial_done;output reg res_oled;//--------------------------------------//复位OLEDparameter RES100MS = 20'd100000;reg [19:0] count;reg res_done;always @(posedge clk_1m or negedge rst_n)beginif(!rst_n)begincount <= 20'd0;res_oled <= 1'b0;res_done <= 1'b0;endelseif(count == RES100MS)beginres_oled <= 1'b1;res_done <= 1'b1;count <= RES100MS;endelsebegincount <= count + 1'b1;res_oled <= 1'b0;res_done <= 1'b0;endend//--------------------------------------reg [7:0] i;reg start;reg [9:0] data;reg isdone;//--------------------------------------------------------always@(posedge clk_1m or negedge rst_n)beginif(!rst_n)begini <= 8'd0;start <= 1'b0;isdone <= 1'b0;data <= {2'b11,8'd0};endelsebeginif(initial_start && res_done)begincase(i)//------------------------------------------------------------------------------------- 8'd0:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hae}; start <= 1'b1;end8'd1:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h00}; start <= 1'b1;end 8'd2:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h10}; start <= 1'b1;end8'd3:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h40}; start <= 1'b1;end8'd4:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h81}; start <= 1'b1;end8'd5:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hCF}; start <= 1'b1;end8'd6:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hA1}; start <= 1'b1;end8'd7:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hC8}; start <= 1'b1;end8'd8:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hA6}; start <= 1'b1;end8'd9:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hA8}; start <= 1'b1;end8'd10:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h3F}; start <= 1'b1;end8'd11:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hD3}; start <= 1'b1;end8'd12:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h00}; start <= 1'b1;end8'd13:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hD5}; start <= 1'b1;end8'd14:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h80}; start <= 1'b1;end8'd15:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hD9}; start <= 1'b1;end8'd16:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hF1}; start <= 1'b1;end8'd17:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hDA}; start <= 1'b1;end 8'd18:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h12}; start <= 1'b1;end8'd19:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hDB}; start <= 1'b1;end 8'd20:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h40}; start <= 1'b1;end8'd21:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h20}; start <= 1'b1;end8'd22:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h02}; start <= 1'b1;end8'd23:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h8D}; start <= 1'b1;end8'd24:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'h14}; start <= 1'b1;end8'd25:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hA4}; start <= 1'b1;end8'd26:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hA6}; start <= 1'b1;end8'd27:if(spi_write_done) begin start <= 1'b0; i <= i + 1'b1;endelse begin data <= {2'b00,8'hAF}; start <= 1'b1;end//--------------------------------------------------------------------------------8'd28:begindata <= {2'b11,8'd0}; isdone <= 1'b1; i <= i + 1'b1;end8'd29:beginisdone <= 1'b0; i <= 8'd0;endendcaseendendendassign spi_data = data;assign spi_write_start = start;assign initial_done = isdone;endmodule注释:1、以上初始化数据是针对驱动芯⽚SSD1306,128*64的OLED;2、应该先复位OLED;3、初始化之后应该将⽚选CS置⾼,如8'd28:data <= {2'b11,8'd0};。

常见液晶驱动控制芯片详解前言因此各位朋友在选择LCD液晶模块的时候,在考虑到串行,还是并行的方式时,可根据其驱动控制IC的型号来判别,当然你还需要看你选择的LCD模块引脚定义是固定支持并行,还是可选择并行或串行的方式。

一、字符型LCD驱动控制IC市场上通用的8×1、8×2、16×1、16X2、16X4、20X2、20X4、40X4等字符型LCD,基本上都采用的KS0066 作为LCD 的驱动控制器。

二、图形点阵型LCD驱动控制IC2.1、点阵数122X32—SED1520。

2.2、点阵数128×64。

(1)RA8816,支持串行或并行数据操作方式,内置中文汉字字库。

(2)KS0108/RA8808,只支持并行数据操作方式,也是最通用的12864点阵液晶的驱动控制IC。

(3)ST7565,支持中行或并行数据操作方式。

(4)S6B0724,支持中行或并行数据操作方式。

(5)RA6963,支持并行数据操作方式。

2.3、其他点阵数如192×64、240×64、320X64、240X128 的一般都是采用RA6963驱动控制芯片。

2.4、点阵数320X240,通用的采用RA8835 内置ASCII字库,以及RA8806驱动IC内置ASCII和中文等字库。

这里列举的只是一些常用的,当然还有其他LCD 驱动控制IC,在写LCD 驱动时要清楚是哪个型号的IC,再到网上去寻找对应的IC 数据手册吧。

后面我将慢慢补上其它一些常见的。

三、12864 液晶的奥秘CD1601/1602和LCD12864 都是通常使用的液晶,有人以为12864是一个统一的编号,主要是12864 的液晶驱动都是一样的,其实12864只是表示液晶的点阵是128*64点阵,而实际的12864 有带字库的,也有不带字库的:有5V电压的,也有3.3V工作电压:归根到底的区别在于驱动控制芯片,常用的控制芯片有RA8816、KS0108/RA8808、RA6963等等。

广州致远电子有限公司TFT 控制器方案基于Actel FPGA 实现类别内容关键词 TFT ,Actel FPGA摘 要TFT 诞生于80年代末,在1995年之后被广泛的应用,随着TFT 价格的下降,应用范围出现了前所未有的变化,可以适用于医疗、电梯、数控机床、汽车电子、消费类电子等行业。

修订历史版本日期原因V0.00 2009/11/30 创建文档V1.00 2010/05/10 文档修订销售与服务网络(一)广州周立功单片机发展有限公司地址:广州市天河北路689号光大银行大厦12楼F4 邮编:510630电话:(020)38730916 38730917 38730972 38730976 38730977 传真:(020)38730925 网址:广州专卖店地址:广州市天河区新赛格电子城203-204室 电话:(020)87578634 87569917 传真:(020)87578842南京周立功地址:南京市珠江路280号珠江大厦2006室 电话:(025)83613221 83613271 83603500 传真:(025)83613271北京周立功地址:北京市海淀区知春路113号银网中心A 座1207-1208室 (中发电子市场斜对面) 电话:(010)62536178 62536179 82628073 传真:(010)82614433重庆周立功地址:重庆市石桥铺科园一路二号大西洋国际大厦(赛格电子市场)1611室 电话:(023)68796438 68796439 传真:(023)68796439杭州周立功地址:杭州市天目山路217号江南电子大厦502室 电话:(0571)89719480 89719481 89719482 89719483 89719484 89719485 传真:(0571)89719494成都周立功地址:成都市一环路南二段1号数码同人港401室(磨子桥立交西北角)电话:(028)85439836 85437446 传真:(028)85437896深圳周立功地址:深圳市深南中路 2070号电子科技大厦C 座4楼D 室电话:(0755)83781788(5线) 传真:(0755)83793285武汉周立功地址:武汉市洪山区广埠屯珞瑜路158号12128室(华中电脑数码市场)电话:(027)87168497 87168297 87168397 传真:(027)87163755上海周立功地址:上海市北京东路668号科技京城东座7E 室 电话:(021)53083452 53083453 53083496 传真:(021)53083491西安办事处地址:西安市长安北路54号太平洋大厦1201室 电话:(029)87881296 83063000 87881295 传真:(029)87880865销售与服务网络(二)广州致远电子有限公司地址:广州市天河区车陂路黄洲工业区3栋2楼邮编:510660传真:(020)38601859网址:(嵌入式系统事业部)(工控网络事业部)(楼宇自动化事业部)技术支持:CAN-bus:电话:(020)22644381 22644382 22644253 邮箱:can.support@ iCAN及数据采集:电话:(020)28872344 22644373 邮箱:ican@MiniARM:电话:(020)28872684 28267813邮箱:miniarm.support@ 以太网:电话:(020)22644380 22644385邮箱:ethernet.support@无线通讯:电话:(020) 22644386邮箱:wireless@ 串行通讯:电话:(020)28267800 22644385 邮箱:serial@编程器:电话:(020)22644371邮箱:programmer@ 分析仪器:电话:(020)22644375 28872624 28872345 邮箱:tools@ARM嵌入式系统:电话:(020)28872347 28872377 22644383 22644384 邮箱:arm.support@楼宇自动化:电话:(020)22644376 22644389 28267806 邮箱:mjs.support@mifare.support@销售:电话:(020)22644249 22644399 22644372 22644261 28872524 28872342 28872349 28872569 28872573 38601786维修:电话:(020)22644245目录1. TFT简介 (1)2. 原理概述 (2)2.1方案简介 (2)2.2基于Actel FPGA的TFT控制器方案 (2)2.2.1低成本、多功能、低分辨率显示方案 (2)2.2.2低成本、多功能、高分辨率显示方案 (3)2.2.3高性能、低分辨率显示方案 (4)2.2.4多功能、高分辨率显示方案 (4)3. 典型应用 (6)4. 免责声明 (7)1. TFT简介在1970年,Fergason制造了第一台具有实用性的LCD,从此之后,用户产品的界面发生了巨大改变,变得更加的美观、实用,在一定场合下逐渐取代传统的数码管、LED的显示。

使用单片机ram加速刷新tft屏幕的方法在嵌入式系统应用中,我们有时会需要用到TFT(薄膜晶体管)屏幕来显示图像或文本。

TFT屏幕的刷新率决定了显示的流畅度,而单片机(MCU)的RAM(随机存取存储器)大小则影响了刷新率的上限。

以下是一个使用单片机RAM加速刷新TFT屏幕的方法:1. **了解RAM和TFT屏幕的关系**:TFT屏幕的刷新率与单片机RAM 的大小直接相关。

RAM越大,可以缓存的像素数据越多,从而可以更快地刷新屏幕。

2. **优化数据传输**:尽量减少从单片机RAM到TFT屏幕的数据传输。

可以通过在RAM中预存多行或一整屏的像素数据来实现。

这样,当需要刷新屏幕时,直接从RAM中读取数据,而不是从其他存储器或处理器缓存中。

3. **多线程处理**:在条件允许的情况下,可以考虑使用多线程。

一个线程专门用于处理显示逻辑,持续从RAM中读取数据并写入TFT 屏幕;另一个线程则可以处理其他任务,如用户输入或数据处理。

4. **优化数据结构**:考虑使用最适合你应用的数据结构来存储像素数据。

例如,如果你需要频繁地读取和写入像素数据,使用数组可能更为高效。

5. **使用DMA(直接内存访问)**:如果单片机支持DMA(直接内存访问),那么可以使用DMA来传输像素数据到TFT屏幕。

DMA可以在后台进行数据传输,从而释放CPU资源用于其他任务。

6. **硬件加速**:一些高级的单片机或TFT屏幕控制器可能提供硬件加速功能,这可以在特定情况下进一步提高刷新率。

7. **软件优化**:编写优化的驱动代码来控制TFT屏幕。

确保你的代码在读写像素数据时是高效的,并尽量减少不必要的中断或上下文切换。

8. **考虑硬件升级**:如果你的应用对刷新率有特别高的要求,而单片机的RAM大小成为瓶颈,那么可能需要考虑升级到具有更大RAM 或更高级处理能力的单片机。

9. **测试和调试**:在实施上述优化后,进行彻底的测试以确保一切工作正常,并且刷新率达到了预期。

西安电子科技大学硕士学位论文TFT LCD驱动芯片的研究与设计姓名:唐华申请学位级别:硕士专业:微电子学与固体电子学指导教师:吴玉广200601012TFTLCD驱动芯片的研究与设计图1.1液晶屏显示原理如上所述,在LcD屏上外加电压,液晶分子排列会改变,LcD将根据电压的有无和大小,控制液晶分子排列方向,使面板达到显示效果。

若上、下偏光板吸收轴方向成900,唯一一个方向振动的光能否通过LCD屏,取决于是否外加电压,而光通过与否则决定了“白”和“黑”,这样在LcD上可显示出图像。

当然,白和黑的中间色是由外加电压的中间电位决定的,电压不同透光率不同,显示的明暗程度就不同。

若加上彩色滤光膜(cF),则可显示彩色影像。

1.2TFTLCD的发展在众多平板显示器的激烈竞争中,肝LcD能够脱颖而出,成为新一代的主流显示器决不是偶然,是人类科技发展和思维模式发展的必然。

液晶先后避开了困难的发光问题,利用液晶作为光阀的优良特性把发光显示器件分解成两部分,即光源和对光源的控制。

作为光源,无论从发光效率、全彩色,还是寿命,都已取得了辉煌的成果,而且还在不断深化之中。

自LCD发明以来,背光源在不断地进步,由单色到彩色,由厚到薄,由侧置荧光灯式到平板荧光灯式。

在发光光源方面取得的最新成果都会为LcD提供新的背光源。

随着光源科技的进步,会有更新更好的光源出现并为LcD所应用。

余下的就是对光源的控制,把半导体大规模集成电路的技术和工艺移植过来,研制成功了薄膜晶体管(TFD生产工艺,实现了对液晶光阀的矩阵寻址控制,解决了液晶显示器的光阀和控制器的配合,从而使波晶显示的优势得以实现。

液晶显示器包括无源矩阵液晶显示器口M-LcD)与有源矩阵液晶显示器(AM.LcD)。

sTN与TN液晶显示器均同属于无源矩阵液晶显示器。

90年代,有源矩阵液晶显示器技术获得了飞速发展,特别是薄膜晶体管液晶显示器(TFT.LCD)。

它作为sTN的换代产品具有响应速度快、不闪烁等优点,广泛应用到便携式计算机及工作站、电视、摄录像机和手持式视频游戏机等产品中。

FPGA的触摸屏控制系统1 概述触摸屏操作简单,控制方便,越来越成为手机及平板电脑的主流输入和显示设备。

目前,世界上常用的触摸屏有电阻式触摸屏和电感式触摸屏。

由于电阻式触摸屏具备结构简单、制造便捷、各项功能易被大多数设备所兼容的特点,故本系统选用电阻式触摸屏作为输入设备。

FPGA具有性能高速、控制精准、实时性好的特点,当把FPGA设置为ASIC,性能和效率将大大提升,功耗得到大幅降低。

2 总体设计本系统选用FPGA为主控制器,从触摸数据采集模块中读取触摸点数据,对数据进行处理得到相应点的坐标值,然后在显示器上显示相应的数据,同时LED指示完成相应的操作,系统的总体框图如图1。

图1 触摸屏控制系统框图触摸屏接受外部触摸信号,触摸坐标点的偏置电压随着屏幕水平和垂直方向的滑变电阻而变化。

触摸屏控制器主要完成触摸屏和FPGA控制器间的数据传输,对触摸数据进行实施采样,一旦发生触摸操作,即将中断信号发送至FPGA,由FPGA进行数据采集,发送指令启动AD转换,并将转换信号传输至FPGA控制器,完成数据转换。

显示控制器接受FPGA发送的控制数据,在TFT屏幕上进行显示。

在这里,FGPA选用ALTERA公司的EP2C8Q208,触摸屏控制器选用四线式电阻控制器XPT2046,便于实现触摸点压力测量,TFT控制器选用通用的LCD控制器ILI9325。

3 硬件电路设计系统电源需要5V、3.3V和1.2V电压,由于TFT背光需要较高的亮度,故采用5V供电;3.3V电压主要提供给TFT显示控制器、触摸屏控制器、FPGA芯片IO接口、SDRAM等,选用LM1085稳压芯片;1.2V作为FPGA芯片核心工作电压,采用AMS117-1.2稳压芯片。

为保证系统稳定工作,在各电源输入输出部分均使用滤波电容。

FPGA系统由时钟电路、复位电路和FPGA芯片构成。

本系统选用50MHz 晶振作为FPGA的工作时钟,晶振输出的时钟信号送至FPGA的第23引脚,即CLK0。

毕业设计(论文)任务书基于FPGA的LCD驱动显示电路的设计与实现摘要本课题主要任务是设计基于FPGA的LCD驱动电路的设计和实现,兼顾好程序的易用性,以方便之后模块的移植和应用。

控制器部分采用Verilog语言编写,主体程序采用了状态机作为主要控制方式。

最后实现使用FPGA在LCD上显示任意的英文字符和阿拉伯数字,另外要能根据输入数据的变化同步变化LCD上显示的内容。

同时要能将储存模块中的数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

本文中对FPGA,LCD,ModelSim,Xilinx ISE8.2i硬件设计工具等进行了简单的介绍,对其功能进行了简单的描述,并了解了LCD液晶显示器的发展历史,日常应用以及相对比于其他种类显示器的优缺点,并对基于FPGA的LCD液晶显示器驱动电路未来的发展趋势进行了展望。

关键词:FPGA,LCD,状态机,VerilogDesign and Implementation of LCD Drive DisplayCircuit based on FPGAAbstractIn this project, the main object is to design a LCD controller based on FPGA, and at the same time emphasize on the convenience for the later application and migration.The program of the controller is written by Verilog language, and the main body of the program used state machine as the primary control method. displayed picture which was put earlier.In this project, I finally realized the following function. The first one is to display any English and figureon character any position of the display screen. The second one is the display information will instantaneously update as the input data changes.The research of this project will contribute to the developing process of those products which use FPGAs, especially those products also use LCD. And at the same time, it can reduce dramatically on the developing time. In addition, for the convenience of this controller, more and more FPGA based products will come out with LCD screen. This change will enhance the interaction between human and the machine, and bring innovation to the industry and our lives.In this project, FPGA, LCD, ModelSim, Xilinx ISE8.2 I hardware design tools simply introduces its functions were a simple description, and understanding the LCD monitor the development history, and relative everyday applications than in other types of monitor based on FPGA advantages and disadvantages, and the LCD monitor driver circuit future development trends are discussed.Key words:, FPGA, LCD, State Machine, Verilog目录任务书 (I)摘要 ....................................................错误!未定义书签。

FPGA的TFT-LCD真彩液晶屏显示控制宋云霞【摘要】目前液晶屏的使用越来越广泛,TFT-LCD真彩液晶屏由于其良好的视觉效果,简便的控制方法在液晶屏使用市场中占有很大的空间,但是目前常用的TFT-LCD 液晶屏主控芯片主要是单片机、STM32等,不能满足更进一步的研发需求,本文主要研究了FPGA驱动TFT-LCD液晶屏的方法,使用80并口控制芯片操作完成复杂的屏幕显示功能.%The use of LCD screen is aboard at present,the TFT-LCD screen occupies a lot of space in the use of LCD screen because of its great visual effect and simple control method.But the main control chip of TFT-LCD screen usually uses the single chip of microcontroller or STM32,it can not satisfy the further research and development needs.In the paper,the methods of FPGA drive TFT-LCD screen are researched,80 parallel ports control chip is used to complete the complex screen display function.【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2017(017)004【总页数】3页(P41-42,50)【关键词】FPGA;TFT-LCD液晶屏;80并口;控制电路【作者】宋云霞【作者单位】中国电子科技集团公司第38研究所,孔径阵列与空间探测安徽省重点实验室,合肥230088【正文语种】中文【中图分类】TN911.72液晶屏作为人机交互的重要手段,已经应用得越来越广泛。

基于S3C2410的TFT-LCD驱动电路设计作者:北京清华大学电子工程系 刘立涛 罗嵘 金平关键词:驱动电路,嵌入式系统,TFT-LCD,嵌入式处理器,S3C2410,液晶显示器引言随着电子技术的迅猛发展,具有耗电少、亮度高、体积小等特点的液晶显示器被广泛应用于嵌入式系统中。

S3C2410是三星公司开发的一款以ARM920T为核心的16/32位嵌入式处理器。

它主要面向手持设备以及高性价比、低功耗的应用。

LTS350Q1-PE1是三星电子公司生产的一款非晶硅有源矩阵TFT-LCD,它具有功耗低、亮度高和体积小等特点,目前在嵌入式设备中应用非常广泛。

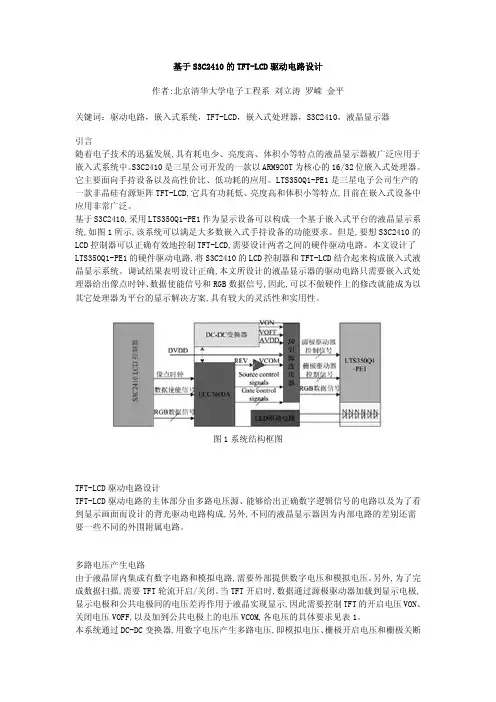

基于S3C2410,采用LTS350Q1-PE1作为显示设备可以构成一个基于嵌入式平台的液晶显示系统,如图1所示,该系统可以满足大多数嵌入式手持设备的功能要求。

但是,要想S3C2410的LCD控制器可以正确有效地控制TFT-LCD,需要设计两者之间的硬件驱动电路。

本文设计了LTS350Q1-PE1的硬件驱动电路,将S3C2410的LCD控制器和TFT-LCD结合起来构成嵌入式液晶显示系统。

调试结果表明设计正确,本文所设计的液晶显示器的驱动电路只需要嵌入式处理器给出像点时钟、数据使能信号和RGB数据信号,因此,可以不做硬件上的修改就能成为以其它处理器为平台的显示解决方案,具有较大的灵活性和实用性。

图1系统结构框图TFT-LCD驱动电路设计TFT-LCD驱动电路的主体部分由多路电压源、能够给出正确数字逻辑信号的电路以及为了看到显示画面而设计的背光驱动电路构成,另外,不同的液晶显示器因为内部电路的差别还需要一些不同的外围附属电路。

多路电压产生电路由于液晶屏内集成有数字电路和模拟电路,需要外部提供数字电压和模拟电压。

另外,为了完成数据扫描,需要TFT轮流开启/关闭。

当TFT开启时,数据通过源极驱动器加载到显示电极,显示电极和公共电极间的电压差再作用于液晶实现显示,因此需要控制TFT的开启电压VON、关闭电压VOFF,以及加到公共电极上的电压VCOM,各电压的具体要求见表1。

TFT LCD液晶显示器的驱动原理TFT LCD液晶显示器的驱动原理(一)我们针对TFT LCD的整体系统面来做介绍, 也就是对其驱动原理来做介绍, 而其驱动原理仍然因为一些架构上差异的关系, 而有所不同. 首先我们来介绍由于Cs(storage capacitor)储存电容架构不同, 所形成不同驱动系统架构的原理.Cs(storage capacitor)储存电容的架构一般最常见的储存电容架构有两种, 分别是Cs on gate与Cs on common这两种. 这两种顾名思义就可以知道, 它的主要差别就在于储存电容是利用gate走线或是common走线来完成的. 在上一篇文章中, 我曾提到, 储存电容主要是为了让充好电的电压,能保持到下一次更新画面的时候之用. 所以我们就必须像在CMOS的制程之中, 利用不同层的走线, 来形成平行板电容. 而在TFT LCD的制程之中, 则是利用显示电极与gate走线或是common走线,所形成的平行板电容,来制作出储存电容Cs.图1就是这两种储存电容架构, 从图中我们可以很明显的知道, Cs on gate由于不必像Cs on common一样, 需要增加一条额外的common走线, 所以它的开口率(Aperture ratio)会比较大. 而开口率的大小, 是影响面板的亮度与设计的重要因素. 所以现今面板的设计大多使用Cs on gate的方式. 但是由于Cs on gate的方式, 它的储存电容是由下一条的gate走线与显示电极之间形成的.(请见图2的Cs on gate与Cs on common的等效电路) 而gate走线, 顾名思义就是接到每一个TFT的gate端的走线, 主要就是作为gate driver送出信号, 来打开TFT, 好让TFT对显示电极作充放电的动作. 所以当下一条gate走线, 送出电压要打开下一个TFT时 ,便会影响到储存电容上储存电压的大小. 不过由于下一条gate走线打开到关闭的时间很短,(以1024*768分辨率, 60Hz更新频率的面板来说. 一条gate走线打开的时间约为20us, 而显示画面更新的时间约为16ms, 所以相对而言, 影响有限.) 所以当下一条gate走线关闭, 回复到原先的电压, 则Cs储存电容的电压, 也会随之恢复到正常. 这也是为什么, 大多数的储存电容设计都是采用Cs on gate 的方式的原因.至于common走线, 我们在这边也需要顺便介绍一下. 从图2中我们可以发现, 不管您采用怎样的储存电容架构, Clc的两端都是分别接到显示电极与common. 既然液晶是充满在上下两片玻璃之间, 而显示电极与TFT都是位在同一片玻璃上, 则common电极很明显的就是位在另一片玻璃之上. 如此一来, 由液晶所形成的平行板电容Clc, 便是由上下两片玻璃的显示电极与common电极所形成. 而位于Cs储存电容上的common电极, 则是另外利用位于与显示电极同一片玻璃上的走线, 这跟Clc上的common电极是不一样的, 只不过它们最后都是接到相同的电压就是了.整块面板的电路架构从图3中我们可以看到整片面板的等效电路, 其中每一个TFT与Clc跟Cs所并联的电容, 代表一个显示的点. 而一个基本的显示单元pixel,则需要三个这样显示的点,分别来代表RGB三原色. 以一个1024*768分辨率的TFT LCD来说, 共需要1024*768*3个这样的点组合而成. 整片面板的大致结构就是这样, 然后再藉由如图3中 gate driver所送出的波形, 依序将每一行的TFT打开, 好让整排的source driver同时将一整行的显示点, 充电到各自所需的电压, 显示不同的灰阶. 当这一行充好电时, gate driver便将电压关闭, 然后下一行的gate driver便将电压打开, 再由相同的一排source driver对下一行的显示点进行充放电. 如此依序下去, 当充好了最后一行的显示点, 便又回过来从头从第一行再开始充电. 以一个1024*768 SVGA分辨率的液晶显示器来说, 总共会有768行的g ate走线, 而source走线则共需要1024*3=3072条. 以一般的液晶显示器多为60Hz的更新频率来说, 每一个画面的显示时间约为1/6 0=16.67ms. 由于画面的组成为768行的gate走线, 所以分配给每一条gate走线的开关时间约为16.67ms/768=21.7us. 所以在图3 g ate driver送出的波形中, 我们就可以看到, 这些波形为一个接着一个宽度为21.7us的脉波, 依序打开每一行的TFT. 而sourcedriver则在这21.7us的时间内, 经由source走线, 将显示电极充放电到所需的电压, 好显示出相对应的灰阶.面板的各种极性变换方式由于液晶分子还有一种特性,就是不能够一直固定在某一个电压不变, 不然时间久了, 你即使将电压取消掉, 液晶分子会因为特性的破坏, 而无法再因应电场的变化来转动, 以形成不同的灰阶. 所以每隔一段时间, 就必须将电压恢复原状, 以避免液晶分子的特性遭到破坏. 但是如果画面一直不动, 也就是说画面一直显示同一个灰阶的时候怎么办? 所以液晶显示器内的显示电压就分成了两种极性, 一个是正极性, 而另一个是负极性. 当显示电极的电压高于common电极电压时, 就称之为正极性. 而当显示电极的电压低于c ommon电极的电压时, 就称之为负极性. 不管是正极性或是负极性, 都会有一组相同亮度的灰阶. 所以当上下两层玻璃的压差绝对值是固定时, 不管是显示电极的电压高, 或是common电极的电压高, 所表现出来的灰阶是一模一样的. 不过这两种情况下, 液晶分子的转向却是完全相反, 也就可以避免掉上述当液晶分子转向一直固定在一个方向时, 所造成的特性破坏. 也就是说, 当显示画面一直不动时, 我们仍然可以藉由正负极性不停的交替, 达到显示画面不动, 同时液晶分子不被破坏掉特性的结果. 所以当您所看到的液晶显示器画面虽然静止不动, 其实里面的电压正在不停的作更换, 而其中的液晶分子正不停的一次往这边转, 另一次往反方向转呢!图4就是面板各种不同极性的变换方式, 虽然有这么多种的转换方式, 它们有一个共通点, 都是在下一次更换画面数据的时候来改变极性. 以60Hz的更新频率来说, 也就是每16ms, 更改一次画面的极性. 也就是说, 对于同一点而言, 它的极性是不停的变换的. 而相邻的点是否拥有相同的极性, 那可就依照不同的极性转换方式来决定了. 首先是frame inversion, 它整个画面所有相邻的点, 都是拥有相同的极性. 而row inversion与column inversion则各自在相邻的行与列上拥有相同的极性. 另外在dot inversion上, 则是每个点与自己相邻的上下左右四个点, 是不一样的极性. 最后是delta inversion, 由于它的排列比较不一样, 所以它是以RGB 三个点所形成的pixel作为一个基本单位, 当以pixel为单位时, 它就与dot inversion很相似了, 也就是每个pixel与自己上下左右相邻的pixel,是使用不同的极性来显示的.Common电极的驱动方式图5及图6为两种不同的Common电极的电压驱动方式, 图5中Common电极的电压是一直固定不动的, 而显示电极的电压却是依照其灰阶的不同, 不停的上下变动. 图5中是256灰阶的显示电极波形变化, 以V0这个灰阶而言, 如果您要在面板上一直显示V0这个灰阶的话, 则显示电极的电压就必须一次很高, 但是另一次却很低的这种方式来变化. 为什么要这么复杂呢? 就如同我们前面所提到的原因一样, 就是为了让液晶分子不会一直保持在同一个转向, 而导致物理特性的永久破坏. 因此在不同的frame中, 以V0这个灰阶来说, 它的显示电极与common电极的压差绝对值是固定的, 所以它的灰阶也一直不曾更动. 只不过位在Clc两端的电压, 一次是正的, 称之为正极性, 而另一次是负的, 称之为负极性. 而为了达到极性不停变换这个目的, 我们也可以让common电压不停的变动, 同样也可以达到让Clc两端的压差绝对值固定不变, 而灰阶也不会变化的效果, 而这种方法, 就是图6所显示的波形变化. 这个方法只是将common电压 一次很大, 一次很小的变化. 当然啦, 它一定要比灰阶中最大的电压还大, 而电压小的时候则要比灰阶中最小的电压还要小才行. 而各灰阶的电压与图5中的一样, 仍然要一次大一次小的变化.这两种不同的Common驱动方式影响最大的就是source driver的使用. 以图7中的不同Common电压驱动方式的穿透率来说, 我们可以看到, 当common电极的电压是固定不变的时候, 显示电极的最高电压, 需要到达common电极电压的两倍以上. 而显示电极电压的提供, 则是来自于source driver. 以图七中common电极电压若是固定于5伏特的话, 则source driver所能提供的工作电压范围就要到10伏特以上. 但是如果common电极的电压是变动的话, 假使common电极电压最大为5伏特, 则source driver的最大工作电压也只要为5伏特就可以了. 就source driver的设计制造来说, 需要越高电压的工作范围, 制程与电路的复杂度相对会提高, 成本也会因此而加高.面板极性变换与common电极驱动方式的选用并不是所有的面板极性转换方式都可以搭配上述两种common电极的驱动方式. 当common电极电压固定不变时, 可以使用所有的面板极性转换. 但是如果common电压是变动的话, 则面板极性转换就只能选用frame inversion与row inversion.(请见表1) 也就是说, 如果你想使用column inversion或是dot inversion的话, 你就只能选用 common电极电压固定不动的驱动方式. 为什么呢? 之前我们曾经提到 common电极是位于跟显示电极不同的玻璃上, 在实际的制作上时, 其实这一整片玻璃都是common电极. 也就是说, 在面板上所有的显示点, 它们的common电压是全部接在一起的. 其次由于gate driver的操作方式是将同一行的所有TFT打开,好让source driver去充电, 而这一行的所有显示点, 它的common电极都是接在一起的, 所以如果你是选用common电极电压是可变动的方式的话, 是无法在一行TFT上, 来同时做到显示正极性与负极性的. 而column inversion与dot inversion的极性变换方式, 在一行的显示点上, 是要求每个相邻的点拥有不同的正负极性的. 这也就是为什么 common电极电压变动的方式仅能适用于frame inv ersion与row inversion的缘故. 而common电极电压固定的方式, 就没有这些限制. 因为其common电压一直固定, 只要source dri ver能将电压充到比common大就可以得到正极性, 比common电压小就可以得到负极性, 所以common电极电压固定的方式, 可以适用于各种面板极性的变换方式.表1面板极性变换方式 可使用的common电极驱动方式Frame inversion固定与变动Row inversion固定与变动Column inversion只能使用固定的common电极电压Dot inversion只能使用固定的common电极电压各种面板极性变换的比较现在常见使用在个人计算机上的液晶显示器, 所使用的面板极性变换方式, 大部分都是dot inversion. 为什么呢? 原因无它, 只因为dot inversion的显示品质相对于其它的面板极性变换方式, 要来的好太多了. 表2是各种面板极性变换方式的比较表. 所谓F licker的现象, 就是当你看液晶显示器的画面上时, 你会感觉到画面会有闪烁的感觉. 它并不是故意让显示画面一亮一灭来做出闪烁的视觉效果, 而是因为显示的画面灰阶在每次更新画面时, 会有些微的变动, 让人眼感受到画面在闪烁. 这种情况最容易发生在使用frame inversion的极性变换方式, 因为frame inversion整个画面都是同一极性, 当这次画面是正极性时, 下次整个画面就都变成了是负极性. 假若你是使用common电压固定的方式来驱动, 而common电压又有了一点误差(请见图8),这时候正负极性的同一灰阶电压便会有差别, 当然灰阶的感觉也就不一样. 在不停切换画面的情况下, 由于正负极性画面交替出现,你就会感觉到Flicker的存在. 而其它面板的极性变换方式, 虽然也会有此flicker的现象, 但由于它不像frame inversion 是同时整个画面一齐变换极性, 只有一行或是一列, 甚至于是一个点变化极性而已. 以人眼的感觉来说, 就会比较不明显. 至于crosstalk 的现象, 它指的就是相邻的点之间, 要显示的资料会影响到对方, 以致于显示的画面会有不正确的状况. 虽然crosstalk的现象成因有很多种, 只要相邻点的极性不一样, 便可以减低此一现象的发生. 综合这些特性, 我们就可以知道, 为何大多数人都使用dot inve rsion了. 表2面板极性变换方式 Flicker的现象 Crosstalk的现象Frame inversion明显 垂直与水平方向都易发生Row inversion不明显 水平方向容易发生Column inversion不明显 垂直方向容易发生Dot inversion几乎没有 不易发生面板极性变换方式, 对于耗电也有不同的影响. 不过它在耗电上需要考量其搭配的common电极驱动方式. 一般来说 common电极电压若是固定, 其驱动common电极的耗电会比较小. 但是由于搭配common电压固定方式的source driver其所需的电压比较高, 反而在source driver的耗电会比较大. 但是如果使用相同的common电极驱动方式, 在source driver的耗电来说,就要考量其输出电压的变动频率与变动电压大小. 一般来说, 在此种情形下, source driver的耗电,会有 dot inversion > row inversion > column inversion > frame inversion的状况. 不过现今由于dot inversion的source driver多是使用PN型的OP, 而不是像row inversi on是使用rail to rail OP, 在source driver中OP的耗电就会比较小. 也就是说由于source driver在结构及电路上的改进, 虽然先天上它的输出电压变动频率最高也最大(变动电压最大接近10伏特,而row inversion面板由于多是使用common电极电压变动的方式,其source driver的变动电压最大只有5伏特,耗电上会比较小), 但dot inversion面板的整体耗电已经减低很多了. 这也就是为什么大多数的液晶显示器都是使用dot inversion的方式.TFT LCD液晶显示器的驱动原理(二)上次跟大家介绍液晶显示器的驱动原理中有关储存电容架构,面板极性变换方式,以及common电压的驱动方式.这次我们延续上次的内容,继续针对feed through电压,以及二阶驱动的原理来做介绍.简单来说Feed through电压主要是由于面板上的寄生电容而产生的,而所谓三阶驱动的原理就是为了解决此一问题而发展出来的解决方式,不过我们这次只介绍二阶驱动,至于三阶驱动甚至是四阶驱动则留到下一次再介绍.在介绍feed through电压之前,我们先解释驱动系统中gate driver 所送出波形的timing图.SVGA分辨率的二阶驱动波形我们常见的1024*768分辨率的屏幕,就是我们通常称之为SVGA分辨率的屏幕.它的组成顾名思义就是以1024*768=7864 32个pixel来组成一个画面的数据.以液晶显示器来说,共需要1024*768*3个点(乘3是因为一个pixel需要蓝色,绿色,红色三个点来组成.)来显示一个画面.通常在面板的规划,把一个平面分成X-Y轴来说,在X轴上会有1024*3=3072列.这3072列就由8颗384输出channel的source driver来负责推动.而在Y轴上,会有768行.这768行,就由3颗256输出channel 的gate driver来负责驱动.图1就是SVGA分辨率的gate driver输出波形的timing图.图中gate 1 ~ 768分别代表着76 8个gate driver的输出.以SVGA的分辨率,60Hz的画面更新频率来计算,一个frame的周期约为16.67 ms.对gate 1来说,它的启动时间周期一样为16.67ms.而在这16.67 ms之间,分别需要让gate 1 ~ 768共768条输出线,依序打开再关闭.所以分配到每条线打开的时间仅有16.67ms/768=21.7us而已.所以每一条gate driver打开的时间相对于整个frame是很短的,而在这短短的打开时间之内,source driver再将相对应的显示电极充电到所需的电压.而所谓的二阶驱动就是指gate driver的输出电压仅有两种数值,一为打开电压,一为关闭电压.而对于common电压不变的驱动方式,不管何时何地,电压都是固定不动的.但是对于common电压变动的驱动方式,在每一个frame开始的第一条gate 1打开之前,就必须把电压改变一次.为什么要将这些输出电压的timing介绍过一次呢?因为我们接下来要讨论的feed thr ough电压,它的成因主要是因为面板上其它电压的变化,经由寄生电容或是储存电容,影响到显示电极电压的正确性.在LCD 面板上主要的电压变化来源有3个,分别是gate driver电压变化,source driver电压变化,以及common电压变化.而这其中影响最大的就是gate driver电压变化(经由Cgd或是Cs),以及common电压变化(经由Clc或是Cs+Clc).Cs on common架构且common电压固定不动的feed through电压我们刚才提到,造成有feed through电压的主因有两个.而在common电压固定不动的架构下,造成feed through电压的主因就只有gate driver的电压变化了.在图2中,就是显示电极电压因为feed through电压影响,而造成电压变化的波形图.在图中,请注意到gate driver打开的时间,相对于每个frame的时间比例是不正确的.在此我们是为了能仔细解释每个f rame的动作,所以将gate driver打开的时间画的比较大.请记住,正确的gate driver打开时间是如同图1所示,需要在一个frame的时间内,依序将768个gate driver走线打开的.所以每个gate走线打开的时间,相对于一个frame的时间,是很短的.当gate走线打开或关闭的那一瞬间,电压的变化是最激烈的,大约会有30~40伏特,再经由Cgd的寄生电容,影响到显示电极的电压.在图3中,我们可以看到Cgd寄生电容的存在位置.其实Cgd的发生,跟一般的CMOS电路一样,是位于MOS的gate 与drain端的寄生电容.但是由于在TFT LCD面板上gate端是接到gate driver输出的走线,因此一但在gate driver输出走在线的电压有了激烈变化,便会影响到显示电极上的电压.在图2之中,当Frame N的gate走线打开时,会产生一个向上的feed through电压到显示电极之上.不过此时由于gate走线打开的缘故,source driver会对显示电极开始充电,因此即便一开始的电压不对(因为feed through电压的影响),source driver仍会将显示电极充电到正确的电压,影响便不会太大.但是如果当gate走线关闭的时候,由于source driver已经不再对显示电极充电,所以gate driver关闭时的电压压降(30~40伏特),便会经由Cgd寄生电容feed through到显示电极之上,造成显示电极电压有一个feed through的电压压降,而影响到灰阶显示的正确性.而且这个feed through电压不像gate走线打开时的feed through电压一样,只影响一下子,由于此时source driver已经不再对显示电极充放电,feed through电压压降会一值影响显示电极的电压,直到下一次gate driver走在线的电压再打开的时后.所以这个feed through电压对于显示画面的灰阶的影响,人眼是可以明确的感觉到它的存在的.而在Frame N+1的时候,刚开始当gate driver走线打开的那一瞬间,也会对显示电极产生一个向上的feed through电压,不过这时候由于gate已经打开的缘故,source driver会开始对显示电极充电,因此这个向上的feed through电压影响的时间便不会太长.但是当gate走线再度关闭的时候,向下的feed through电压便会让处在负极性的显示电极电压再往下降,而且受到影响的负极性显示电压会一直维持到下一次gate走线再打开的时候.所以整体来说,显示电极上的有效电压,会比source driver的输出电压要低.而减少的电压大小刚好为gate走线电压变化经由Cgd的feed through电压.这个电压有多大呢?在图4中,我们以电荷不灭定律,可以推导出feed through电压为 (Vg2 – Vg1) * Cgd / (Cgd + Clc + Cs) .假设Cg d=0.05pF,而Clc=0.1pF, Cs=0.5pF且gate走线从打开到关闭的电压为 –35伏特的话. 则feed through电压为 –35*0.0 5 / (0.05+0.1+0.5) = 2.69伏特. 一般一个灰阶与另一个灰阶的电压差约仅有30到50 mV而已(这是以6 bit的分辨率而言,若是8 bit分辨率则仅有3到5 mV而已).因此feed through电压影响灰阶是很严重的.以normal white的偏光板配置来说,会造成正极性的灰阶会比原先预期的来得更亮,而负极型的灰阶会比原先预期的来得更暗.不过恰好feed through电压的方向有一致性,所以我们只要将common电压向下调整即可.从图2中我们可以看到,修正后的common电压与原先的comm on电压的压差恰好等于feed through电压.Cs on common架构且common电压变动的feed through电压图5为Cs on common且common电压变动的电压波形,由于其common电压是随着每一个frame而变动的,因此跟common 电压固定的波形比较起来.其产生的feed through电压来源会再多增加一个,那就是common电压的变化.这个common电压的变化,经由Clc+Cs的电容,便会影响到显示电极的电压.且由于整个LCD面板上所有显示点的Clc与Cs都是接到common电压,所以一但common电压有了变化,受影响的就是整个面板的所有点.跟前面gate电压变化不一样的是,gate电压变化影响到的只是一整行的显示点而已.不过Common电压变化虽然对显示电极的电压有影响,但是对于灰阶的影响却没有像gate电压变化来的大.怎么说呢?如果我们使用跟前面一样的电容参数值,再套用图6所推导出来的公式,再假设Common电压由0伏特变到5伏特,则common电压变化所产生的feed through电压为(5 -0)*(0.1pF+ 0.5pF) / (0.05pF + 0.1pF +0.5pF) = 5 * 0.6 /0.65=4.62伏特.虽然显示电极增加这么多电压,但是common电极也增加了5伏特.因此在Clc两端,也就是液晶的两端,所看到的压差变化,就只有4.62-5=0.38伏特而已.跟之前gate走线电压变化所产生的feed through电压2.69伏特比较起来要小的多了,所以对灰阶的影响也小多了.且由于它所产生的feed through电压有对称性,不像Gate走线所产生的feedthrough电压是一律往下,所以就同一个显示点来说,在视觉对灰阶的表现影响会比较小.当然啦,虽然比较小,但是由于对整个LCD面板的横向的768行来说, common电压变化所发生的时间点,跟gate走线打开的时间间隔并不一致,所以对整个画面的灰阶影响是不一样的.这样一来,就很难做调整以便改进画面品质,这也是为什么common电压变动的驱动方式,越来越少人使用的缘故.Cs on gate架构且common电压固定不动的feed through电压图7是Cs on gate且common电压固定不动的电压波形图.它并没有common电压变化所造成的feed through电压,它只有由于gate电压变化所造成的feed through电压.不过它跟Cs on common不一样的是,由gate电压变化所造成的feed th rough电压来源有两个地方,一个是自己这一条gate走线打开经由Cgd产生的feed through电压,另一个则是上一条gate 走线打开时,经由Cs所产生的feed through电压.经由Cgd的feed through电压跟前面所讨论过的状况是一样的,在这边就不再提了.但是经由Cs的feed through电压,是因为Cs on gate的关系,如图3所示.Cs on gate的架构,它的储存电容另一端并不是接到common电压,而是接到前一条gate走线,因此在我们这一条gate走线打开之前,也就是前一条gate走线打开时,在前一条gate走线的电压变化,便会经由Cs对我们的显示电极造成feed through电压.依照图8的公式,同时套用前面的电容参数与gate电压变化值,我们可得到此一feed through电压约为 35*0.5pF/(0.5pF+0.1pF+0.05pF)=26.92伏特.这样的feed through电压是很大的,不过当前一条gate走线关闭时,这个feed through电压也会随之消失.而且前一条gat e走线从打开到关闭,以SVGA分辨率的屏幕来说,约只有21.7us的时间而已.相对于一个frame的时间16.67ms是很短的.再者当前一条gate走线的feed through电压影响显示电极后,我们这一条的gate走线也随之打开,source driver立刻将显示电极的电压充放电到所要的目标值.从这种种的结果看来,前一条gate走线的电压变化,对于我们的显示电极所表现的灰阶,几乎是没有影响的.因此对于Cs on gate且common电压固定不动的驱动方式来说,影响最大的仍然是gate走在线电压变化经由Cgd产生的feed through电压,而其解决方式跟前面几个一样,只需将common电压往下调整即可.Cs on gate架构且common电压变动的feed through电压图9是Cs on gate架构且common电压变动的feed through电压波形图.这样子的架构,刚好有了前面3种架构的所有缺点,那就是 gate走线经由Cgd的feed through电压,和前一条gate走线经由Cs的feed through电压,以及Common电压变化经由Clc的feed through电压.可想而知,在实际的面板设计上几乎是没有人使用这种架构的.而这4种架构中最常用的就是 Cs on gate架构且common电压固定不动的架构.因为它只需要考虑经由Cgd的feed through电压,而Cs on gate的架构可得到较大的开口率的缘故.。

/*---—-—--—--—---—--—-——------—-—--—--—————----—-——----—-—-—-————-320x240彩屏液晶驱动程序-——----—--—--—-—-———-——--——-————-——---—--—-—-—----———-----—-——--*/#include"R61505.h"#include”reg52.h”/*-——-——--—-—-———-—————---—-—----—----—--—-—-———------————----——--全局变量-—--—--——--——————————----————-—--——-—--——-—-—--—---—-———--———-—-*/#define WINDOW_XADDR_START 0x0050 // Horizontal Start Address Set#define WINDOW_XADDR_END 0x0051 // Horizontal End Address Set#define WINDOW_YADDR_START 0x0052 // Vertical Start Address Set#define WINDOW_YADDR_END 0x0053 // Vertical End Address Set#define GRAM_XADDR 0x0020 // GRAM Horizontal Address Set#define GRAM_YADDR 0x0021 // GRAM Vertical Address Set#define GRAMWR 0x0022 // memory write#define DataPort P0 //数据口使用DataPort/*——-——————--—-------——------——-—-—-—-———--—-—-————-—-—--——--—-—--定义TFT硬件控制端口--—————-—-—--—————--——-———————-——-——--———----—-——-—--—-—-———————*/sbit CS =P2^2; //片选sbit RES =P2^1; //复位sbit RS =P2^5; //数据/命令选择sbit RW =P2^4; //写数据/命令//================/*-———-———-——---——--———-—————-—————--—--—-———-—-————————--—----—-—清屏函数输入参数:bColor 清屏所使用的背景色——-—-—-—--————----—————-—-—-———-———--—-—---—---—---—-—-—----——--*/void CLR_Screen(unsigned int bColor){unsigned int i,j;LCD_SetPos(0,240,0,320);//320x240for (i=0;i<320;i++){}/*—-—-—-——---——------———--—--—--—--——--———--———-———-—-——-——-—---—-显示英文字符输入参数:x 横坐标y 纵坐标c 需要显示的字符fColor 字符颜色bColor 字符背景颜色-———————---——-—-——-——-—-——-————-———-——--------—-—————--—-—-—---—*/#include ”8X16。

通过编写verilog代码实现OLED驱动和内容显示的

解决方案

本系列所有演示实验均出自由东南大学汤勇明教授、张圣清教授与Xilinx大学计划经理陆佳华先生所编着的教材《搭建你的数字积木·数字电路与逻辑设计(Verilog HDL&Vivado版)》。

此教材为教育部Xilinx公司产学合作专业综合改革重点支持项目,并作为Xilinx公司大学计划指定教材。

本书系统论述了数字电路与逻辑设计的理论、方法与实践技术。

全书基于Verilog HDL与Vivado开发环境,共18章,详尽介绍了如下内容:逻辑设计与Vivado基础、布尔代数与Verilog HDL基础、组合逻辑电路设计基础、时序逻辑电路设计基础、有限状态机设计基础、逻辑设计工程技术基础、Vivado数字积木流程、串行通信接口控制器、RAM接口控制器、字符点阵

显示模块接口控制器、VGA接口控制器、数字图像采集、数字逻辑系统设计案例、单周期CPU设计案例、数字信号处理设计案例(FIR)、数字图像处理设计案例、大学生FPGA设计案例以及Xilinx资源导读。

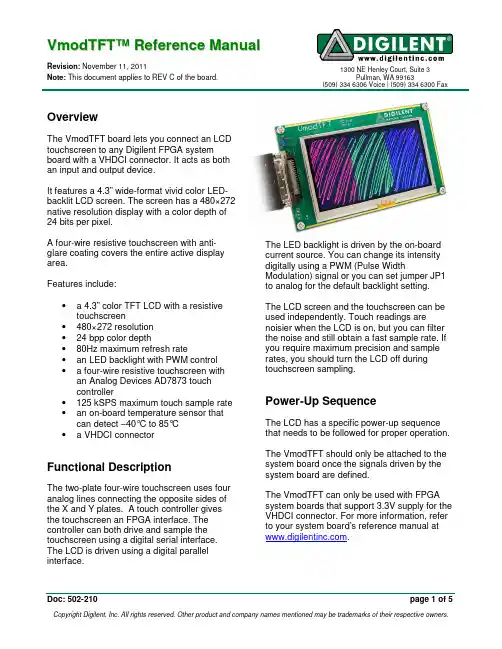

FPGA 驱动触摸屏(TFT)发表于2010 年09 月07 日由hulin 1,830 views可视化的操作已经广泛的深入我们的生活方方面面了,自己在做一些项目和实验都要用到可视化。

我这儿把ALTERA公司的飓风二系列中的ep2c5接上触摸屏,本来是R[7:0],G[7:0]和B[7:0]。

也就是一个像素的数据量就是3字节,但由于很多DSP或者单片机数据总线格式一般是16bit和32bit。

本人在这儿使用16bit,根据人的视觉感受,我们把24bit抽取出16bit。

格式为pixdata[15:0]={R[7:3],G[7:2],B[7:3]}取其每个色相的高位(取R高5位,取G高6位,取B高5位,组成RBG565格式)。

虽然在每一个像素都有色相不全,但是这样基本能显示所有的图片。

FPGA的程序模块根据TFT LCD的显示控制时序编写Verilog代码,以实现显示图片的功能。

其时序如图:一、FPGA LCD显示模块的Verilog代码:module TftControl(// inputsreset,tftcs,clk,R_in,G_in,B_in,//outputshsync,vsync,R,G,B,pixclk,tften,startpicture,pictureclk);//inputsinput reset;input tftcs;input clk;input [4:0] R_in;input [5:0] G_in;input [4:0] B_in;//outputs output hsync;output vsync;output [4:0] R;output [5:0] G;output [4:0] B;output startpicture; output pictureclk;output pixclk;output tften;wire hsync;wire vsync;wire startpicture;reg tften;reg [4:0] R;reg [5:0] G;reg [4:0] B;reg pixclk;reg pictureclk;reg [10:0] pix_count;reg [10:0] line_count;reg [2:0] counter;// 320 by 240 VGA timing parameters// horizontal timing parametersparameter hsync_end = 30; //sync pulse, 320×240 = 96parameter hblank_begin = 68; // = sync + back porch, 320×240 = 68parameter hblank_end = 388; // = sync + back porch + h_resolution, 320×240 = 388parameter hline_end = 408; // = sync + back porch + h_resolution + front porch, 320×240 = 408// vertical timing parametersparameter vsync_end = 3; //sync pulse, 320×240 = 3parameter vblank_begin = 18; // = sync + back porch, 320×240 = 18parameter vblank_end = 258; // = sync + back porch + v_resolution, 320×240 = 258parameter vframe_end = 262; // = sync + back porch + v_resolution + front porch, 320×240 = 262// these are all the syncs and blanks for the video timingassign hsync = (pix_count < hsync_end) ? 1′b0 : 1′b1;assign vsync = (line_count < vsync_end) ? 1′b0 : 1′b1; // active indicates that the color value should be output, or black when not activeassign startpicture= ((line_count > (vblank_begin-1)) && (line_count < (vblank_end)) && (pix_count > (hblank_begin –1)) && (pix_count < (hblank_end))) ? 1′b1 : 1′b0;always @ (posedge clk)beginif (!reset)begincounter<=0;tften<=1;endelse if(!tftcs)begintften<=0;counter<=counter+1;pixclk<=counter[2];R <= (startpicture) ? R_in : 5′h00; // red color value output to video DACG <= (startp icture) ? G_in : 6′h00; // green color value output to video DACB <= (startpicture) ? B_in : 5′h00; // blue color value output to video DACpictureclk<=(startpicture) ? counter[2]:1′bz ;endelsebegintften<=1;R <= 5′hzz; // red color value output to video DACG <= 6′hzz; // green color value output to video DACB <= 5′hzz; // blue color value output to video DACendend// the heart of the time base these two counters, the pixel and line countersalways @ (posedge pixclk)beginif (!reset)beginpix_count <= 11′h0;line_count <= 11′h0;endelsebeginif(pix_count == (hline_end-1))beginpix_count <= 11′h0;if(line_count == (vframe_end-1))beginline_count <= 11′h0;endelsebeginline_count <= line_count + 1′b1;endendelsebeginpix_count <= pix_count + 1′b1;endendendendmodule触摸屏输入由于面板上的触摸屏产生的输出信号不是直接的数字电平,其产生的为模拟电压。

通过压力传感电阻把触摸笔在面板上的位置通过传感电阻转换成不同的电压值通过+X,+Y,-X,-Y四个脚输出模拟信号。

如图所示:电阻式触摸屏专用控制器ADS7843的应用就构成了集文字图形笔输入控制、编辑和无线传送于一体的无线掌上电脑产品。

ADS7843是BURR-BROWN公司专用于4线电阻式触摸屏的12位模/数采样转换器,单一电源供电、完全降功耗模式、转换速度快。

ADS7843大量用在电池供电PDA(personaldigitalassistants)和手持便携式装置中。

通过FPGA IO 脚对ADS7843进行接口控制就能获取触摸屏位置转换信号,FPGA作为液晶显示控制器就能将显示缓冲区数据送到液晶屏上正确显示。

二、FPGA触摸输入Verilog程序:module TouchControl(mclk,rst,csn,dclk,din,dout,busy,tint,datareg,datax1,datax2,datay1,datay2,LCD_POWERON,dout_en);input mclk,rst,dout,busy,tint;output csn,dclk,din;output [11:0]datareg,datax1,datax2,datay1,datay2;output wire LCD_POWERON=1′bz;output dout_en;reg [10:0] clkcnt;always @ (posedge mclk or negedge rst)if(!rst)clkcnt<=11′d0;elseclkcnt<=clkcnt+1′b1;wire clk_32=clkcnt[9];reg csn,flagxy,startflag;reg [1:0] cnty;reg [3:0] cmdx,waitdin,waitdin2;reg [7:0] cmd;reg [9:0] tintflag;reg din;reg [19:0] endcnt;wire dclk=(!cs n)?clk_32:1′b0;always @ (negedge clk_32 or negedge rst)if(!rst)beginstate<=6′d0;csn<=1′b1;cmdx<=4′d0;din<=1′b0;waitdin<=4′d0;flagxy<=1′b0;cnty<=2′d0;waitdin2<=4′d0;startflag<=1′b0;endcnt<=20′d0;endelsecase(state)6′d0:beginstate<=6′d1;end6′d1:beginif(!tint)state<=6′d2;elsestate<=state;end6′d2:begincmd<=8′b10010000;state<=3′d3;end6′d3:begincsn<=1′b0;if(cmdx!=4′d7)begindin<=cmd[7];cmd<=(cmd<<1);cmdx<=cmdx+1′b1;state<=state;endelsedin<=cmd[7];cmdx<=4′d0;case(cnty)2′d0:begincmd<=8′b11010000;cnty<=2′d1;state<=6′d4;end2′d1:begincmd<=8′b10010000;cnty<=2′d2;state<=6′d4;end2′d2:begincmd<=8′b11010000;cnty<=2′d3;state<=6′d4;end2′d3:begincnty<=2′d0;state<=6′d5;endendcaseendend6′d4:beginif(waitdin!=4′d15)beginwaitdin<=waitdin+1′b1;din<=1′b0;state<=state;endelsebeginwaitdin<=4′d0;din<=1′b0;state<=3′d3;endend6′d5:beginif(waitdin2!=4′d15)beginwaitdin2<=waitdin2+1′b1;state<=state;endelsebeginwaitdin2<=4′d0;csn<=1′b1;state<=6′d6;//if(!startflag) begin state<=6′d1;startflag<=1′b1;end//else begin state<=6′d1;startflag<=1′b0;endendend6′d6:beginif(endcnt==20′d10000)beginendcnt<=20′d0;state<=6′d1;endelsebeginendcnt<=endcnt+1′b1;state<=state;endendendcasereg [11:0] datareg,datax1,datax2,datay1,datay2;reg [3:0] readcnt,statedin,readxy;reg dout_en;always @ (posedge dclk or negedge rst)if(!rst)begindatareg<=12′d0;datax1=12′d0;datax2=12′d0;datay1=12′d0;datay2=12′d0;readcnt<=4′d0;statedin<=4′d0;readxy<=4′d0;dout_en<=1′b1;endelsebegincase(statedin)4′d0:begindout_en<=1′b1;if(busy)begin datareg<=12′d0;statedin<=4′d1; endelsestatedin<=statedin;end4′d1:begincase(readcnt)4′d0:begin datareg[11]<=dout;readcnt<=4′d1;statedin<=statedin;end4′d1:begin datareg[10]<=dout;readcnt<=4′d2;statedin<=st atedin;end4′d2:begin datareg[9] <=dout;readcnt<=4′d3;statedin<=statedin;end4′d3:begin datareg[8] <=dout;readcnt<=4′d4;statedin<=statedin;end4′d4:begin datareg[7] <=dout;readcnt<=4′d5;statedin<=stated in;end4′d5:begin datareg[6] <=dout;readcnt<=4′d6;statedin<=statedin;end4′d6:begin datareg[5] <=dout;readcnt<=4′d7;statedin<=statedin;end4′d7:begin datareg[4] <=dout;readcnt<=4′d8;statedin<=statedin;e nd4′d8:begin datareg[3] <=dout;readcnt<=4′d9;statedin<=statedin;end4′d9:begin datareg[2] <=dout;readcnt<=4′d10;statedin<=statedin;end4′d10:begin datareg[1]<=dout;readcnt<=4′d11;statedin<=statedin;end4′d11:begin datareg[0]<=dout;readcnt<=4′d0;statedin<=4′d2;endendcaseend4′d2:begincase(readxy)4′d0:begin datay1<=datareg;readxy<=4′d1;statedin<=4′d0;end4′d1:begin datax1<=datareg;readxy<=4′d2;statedin<=4′d0;end4′d2:begin datay2<=datareg;readxy<=4′d3;statedin<=4′d0;end4′d3:begin datax2<=datareg;readxy<=4′d0;statedin<=4′d0;dout_en<=1′b0;end endcaseendendcaseendendmodule。