FPGA驱动VGA显示VHDL程序(彩条,可用)

- 格式:doc

- 大小:57.00 KB

- 文档页数:7

四川师范大学成都学院电路与电子技术课程设计VGA显示接口设计学生姓名秦谌磊学号2012101315所在学院通信工程学院专业名称通信工程班级2012级移动通信2班指导教师胡迎刚成绩四川师范大学成都学院二○一四年十二月课程设计任务书VGA显示接口设计内容摘要:本文利用现场可编程逻辑器件FPGA产生VGA时序信号和彩条图像信号,并将其作为信号源,应用于彩色等离子显示器的电路开发,方便彩色等离子显示器驱动控制电路的调试。

FPGA芯片具有可靠性高、编程灵活、体积小等优点,实验经过软硬件调试,最终在显示器上显示彩条正确图像。

利用此原理,可以设计更多的彩色图像,且可将采集的图像进行实时显示,将此作为信号源,应用于显示器电路的开发或某些嵌入式系统中,进行视频设备的调试与性能分析或系统中信号处理模块的调试与性能分析等。

关键词:FPGA VGA 显示接口VGA Interface of display of design Abstract:VGA-timing signals and color strip image were obtained by using FPGA. The signals were used as sources when developing the circuits of color plasma display panel, and it took great convenience to the debugging of the driving and controlling circuit of color plasma display panel. The FPGA chip has the advantages of high reliability, small volume, flexible programming, just because of this, the test could achieve the desired results, display screen displays color bar signals. According to this principle, we can design color image more, and make the image real-time display, such as the signal source, used in display circuit development or some embedded systems, video equipment debugging and performance analysis of the system signal processing module debugging and performance analysis.Keywords:FPGA VGA Interface of display目录前言 (1)1 VGA接口概述 (1)1.1 VGA接口 (1)1.2 VGA显示 (2)1.3 VGA信号时序 (3)1.4 VGA图形编码 (4)2 EDA概述 (5)2.1 EDA技术及其发展 (5)2.2 EDA技术开发流程 (6)2.3 Quartus II软件简介 (6)2.4硬件描述语言VHDL (7)2.5 现场可编程逻辑门阵列FPGA (7)3 设计方案 (8)3.1 总体设计框架图 (8)3.2 主模块设计 (9)3.2.1 分频模块 (9)3.2.2 VGA彩条信号产生模块 (9)4 设计实现 (10)4.1 新建工程项目 (10)4.2 选择芯片 (10)4.3 使用硬件描述语言编程 (11)4.4 锁定引脚 (11)4.5 下载 (11)5 仿真结果 (12)5.1 仿真波形 (12)5.2 下载调试 (12)6 总结 (13)附录 (14)参考文献 (17)VGA显示接口设计前言VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

EDA课程设计报告—VGA显示器彩色信号发生器电路班级:08通信A班姓名:崔儒学号: 0815231013指导老师:凌朝东摘要:VGA(Video Graphic Array)接口是与显示器进行通信的唯一接口。

通过FPGA器件控制RGB信号、行同步信号、场同步信号等信号,并参照有关标准,最后可以实现对VGA显示器的控制。

本设计与传统的图像显示方法不同,为节省储存空间在设计中采用R、G、B三种基色利用FPGA芯片和EDA设计方法,可以显示8种颜色,设计出针对性强的VGA显示控制器,而且不需要依靠计算机,既能够大大降低成本,又可以满足生产实践中不断变化的需要,同时产品的升级换代也方便迅速。

本设计采用Altera公司的EDA软件0uartus II,并以Cylone 系列FPGA器件为硬件平台进行系统设计。

关键词:VGA;FPGA:VHDL;Ouartus II目录1、系统设计 (4)2、单元电路设计 (6)3、软件设计 (8)4、系统测试 (11)5、小结 (12)6、参考文献 (12)7、附录 (13)一、系统设计1、设计要求:VGA显示器彩色信号发生器电路,能在VGA显示器上显示8种颜色的图形(条型、方块型)。

2、系统设计方案:方案一:采用传统的图像显示方法,将图像数据传回电脑在传输过程中通过CPU对图像数据信号进行控制,通过显示器显示出来。

方案二:采用FPGA和EDA的设计方法,通过FPGA器件控制RGB信号、行同步信号、场同步信号等信号,并参照有关标准,最终可以实现对VGA 的控制。

方案一为传统的图像显示方法,在传输过程中需要CPU不断对图像数据信号进行控制,这样就造成了CPU的浪费,同时系统还需要依赖电脑,降低了系统的灵活性。

方案二是利用可编程器件FPGA和EDA的设计方法,可以根据设计的需要设计出针对性比较强的VGA显示器,而且不需要依靠计算机,大大降低了成本提高了系统的灵活性。

综合上诉分析本设计中采用方案二。

浅谈用SPATAN 3E系列开发板实现彩条信号显示作者:李琳来源:《科技创业月刊》 2013年第9期李琳(武汉职业技术学院计算机系湖北武汉 430074)摘要:以研究项目“应用FPGA实现时序彩条信号显示”为依托,描述用Xilinx公司的SPATAN3E系列的FPGA开发板进行设计,再用Xilinx公司的ISE软件编程,程序验证和综合,最后将程序下载到FPGA的开发板上,实现在LCD屏的时序横条,竖条和棋盘格信号的过程。

关键词:VGA;VHDL;分频电路中图分类号:TP311文献标识码:Adoi:10.3969/j.issn.1665-2272.2013.09.0811选题背景现如今,越来越多的数字产品开始使用液晶作为显示终端。

但基于VGA标准的显示器仍是目前普及率最高的显示器。

若驱动此类显示器,需要很高的扫描频率及较短的处理时间。

所以需要用FPGA来实现对VGA显示器的驱动。

VGA是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

采用FPGA对显示器的VGA接口进行设计,数据流只需要在整个系统的内部流动,而不需要依靠计算机,增强了系统的可靠性和设计的灵活性。

2VHDL硬件描述语言美国国防部在20世纪80年代初提出了VHSIC(VeryHighSpeedIntegratedCircuit)计划,其目标之一是为下一代集成电路的生产,实现阶段性的工艺极限以及完成10万门级以上的设计,建立一项新的描述方法。

1981年提出了一种新的HDL,称之为VHSICHardwareDescriptionLanguage,简称为VHDL。

在逻辑描述上,VHDL是一种高级描述语言,适合于行为级和RTL级的描述,最适于描述电路的行为。

在设计要求上,VHDL进行电子系统设计时可以不了解电路的结构细节,而把模块的逻辑关系描述出来就可以了,设计起来比较简单。

基于FPGA的VGA图像显示1、VGA显示原理VGA标准是一种计算机显示标准,最初是由IBM公司在1987 年提出的,分辨率是640*480。

VGA 接口也叫做D_Sub 接口,是显卡上输出模拟信号的接口。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A 转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

常见的彩色显示器一般由阴极射线管(CRT) 构成,彩色由GRB(Green Red Blue) 基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB 基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。

VGA的标准参考显示时序如图1所示。

行时序和帧时序都需要产生同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四个部分。

2、方案设计由VGA的显示原理可知,该任务的关键是VGA时序控制部分和汉字图形显示部分:(1)VGA时序控制部分,采用FPGA本地50MHz时钟,根据所需时序要求,经Verilog语言编写的计数模块分频而得到,该部分十分重要,如果产生的时序有偏差,那么就会使汉字图形无法显示或显示结果混乱;(2)汉字图形显示部分,有2种方法可以实现:第1 种是在对像素进行行计数、场计数的时候,就把字库信息直接赋值给颜色信号R、G、B,这种方法虽然简单,但是控制很不灵活,需要对汉字的显示像素一一判定对应的位置,容易出现错误,不易修改,所以本次采用的是第2 种方法,第2 种方法是使用FPGA内部的一种资源来存储汉字的字库信息,然后由程序将其提取出来作为显示信号发送到VGA 接口,以实现汉字图形的显示,这样就克服了第一种方法易出错又不易修改的缺点。

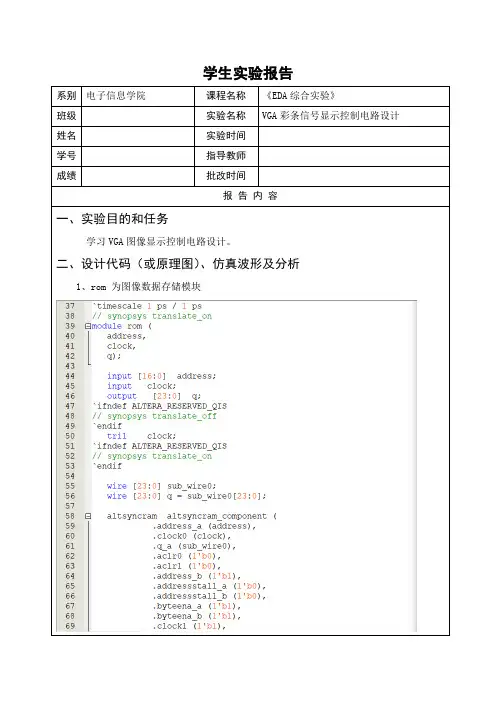

编号:EDA技术实训实训(论文)说明书题目:VGA彩条信号显示控制器设计院(系):信息与通信学院专业:电子信息工程学生姓名:***学号: ********** 指导教师:付强、陈小毛、归发第2013 年1 月4 日本设计采用EDA技术,通过FPGA芯片实现了实现VGA彩条信号的显示的设计,本文采用VHDL 硬件描述语言描述VGA彩条信号的显示电路,完成对电路的功能仿真。

通过按键来实现横彩条、竖彩条、棋盘式方格图案的选择。

显示图像分辨率为640×480,刷新率为60Hz。

与传统的设计方式相比,本设计由于采用了FPGA芯片来实现,它将大量的电路功能集成到一个芯片中,并且可以由用户自行设计逻辑功能,提高了系统的集成度和可靠性。

关键词:电子设计自动化、可编程门阵列、硬件描述语言、状态机This design used the EDA technology, through the FPGA chip realized the realization of the signal that striped VGA is adopted in this paper, the design of the VHDL hardware description language describe VGA striped signal display circuit and the completion of the function of the circuit simulation. By pressing buttons horizontal striped, perpendicular striped, chessboard type pane design choice. Display image resolution for 640 x 480, refresh rate of 60 Hz ac. Compared with the traditional design methods, the design with FPGA chip to achieve, it will be a lot of circuit function integration to a chip, and can be by the user to design logical function, improve the system integrity and reliability.Keywords:Electronic Design Automatic technology,Flied Programmable,Gate Array, Hardware Description Language, State Machine1. 绪论 (1)1.1 EDA技术的发展 (1)1.2 课程设计的任务 (1)2. 系统设计 (2)2.1 系统的工作原理 (2)2.2 VGA显示原理 (2)2.3 键盘驱动 (4)3 系统设计 (4)3.1图像信号产生模块的设计 (4)3.2 视频输出接口电路部分设计 (5)3.3 模式控制与显示部分设计 (6)3.4 VGA显示模块 (6)4 课程设计心得 (9)5 致谢 (10)参考文献 (11)附录 (12)附录A 总原理图 (12)附录B 实验现象 (12)附录C 引脚分布图 (14)附录D 实验程序 (14)1.绪论1.1 EDA技术的发展我们已经进入数字化和信息化的时代,其特点就是各种数字产品的广泛应用。

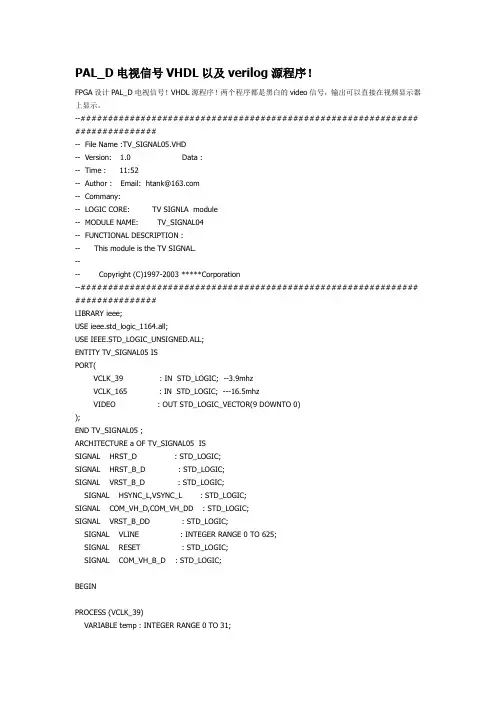

PAL_D电视信号VHDL以及verilog源程序!FPGA设计PAL_D电视信号!VHDL源程序!两个程序都是黑白的video信号,输出可以直接在视频显示器上显示。

--############################################################## ###############-- File Name :TV_SIGNAL05.VHD-- Version: 1.0 Data :-- Time : 11:52-- Author : Email: htank@-- Commany:-- LOGIC CORE: TV SIGNLA module-- MODULE NAME: TV_SIGNAL04-- FUNCTIONAL DESCRIPTION :-- This module is the TV SIGNAL.---- Copyright (C)1997-2003 *****Corporation--############################################################## ###############LIBRARY ieee;USE ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TV_SIGNAL05 ISPORT(VCLK_39 : IN STD_LOGIC; --3.9mhzVCLK_165 : IN STD_LOGIC; ---16.5mhzVIDEO : OUT STD_LOGIC_VECTOR(9 DOWNTO 0));END TV_SIGNAL05 ;ARCHITECTURE a OF TV_SIGNAL05 ISSIGNAL HRST_D : STD_LOGIC;SIGNAL HRST_B_D : STD_LOGIC;SIGNAL VRST_B_D : STD_LOGIC;SIGNAL HSYNC_L,VSYNC_L : STD_LOGIC;SIGNAL COM_VH_D,COM_VH_DD : STD_LOGIC;SIGNAL VRST_B_DD : STD_LOGIC;SIGNAL VLINE : INTEGER RANGE 0 TO 625;SIGNAL RESET : STD_LOGIC;SIGNAL COM_VH_B_D : STD_LOGIC;BEGINPROCESS (VCLK_39)VARIABLE temp : INTEGER RANGE 0 TO 31;BEGINIF (Vclk_39'EVENT AND Vclk_39= '1') THENIF TEMP>=20 THENRESET <='1';ELSERESET <='0';TEMP:= TEMP +1;END IF;END IF;END PROCESS;PROCESS (VCLK_39,reset) ----TV,VGA_TV_STVARIABLE temp_tv : INTEGER RANGE 0 TO 255;VARIABLE VLINE : INTEGER RANGE 0 TO 628; ---2003.10.20修改BEGINIF reset ='0' THEN --VGA_TV_ST='1' ORtemp_tv := 0;VLINE:= 1;ELSIF (VCLK_39'EVENT AND VCLK_39= '1') THENtemp_tv :=temp_tv + 1;IF temp_tv=252 THEN ---------0---237---238 POINT-238252temp_tv :=0;VLINE :=VLINE+ 1;END IF;IF VLINE=626 THEN-----1--617 =617VLINE:=1;END IF;IF temp_tv>=5 AND temp_tv <=22 THEN---5--22--18---------FOR HRST HRST_D<='1';-------5--22---18ELSEHRST_D <='0';END IF;IF temp_tv>=1 AND temp_tv <=52 THEN ---1--38--38------FOR HRST BANK HRST_B_D<='1';----0--51--52ELSEHRST_B_D<='0';END IF;IF VLINE>=1 AND VLINE<=23 THEN -----FOR VRST BANK--18VRST_B_D<='1';ELSIF VLINE >=311 AND VLINE <=335 THEN----21VRST_B_D<='1';ELSIF VLINE >=622 AND VLINE <=625 THEN---3 ---18+21+3=42 VRST_B_D<='1';ELSEVRST_B_D<='0';END IF;IF VLINE>=1 AND VLINE <=2 THEN --------FOR COM_VH IF temp_tv>=5 AND temp_tv<=113 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=239 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE =3 THENIF temp_tv>=5 AND temp_tv<=113 THEN-----105---111COM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THENCOM_VH_D <='1';--old-124-132---- new-131--237ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=4 AND VLINE<=5 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=6 AND VLINE<=310 THENIF temp_tv>=5 AND temp_tv<=22 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=311 AND VLINE<=312 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THENCOM_VH_D <='1';ELSEEND IF;ELSIF VLINE =313 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=239 THEN COM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=314 AND VLINE<=315 THENIF temp_tv>=5 AND temp_tv<=113 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=239 THEN COM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=316 AND VLINE<=317 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THEN COM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE =318 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE>=319 AND VLINE<=622 THENIF temp_tv>=5 AND temp_tv<=22 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;ELSIF VLINE =623 THENIF temp_tv>=5 AND temp_tv<=22 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THEN COM_VH_D <='1';ELSEEND IF;ELSIF VLINE>=624 AND VLINE<=625 THENIF temp_tv>=5 AND temp_tv<=13 THENCOM_VH_D <='1';ELSIF temp_tv>=131 AND temp_tv<=139 THENCOM_VH_D <='1';ELSECOM_VH_D <='0';END IF;END IF;END IF;END PROCESS;PROCESS( VCLK_39)BEGINIF VCLK_39'EVENT AND VCLK_39='1' THENCOM_VH_DD <= COM_VH_D;--COM_VH_B <=VRST_B_D OR HRST_B_D;COM_VH_B_D <=VRST_B_D OR HRST_B_D;--VRST_B <=VRST_B_D;--HRST <=HRST_D;--HRST_B <=HRST_B_D;END IF;END PROCESS;PROCESS( CLK_165)-- VARIABLE DATA_O : STD_LOGIC_VECTOR (7 DOWNTO 0);VARIABLE TTT : STD_LOGIC_VECTOR (9 DOWNTO 0);VARIABLE IMAGE : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF ( CLK_165'EVENT AND CLK_165='1') THENIF COM_VH_B_D ='1' THENIMAGE := (OTHERS=>'0');TTT := (OTHERS=>'0');VIDEO <= (NOT COM_VH_DD) & '0'&"00000000";ELSIF COM_VH_B_D ='0' THENTTT := TTT + 1;IF ( (VLINE >=24 AND VLINE <=124) or ( VLINE >=335 AND VLINE <=436 ) )THEN---2 IF TTT>=0 AND TTT <=75 THEN ---------FOR VIDEO OUTIMAGE:="00001111";-- TV_TT:=TV_TT+1;ELSIF TTT>=76 AND TTT <=150 THEN ---------FOR VIDEO OUTIMAGE:="00100000";-- TV_TT:=TV_TT+1;ELSIF TTT>=151 AND TTT <=225 THEN ---------FOR VIDEO OUT IMAGE:="00101111";-- TV_TT:=TV_TT+1;ELSIF TTT>=226 AND TTT <=300 THEN ---------FOR VIDEO OUT IMAGE:="01000000";-- TV_TT:=TV_TT+1;ELSIF TTT>=301 AND TTT <=375 THEN ---------FOR VIDEO OUT IMAGE:="01001111";-- TV_TT:=TV_TT+1;ELSIF TTT>=376 AND TTT <=450 THEN ---------FOR VIDEO OUT IMAGE:="01100000";-- TV_TT:=TV_TT+1;ELSIF TTT>=451 AND TTT <=525 THEN ---------FOR VIDEO OUT IMAGE:="01101111";-- TV_TT:=TV_TT+1;ELSIF TTT>=526 AND TTT <=600 THEN ---------FOR VIDEO OUT IMAGE:="11111111";-- TV_TT:=TV_TT+1;ELSEIMAGE:="00000000";END IF;ELSEIMAGE:=(OTHERS=>'0');END IF;VIDEO <= (NOT COM_VH_DD)&'1'&IMAGE;END IF;END IF;END PROCESS;END a;FPGA设计PAL_D电视信号!verilog源程序!verilog 版本:/*信号定义与说明:clk_66MHz:input clock with a frequency of 66MHz;clk_33MHz:division twice from clk_66MHz;clk_4MHz: division from clk_33MHz,as a matter of fact,its frequency is 4.125MHz; H_HIDE: 行消隐信号;V_HIDE: 场消隐信号;COM_HIDE:复合消隐信号;H_SYNC: 行同步信号;V_SYNC: 场同步信号;COM_SYNC:复合同步信号;Gray:扫描灰阶图像信号;front_balance,back_balance:前后均衡脉冲;Slot_ON_V_SYNC:场同步期中的槽脉冲;*/moduletv_sig_gen(clk_66MHz,clk_33MHz,clk_4MHz,H_HIDE,V_HIDE,H_SYNC,Gray,COM_HIDE,front_balance,ba ck_balance,Slot_ON_V_SYNC,V_SYNC,COM_SYNC);parameter size=4; //定义一个寄存器的大小,产生4MHz时钟用;input clk_66MHz;outputclk_33MHz,clk_4MHz,H_HIDE,V_HIDE,H_SYNC,Gray,COM_HIDE,front_balance,back_balance,Slot_ON_V _SYNC,V_SYNC,COM_SYNC;reg[size-1:0] reg_for_4MHz;reg[8:0] Counter_For_H_SYNC;reg[9:0] Hcounter;reg[7:0] Gray;reg[3:0] counter_for_Gray;regclk_33MHz,clk_4MHz,temp,H_HIDE,V_HIDE,H_SYNC,front_balance,back_balance,Slot_ON_V_SYNC,V_S YNC,Htongbu_mask;wire COM_HIDE,COM_SYNC;assign COM_SYNC=(front_balance|back_balance|Slot_ON_V_SYNC)|((!Htongbu_mask)&H_SYNC); assign COM_HIDE=H_HIDE||V_HIDE;always @(posedge clk_66MHz) //产生33MHz频率时钟;clk_33MHz=~clk_33MHz;always @(posedge clk_33MHz)beginif(reg_for_4MHz==0) reg_for_4MHz=1; //对寄存器进行初始化;elsebeginif(reg_for_4MHz[size-1]) clk_4MHz=~clk_4MHz; //每size个时钟脉冲clk_4MHz跳变;temp=reg_for_4MHz[size-1]; //暂存;reg_for_4MHz[size-1:1]=reg_for_4MHz[size-2:0];reg_for_4MHz[0]=temp;endendalways @(posedge clk_4MHz) //产生行消隐信号,行同步信号;begincase(Counter_For_H_SYNC)213: beginCounter_For_H_SYNC=Counter_For_H_SYNC+1;H_HIDE=~H_HIDE;end219: beginCounter_For_H_SYNC=Counter_For_H_SYNC+1;H_SYNC=~H_SYNC;end238: beginCounter_For_H_SYNC=Counter_For_H_SYNC+1;H_SYNC=~H_SYNC;end263: beginCounter_For_H_SYNC=0;H_HIDE=~H_HIDE;enddefault:Counter_For_H_SYNC=Counter_For_H_SYNC+1;endcaseendalways @(posedge clk_4MHz) //在行正程产生灰阶信号; begincase(H_HIDE)0: begincase(counter_for_Gray)12: begin //每13个4MHz时钟周期灰阶加一;counter_for_Gray=0;Gray[7:4]=Gray[7:4]+1;enddefault:counter_for_Gray=counter_for_Gray+1;endcaseend1: begincounter_for_Gray=0;Gray=0;endendcaseendalways @(posedge clk_4MHz) //产生场消隐信号;begincase(Counter_For_H_SYNC)82: case(Hcounter)286: V_HIDE=~V_HIDE;311: V_HIDE=~V_HIDE;endcase263: case(Hcounter)599:V_HIDE=~V_HIDE;624:V_HIDE=~V_HIDE;endcaseendcaseendalways @(posedge H_HIDE) //行计数;begincase(Hcounter)624: Hcounter=0;default:Hcounter=Hcounter+1;endcaseendalways @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)82: case(Hcounter)286: begin front_balance=~front_balance; Htongbu_mask=~Htongbu_mask; end 287: front_balance=~front_balance;288: front_balance=~front_balance;291: back_balance=~back_balance;292: back_balance=~back_balance;293: back_balance=~back_balance;endcase92: case(Hcounter)286: front_balance=~front_balance;287: front_balance=~front_balance;288: front_balance=~front_balance;291: back_balance=~back_balance;292: back_balance=~back_balance;293: begin back_balance=~back_balance; Htongbu_mask=~Htongbu_mask; end endcase213: case(Hcounter)286: front_balance=~front_balance;287: front_balance=~front_balance;291: back_balance=~back_balance;292: back_balance=~back_balance;endcase222: case(Hcounter)287: front_balance=~front_balance;288: front_balance=~front_balance;292: back_balance=~back_balance;293: back_balance=~back_balance;endcase263: case(Hcounter)599: begin front_balance=~front_balance; Htongbu_mask=~Htongbu_mask; end 600: front_balance=~front_balance;601: front_balance=~front_balance;604: back_balance=~back_balance;605: back_balance=~back_balance;606: back_balance=~back_balance;endcase9: case(Hcounter)599: front_balance=~front_balance;600: front_balance=~front_balance;601: front_balance=~front_balance;604: back_balance=~back_balance;605: back_balance=~back_balance;606: begin back_balance=~back_balance; Htongbu_mask=~Htongbu_mask; end endcase130: case(Hcounter)599: front_balance=~front_balance;600: front_balance=~front_balance;604: back_balance=~back_balance;605: back_balance=~back_balance;endcase140: case(Hcounter)599: front_balance=~front_balance;600: front_balance=~front_balance;604: back_balance=~back_balance;605: back_balance=~back_balance;endcaseendcaseendalways @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)79: case(Hcounter)291: V_SYNC=~V_SYNC;endcase131: case(Hcounter)601: V_SYNC=~V_SYNC;213: case(Hcounter)288: V_SYNC=~V_SYNC;endcase263: case(Hcounter)604: V_SYNC=~V_SYNC;endcaseendcaseendalways @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)213: case(Hcounter)288: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase62: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;291: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase81: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;endcase131: case(Hcounter)601: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase200: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;601: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase219: case(Hcounter)290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;291: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase68: case(Hcounter)602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;87: case(Hcounter)602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;endcaseendcaseend/*always @(posedge H_HIDE)begincase(Hcounter)286: beginif(Counter_For_H_SYNC==130) V_HIDE=~V_HIDE; //第287行的第32us时刻场消隐开始; Hcounter=Hcounter+1;end311: beginif(Counter_For_H_SYNC==130) V_HIDE=~V_HIDE;Hcounter=Hcounter+1;end599: beginif(Counter_For_H_SYNC==263) V_HIDE=~V_HIDE;Hcounter=Hcounter+1;end624: beginif(Counter_For_H_SYNC==263) V_HIDE=~V_HIDE;Hcounter=0;enddefault:Hcounter=Hcountr+1;endcaseend*//*always @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)82: case(Hcounter)286: front_balance=~front_balance;287: front_balance=~front_balance;288: front_balance=~front_balance;291: back_balance=~back_balance;292: back_balance=~back_balance;293: back_balance=~back_balance;endcase92: case(Hcounter)286: front_balance=~front_balance; 287: front_balance=~front_balance; 288: front_balance=~front_balance; 291: back_balance=~back_balance; 292: back_balance=~back_balance; 293: back_balance=~back_balance;endcase213: case(Hcounter)286: front_balance=~front_balance; 287: front_balance=~front_balance; 291: back_balance=~back_balance; 292: back_balance=~back_balance;endcase222: case(Hcounter)287: front_balance=~front_balance; 288: front_balance=~front_balance; 292: back_balance=~back_balance; 293: back_balance=~back_balance; endcase263: case(Hcounter)599: front_balance=~front_balance; 600: front_balance=~front_balance; 601: front_balance=~front_balance; 604: back_balance=~back_balance; 605: back_balance=~back_balance; 606: back_balance=~back_balance;endcase9: case(Hcounter)599: front_balance=~front_balance; 600: front_balance=~front_balance; 601: front_balance=~front_balance; 604: back_balance=~back_balance; 605: back_balance=~back_balance; 606: back_balance=~back_balance;endcase130: case(Hcounter)599: front_balance=~front_balance; 600: front_balance=~front_balance; 604: back_balance=~back_balance; 605: back_balance=~back_balance;endcase140: case(Hcounter)599: front_balance=~front_balance;600: front_balance=~front_balance;604: back_balance=~back_balance;605: back_balance=~back_balance;endcaseendcaseendalways @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)82: case(Hcounter)291: V_SYNC=~V_SYNC;endcase263: case(Hcounter)288: V_SYNC=~V_SYNC;603: V_SYNC=~V_SYNC;endcase131: case(Hcounter)601: V_SYNC=~V_SYNC;endcaseendcaseendalways @(posedge clk_4MHz)begincase(Counter_For_H_SYNC)263: case(Hcounter)288: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase117: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase136: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase253: case(Hcounter)289: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase6: case(Hcounter)290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;291: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;604: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase118: case(Hcounter)290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;291: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase137: case(Hcounter)290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;endcase249: case(Hcounter)290: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;602: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;603: Slot_ON_V_SYNC=~Slot_ON_V_SYNC;604: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcase131: case(Hcounter)601: Slot_ON_V_SYNC=~Slot_ON_V_SYNC; endcaseendcase*/endmodule。

VGA显示器控制电路论文前言VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

利用FPGA 芯片和EDA设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA显示控制器,不仅能够大大的降低成本,还可以满足生产实践中不断变化的用户需要,产品升级换代方便迅速。

在本设计中采用Altera公司的EDA软件工具Quartus II,并以Cyclone II 系列的FPGA的器件作为主实现硬件平台的设计。

一、FPGA的原理FPGA 是Filed Progranmmable Gate Array的缩写,即现场可编程逻辑阵列。

FPGA是在CPLD的基础上发展起来的新型高性能可编程逻辑器件它一般采用SRAM工艺,也有一些专用器件采用Flash工艺或反熔丝(Anti_Fuse)工艺等。

FPGA的集成度很高,其器件密度从数万系统门到数千万系统门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。

FPGA的基本组成部分有可编程输入/输出单元,基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元、内嵌专用硬核等。

FPGA 的主要器件供应商有Xilinx、 Altera、 Lattice、 Actel和 Atmel 等。

二、 VGA转换接口的简单描述本设计另外自制VGA接口电路。

VGA时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA时序标准产生相应的脉冲信号。

对于普通的VGA显示器,其引出线的共含5个信号:G,R,B(三基色信号),HS(行同步信号),VS(场同步信号)。

在五个信号时序驱动时,VGA显示器要严格遵循“VGA工业标准”,即640Hz×480 Hz×60Hz模式。

下图(1)为VGA显示控制器控制CRT显示器VGA(Video Graphic Array)接口,即视频图形阵列,也叫做D-Sub接口,是15针的梯形插头,分3排,每排5个,传输模拟信号。

fpga课程设计报告彩灯实验一、课程目标知识目标:1. 学生能理解FPGA的基本原理和结构,掌握彩灯实验相关的硬件描述语言(HDL)基础;2. 学生能描述数字电路设计的基本流程,并运用FPGA设计简单的数字电路;3. 学生掌握彩灯实验的原理,能够解释彩灯显示背后的逻辑控制过程。

技能目标:4. 学生能够运用所学知识,设计并实现一个基于FPGA的彩灯控制电路;5. 学生通过实际操作,提高问题解决能力和实验操作技能,包括电路调试和故障排查;6. 学生能够利用FPGA设计软件进行电路设计和仿真,并完成硬件的实现和测试。

情感态度价值观目标:7. 学生通过实验探究,培养对电子工程领域的兴趣,增强创新意识和实践能力;8. 学生在小组合作中,提升团队协作能力和沟通技巧,理解集体智慧的重要性;9. 学生能够在实验过程中,形成良好的工程伦理观念,认识到技术对社会发展的积极影响和责任。

二、教学内容本课程教学内容围绕FPGA的原理与应用,结合彩灯实验项目,进行以下组织和安排:1. FPGA基础知识:- 数字电路设计基础;- FPGA原理与结构;- 硬件描述语言(HDL)入门。

2. 彩灯实验原理与设计:- 彩灯显示原理;- FPGA在彩灯控制中的应用;- 彩灯控制电路设计流程。

3. 教学大纲与进度安排:- 第一周:FPGA基本原理学习,了解硬件描述语言;- 第二周:数字电路设计基础,学习彩灯显示原理;- 第三周:彩灯控制电路设计,进行FPGA编程与仿真;- 第四周:电路调试与测试,优化设计方案。

4. 教材关联内容:- 教材第3章:“数字电路设计基础”;- 教材第4章:“FPGA原理与结构”;- 教材第5章:“硬件描述语言(HDL)应用”;- 教材第6章:“数字电路设计实例”。

5. 实践环节:- 彩灯控制电路设计实践;- FPGA编程与仿真;- 电路调试与故障排查。

三、教学方法针对FPGA课程设计报告彩灯实验,采用以下多样化的教学方法,以激发学生的学习兴趣和主动性:1. 讲授法:- 对FPGA基本原理、数字电路设计基础和硬件描述语言(HDL)等理论知识进行系统讲解,为学生奠定扎实的理论基础。

毕业设计(论文)任务书基于FPGA的LCD驱动显示电路的设计与实现摘要本课题主要任务是设计基于FPGA的LCD驱动电路的设计和实现,兼顾好程序的易用性,以方便之后模块的移植和应用。

控制器部分采用Verilog语言编写,主体程序采用了状态机作为主要控制方式。

最后实现使用FPGA在LCD上显示任意的英文字符和阿拉伯数字,另外要能根据输入数据的变化同步变化LCD上显示的内容。

同时要能将储存模块中的数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

本文中对FPGA,LCD,ModelSim,Xilinx ISE8.2i硬件设计工具等进行了简单的介绍,对其功能进行了简单的描述,并了解了LCD液晶显示器的发展历史,日常应用以及相对比于其他种类显示器的优缺点,并对基于FPGA的LCD液晶显示器驱动电路未来的发展趋势进行了展望。

关键词:FPGA,LCD,状态机,VerilogDesign and Implementation of LCD Drive DisplayCircuit based on FPGAAbstractIn this project, the main object is to design a LCD controller based on FPGA, and at the same time emphasize on the convenience for the later application and migration.The program of the controller is written by Verilog language, and the main body of the program used state machine as the primary control method. displayed picture which was put earlier.In this project, I finally realized the following function. The first one is to display any English and figureon character any position of the display screen. The second one is the display information will instantaneously update as the input data changes.The research of this project will contribute to the developing process of those products which use FPGAs, especially those products also use LCD. And at the same time, it can reduce dramatically on the developing time. In addition, for the convenience of this controller, more and more FPGA based products will come out with LCD screen. This change will enhance the interaction between human and the machine, and bring innovation to the industry and our lives.In this project, FPGA, LCD, ModelSim, Xilinx ISE8.2 I hardware design tools simply introduces its functions were a simple description, and understanding the LCD monitor the development history, and relative everyday applications than in other types of monitor based on FPGA advantages and disadvantages, and the LCD monitor driver circuit future development trends are discussed.Key words:, FPGA, LCD, State Machine, Verilog目录任务书 (I)摘要 ....................................................错误!未定义书签。

《FPGA设计与应用》实验指导书某某编武汉理工大学华夏学院2011年9月前言一、实验课目的数字电路与系统设计实验课是电子工程类专业教学中重要的实践环节,包括了ISE开发环境基本操作及FPGA的基本原理、基带传输系统的设计、Uart串口控制器电路的设计、PS/2接口的设计、VGA显示接口设计。

要求学生通过实验学会正确使用EDA技术,掌握FPGA器件的开发,熟练使用ISE开发环境,掌握Verilog语言的编程,掌握数字电路和系统的设计。

通过实验,使学生加深对课堂专业教学内容的理解,培养学生理论联系实际的能力,实事求是,严谨的科学作风,使学生通过实验结果,利用所学的理论去分析研究EDA技术。

培养学生使用Basys 2开发板的能力以及运用实验方法解决实际问题的能力。

二、实验要求:1.课前预习①认真阅读实验指导书,了解实验内容;②认真阅读有关实验的理论知识;③读懂程序代码。

2.实验过程①按时到达实验室;②认真听取老师对实验内容及实验要求的讲解;③认真进行实验的每一步,观察程序代码与仿真结果是否相符;④将实验过程中程序代码和仿真结果提交给老师审查;⑤做完实验后,整理实验设备,关闭实验开发板电源、电脑电源后方可离开。

3.实验报告①按要求认真填写实验报告书;②认真分析实验结果;③按时将实验报告交给老师批阅。

三、实验学生守则1.保持室内整洁,不准随地吐痰、不准乱丢杂物、不准大声喧哗、不准吸烟、不准吃东西;2.爱护公务,不得在实验桌及墙壁上书写刻画,不得擅自删除电脑里面的文件;3.安全用电,严禁触及任何带电体的裸露部分,严禁带电接线和拆线;4.任何规章或不按老师要求操作造成仪器设备损坏须论价赔偿。

目录实验一Uart通用串口接口的设计 (4)实验二PS/2接口的设计 (28)实验三VGA显示接口设计 (30)附录一 basys 2开发板资料 (36)实验一 Uart串口控制接口电路的设计一、实验目的1.掌握分频模块的设计方法。

FPGA入门系列实验教程——数码管动态显示FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,它可以通过编程的方式实现各种数字逻辑电路的功能。

在FPGA入门的过程中,了解如何使用数码管进行动态显示是一项非常基础而重要的实验。

本文将向读者介绍如何使用FPGA实现数码管的动态显示,并提供相关的实验教程。

一、实验目的本实验的目的是通过FPGA控制数码管以一定的时间间隔显示不同的数字或字符。

通过本实验的学习,读者可以了解到FPGA的编程方式和数码管的控制原理,并初步掌握FPGA的基本应用。

二、实验材料和准备1. FPGA开发板(如Xilinx Spartan系列)2.七段数码管模块3.连接线三、实验步骤1.搭建电路连接将开发板上的数码管模块通过连接线与FPGA的GPIO引脚相连接,确保连接正确无误。

2.创建工程打开FPGA开发环境(如Xilinx ISE),创建一个新的工程。

3.编写代码在创建的工程中,通过HDL语言(如Verilog或VHDL)编写数码管控制的代码。

以下是一个简单的Verilog代码示例:module seven_segment_displayinput wire clk,output wire [6:0] seg,output wire [3:0] anreg [23:0] count;reg [3:0] digit;reg [6:0] segment;count <= count + 1;digit <= 0;digit <= 1;digit <= 2;digit <= 3;count <= 0;endendassign seg = segment;assign an = digit;endmodule以上代码实现了数码管的动态显示功能。

其中,clk为时钟信号,seg为七段数码管的引脚,an为数码管的位选引脚。

实验报告书实验项目名称:彩灯循环控制器的设计实验项目性质:综合性实验所属课程名称:VHDL程序设计实验实验计划学时:4一、实验目的掌握VHDL程序设计方法二、实验内容和要求1)彩灯能够自动循环点亮2)彩灯循环显示且频率快慢可调(可选)。

3)该控制电路具有8路以上输出在软件工具平台上,进行VHDL语言的各模块编程输入、编译实现和仿真验证。

三、实验主要仪器设备和材料计算机四、实验方法、步骤及结构测试1.方案设计与功能描述彩灯的循环是通过clk的计数实现的,当有一个高电平来到的时候,则通过Q=Q+1计数来实现。

当Q的值从“000”逐次加“1”到“111”的时候,通过判断Q的值是否为“111”的时候,进行清“0”,即变为“000”再次重新计数。

那么通过Q的状态值从“000”->“001”->“010” ->“011”->“100” ->“101”->“110” ->“111”->“000”的循环,实现了彩灯的循环。

彩灯的亮灭是通过判断Q的值来选择的,用case_when语句。

对于频率的调节,则是通过timer来控制,由人为的设定timer 的值,通过赋不同的初值来改变频率。

也是通过计数来分频的2.程序代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity light8a isport (clk,en,rst:in std_logic;timer:in std_logic_vector(3 downto 0);a,b,c,d,e,f,g,h:out std_logic);end light8a;architecture one of light8a issignal w:std_logic_vector(3 downto 0);signal couts:std_logic;beginprocess(clk,timer) ----------分频进程variable x : std_logic_vector(3 downto 0):=timer; beginif clk'event and clk='1' thenif x<4 then x:=x+1;else x:=timer;end if;end if;if x="0100" then couts<='1';else couts<='0';end if;end process;process(clk,en,rst,couts) ----------计数循环进程variable Q : std_logic_vector(3 downto 0);beginif rst='0'then Q:=(others=>'0');elsif clk'event and clk='1' thenif couts='1' thenif en='1' thenif Q<8 thenQ:=Q+1;w<=Q;if Q="1000" then Q:=(others=>'0'); -end if;end if;end if;end if;end if;end process;process(w) --------选择灯亮灭,即控制彩灯循环进程begincase w iswhen"0001"=>a<='1';b<='0';c<='0';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0010"=>a<='0';b<='1';c<='0';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0011"=>a<='0';b<='0';c<='1';d<='0';e<='0';f<='0';g<='0';h<='0'; when"0100"=>a<='0';b<='0';c<='0';d<='1';e<='0';f<='0';g<='0';h<='0'; when"0101"=>a<='0';b<='0';c<='0';d<='0';e<='1';f<='0';g<='0';h<='0'; when"0110"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='1';g<='0';h<='0'; when"0111"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='0';g<='1';h<='0'; when"1000"=>a<='0';b<='0';c<='0';d<='0';e<='0';f<='0';g<='0';h<='1'; when others=>null;end case;end process;end architecture one;4仿真分析当设定timer的值为1的时候,仿真图如下:当设定timer的值为3的时候,仿真图如下:通过仿真可知,timer可以控制频率快慢,且彩灯a,b,c,d,e,f,g,h能循环点亮5总结:通过这次是上机实验,进一步的巩固了我的VHDL的知识,基本掌握了VHDL的编程方法等。

——基于FPGA的VGA显示姓名:王青鹏学号:200661175班级:电子0604日期:200910201.实验目的 (3)2.实验要求 (3)3.实验原理 (3)3.1VGA时序信号 (3)3.2VGA显示时序图 (4)3.3关键参数 (5)3.4VGA显示工作过程 (5)3.5整体设计思路及过程 (6)3.6管脚分配及下载 (15)4.实验心得体会 (16)FPGA的VGA显示一.实验目的1.熟悉和掌握时序控制电路的设计方法。

2.了解VGA显示器的工作时序及其控制电路的工作原理。

3.培养分析系统、进行模块设计及独立解决问题的能力。

二.实验要求1.设计VGA显示器的控制电路,使之控制显示器,完成相应的显示功能。

2.使用一个按钮mod(低有效),使VGA显示器在3种(或4种)不同的显示模式间切换。

使用一个按钮reset,将控制器恢复模式00。

模式00:将屏幕均分,从左到右,依次显示八种不同的颜色。

模式01:将屏幕均分,从上到下,依次显示八种不同的颜色。

模式10:将屏幕均分为8*8棋盘格。

模式11:复位模式,屏幕全黑。

3.利用GW48实验开发系统实现设计的编程下载.三.实验原理3.1VGA时序信号H_SYNC:水平同步信号(负脉冲),每个水平扫描周期显示器刷新V_SYNC:垂直同步信号(负脉冲),每个垂直扫描周期显示器刷新一帧;RGB[2..0]:颜色信号,R——红色信号;G——绿色信号;B——蓝色信号。

其对应颜色关系如下表所示。

3.2VGA显示器的时序图垂直刷新循环3.3关键参数1.实验板上的晶振提供全局时钟信号(50MHz),通过分频得到时钟信号clk25M(fclk=25MHz)作为输入时钟。

2.刷新1个像素所需时间Tpixel=1/fclk=40ns;3.刷新一行所需时间Trow=Tpixel*640+guard bands=25.6us+B +C+E=32.2us;4.一个垂直扫描周期内包含480个水平扫描周期,完成一帧的刷新。

-----------------------------------------------------------------------------------------------------***************************************************************************** ********************-- CreateDate : 2009-03-28-- ModifData : 2009-03-28-- Description : VGA Interface-- Author : Explorer01-- Version : V1.1--***************************************************************************** ********************----------------------------------------------------------------------------------------------------- VHDL library DeclarationsLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------- The Entity DeclarationsENTITY VGA ISPORT(RESET : IN STD_LOGIC;GCLKP1 : IN STD_LOGIC;GCLKP2 : IN STD_LOGIC;--------------------------------------- VGAR : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);G : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);B : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);VS : OUT STD_LOGIC;HS : OUT STD_LOGIC);END VGA;-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------- The Architecture of Entity DeclarationsARCHITECTURE Behavioral OF VGA IS-- SuperVGA timing from NEC monitor manual-- Horizontal :-- ______________ _____________-- | | |-- _______________| VIDEO |_______________| VIDEO (next line) ---- ___________ _____________________ ______________________-- |_| |_|-- B C <------D-----><-E->-- <----------A---------->------ Vertical :-- ______________ _____________-- | | |-- _______________| VIDEO |_______________| VIDEO (next frame) ---- ___________ _____________________ ______________________-- |_| |_|-- P Q <------R-----><-S->-- <----------O---------->---- For VESA 800*600 @ 60Hz:-- Fh (kHz) :37.88-- A (us) :26.4-- B (us) :3.2-- C (us) :2.2-- D (us) :20.0-- E (us) :1.0---- Fv (Hz) :60.32-- O (ms) :16.579-- P (ms) :0.106-- Q (ms) :0.607-- R (ms) :15.84-- S (ms) :0.026------ Horizonal timing information:---- Mode name Pixel sync back active front whole line -- clock pulse porch time porch period -- (MHz) (us) (pix) (pix) (pix) (pix) (pix)---- VGA 800x600 60Hz 40 3.2 128 85 806 37 1056---- Vertical timing information:-- Mode name Lines line sync back active front whole frame-- Total width pulse porch time porch period-- (us) (us)(lin) (us)(lin) (us) (lin) (us)(lin) (us) (lin)---- VGA 800x600 60Hz 628 26.40 106 4 554 21 15945 604 -1* 16579 628--------------------------------------------------CONSTANT H_PIXELS : INTEGER := 640; -- 806CONSTANT H_FRONTPORCH : INTEGER := 16; -- 37CONSTANT H_SYNCTIME : INTEGER := 96; -- 128CONSTANT H_BACKPORCH : INTEGER := 48; -- 85CONSTANT H_SYNCSTART : INTEGER := H_PIXELS + H_FRONTPORCH;CONSTANT H_SYNCEND : INTEGER := H_SYNCSTART + H_SYNCTIME;CONSTANT H_PERIOD : INTEGER := H_SYNCEND + H_BACKPORCH;CONSTANT V_LINES : INTEGER := 480; -- 604CONSTANT V_FRONTPORCH : INTEGER := 11; -- -1CONSTANT V_SYNCTIME : INTEGER := 2; -- 4CONSTANT V_BACKPORCH : INTEGER := 32; -- 21CONSTANT V_SYNCSTART : INTEGER := V_LINES + V_FRONTPORCH;CONSTANT V_SYNCEND : INTEGER := V_SYNCSTART + V_SYNCTIME;CONSTANT V_PERIOD : INTEGER := V_SYNCEND + V_BACKPORCH;------------------------------------------------------------------------------------------------SIGNAL HsyncB : STD_LOGIC;SIGNAL VsyncB : STD_LOGIC;SIGNAL Hcnt : STD_LOGIC_VECTOR(9 DOWNTO 0);SIGNAL Vcnt : STD_LOGIC_VECTOR(9 DOWNTO 0);SIGNAL Enable : STD_LOGIC;SIGNAL TempR : STD_LOGIC;SIGNAL TempG : STD_LOGIC;SIGNAL TempB : STD_LOGIC;SIGNAL ColorR : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL ColorG : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL ColorB : STD_LOGIC_VECTOR(3 DOWNTO 0);--------------------------------------------------Clock:SIGNAL Period1uS, Period1mS: STD_LOGIC;------------------------------------------------SIGNAL Count : STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL CLK, CLKTemp : STD_LOGIC;BEGIN---------------------------------------------------------------------------------------------------- Globle Clock AssignmentGlobleClk:PROCESS( RESET, GCLKP1, GCLKP2, Period1uS, Period1mS ) V ARIABLE Count : STD_LOGIC_VECTOR(5 DOWNTO 0); -- 1MHzV ARIABLE Count1 : STD_LOGIC_VECTOR(9 DOWNTO 0); -- 1KHzV ARIABLE Count2 : STD_LOGIC_VECTOR(9 DOWNTO 0); -- 1Hz BEGIN------------------------------------------------- 25 MHzIF( GCLKP1'EVENT AND GCLKP1='1' ) THEN CLK <= NOT CLK;END IF;-------------------------------------------------GCLKP : 50MHz--Period: 1uS (Period1uS <= GCLKP1; )IF( RESET = '0' ) THENCount := (OTHERS=>'0');ELSIF( GCLKP2'EVENT AND GCLKP2='1' ) THENIF( Count>"110000" ) THEN Count := (OTHERS=>'0'); -- 1uSELSE Count := Count + 1;END IF;END IF;Period1uS <= Count(5);-------------------------------------------------Period: 1mSIF( RESET = '0' ) THENCount1 := (OTHERS=>'0');ELSIF( Period1uS'EVENT AND Period1uS='1' ) THENIF( Count1>"1111100110" ) THEN Count1 := (OTHERS=>'0'); -- 1uSELSE Count1 := Count1 + 1;END IF;END IF;Period1mS <= Count1(9);-------------------------------------------------Period: 1SIF( RESET = '0' ) THENCount2 := (OTHERS=>'0');ELSIF( Period1mS'EVENT AND Period1mS='1' ) THENIF( Count2>"1111100110" ) THEN Count2 := (OTHERS=>'0'); -- 1uSELSE Count2 := Count2 + 1;END IF;END IF;-- 2 HzCLKTemp <= Count2(8);END PROCESS;--================================================================= ===============================-- VGA Clock process---------------------------------------------------------------------------------------------------- Horizontal counterPROCESS( RESET, CLK )BEGINIF( RESET='0' ) THEN Hcnt <= (OTHERS=>'0');ELSIF( CLK'EVENT AND CLK='1' ) THENIF( Hcnt<H_PERIOD ) THEN Hcnt <= Hcnt + 1;ELSE Hcnt <= (OTHERS=>'0');END IF;END IF;END PROCESS;-------------------------------------------------- Vertical counterPROCESS( RESET, HsyncB )BEGINIF( RESET='0' ) THEN Vcnt <= (OTHERS=>'0');ELSIF( HsyncB'EVENT AND HsyncB='1' ) THENIF( Vcnt<V_PERIOD ) THEN Vcnt <= Vcnt + 1;ELSE Vcnt <= (OTHERS=>'0');END IF;END IF;END PROCESS;-------------------------------------------------------------------------------------------------- Horizontal SyncPROCESS( RESET, CLK )BEGINIF( RESET='0' ) THEN HsyncB <= '1';ELSIF( CLK'EVENT AND CLK='1' ) THENIF( Hcnt>=(H_PIXELS + H_FRONTPORCH) AND Hcnt<(H_PIXELS + H_FRONTPORCH + H_SYNCTIME) ) THENHsyncB <= '0';ELSEHsyncB <= '1';END IF;END IF;END PROCESS;-------------------------------------------------- Vertical SyncPROCESS( RESET, HsyncB )BEGINIF( RESET='0' ) THEN VsyncB <= '1';ELSIF( HsyncB'EVENT AND HsyncB='1' ) THENIF( Vcnt>=(V_LINES + V_FRONTPORCH) AND Vcnt<(V_LINES + V_FRONTPORCH + V_SYNCTIME) ) THENVsyncB <= '0';ELSEVsyncB <= '1';END IF;END IF;END PROCESS;HS <= HsyncB;VS <= VsyncB;--==============================================--------------------------------------------------PROCESS( RESET, CLK, Hcnt, Vcnt )BEGINIF( CLK'EVENT AND CLK='1' ) THENIF ( RESET='0' ) THEN Enable <= '0';ELSIF( Hcnt>=H_PIXELS OR Vcnt>=V_LINES ) THEN Enable <= '0';ELSE Enable <= '1';END IF;END IF;END PROCESS;--------------------------------------------------PROCESS( RESET, CLKTemp, Hcnt, Vcnt, Enable, TempR, TempG, TempB, Count ) -- V ARIABLE Count : STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINIF ( RESET='0' ) THEN Count <= "000";ELSIF( CLKTemp'EVENT AND CLKTemp='1' ) THEN Count <= Count + 1;END IF;------------------------------------------------CASE Hcnt(7 DOWNTO 5) ISWHEN "000" => TempR <= '1'; TempG <= '1'; TempB <= '1';WHEN "001" => TempR <= '0'; TempG <= '0'; TempB <= '0';WHEN "010" => TempR <= '1'; TempG <= '0'; TempB <= '0';WHEN "011" => TempR <= '0'; TempG <= '0'; TempB <= '1';WHEN "100" => TempR <= '0'; TempG <= '1'; TempB <= '0';WHEN "101" => TempR <= '1'; TempG <= '0'; TempB <= '1';WHEN "110" => TempR <= '1'; TempG <= '1'; TempB <= '0';WHEN "111" => TempR <= '1'; TempG <= '1'; TempB <= '1';WHEN OTHERS=> TempR <= '0'; TempG <= '0'; TempB <= '0';END CASE;IF( Enable='1' ) THENIF( TempR='1' ) THEN R <= Count & '1';ELSE R <= (OTHERS=>'0');END IF;IF( TempG='1' ) THEN G <= '1' & Count;ELSE G <= (OTHERS=>'0');END IF;IF( TempB='1' ) THEN B <= '1' & Count(0) & Count(1) & Count(2);ELSE B <= (OTHERS=>'0');END IF;ELSER <= (OTHERS=>'0');G <= (OTHERS=>'0');B <= (OTHERS=>'0');END IF;END PROCESS;--------------------------------------------------------------------------------------------------END Behavioral;。