共源共栅放大器实验报告材料

- 格式:doc

- 大小:2.71 MB

- 文档页数:13

6折叠式共源共栅运算放大器设计实验之欧阳法创编欧阳法是一种常用的运算放大器设计方法,它在设计中充分利用了共源共栅结构的优点,既能实现放大器的高增益、高输入阻抗和低输出阻抗,又能保证输出波形的线性度。

在设计6折叠式共源共栅运算放大器之前,首先需要明确一些设计参数,例如设计的输入电压范围、输出电压范围、增益要求等。

接下来,我们按照以下步骤进行设计实验。

第一步:确定输出电流偏置在共源共栅运算放大器中,偏置电流决定了放大器的输入阻抗和输出电压范围。

为了实现输出电压范围的最大化,一般选择输出电流的一半作为偏置电流。

假设输出电流为Iout,则偏置电流为Ibias=0.5*Iout。

第二步:确定放大器的增益根据设计要求确定放大器所需的增益。

对于共源共栅结构,其放大倍数可以通过控制输入电流和输出电流之间的比值来实现。

输出电流为Iout,输入电流为Iin,则放大倍数Av=Iout/Iin。

第三步:确定放大器的工作电压根据设计要求确定放大器的工作电压。

将放大器的工作电压设为VDD/2,这样可以最大程度地利用电源电压范围。

第四步:确定电阻值根据欧阳法的设计准则,可选择如下电阻值:R1=R2=RL=1.2*VDD/(Ibias*Av)R3=R4=2*RL第五步:确定电容值选择合适的电容值可以提高放大器的频率响应。

一般选择的电容值为:Cgs=Cgd=2*Iout/(Av*VDD*fL)Cdb=Cgd/5其中,fL为放大器的最低截止频率。

第六步:确定晶体管尺寸根据电阻和电容的选择,可以反推出晶体管的尺寸。

根据晶体管的工作点,选择适当的W/L比值来满足电流需求。

完成以上步骤后,可以利用电路设计软件进行模拟仿真,并根据仿真结果进行优化调整。

最后,可以进行实验验证,并对实验结果进行分析。

以上是关于6折叠式共源共栅运算放大器设计实验的欧阳法创编的详细步骤。

在实际设计中,还需要注意噪声和功耗等因素,并进行合理的折衷考虑。

希望以上内容能对你的实验展开有所帮助。

共源共栅放大器的分析1.基本结构和工作原理当输入信号施加在共源共栅放大器的输入端(栅极)时,栅极结电容Cgs会对输入信号起到隔离作用。

通过共源共栅放大器的源极电压调整,可以改变输出电压的增益和相位。

工作原理:当输入信号施加在栅极上时,栅极电阻Rg将输入电流转换为输入电压,并施加到栅极上。

当栅极电压超过阈值电压,漏极电流开始流动。

漏极电流经过源极电阻Rs,形成输出电压。

由于栅极和源极之间存在电容Cgs,所以输出电压的幅频特性非常好,可以达到高频的放大。

2.放大性能分析(1)集大于放大倍数:共源共栅放大器的电压放大倍数由源极电阻Rs决定,与负载电阻RL共同决定。

较小的Rs和RL能够提高放大倍数。

(2) 输入阻抗:共源共栅放大器的输入阻抗由输入电阻Rg和栅极结电容Cgs共同决定。

较大的Rg和较小的Cgs能够提高输入阻抗。

(3)输出阻抗:共源共栅放大器的输出阻抗由源极电阻Rs和漏极电阻Rd共同决定。

较小的Rs和Rd能够提高输出阻抗。

(4)漏极电流偏置:通过控制栅极电压和源极电阻,可以调整共源共栅放大器的偏置电压和偏置电流。

适当选择偏置电流可以减小失调,提高放大器的线性度。

(5) 高频特性:由于栅极和源极之间存在电容Cgs,共源共栅放大器在高频范围有较好的性能,能够实现高频信号的放大。

3.稳定性分析4.应用领域总结:共源共栅放大器是一种常见的放大电路,其工作原理基于MOSFET。

通过调整偏置电流、增加负反馈等手段,可以改善共源共栅放大器的性能。

共源共栅放大器在应用中具有广泛的用途,是电子设备中不可或缺的一部分。

MOS放大电路设计仿真与实现实验报告实验报告:MOS放大电路设计、仿真与实现一、实验目的本实验的主要目的是通过设计、仿真和实现MOS放大电路来加深对MOSFET的理解,并熟悉模拟电路的设计过程。

二、实验原理MOSFET是一种主要由金属氧化物半导体场效应管构成的电流驱动元件。

与BJT相比,MOSFET具有输入阻抗高、功率损耗小、耐电压高、尺寸小等优点。

在MOS放大电路中,可以采用共源共源极放大电路、共栅共栅极放大电路等不同的电路结构。

三、实验步骤1.根据实验要求选择合适的电路结构,并计算所需材料参数(参考已知电流源和负载阻抗)。

2.选择合适的MOS管,并仿真验证其工作参数。

3.根据仿真结果确定电路的放大倍数、频率响应等。

4.根据电路需求,设计电流源电路和源极/栅极电路。

5.仿真整个电路的性能,并调整参数以优化电路性能。

6.根据仿真结果确定电路的工作参数,并进行电路的实现。

7.通过实验测量电路性能,验证仿真结果的正确性。

8.对实验结果进行分析,总结实验的过程和经验。

四、实验设备和材料1.计算机及电子仿真软件。

2.实验电路板。

3.集成电路元器件(MOSFET、电阻等)。

4.信号发生器。

5.示波器。

6.万用表等实验设备。

五、实验结果与分析通过仿真和实验,可以得到MOS放大电路的电压增益、输入输出阻抗、频率响应等参数。

根据实验结果,可以验证设计的合理性,并进行参数调整优化。

在实际应用中,MOS放大电路被广泛应用于音频放大器、功率放大器、运算放大器等场合。

因为MOSFET具有较大输入阻抗,所以MOS放大电路可以在输入端直接连接信号源,而不需要额外的输入电阻。

此外,MOS放大电路的功率损耗较小,适用于各种功率要求不同的应用场合。

六、实验心得通过设计、仿真和实现MOS放大电路的实验,我更加深入地理解了MOSFET的原理和应用。

在实验过程中,我通过不断调整电路参数和元器件选择,逐步提高了电路的性能。

通过与实验结果的对比,我发现仿真和实验结果基本吻合,验证了仿真的准确性。

共源共栅运算放大器的设计共源共栅运算放大器,也称为共源共栅放大器或共栅源跟随器,是常用的运算放大器电路结构。

它由共源放大器和共栅放大器组成,可以提供高增益、宽带宽并具有高输入电阻和低输出阻抗的特点。

下面将详细讨论共源共栅运算放大器的设计。

设计目标:1.高增益:希望放大器具有高增益,以提供较大的放大倍数。

2.宽带宽:希望放大器具有较宽的频带,以传输更高频率的信号。

3.高输入电阻:希望放大器具有较高的输入电阻,以不对被测电路产生影响。

4.低输出阻抗:希望放大器具有较低的输出阻抗,以不对后级电路产生影响。

设计步骤:1.选择晶体管:选择性能良好、参数稳定的晶体管作为放大器的关键部件。

常用的晶体管有MOSFET和JFET,选用适合的型号,使其性能满足设计的要求。

2.偏置电路设计:根据晶体管的工作条件,设计偏置电路以保证放大器的工作稳定性。

通常采用电流源和电阻网络来实现晶体管的偏置。

3.增益极化设计:确定放大器的增益级数和增益大小,并选择适当的分压比例和电阻值,使得输出电压能够满足要求。

同时考虑增益的稳定性,防止输出波形失真。

4.频率补偿设计:由于共源共栅放大器的频率响应受到极点和零点的影响,需要设计频率补偿电路来提高带宽。

常用的频率补偿方法有米勒补偿电容和并联补偿电容等。

5.输入和输出阻抗设计:通过选择合适的电路参数和组件数值,使得输入电阻和输出电阻达到所需的要求。

一般采用反馈电阻网络来实现输入和输出阻抗的调节。

6.功耗和温度设计:考虑到功耗和温度对放大器性能的影响,需要进行功耗和热量分析,并选择适当的散热器来保证放大器的长期稳定工作。

7.电源设计:根据放大器的电源需求,选择适当的电源电压和电源过滤电路,以保证放大器的工作正常和稳定性。

以上是共源共栅运算放大器的设计步骤。

在设计过程中,需要综合考虑各种因素,并根据具体的应用场景和要求进行优化。

通过合理的设计和调试,可以获得性能良好的共源共栅运算放大器。

共源共栅放大器电路增益90db的文章在现代电子技术领域中,放大器被广泛应用于信号处理、音频放大、通信等许多领域。

其中,共源共栅放大器在各种放大器电路中具有独特的特点,被广泛应用于各种领域。

在本文中,我将针对共源共栅放大器电路的概念、原理、特点,以及增益90db的情况下进行全面的评估,并撰写一篇有价值的文章。

1. 共源共栅放大器电路的概念共源共栅放大器是一种常见的场效应管放大器电路,通常由一个MOS 场效应管组成。

在这种电路中,输入信号通过栅极加到场效应管的栅极,输出信号则从源极获取。

栅极也通过RC耦合电路与源极相连,形成共源共栅的电路结构。

这种电路的特点是具有高输入阻抗和低输出阻抗。

2. 共源共栅放大器电路的原理共源共栅放大器电路通过栅极的输入信号来控制场效应管的导通,进而在源极获得放大后的输出信号。

栅极与源极之间的耦合电路可以提供恰当的电压偏置,使得场效应管在工作点上能够正常放大输入信号。

由于栅极和源极之间是共源共栅的结构,这种放大器电路具有较高的增益和较低的失真。

3. 共源共栅放大器电路的特点共源共栅放大器电路具有许多特点,包括高输入阻抗、低输出阻抗、较高的增益、良好的线性度和较小的失真。

这些特点使得共源共栅放大器电路在各种领域,尤其是需要高质量音频放大和精密信号处理的应用中得到广泛的应用。

4. 共源共栅放大器电路增益90db的评估在具体应用中,共源共栅放大器电路的增益可以根据具体的电路设计和参数选择进行调整。

如果需要实现高增益的放大器电路,可以通过精心设计和合理选择电路元件来实现。

一些需要大幅度放大的音频放大器或者精密仪器放大器,就需要较高的增益。

在这种情况下,我们可以根据具体需求,调整放大器电路的设计参数,以达到增益90db的要求。

5. 个人观点和理解在我看来,共源共栅放大器电路是一种非常有价值的放大器电路,它不仅具有较高的增益和良好的线性度,而且还具有稳定的工作特性和较小的失真。

这使得它在各种高要求的放大应用中都能发挥重要作用。

mos管共源、共漏、共栅三种组态放大电路下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!共源、共漏、共栅三种组态放大电路是常见的MOS管放大电路配置,它们在集成电路设计中起到非常重要的作用。

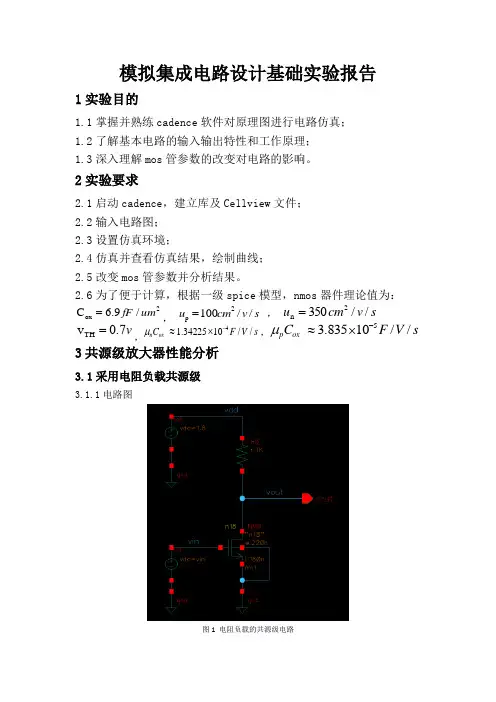

模拟集成电路设计基础实验报告1实验目的1.1掌握并熟练cadence 软件对原理图进行电路仿真;1.2了解基本电路的输入输出特性和工作原理;1.3深入理解mos 管参数的改变对电路的影响。

2实验要求2.1启动cadence ,建立库及Cellview 文件;2.2输入电路图;2.3设置仿真环境;2.4仿真并查看仿真结果,绘制曲线;2.5改变mos 管参数并分析结果。

2.6为了便于计算,根据一级spice 模型,nmos 器件理论值为:2ox /9.6C um fF =, s v cm u //1002p = , s v cm u //3502n =v 7.0v TH =,41.3422510//n ox C F V s μ-≈⨯,53.83510//p ox C F V s μ-≈⨯ 3共源级放大器性能分析3.1采用电阻负载共源级3.1.1电路图图1 电阻负载的共源级电路2))(/()2/1(v out in ox n dd out v v l w C Ru v --=(忽略沟道长度调制效应)(1)直流分析dd V =1.8V,in V 参数扫描范围0-2V ,R=5k Ω,nmos 宽长比3.6u/180n=20.图2 直流仿真结果MOS 管工作在饱和区时:2))(/()2/1(V TH in ox n dd out V V l w C Ru V --=.MOS 管工作在线性区时:)V 2)(/()2/1(V 2out V V V l w C Ru V TH in ox n dd out ---=)(图3 g m 图在饱和区))(/(g m TH gs ox n V V l w C u -=,当in V >TH V 时,跨导开始增大;在线性区DS ox n V l w C u )/(g m =,当in V >m ax V 时,m g 将会下降.m ax V -TH V =2))(/()2/1(V TH in ox n dd out V V l w C Ru V --=这个仿真结果表示,当in V =0.72V 时跨导最大。

一、实验目的1. 理解共源极放大电路的工作原理和基本组成。

2. 掌握共源极放大电路静态工作点的设置方法。

3. 学习共源极放大电路的动态性能分析,包括电压放大倍数、输入阻抗、输出阻抗等。

4. 通过实验验证理论分析的正确性。

二、实验原理共源极放大电路是场效应管放大电路的一种基本形式,其工作原理基于场效应管栅源电压(VGS)对漏源电流(ID)的控制。

在共源极放大电路中,信号从源极输入,经过放大后从漏极输出。

三、实验仪器与设备1. 数字万用表2. 函数信号发生器3. 示波器4. 源极跟随器5. 晶体管6. 电位器7. 电阻8. 电容四、实验步骤1. 搭建共源极放大电路根据实验电路图,将晶体管、电阻、电容等元件按照要求连接成共源极放大电路。

2. 设置静态工作点通过调整源极电阻和漏极电阻,使晶体管工作在放大区。

使用数字万用表测量晶体管的漏源电压(VDS)和栅源电压(VGS),确保静态工作点符合设计要求。

3. 测量输入阻抗将函数信号发生器输出信号连接到共源极放大电路的源极,使用示波器测量输入端电压和电流。

根据输入电阻的定义,计算输入阻抗。

4. 测量输出阻抗在共源极放大电路的漏极接上负载电阻,使用示波器测量输出端电压和电流。

根据输出电阻的定义,计算输出阻抗。

5. 测量电压放大倍数在共源极放大电路的源极输入正弦波信号,调整信号幅度,使输出信号不失真。

使用示波器测量输入端和输出端的电压峰值,根据电压放大倍数的定义,计算电压放大倍数。

6. 测量频率响应改变输入信号的频率,观察输出信号的幅度变化。

绘制幅频特性曲线,分析共源极放大电路的频率响应。

五、实验结果与分析1. 静态工作点实验测得的静态工作点VDS和VGS与设计要求基本一致,说明共源极放大电路的静态工作点设置正确。

2. 输入阻抗实验测得的输入阻抗与理论计算值基本一致,说明共源极放大电路的输入阻抗符合设计要求。

3. 输出阻抗实验测得的输出阻抗与理论计算值基本一致,说明共源极放大电路的输出阻抗符合设计要求。

共源共栅放大器姓名:郭佛威学号:2140320071共源共栅放大器源共栅放大器又称为级联放大器,是共源极和共栅极的级联。

由于共源放大级把电压信号转换为电流信号,而共栅放大级的输入信号为电流信号,故可把共源与共栅放大电路级联起来构成了共源共栅放大器,如右图所示。

M1产生正比于V in的小信号漏电流而M2电流流过R D,M1为输入器件,M2为级联器件,且M1与M2具有相同的电流。

偏置条件:M1和M2均工作在饱和区即V b≥ V in + V GS2 -V TH1;V out≥ V in-V TH1+V GS2-V TH21.共源共栅——大信号特性分析:输入—输出特性曲线1.1大信号特性:V in≤V TH1,M1,M2处于截止状态,V out=V DD,且V X≈ V b -V TH2 (忽略亚阈值导通);当Vin≥V TH1,M1产生电流,V out则降低,V GS2上升而V X下降。

V in>V TH1,开始出现电流,V out下降,V X下降,到一定值时M1或M2 进入线性区,增益(V out曲线的斜率)减小。

1.2输出摆幅:M1工作在饱和区:V A=V b-V GS2≥V ov1=V in-V t1V b≥V in+V GS2-V t1M2工作在饱和区:V out≥V b-V t2≥V in+V GS2-V t1-V t2=V ov1+V ov2为了使M4工作在饱和区:V out<V DD-|V GS4-V TH4|所以输出摆幅为:V on1+V on2<V out<V DD-|V GS4-V TH4|2.共源共栅级______小信号特性2.1增益:当两个晶体管工作在饱和区时;假设两个管子的λ均等于0,由于输入管产生的漏电流必定流过整个共源共栅级电路,所以A V=V out/V in=-g m1V1R D/V in,而V1= V in,所以A V=-g m1R D。

当忽略沟道长度调制效应时,共源共栅级放大器的电压增益与共源级放大器的电压增益相同。

折叠式共源共栅运算放大器设计实验一、设计步骤1.确定规格和目标:首先确定设计的规格和目标,例如增益、带宽、输入输出电阻等。

2.选择适当的工作点:根据目标确定合适的工作点。

通常,选择中间状态的电流偏置,例如源极电流和漏极电流各占目标电流的一半。

3.估计W/L比例:根据工作点电流和所用晶体管的尺寸参数,估计晶体管的W/L比例。

可以使用厂商提供的模型参数进行计算。

4.电流源设计:设计适当的电流源,用于提供偏置电流。

电流源可以采用单端(如PMOS、NMOS)或差分结构(如源随器)。

5.阶数计算:根据需求和规格,计算需要的放大器阶数。

6.确定并绘制电路拓扑:根据放大器的阶数,选择合适的电路拓扑。

折叠式共源共栅运放通常由两个共源共栅级联组成。

绘制电路图,包括晶体管、电容、电流源等。

7.进行直流偏置分析:进行直流偏置分析,计算电压、电流等参数。

确保电路能够在合适的工作点工作,并且各个极点和零点在期望的频率范围内。

8.进行交流分析:进行交流分析,计算增益、带宽等参数。

可以使用电路仿真软件进行模拟分析,找到需要优化的部分。

9.优化设计:根据仿真结果,逐步调整电路参数,优化设计。

可以通过改变晶体管的W/L比例、电容的数值等参数,使得仿真结果符合要求。

10.布局设计:进行电路的布局设计,包括电源、接地、电容、晶体管等部分的布局。

注意避开毫米波的射频干扰源,并且尽量减少板间互电容等干扰。

11.进行仿真验证:进行全局电路的仿真验证,确保电路能够满足设计要求。

12.绘制电路原理图和PCB板:根据最终的设计结果,绘制电路原理图和PCB板,进行制作。

二、实验过程1.制作PCB板:根据设计的PCB布局图,制作PCB板。

2.感知电路:将制作好的PCB板安装到实验台上,连接电源和信号源。

3.测量电路参数:使用万用表、示波器等仪器,测量电路参数,例如增益、带宽、输入输出电阻等。

4.分析结果:根据测量结果,分析电路的性能是否满足设计要求。

CMOS课程设计折叠式共源共栅运算放大器设计学院: 机械与电子工程学院专业: 电子科学与技术指导老师: 蔡志民班级: 1221401学号: 201220140125姓名: 姜国理报告时间: 2015-07-05一、设计目的设计共源共栅运算放大器,使其满足V DD=5V,功率P=10mW,输出摆幅为2.35V,增益A V约10dB。

使用st02 0.5um 5V CMOS工艺5V晶体管模型。

学习差动放大器DC扫描、AC、瞬态分析的方法。

参数给定:C OX=(εsiεo)/t ox其中εsi=8.85*10-12,εo=3.9,t ox =9nm;u n=350cm2/v/s,u p=100 cm2/v/s。

二、设计步骤本次实验采用IC615设计整个过程。

启动cadence工具,在terminal中输入virtuoso &启动IC615并后台运行,如图所示:启动后CIW窗口如图所示:启动IC615后,新建library取名201220140125,并关联到st02库,如图所示:在library中新建cell,选择schematic原理图输入,并调用st02器件mn及mp,分别修改参数,最后原理图如图所示:参数的设定:1)电流分配:根据10mw的功率,及电源电压5v,由公式p=ui,算出I总=2mA,由电路对称性平均分配电流M0,M1为1mA,M9流过M8,及M10的电流之和也为1mA,其他的管子电流都为0.5mA。

2)过驱动电压分配:电流确定后,根据摆幅2.35v分配过驱动电压,M0,M1的V on=0.45v,M2,3的V on=0.8v,M4,5,8,10的V on=0.8v,M6,7的V on=0.6v,M9的V on=1v。

3)宽长比确定:通过电流与过驱动电压的关系式确定宽长比,由于所有mos管都必须工作在饱和区,所以使用饱和区的电流-过驱动电压的关系:Nmos管:I DS=1/2u n C OX(W/L)(V GS-V th)2=1/2u n C OX V OD2=>(W/L)=(2 I DS) /( u n C OX V OD2)Pmos管:I DS=1/2u p C OX(W/L)(V GS-V th)2=1/2u p C OX V OD2=>(W/L)= (2 I DS)/(u p C OX V OD2)根据公式可得所有mos管的宽长比,分别为:(w/l)0,1=149.25/0.55, (w/l)2,3=22.62/0.55, (w/l)4,5,8,10=5.87/0.5,(w/l)6,7=10.44/0.5, (w/l)9=7.5/0.54)分配初始偏置电压值:mos管阈值电压的初始值由工艺库中给定,pmos管的阈值电压为V th=-0.8V,nmos管的阈值电压为V th=0.7V,这些值将在仿真过程中修正。

6折叠式共源共栅运算放大器设计实验汇总折叠式共源共栅运算放大器是一种常用的电路结构,常用于设计高增益、低功耗的放大器电路。

本文将对这种电路进行实验设计和汇总,总结电路设计过程中的关键问题和解决方法。

首先,我们需要确定设计的目标。

折叠式共源共栅运算放大器的主要性能指标包括增益、带宽、输入电阻、输出电阻、功耗等。

在设计之前,我们要先确定这些性能指标的要求,以便在设计中进行优化。

接下来,我们需要确定电路的工作点。

工作点决定了电路的偏置电流和电压,对放大器的性能起着重要作用。

在折叠式共源共栅运算放大器中,我们可以通过调整源极电流和栅极电压来实现合适的工作点。

一般情况下,我们希望工作点在电压-电流特性曲线的中间位置,以便有足够的线性放大范围。

然后,我们需要选择合适的晶体管。

在折叠式共源共栅运算放大器中,常常选择NMOS晶体管作为放大器管,因为NMOS晶体管具有较好的线性特性和较高的增益。

根据工作点的要求,我们可以在晶体管的数据手册中找到合适的晶体管型号。

接下来,我们需要确定电路的输入阻抗。

由于折叠式共源共栅运算放大器的输入是通过共源极实现的,所以输入阻抗受到源极电流的影响。

为了实现较高的输入阻抗,我们可以选择较大的源极电流。

此外,还可以通过并联电容以降低输入阻抗。

然后,我们需要确定电路的增益和带宽。

增益和带宽是折叠式共源共栅运算放大器的两个主要指标。

增益可以通过选择合适的电阻和电容来调整,通常可以通过负反馈来实现。

带宽则受到晶体管的频率特性限制,可以通过合适的电容和电感来进行补偿。

最后,我们需要进行电路的仿真和测试。

通过电路仿真软件,我们可以验证电路的性能指标是否满足设计要求,并进行一些优化调整。

在测试中,我们可以使用示波器、函数发生器等仪器测量电路的增益、带宽和失调等指标。

综上所述,折叠式共源共栅运算放大器设计的关键问题包括确定设计目标、确定电路的工作点、选择合适的晶体管、确定电路的输入阻抗、确定电路的增益和带宽,以及进行电路的仿真和测试。

实验名称:共源共栅放大器设计

实验目的:

1.了解共源共栅级放大器的基本工作原理及相关优缺点

2.学会CMOS电路中的基本参数的设计和分析参数之间的折中关系

3. 共源共栅放大器设计及仿真

实验设备及型号:orcd仿真软件

实验原理及实验步骤:

实验原理:

共栅级的输入信号可以是电流,共源级可以可以将电压信号转换为电流信号。

共源共栅级的级联叫做共源共栅结构。

共源共栅级的输出阻抗很高

通过计算Rout可得Rout约=(gm1+gmb2)r o2r o1

也就是说M2将M1的增益提高至原来的(gm1+gmb2)r o2倍

其还可以扩展为三个或多个以获得更高的输出电阻

但这需要额外的电压余度

共源共栅结构不仅可以作为放大器而且可以作为恒定电流源高的输出阻抗接近一个理想电流源

本次需要仿真的pmos 共源共栅负载的nmos 共源共栅放大器即是如此。

在某种意义上,共源共栅晶体管结构“屏蔽”输入器件使它不受输出节点电压变化的影响。

这种共源共栅结构屏蔽特性在许多电路中是非常有用的 实验步骤:

由于共源共栅放大器的电路图已给出,所以电路设计省略 2.按所给设计图绘制相应电路图所得电路图如下

0.65FREQ = 1k

VAMP VOFF = 0

3.根据题目要求先对其进行相应仿真 1)设置静态工作点和器件参数。

如此处静态输出电压Vout=3v Vcc=6v Vb1=5.13v Vb2=4.88v Vb3= 0.904v 等

2):设定静态电流。

①设定长L=2u

②调试W

L

主要是调试W,要使静态电流为100uA,L固定以后,就调节W来达到需要的电流。

此处用快速扫描的方法来调试出所需W的大小

待所需各个管的w值扫描出后

③bias point 仿真检验电流i是否达到要求。

3)根据题目要求进行相应的交流仿真。

以下是相关的扫描实验数据

扫描w的值

测得MN1 管w的值为104.5u

测得MN2 管w的值为92.7u

注:此时测得的MN2管w的值是加了一个稳定电压Va=0.25v的

当没加Va时测得MN2 管w的值为90.1u

测得MP2 管w的值为179.5u

测得MP1管w的值为205u

bias point 仿真检验。

去掉输出端的3v电压后原则上在每个管子的W定好了之后通过bias point仿真静态输出电压为3V静态电流约为100uA。

交流仿真

因要求Ad>=70DB故将电压调至0.6535v

此时的电路图为

0P ARAM E T ER S:

w = 10u

0vb 1

VDB

MN1

W = 104.5u L = 2u

R12k

2

1

0MP2

W = 179.5u L = 2u

V4

4.88Vdc

vb 3

V7

3V dc

V5

0.904Vdc

vb 3

vb 2

V3

5.13Vdc

vb 1

V6

6V dc

vcc

MN2

W = 92.7u L = 2u

vo ut

vcc

V2

0.6535Vd c vb 2

V1FREQ = 1k

VAMP L = 15m VOFF = 0AC = 1

MP1

W = 205u

L = 2u

得到F3db=494.613khz

当w1变从205u变为204u时

F3db=414.795khz

当w1变从205u变为206u时

Ad 变为63.519 F3db=1.1508mhz

当w2变从179.5u变为178.5u时

F3db=473.324khz

当w2变从179.5u变为180.5u时

Ad 变为72.887 F3db=516.865khz

当w3变从92.7u变为91.7u时F3db=532.248khz

当w3变从92.7u变为93.7u时F3db=459.642khz

改变R时

当R=1K F3db=494.615khz

当R=3K F3db=487.413khz

当加上电容时 对应电路图为

MP2

W = 179.5u L = 2u

0VDB

P ARAM E T ER S:

w = 10u

MN1

W = 104.5u L = 2u

0MP1

W = 205u L = 2u

0V2

0.6535Vd c vb 2

0V6

6V dc

V1FREQ = 1k

VAMP L = 15m VOFF = 0AC = 1

vb 3

MN2

W = 92.7u L = 2u

V5

0.904Vdc

vb 1

V3

5.13Vdc

vcc

vo ut

vb 3

R12k

2

1

vb 1

V4

4.88Vdc

vb 2

C110p

当加上电容C=5p 时F3db=7.7798khz

当加上电容C=10p时F3db=4.0037khz。