数字逻辑习题案例

- 格式:pdf

- 大小:586.20 KB

- 文档页数:20

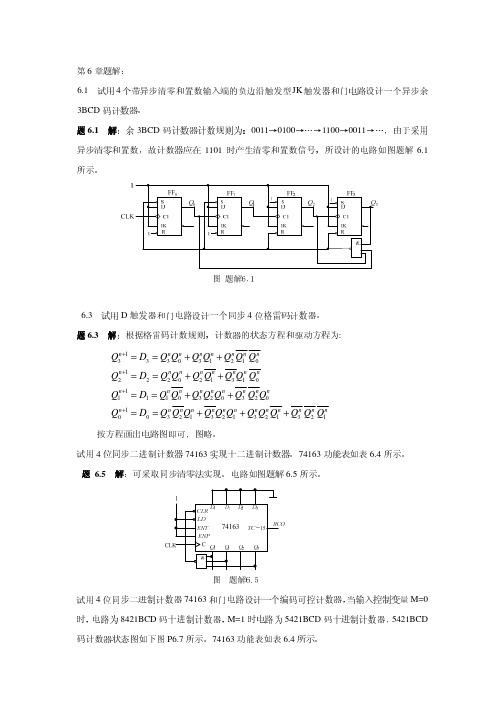

第6章题解:6.1 试用4个带异步清零和置数输入端的负边沿触发型JK触发器和门电路设计一个异步余3BCD码计数器。

题6.1 解:余3BCD码计数器计数规则为:0011→0100→…→1100→0011→…,由于采用异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1所示。

试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变量M=0时,电路为8421BCD码十进制计数器,M=1时电路为5421BCD码十进制计数器,5421BCD 码计数器状态图如下图P6.7所示。

74163功能表如表6.4所示。

试用同步十进制计数器74160和必要的门电路设计一个365进制计数器。

要求 各位之间为十进制关系。

74160功能表如表6.6所示。

题6.9 解:用3片74160构成3位十进制计数器,通过反馈置数法,完成365进制计数器设计。

电路如图题解6.9所示。

B ,C ,D ,E ,F ,G ,H ,I 分别为低电平时,Y 端输出的脉冲频率各为多少。

优先编码器74147功能表如表4.4所示,74160功能表如表6.6所示。

CLK Y I 图 P6.11 题6.11解: 当0A =时,74160构成模9计数器,Y 端输出频率为109KHz ;当0B =时,74160构成模8计数器,Y 端输出频率为108KHz ;当0C =时,74160构成模7计数器,Y 端输出频率为107KHz ;当0D =时,74160构成模6计数器,Y 端输出频率为106KHz ;当0E =时,74160构成模5计数器,Y 端输出频率为105KHz ;当0F =时,74160构成模4计数器,Y 端输出频率为104KHz ; 当0G =时,74160构成模3计数器,Y 端输出频率为103KHz ;当0H =时,74160构成模2计数器,Y 端输出频率为102KHz ;当0I =时,74160循环置9,Y 端输出频率为0Hz ;6.13 试用D 触发器、与非门和一个2线—4线译码器设计一个4位多功能移位寄存器,移位寄存器的功能表如图P6.13所示。

For personal use only in study and research; not for commercialuse《数字逻辑》习题案例(计算机科学与技术专业、信息安全专业)2004年7月计算机与信息学院、计算机系统结构教研室一、选择题1.十进制数33的余3码为 。

A. 00110110B. 110110C. 01100110D. 1001002.二进制小数-0.0110的补码表示为 。

A .0.1010B .1.1001C .1.0110D .1.10103.两输入与非门输出为0时,输入应满足 。

A .两个同时为1B .两个同时为0C .两个互为相反D .两个中至少有一个为04.某4变量卡诺图中有9个“0”方格7个“1”方格,则相应的标准与或表达式中共有多少个与项 ?A . 9B .7C .16D .不能确定5. 下列逻辑函数中,与A F =相等的是 。

)(A 11⊕=A F )(B A F =2⊙1 )(C 13⋅=A F )(D 04+=A F6. 设计一个6进制的同步计数器,需要 个触发器。

)(A 3 )(B 4 )(C 5 )(D 67. 下列电路中,属于时序逻辑电路的是 。

)(A 编码器 )(B 半加器 )(C 寄存器 )(D 译码器8. 列电路中,实现逻辑功能n n Q Q =+1的是 。

)(A )(B)(C (D) 9. 的输出端可直接相连,实现线与逻辑功能。

)(A 与非门 )(B 一般TTL 门)(C 集电极开路OC 门 )(D 一般CMOS 门 10.以下代码中为无权码的为 。

A . 8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码11.以下代码中为恒权码的为 。

A .8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码12.一位十六进制数可以用 位二进制数来表示。

A . 1B . 2C . 4D . 1613.十进制数25用8421BCD码表示为。

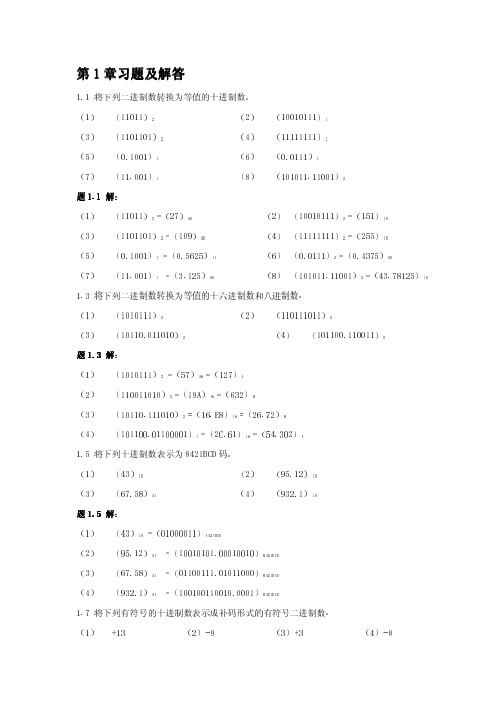

第1章习题及解答习题及解答及解答1.1 将下列二进制数转换为等值的十进制数。

(1) (11011)2 (2) (10010111)2(3) (1101101)2 (4) (11111111)2(5) (0.1001)2(6) (0.0111)2(7) (11.001)2 (8) (101011.11001)2.1 解解:题1.1(1) (11011)2 =(27)10 (2) (10010111)2 =(151)10(3) (1101101)2 =(109)10 (4) (11111111)2 =(255)10(5) (0.1001)2 =(0.5625)10 (6) (0.0111)2 =(0.4375)10(7) (11.001)2=(3.125)10 (8) (101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1) (1010111)2 (2) (110111011)2(3) (10110.011010)2 (4) (101100.110011)2题1.3解:(1) (1010111)2 =(57)16 =(127)8(2) (110011010)2 =(19A)16 =(632)8(3) (10110.111010)2 =(16.E8)16 =(26.72)8(4) (101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1) (43)10 (2) (95.12)10(3) (67.58)10 (4) (932.1)10题1.5解:(1) (43)10 =(01000011)8421BCD(2) (95.12)10 =(10010101.00010010)8421BCD(3) (67.58)10 =(01100111.01011000)8421BCD(4) (932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

习题四部分习题参考答案4.1 将下列函数简化,并用与非门和或非门画出逻辑电路图。

& (3)C B C A D C A B A D C B A F +++=),,,( 解:化简得F=C B C A B A ++F 的与非式为:F=C B C A B A •• ,逻辑电路图如图1所示。

F 的或非式为:F=C B A C B A C B A ABC F +++++=+=,逻辑电路图如图2所示。

图1 图2 4.3分析图4.59所示的逻辑电路图,并说明其逻辑功能。

解:(1)由逻辑电路图写出逻辑表达式并化简可得:DC D B D C D B F D BC D C B D C A D BC D C B D C A F CDABD CD ABD F +=⋅=++=⋅⋅=+=⋅=012(2)根据逻辑表达式,其逻辑功能如表所示。

1 C1&1&&&& &&ABF≥1 0 ≥1≥1≥1ACB ≥1≥1F由真值表可知,DCBA 表示的二进制数,当该值小于等于5,F0=1,当当该值小于等于10,大于5,F1=1,当该值小于等于15,大于10,F2=1。

4.4 试分析图4.60 所示的码制转换电路的工作原理答:①写出逻辑表达式001G B B =⊕ 112G B B =⊕ 223G B B =⊕ 33G B =D C B A F2 F1 F0 输 入 输 出0 00 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 0 0 1 0 0 1 1 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 1 0 1 0 1 0 0 1 0 1 0 1 1 1 0 0 1 1 0 0 1 0 0 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 1 1 0 0③由真值表可以发现,任意相邻的两个代码之间只有一位不同,而其余各位均相同。

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

数字逻辑练习题1. 题目描述:设计一个电路,将一个3位的二进制数转换为相应的BCD码。

BCD码是4位二进制数,表示0~9的十进制数字。

2. 解题思路:为了将一个3位的二进制数转换为BCD码,我们可以使用以下步骤:- 首先,将输入的3位二进制数分解为个位、十位和百位。

- 然后,将每一位上的二进制数转换为BCD码。

例如,对于个位数,可以使用一个4位的BCD码来表示,其中最高位为0,剩下的三位为个位数的二进制数。

同样地,对于十位和百位数,也需要使用4位的BCD码来表示。

- 最后,将个位、十位和百位上的BCD码连接起来,得到最终的BCD码输出。

3. 电路图设计:根据解题思路,我们可以设计如下的电路图:```+---------------+A0 --| |-- B0A1 --| |-- B1A2 --| 3-BIT TO |-- B2| BCD CODE |-- B3X3-BIN --| CONVERT |-- B4| ER |-- B5| |-- B6| |-- B7+---------------+```其中,A0、A1和A2分别表示输入的3位二进制数的个位、十位和百位。

X3-BIN表示这个3位二进制数的输入。

B0至B7分别表示输出的BCD码的4位。

4. 电路工作原理:在电路中,我们使用了一个“3-BIT TO BCD CODE CONVERTER”(3位二进制数转BCD码)芯片。

该芯片将输入的3位二进制数转换为相应的BCD码。

具体地,对于每一位二进制数,我们使用一个4位的BCD码来表示。

例如,对于个位数,最高位B0设置为0,剩下的三位B1, B2和B3设置为个位数的二进制数。

同样地,对于十位和百位数,也根据相应的二进制数设置BCD码的三位。

最终,我们将三个BCD码连接起来,得到一个12位的BCD码作为输出。

5. 总结:通过这个练习题,我们学习了如何将一个3位的二进制数转换为相应的BCD码。

在电路中,我们使用了一个“3-BIT TO BCD CODE CONVERTER”芯片来实现这个转换。

行政能力测试数字推理315道及详解1. 256 ,269 ,286 ,302 ,().307解析: 2+5+6=13 256+13=2692+6+9=17 269+17=2862+8+6=16 286+16=302=302+3+2=3072. 72 , 36 , 24 , 18 , ( ).16 C 解析:(方法一)相邻两项相除,72 36 24 18\ / \ / \ /2/1 3/2 4/3(分子与分母相差1且前一项的分子是后一项的分母)接下来貌似该轮到5/4,而18/=5/4. 选C3. 8 , 10 , 14 , 18 ,()A. 24B. 32C. 26D. 20分析:8,10,14,18分别相差2,4,4,?可考虑满足2/4=4/?则?=8所以,此题选18+8=264. 3 , 11 , 13 , 29 , 31 ,().53 C分析:奇偶项分别相差11-3=8,29-13=16=8×2,?-31=24=8×3则可得?=55,故此题选D5. -2/5,1/5,-8/750,()。

A 11/375B 9/375C 7/375D 8/375解析: -2/5,1/5,-8/750,11/375=>4/(-10),1/5,8/(-750),11/375=>分子 4、1、8、11=>头尾相减=>7、7分母 -10、5、-750、375=>分2组(-10,5)、(-750,375)=>每组第二项除以第一项=>-1/2,-1/2所以答案为A6. 16 , 8 , 8 , 12 , 24 , 60 , ( ).120 C分析:后项÷前项,得相邻两项的商为,1,,2,,3,所以选18010. 2 ,3 ,6 ,9 ,17 ,().23 C分析:6+9=15=3×53+17=20=4×5 那么2+?=5×5=25 所以?=2311. 3 ,2 ,5/3 ,3/2 ,()5 6 C.3/5 4分析:通分3/1 4/2 5/3 6/4 ----7/513. 20 ,22 ,25 ,30 ,37 ,().45分析:它们相差的值分别为2,3,5,7。

1.用代数法简化函数F=(A+B)(AB+C)为最简与或式。

2.试写出下图所示的同步时序逻辑电路的激励函数和输出函数表达式,并做出状态表。

3.图为某电平异步时序电路的结构框图,图中,做出电路的流程表。

4、用代数化简法求出逻辑函数BC C B A AB D C B A F ++=--),,,(的最简“与-或”表达式。

5、用“与或非”门实现逻辑函数∑=)14,12,7,6,5,4,3,1(),,,(m D C B A F ,并作出电路图。

6、某序列检测器有一个输入端x 和一个输出端Z 。

输 入端 x 输入一串随机的二进制代码,当输入序列中出现“011“时,输出Z 产生一个1输出,平时Z 输出0 。

典型输入、输出序列如下。

输入x: 1 0 1 0 1 1 1 0 0 1 1 0输出Z: 0 0 0 0 0 1 0 0 0 0 1 0试作出该序列检测器的Mealy 型原始状态图和原始状态表。

7、用一片3-8线译码器(74LS138引脚图如图示)和必要的逻辑门实现下列逻辑函数表达式。

---+=C AB C A F 1B A F +=-2 AB B A F +=--38.用卡诺图法化简函数AD)D A (C C B D)A D B(A P ++++=。

9.用多路选择器实现如下逻辑函数的功能 F(A,B,C)=∑m(2,3,5,6)。

P242.74153逻辑符号答案:1. 解:F = (A + B)(AB+ C)= AC +BC2.解:(1).输出函数和激励函数的表达式(2).电路次态真值表(3)状态表3、解:流程表:4.5、6、解:设:状态A------电路的初始状态;状态B------表示收到了序列“011”中的第一个信号“0”;状态C------表示收到了序列“011”中的前面两位“01”;状态D------表示收到了序列“011”。

(2)该序列检测器Mealy型状态图如下。

相应的原始状态表如下表所示。

习题一1.6 将下列二进制数据转换成十进制数、八进制数和十六进制数。

(1)1110101 (2)0.110101 (3)10111.011.7 将下列十进制数转换成二进制数、八进制数和十六进制数(二进制数精确到小数点后4位)(1)29 (2)0.27 (3)33.331.10 已知【N】补=1.0110,求【N】原,【N】反和N。

习题二2.2 用逻辑代数的公理、定理和规则证明下列表达式:2.4 利用反演规则和对偶规则求下列函数的反函数和对偶函数:2.6 用代数化简法求下列逻辑函数的最简式与-或表达式:2.7 将下列逻辑函数表示成“最小项之和”和“最大项之积”的简写形式:2.8 用卡诺图化简法求下列逻辑函数的最简或-与表达式:(1)(,,,)(2)(,,,)()()(3)(,,,)(2,4,6,10,11,12,13,14,15)F A B C D AB ACD AC BCF A B C D BC D D B C AD B F A B C D M =+++=++++=∏习题三3.13 在图3.68(a )所示的D 触发器电路中,若输入端D 的波形如图3.68(b )所示,试画出输出端Q 的波形(设触发器初态为0)。

(a )(b)3.14 已知输入信号A和B的波形如图3.69(a)所示,试画出图3.69(b)、(c)中两个触发器Q端的输出波形,设触发器初态为0。

习题四4.2 分析图3所示组合逻辑电路:(1) 指出在哪些输入取值下,输出F的值为1;(2)改用异或门实现该电路的逻辑功能。

4.4 设计一个组合逻辑电路,该电路输入端接收俩个2位二进制数A=A2A1,B=B2B1。

当A>B时,输出Z=1,否则Z=0。

4.8 设计一个“四舍五入”电路。

该电路输入为1位十进制数的8421码,当其值大于或等于5时,输出F 的值为1,否则F 的值为0。

4.12 下列函数描述的电路是否可能发生竞争?竞争结果是否会产生显像?若产生显象,试用增加亢余项的方法消除。