第四章 cadence ic5141教程Verilog 的使用方法

- 格式:pdf

- 大小:205.58 KB

- 文档页数:14

关于Cadenceic5141的安装关于Cadenceic5141的安装2008-04-17版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明/logs/19205304.html[绝对原创]经过一个多星期的反复摸索和实验,在无数次的重装与删除之后,本先生终于把万恶的Cadence塞到了笔记本里(洒花庆祝一下)。

在参考了网上无数大牛门的安装心得之后,决定写下此文。

一来为以后重装(呸呸呸……不吉利)留下技术参考,二来为和本先生一样的菜鸟抛砖引玉。

我的失败就是你们的经验啊,上帝啊,我不入地狱谁入地狱。

阿拉真主,阿弥陀佛…… 废话说完了,进入正题。

Cadence软件很好用,但安装起来很麻烦,所以在决定安装之前,需要做以下几件事情。

第一,下载安装文件。

IC5141一共是七张盘。

包括3张Base 和4张Update。

本先生只下到三张Base,Update没有找到。

如果谁有希望提供一下哈。

基本安装用Base就可以了,Update有当然更好,不过没有也基本不影响使用。

另外还要准备好license文件。

各大论坛都有,自己找吧,这里就不提供了。

如果找不到链接的本人提供一个地方,去上交BBS的微电子版块找找看,那里有一个内部的FTP,下载速度很快的,差不多300K/s,两个小时可以下完的。

IC5141和IC610的版本都有,还有MMSIM610,教育网的同志们可以去下。

具体地址就不提供了,我也忘记了。

第二,安装Linux。

现在Linux的版本很多,麻烦各位挑的时候别太随意。

本人在这里吃了很大的亏。

一般来说,版本越新的安装的难度就越大。

具体原因是这样的。

Linux的进程机制分两种。

Linuxthreads和NPTL,其中早期的Linux支持前者,随着内核的升级,目前版本的Linux都已经放弃了对Linuxthreads的支持,转为采用NPTL。

很不幸的是,IC5141采用了比较保守的原则,只支持Linuxthreads,所以一定要在支持Linuxthreads的Linux内核下才能够运行。

verilog !用法-回复Verilog 是硬件描述语言(Hardware Description Language, HDL) 的一种,主要用于描述数字系统的行为和结构。

它是一种高级语言,可用于描述电子系统的硬件功能和电路行为。

Verilog 具有模块化和并行化的特性,能够快速且准确地描述电子系统及其各个组件之间的相互关系。

本文将以"Verilog 用法" 为主题,为读者逐步介绍Verilog 的基础知识和常见用法。

第一部分:Verilog 简介和基础知识(500 字)1. 什么是Verilog?Verilog 是一种硬件描述语言,用于描述数字系统的行为和结构。

它是一种高级语言,能够准确描述电子系统的硬件功能和电路行为。

2. Verilog 的起源和发展最早的Verilog 是在1984 年由Gateway Design Automation 公司的Philip Moorby 发明的。

之后,它被开放出来,并逐渐成为数字系统设计的行业标准。

3. Verilog 的基本元素Verilog 包含模块(module)、端口(port)、信号(signal)、寄存器(register)、线网(wire)、输入(input)、输出(output)、内部连接(assign)等基本元素,这些元素共同构成了一个完整的Verilog 描述。

4. Verilog 的行为建模Verilog 提供了多种行为建模的方式,包括组合逻辑(combinational)、时序逻辑(sequential)、有限状态机(finite state machine)等,使得设计者能够准确地描述电子系统的行为和时序。

第二部分:Verilog 模块和端口定义(500 字)1. Verilog 模块的定义Verilog 中的模块是一个独立的功能单元,它可以包含多个输入输出端口和内部信号,用于描述一个子系统的功能。

模块内部可以包含连接和互连逻辑,以及寄存器等具体的硬件描述。

c@dence_i_c5141和mm$im61的安装过程和配置方法。

系统的考虑,按照道理来说应该是所有的linux系统都能安装运行i_c5141的,只不过因为各个linux组件实现不完全统一,所以在安装i_c5141的时候会出现各种问题,但是只要你有相关linux系统的知识,对于linux一些基本设计理念比较熟悉的话,应该都是可以通过调整系统来安装运行i_c5141的。

安装i_c5141的过程实际上就是一个根据c@dence给出的错误信息进行debug的过程,你把所有的bug都解决了,软件也就自然能运行了。

现在已知可以运行i_c5141的系统rehl,centos,suse,ubuntu还有archlinux。

推荐使用的系统是rehl或是centos,这两个应该是兼容性最好的,当然下面的安装过程还是以archlinux为例来讲解的。

1 确认所用linux系统的tar版本在1.14以下,否则不能正常解压安装包。

2 下载安装包,包括:Update_IC50.46.006_lnx86_1of4.tarUpdate_IC50.46.006_lnx86_2of4.tarUpdate_IC50.46.006_lnx86_3of4.tarUpdate_IC50.46.006_lnx86_4of4.tarCadence.Base.IC5141.Lnx86.3CDs[.ck].rar,---这个是5141的三个base包合成一个了。

Base_MMSIM61_lnx86_1of2.tarBase_MMSIM61_lnx86_2of2.tar用tar xvf filename全部解压缩,将得到的update包放在一个文件夹内,如/ic/IC50.46.006_lnx86.Update,base包会解压到另一个文件夹,如/ic/base_5141,将mm_sim的cd1和cd2放在另一个文件夹内,如/ic/mm_sim。

- Cadence中V erilog XL的一些使用方法一、学习Verilog 的必要性。

随着电路规模的增大和复杂,传统的图形输入模式已不可行。

语言描述电路成为潮流。

它的方便性和好的更改性、维护性在实践中得到很好的体现。

尤其现在强大的综合工具,和系统集成对核的需求性使Verilog更有用武之地。

每个硬件工程师应该学习掌握它。

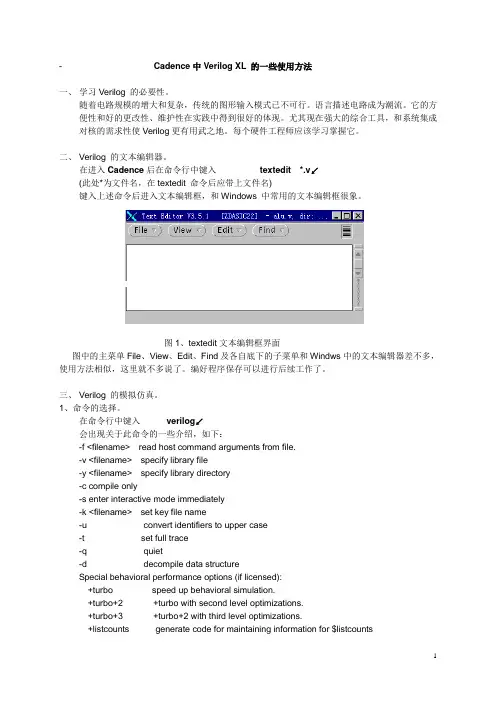

二、Verilog 的文本编辑器。

在进入Cadence后在命令行中键入textedit *.v↙(此处*为文件名,在textedit 命令后应带上文件名)键入上述命令后进入文本编辑框,和Windows 中常用的文本编辑框很象。

图1、textedit文本编辑框界面图中的主菜单File、View、Edit、Find及各自底下的子菜单和Windws中的文本编辑器差不多,使用方法相似,这里就不多说了。

编好程序保存可以进行后续工作了。

三、Verilog 的模拟仿真。

1、命令的选择。

在命令行中键入verilog↙会出现关于此命令的一些介绍,如下:-f <filename> read host command arguments from file.-v <filename> specify library file-y <filename> specify library directory-c compile only-s enter interactive mode immediately-k <filename> set key file name-u convert identifiers to upper case-t set full trace-q quiet-d decompile data structureSpecial behavioral performance options (if licensed):+turbo speed up behavioral simulation.+turbo+2 +turbo with second level optimizations.+turbo+3 +turbo+2 with third level optimizations.+listcounts generate code for maintaining information for $listcounts+no_turbo don't use a VXL-TURBO license.+noxl disable XL acceleration of gates in all modulesSpecial environment invocation options (if licensed):+gui invoke the verilog graphical environment在上面的参数选择中,简单介绍几个常用的:(1) -c首先应该保证所编程序的语法正确性。

verilog教程当您开始学习Verilog时,以下是一些重要的基础知识和概念。

1. Verilog是一种硬件描述语言(HDL),用于描述和设计数字电路。

它可以用于模拟、合成和验证电路。

2. Verilog使用模块化的设计风格。

每个设计都由一个或多个模块组成,每个模块有自己的输入和输出。

3. 使用`module`关键字定义一个模块,并在其后给出模块的名称。

```verilogmodule my_module;// 模块主体endmodule```4. 模块内部包含用`input`和`output`声明的端口,用于与其他模块进行通信。

```verilogmodule my_module(input wire a,input wire b,output wire c);// 模块主体endmodule```5. `wire`关键字用于声明连接不同模块的导线。

可以将导线看作是用于传输数字信号的线。

6. 在模块主体中,可以使用`assign`关键字创建逻辑连接。

逻辑连接使用`=`运算符连接输入和输出。

```verilogmodule my_module(input wire a,input wire b,output wire c);assign c = a & b;endmodule```7. 除了逻辑连接外,可以在模块内部使用`always`块创建组合和时序逻辑。

```verilogmodule my_module(input wire a,input wire b,output wire c);reg d;always @(a or b)d = a | b;assign c = d;endmodule```8. Verilog还支持使用`if-else`语句,`case`语句和循环结构等常见的编程结构。

9. 为了模拟和验证设计,可以使用Verilog仿真工具,如ModelSim、VCS等。

操作系统:CentOS-5.5-i386;虚拟机:VMwareWorkstation-6;软件:cadence ic5141 USR6和Base 1、安装CentOS-5.5,在软件定制部分需要立即定制,然后选择旧版支持,Java软件等等。

软件定制选择如下:桌面环境全选;应用程序全选;开发全选;基本系统全选;虚拟化全选;服务器选windows文件服务器,万维网服务器,打印支持。

2、由于CentOS-5.5的tar-1.15.1,sort-5.97,expr-5.97版本过高,需要用tar-1.14,sort-5.2.1,expr-5.2.1才能正常解压安装,而这几个程序可以在CentOS-4.8中找到。

之后,使用root账户登录,分别对应替换高版本的/bin/tar,/bin/sort,/usr/bin/expr。

此处记得备份CentOS-5.5的原件哦!(另外,我也给出了CentOS-4.8和CentOS-5.5中的程序,以便大家下载)3、新建一个用户kury(这个根据喜好,但此处我用kury说明),在/home/kury目录中新建文件夹cadence_install。

之后,在cadence_install里面新建文件夹base,update,用于存放IC5141的base 包跟update包。

base包在电驴上有:ed2k://|file|Cadence.Base.IC5141.Lnx86.3CDs[.ck].rar|1201102747|A4DE108A291CC6BDD86D8E46D3E5 A677|h=PWYDUTUBIMHDVZ2EDLNMRNAKGAVIWJFA|/USR6 update包在论坛里有:/viewthread.php?tid=219912&highlight=USR6此处需要说明,在CentOS-5.5下安装必须要有这两个包,不然不能运行cadence!!!4、解压:Cadence.Base.IC5141.Lnx86.3CDs[.ck] 得到三个base包,一个cadence_license_full.dat;解压:Update_IC50.46.006_lnx86得到四个update包。

verilog 函数的使用Verilog函数的使用Verilog是一种硬件描述语言,常用于数字电路的设计和验证。

在Verilog中,函数是一种重要的组织代码的方式,可以将一段具有特定功能的代码封装成函数并在需要的时候进行调用。

本文将介绍Verilog函数的使用方法和一些常见的应用场景。

一、函数的定义和使用在Verilog中,函数的定义使用关键字"function",并指定函数的返回类型和参数列表。

以下是一个简单的函数示例:```function int add(int a, int b);add = a + b;endfunction```以上函数名为"add",返回类型为整数(int),参数列表中有两个整型参数a和b。

函数体中的代码实现了将a和b相加的功能,并将结果赋值给函数的返回值。

函数的调用使用关键字"call",并在括号中传入相应的参数值。

以下是调用上述函数的示例:```int result;result = add(3, 4);```在这个示例中,函数"add"被调用,并将参数3和4传入。

函数执行完毕后,返回值7被赋值给变量"result"。

二、函数的返回值函数在执行完毕后会返回一个值,该值的类型与函数的返回类型相匹配。

在函数体中,可以使用关键字"return"来指定返回的值。

以下是一个返回布尔类型的函数示例:```function bit isEven(int num);if(num % 2 == 0)return 1'b1; // 返回真elsereturn 1'b0; // 返回假endfunction```在这个示例中,函数"isEven"接收一个整数参数"num",并通过判断num是否为偶数来返回一个布尔值。

cadence 5141 安装在linux下安装cadence(设定安装文件放在windows下d盘,为hda5)1切换用户到超级用户:(以下均省略提示符,隔行表示直接输入的字符)Su /切换用户,缺省为超级用户,若是切换普通用户在su后空格加用户名888888 /超级用户密码cd / /至系统根目录2 在系统根目录下建立一个安装目录,如edamkdir eda /建立安装目录文件chmod –R 755 eda /更改文件属性使之能够被普通用户使用chown -R b704:b704 eda /具体释放权限给某个用户3 创建挂载点和执行安装的临时文件cd /mntmkdir evol 挂载d盘的文件夹.起引导作用,不是实际存储mkdir cdrom /用于挂载iso文件,类似光驱mkdir temp4 挂载文件mount /dev/hda5 /mnt/evol /将windows下的硬盘d挂载到本地挂载点cd /mnt/evoldircp -r ic5141 /mnt/temp /将安装文件放置在临时文件夹cd /mnt/tempdircd ic5141dirmount -o loop cd1.iso /mnt/cdrom /挂载iso文件到光驱cd /cd /mnt/cdromdir.setup.sh /执行安装文件5 根据提示进行安装,基本上选择默认设置即可:须注意三点选择安装内容的时候,选a 即全选提示安装信息置放在哪时.选择4(anolog catalog,而不选择默认的2-email)最后确定安装的路径的时候输入以下信息/eda/ic51,自动会提示在eda下创建ic51文件安装进行过程中加入新的iso文件时另开终端执行,安装结束即执行了100%时,选择q退出即可,不需理会其他选项.6 安装结束,在安装ic5141的目录下即/eda/ic51 下新建一个文件夹license,然后将license.dat拷贝到此目录下,具体文件放在mnt/temp/ic5141/lic_setings/license(这一步可以直接在文件系统里拷贝)7 将文件/eda/ic51/tools.lnx86重命名,命令为:(cd /eda/ic51)ln -s tools.lnx86 tools8 将配置文件.bashrc 和.cdsinit文件拷贝到个人用户的根目录下具体配置文件放在/mnt/temp/ic5141/lic_setings 个人用户根目录/home/b704cd /mnt/temp/ic5141/lic_setingscp .bashrc /home/b704cp .cdsinit /home/b7049 用vi命令打开.bashrc 文件,把安装路径修改成与安装路径相一致并保存: /eda/ic51vi /home/b704/.bashrc (最好先进入子目录cd /home/b704)将修改好的.bashrc 文件写入内存source .bashrc10 运行icfb&, 没用问题即可使用.将u盘挂载在linux下的命令是:mkdir /mnt/usbmount -t vfat/dev/sda1/mnt/usb当出现没有读写权限的文件,需要释放权限的话,比如是/home/b704/m 文件夹下的文件有如下问题时chown -R b704:b704/home/b704/m使用Cadence需要加入Library的问题:以使用chrt库为例先将chrt的库文件拷贝到/home/b704/chrt 下这一步可以直接进行文件夹一级的操作,不用使用命令格式运行icfb& 在菜单选项处的tool里选择Library manager->进入新一级的窗口编辑框选择edit ->Library path 又进入一级窗口编辑框选择edit->add Library. 出现一个路径选择窗口chrt chrt _basic 在此添加chrt chrt_dig_basic命令说明用户切换命令su 默认设置为超级用户root,需要以密码进入;若进入普通用户的话:su用户名进入文件命令cd 如:cd/mnt/evol 返回上一次进入的目录路径:cd --返回到root根目录:cd创建文件命令用mkdir直接创建全路径,如mkdir /mnt/temp/usb 或者是先进入cd /mnt/temp 再创建目录mkdir usb显示文件命令有两种形式ls/mnt/temp 这种方式并没有改变提示符所显示的目录路径cd /mnt/temp 进入目录路径再现是目录文件:dir文件拷贝命令cp –r 源文件路径目录文件路径如cp -r /mnt/evol/ic5141 /mnt/temp 若拷贝的仅仅是文件不用添加-r选项.重命名命令ln –s 源文件目的文件这个命令的重命名是新建一个文件,对源文件的东西进行复制,并不会对源文件做任何处理,即源文件仍然不错修改的存在删除文件命令rm 目的文件rm -r 目的目录root下的mnt目录文件是专门为挂载外来文件的,常用于挂载如windows操作系统下的硬盘,usb 接口等:将u盘挂载再linux下的命令是:mkdir /mnt/usbmount -t vfat/dev/sda1 /mnt/usb挂载windows下的硬盘mount/dev/hda5 /mnt/evol (如d盘)挂载镜像文件iso文件mount –o loop **.iso /mnt/cdrom当出现没有读写权限的文件,需要释放权限的话,比如是/home/b704/m 文件夹下的文件有如上问题时chmod -R 755 /home/b704/m /更改文件属性使之能够被普通用户使用chown -R b704:b704 /home/b704/m /具体释放权限给某个用户vi命令时可以对文件进行编辑的命令.通常这种被操作不是文件夹,而是个可编译的文件.修改用户进口令Passwd注意创建用户必须是以root用户名进入才可以执行Useradd 用户名Passwd 用户名输入密码并予以确认.清楚当前屏幕信息Clear。

Cadence IC使用教程说明:本克隆文件包含Cadence IC,Synopsys,Mentor三个大类软件,无需安装,直接用虚拟机打开即可。

文件夹EDA中就是虚拟机的克隆文件,请用VMware15打开EDA.vmx,可到公众号“鱼与渔大学生服务”中回复VMware获取VMware15软件。

虚拟机克隆账户无密码,直接登陆即可。

打开虚拟机克隆以后,先把license文件夹中的License.dat(windows路径)覆盖到/opt/synopsys/License/Liense.dat(虚拟机路径)。

覆盖完以后重启虚拟机系统。

指令为:cp-rf/mnt/hgfs/license/License.dat./License.dat(在License 路径下打开终端)具体软件包含如下:Cadence IC:Assura4:仿真工具IC617:virtuoso设计工具。

Incisive14:NC仿真工具,更名为Incisive,命令完全不变。

Innovus15:encounter后端布局布线工具,已更名,命令可用innovus,也可用encouter启动。

MMSIM15:进行spectre仿真Synopsys:Formality2016:形式验证Hspice2016:网标仿真ICC2016:布局布线Laker2015:PrimeTime2015:形式验证StarRC2015Synplify2015:Design Compiler逻辑综合工具,现已更名,命令几乎不变。

VCS2014:由于VCS2016仿sv时会出现runtime问题,故安装此稳定版本。

Verdi2015MentorCalibre2015:作LVSTessent2013:DFT工作平台。

DFTadvisor、Fastscan、TestKompress:高版本工具以命令行操作为主。

一些注意事项如下:Cadence目录在/opt/CadenceSynopsys目录在/opt/SynopsysSynopsys目录在/opt/SynopsysMentor目录在/opt/MentorIC617中有部分基本库,IC617需要用0a库,文件中“工艺库大全--数字与模拟”包含了一些工艺库,带“OA”字样的文件夹包含IC617能用的OA库,有些是CDB 库,需要转换成OA库,具体方法请参考“Cadence IC工艺库转换方法”Synopsys:使用前先把license文件夹中的License.dat(windows路径)覆盖到/opt/synopsys/License/Liense.dat(虚拟机路径)。

Verilog-HDL仿真软件ModelSim 的基本操作Verilog-HDL与CPLD/FPGA设计应用讲座第 4 讲Verilog-HDL仿真软件的基本操作4.1 建立新的工程文件4.2 一个最简单的仿真实例在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。

4.1 建立新的工程文件启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项,然后选择【Project】选项。

如图1所示。

图1 建立一个新的工程文件单击后,在弹出的对话框内适当填写工程文件名,如图2所示。

单击【OK】后,一个新的工程文件就建立了。

图2 工程文件名称及位置的填写4.2一个最简单的仿真实例[To top]下面,用一个"与"运算的仿真应用例子来说明ModelSim XE仿真软件的操作过程。

通过这个最简单的例子,可以基本掌握该软件的使用方法。

编辑如下两个文件/* exp1-1.v */module AND2 ( A, B, OUT );input A, B;output OUT;and U1 ( OUT, A, B );endmodule/* fig1-9.tst */`timescale 1ns/1nsmodule AND2_TEST;reg A, B;wire OUT;AND2 AND2 (A, B, OUT);initial beginA = 0;B = 0;#100 A = 1;#100 A = 0; B = 1;#100 A = 1;#200 $finish;endendmodule第一个是与门逻辑的Verilog-HDL描述,第二个是相应的顶层模块(测试程序),将这两个文件拷贝到test的目录下,如图3所示。

图3 工作目录下的文件然后,在【Project】选项中单击鼠标右键,就弹出图4所示的快捷菜单。

verilog教程Verilog是一种硬件描述语言(HDL),用于设计和描述数字电路。

它是一种事件驱动的语言,可以用来描述时序逻辑和组合逻辑。

Verilog可以用于设计和验证各种数字电路,从简单的门电路到复杂的处理器和系统。

Verilog的语法和结构与C语言相似,它由模块、端口、信号和行为描述组成。

Verilog中的模块是模块化设计的基本单元,可以将模块集成到更大的设计中。

模块可以具有输入端口、输出端口和内部信号。

输入和输出端口用于与其他模块进行通信,而内部信号用于在模块内部传递和保存数据。

Verilog的行为描述方式包括并行块和顺序块。

并行块表示同时执行的代码,而顺序块表示按顺序执行的代码。

Verilog中的并行块使用关键字"always @(posedge clock)"来表示,其中的代码只在时钟上升沿触发时执行。

顺序块使用关键字"always @(*)"来表示,其中的代码在输入信号变化时立即执行。

在Verilog中,可以使用各种逻辑运算符,如AND、OR、NOT和XOR,来实现组合逻辑。

此外,还可以使用各种触发器和寄存器类型,如D触发器和JK触发器,来实现时序逻辑。

通过将组合逻辑和时序逻辑结合起来,可以实现复杂的数字电路。

Verilog的仿真可以使用各种工具,如ModelSim和Vivado,来验证设计的正确性。

仿真可以通过将输入信号施加到设计中,然后观察输出信号的变化来进行。

如果输出信号与预期的结果一致,那么设计就是正确的。

在Verilog中,还可以使用分层设计的概念来实现模块的结构化和组织。

通过使用层次化模块,可以将设计划分为更小的模块,并将它们组合在一起以实现更大的系统。

尽管Verilog的学习曲线可能有点陡峭,但它是数字电路设计中最常用和最强大的工具之一。

通过掌握Verilog,您可以实现自己的数字电路设计,并进行验证和测试。

总之,Verilog是一种用于设计和描述数字电路的硬件描述语言。

第四章Cadence中Verilog的一些使用方法§ 4-1 Verilog 的文本编辑器随着电路规模的增大和复杂,传统的图形输入模式已不可行。

语言描述电路成为潮流。

它的方便性和好的更改性、维护性在实践中得到很好的体现。

尤其现在强大的综合工具,和系统集成对核的需求性使Verilog更有用武之地。

每个硬件工程师应该学习掌握它。

在进入Cadence后在命令行中键入textedit *.v↙(此处*为文件名,在textedit 命令后应带上文件名)键入上述命令后进入文本编辑框,和Windows 中常用的文本编辑框很象。

图4-1-1textedit文本编辑框界面图中的主菜单File、View、Edit、Find及各自底下的子菜单和Windws中的文本编辑器差不多,使用方法相似,这里就不多说了。

编好程序保存可以进行后续工作了。

§ 4-2 Verilog 的模拟仿真一.命令的选择。

在命令行中键入verilog↙会出现关于此命令的一些介绍,如下:-f <filename> read host command arguments from file.-v <filename> specify library file-y <filename> specify library directory-c compile only-s enter interactive mode immediately-k <filename> set key file name-u convert identifiers to upper case-t set full trace-q quiet-d decompile data structureSpecial behavioral performance options (if licensed):+turbo speed up behavioral simulation.+turbo+2 +turbo with second level optimizations.+turbo+3 +turbo+2 with third level optimizations.+listcounts generate code for maintaining information for $listcounts+no_turbo don't use a VXL-TURBO license.+noxl disable XL acceleration of gates in all modules Special environment invocation options (if licensed):+gui invoke the verilog graphical environment 在上面的参数选择中,简单介绍几个常用的:(1)-c首先应该保证所编程序的语法正确性。

先进行语法的检查,选择参数- c键入如下命令。

verilog –c *.v↙根据Cadence的报告,查找错误信息的性质和位置,然后进入文本编辑器进 行修改,再编译,这是个反复的过程,直到没有语法错误为止。

(2)-s进入交互式的环境,人机交互运行和下面的参数联合使用。

(3)+gui &verilog 仿真有命令和图形界面两种方式。

图形界面友好和windows使用很象,很好掌握,一般都使用图形方式。

“&”符号是后台操作的意思,不影响 前台工作。

如此时你可以在命令行输入其它的命令。

其它的命令参数选择比较复杂,这里就不介绍了,故我们这里常用的命令是:verilog –s *.v +gui &↙ (*代表文件名)进入图形交互界面。

$附:命令行输入!!↙是执行上一条命令,命令行输入!* ↙ (*代表字母)是执行最近的以*开头的命令。

上述附注对命令输入速度提高有所帮助。

二.SimVision 图形环境。

SimVision是Verilog-XL的图形环境。

主要有SimControl、Navigator、 Signal Flow Browswer、 Wactch Objects Window 、SimWave 等窗口。

(1)SimControl 窗口此窗口是主要的仿真控制窗口,让用户和机器进行交互式操作。

执行各种Verilog-XL 命令(菜单),进行仿真、分析、调试你的设计。

该窗口可以显示设计的模块和模块,显示和设置断点、强制信号等。

创建用户自己的按钮和执行经常使用的操作。

图4-2-1 SimControl 窗口界面图I/O Region⑤Message Region⑥部分简介:菜单,让你执行各种模拟仿真命令。

这里就不一一介绍,到使用②、表最常用的操作和功能,能快速对选中的物体执行各种命令。

你各①、Menu Bar有许多的子时,在指明其功能和所在位置。

Tool Bar各种按钮代可以在工具条中加入自己定义的按钮,来代表常用的操作命令。

使用Option-User Buttons-Create 菜单项。

用Options-User Buttons-Edit 菜单项修改修改按钮。

工具条还显示当前模拟时间,当处于交互式的模拟状态时,会随模拟更新时间。

因为工具条按钮的操作为常用操作,下面各功能详细介绍一下。

运行模拟按钮 设置模块按钮 对对象执行操作按钮 调用其它显示窗口按钮显示模拟时间i j 放定义按钮a b c d e f g h k l m n用户自 是否显示程序代码 图4-2-2 SimControl 窗口中的工具条a、Run Simulation 按钮运行模拟,若无断点直至完成,图标变为停止模拟图标。

若有断点则运行到执行到下一个可执行行,即使在子程序中也是单步运行。

行到下一个可执行行,在子程序中步单步执行,而是一步转到被选中的模块。

的上一级模块,但若有对象被选中,不执行。

示正在模拟的模块。

在当前刚执行完的代码行左边point 按钮被选信号变化时发生。

代码左边的行号为高亮的可面有当前选中信号的名字和数值。

用户可以强制信号为一e 按钮切换按钮。

显示当前被选信号的数值。

断点对应信号再改变的位置。

b、Single Step 按钮再任何模块每按一下c、Step Over 按钮在当前的模块中执执行完子程序。

d、Set Scope 按钮 由当前的调试模块e、Scope Up 按钮由当前模块转到它f、Show Execution 按钮模拟时更新当前模块,显有一个箭头g、Set Break 设置断点,当模拟过程中设为断点,灰色则不可以。

h、Set Force 按钮弹出一个窗口,里个希望值。

i、Show Valu n、程序代码是否显示的以下j、k、l、m 调用其它调试窗口,具体介绍放到后面。

j、打开Navigator 窗口。

k、打开Watch Objects 窗口。

显示被选中的对象象放到浏览器中码,每行左边有行号。

你可以在其间选择信号和模块。

这Scope Regiond 和subscopes field。

从下拉按钮选择不同的项,跳到不和模拟输出的结果。

你也可以直接在此键入命令执行操作。

on.Navigator 窗口j 字母所代表的按钮一样的按钮打开Navigator 窗口。

此l、打开Singal Flow Browser 窗口。

把被选中的对m、打开SimWave 窗口。

显示被选中对象的模拟波形。

③、Source Browser显示被调试的程序代种选择会影响其它工具的操作对象,反过来其他工具操作对象的选择也会作用于Source Browser 信号和对象的选择。

可在其间设置断点,如前所说的在行号为高亮的行可设为断点,灰色则不可以。

可在Source Browser 中点鼠标的右键选择菜单进行操作。

另一个对选择对象的操作是双击该对象。

如双击信号得到它的数值,双击模块则调到该模块描述处。

如图4-2-2中的n 字母代表的按钮,Source Browser 可被关掉不显示。

④、 包含scope fiel 同的模块。

对应的Source Browser 显示该模块的代码。

⑤、I/O Region显示执行的命令I/O Region 也可以被关掉不显示,当点击Message Region 右边的三角按钮可切换显示与否。

⑥、Message Regi 显示模拟状态。

三 按下和图4-2-2中窗口用图形,在Scope Tree 中采用树的形式显示设计中各模块的层次关系。

在Objects List 中显出Scope Tree 中被选模块的当前模拟数值和描述。

图4-2-3 Navigator窗口①、Menu Bar提供各种命令和操作,有下拉菜单(如下面的图4-2-4)和右键弹出菜单两种。

选中对象点击右键可选择对对象操作所需的命令,如下面的图4-2-5。

图4-2-4 Navigator窗口的菜单图4-2-5 Navigator中的PoP-Up菜单②、Tool Bara、设置模块b、对选择对象操作c、调用其他显示窗口 图4-2-6 Navigator中的工具条a、b、c同SimControl窗口中的工具条对应按钮的功能一样,都是对选择对象进行相应的操作。

只是对象可以在SimControl窗口选择也可以在Navigator 窗口中选择,互相影响。

③ 、Hierarchy Path显示当前模块的直接路径,其他路径不显示。

可选择其间的模块点击右键弹出菜单进行操作。

④、Scope Tree对被选中的模块用树的形式表示出来。

在图4-2-4中Options-Scope Tree…菜单项中有关于对象显示的的性质,有Filters、Formatting、Layout三栏,各有一些选项供选择。

影响当前Scope Tree显示的内容。

⑤、Objects List显示当前调试模块里的信号和当前数值。

在在图4-2-4中Options-Objects List…菜单选项有Filters、Formatting两栏,会影响Objects List中的显示内容。

在Selcet子菜单中的选项(如图4-2-4)能选取某一类别的信号,如都是Wires型,或是Registers型。

四.Singal Flow Browser 窗口该窗口跟踪可疑信号的值,进入有三个方法(1) 按下图4-2-2中j 字母所代表的按钮(2)SimControl 窗口Tools- Singal Flow Browser 菜单项(3) 图4-2-6 Navigator 中的工具条中字母c 的第二个按钮打开窗口。

(4) Wactch Objects Window 中按下图4-2-2 中j 字母所代表的按钮的一样的按钮界面如下图。