例1某TTL与非门电压传输特性如图2-1(精)

- 格式:doc

- 大小:453.50 KB

- 文档页数:9

ttl与非门的电压传输特性和主要参数

1. TTL门电压传输特性

TTL门的电压传输特性是指TTL门的输入电压和输出电平之间的关系。

TTL门的输入电压范围一般为0V~5V,当输入电压为低电平(0V)时,TTL门将输出高电平(5V);当输入电压为高电平(5V)时,TTL门将输出低电平(0V)。

在TTL门的输入电压范围内,当输入电压超过门电平(VIL和VIH),门的输出电平会及时响应并产生相应的输出电平。

但当输入电压处于门电平之间时,门的输出电平不能保证为确定的电平,即可能出现无法确定的电平输出状态,这种状态称为不稳定区域。

2. TTL门主要参数

(1)输入电平逻辑门限电压(VIL和VIH)

IIL和IIH分别是TTL门的低电平输入电流和高电平输入电流。

IIL和IIH对应的输入电平是VIL和VIH,它们代表向TTL门输入0V和5V时的电流大小。

输入电流的大小会影响门的速度和功耗。

VOH和VOL分别是TTL门的高电平输出电压和低电平输出电压。

输出电平的值应该在规定的范围内,这个范围由标准定义。

(4)输出电流(IOH和IOL)

IOH和IOL分别是TTL门的高电平输出电流和低电平输出电流。

它们表示TTL门在输出高(低)电平时的输出电流大小。

非门的输入电平逻辑门限电压与TTL门的相同,低电平逻辑门限电压VIL为0V,高电平逻辑门限电压VIH为5V。

但是,非门的输入电平逻辑门限电压范围相对较小,因为非门不需要输出不稳定区间。

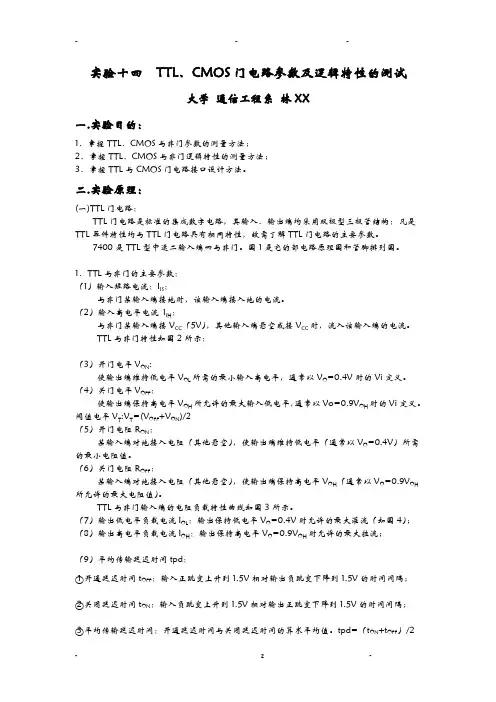

实验十四TTL、CMOS门电路参数及逻辑特性的测试大学通信工程系林XX一.实验目的:1、掌握TTL、CMOS与非门参数的测量方法;2、掌握TTL、CMOS与非门逻辑特性的测量方法;3、掌握TTL与CMOS门电路接口设计方法。

二.实验原理:(一)TTL门电路:TTL门电路是标准的集成数字电路,其输入、输出端均采用双极型三极管结构:凡是TTL器件特性均与TTL门电路具有相同特性,故需了解TTL门电路的主要参数。

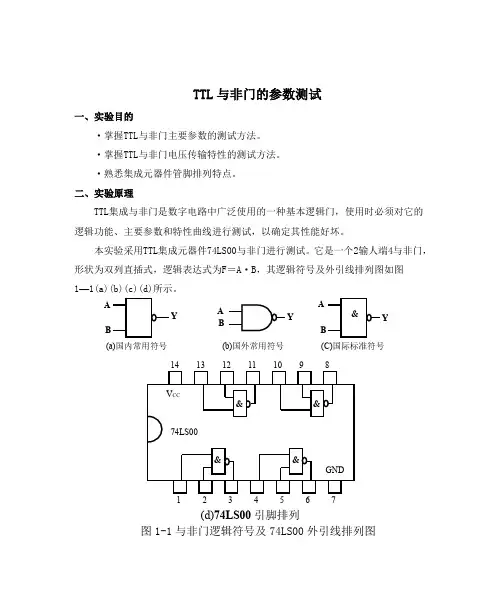

7400是TTL型中速二输入端四与非门。

图1是它的部电路原理图和管脚排列图。

1、TTL与非门的主要参数:(1)输入短路电流:I IS:与非门某输入端接地时,该输入端接入地的电流。

(2)输入高电平电流I IH:与非门某输入端接V CC(5V),其他输入端悬空或接V CC时,流入该输入端的电流。

TTL与非门特性如图2所示:(3)开门电平V ON:使输出端维持低电平V OL所需的最小输入高电平,通常以V O=0.4V时的Vi定义。

(4)关门电平V OFF:使输出端保持高电平V OH所允许的最大输入低电平,通常以Vo=0.9V OH时的Vi定义。

阀值电平V T:V T=(V OFF+V ON)/2(5)开门电阻R ON:某输入端对地接入电阻(其他悬空),使输出端维持低电平(通常以V O=0.4V)所需的最小电阻值。

(6)关门电阻R OFF:某输入端对地接入电阻(其他悬空),使输出端保持高电平V OH(通常以V O=0.9V OH 所允许的最大电阻值)。

TTL与非门输入端的电阻负载特性曲线如图3所示。

(7)输出低电平负载电流I OL:输出保持低电平V O=0.4V时允许的最大灌流(如图4);(8)输出高电平负载电流I OH:输出保持高电平V O=0.9V OH时允许的最大拉流;(9)平均传输延迟时间tpd:○1开通延迟时间t OFF:输入正跳变上升到1.5V相对输出负跳变下降到1.5V的时间间隔;○2关闭延迟时间t ON:输入负跳变上升到1.5V相对输出正跳变下降到1.5V的时间间隔;○3平均传输延迟时间:开通延迟时间与关闭延迟时间的算术平均值。

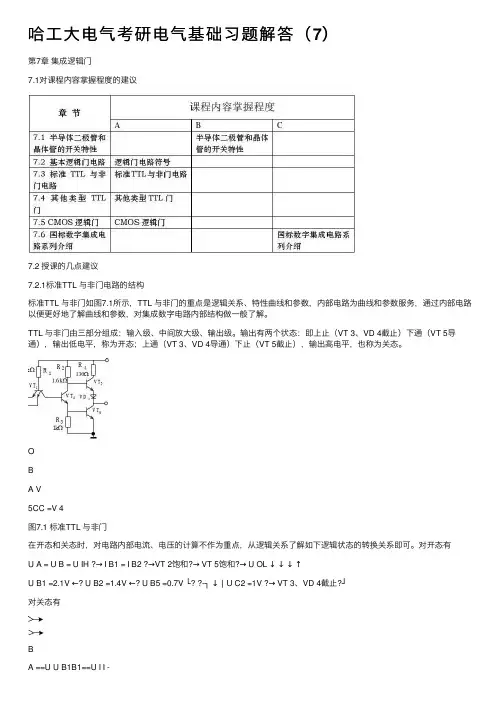

哈⼯⼤电⽓考研电⽓基础习题解答(7)第7章集成逻辑门7.1对课程内容掌握程度的建议7.2 授课的⼏点建议7.2.1标准TTL 与⾮门电路的结构标准TTL 与⾮门如图7.1所⽰,TTL 与⾮门的重点是逻辑关系、特性曲线和参数,内部电路为曲线和参数服务,通过内部电路以便更好地了解曲线和参数,对集成数字电路内部结构做⼀般了解。

TTL 与⾮门由三部分组成:输⼊级、中间放⼤级、输出级。

输出有两个状态:即上⽌(VT 3、VD 4截⽌)下通(VT 5导通),输出低电平,称为开态;上通(VT 3、VD 4导通)下⽌(VT 5截⽌),输出⾼电平,也称为关态。

OBA V5CC =V 4图7.1 标准TTL 与⾮门在开态和关态时,对电路内部电流、电压的计算不作为重点,从逻辑关系了解如下逻辑状态的转换关系即可。

对开态有U A = U B = U IH ?→ I B1 = I B2 ?→VT 2饱和?→ VT 5饱和?→ U OL ↓↓↓↑U B1 =2.1V ←? U B2 =1.4V ←? U B5 =0.7V └? ?-┐↓∣ U C2 =1V ?→ VT 3、VD 4截⽌?┘对关态有BA ==U U B1B1==U I I -----→截⽌截⽌52VT VT ↓OH 43B3R2 VD VT U I I →→=饱和、↓7.2.2标准TTL 与⾮门电路的特性曲线及参数TTL 与⾮门的特性曲线有: u O = f (u I )---电压传输特性曲线;u OL = f (i OL )----输出低电平负载特性曲线; u OH = f (I OH )---输出⾼电平负载特性曲线; u I = f (R )---输⼊负载特性曲线。

对TTL 逻辑门,这五条特性曲线,输出低电平负载特性曲线和输出⾼电平负载特性曲线是反映输出端带负载能⼒的情况,输出⾼电平时,输出电流,即拉电流是向外流;输出低电平时,输出电流,即灌电流是向⾥流。

输出电流与逻辑门带负载的能⼒,⼯作速度有关,是重要的特性曲线。

XX大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)1.逻辑函数Y AB C=+的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

TTL门电路与CMOS门电路主要内容:TTL门电路与CMOS门电路的工作原理。

重点难点:TTL门电路与CMOS门电路的工作原理。

TTL 门电路与CMOS 门电路T 5YR 3R 5 A B CR 4R 2R 1 T 3T 4T 2+5VT 1输入级 中间级 输出级1. TTL 与非门电路(1) 电路E 2 E 3E 1 B 等效电路C多发射极三极管T 5Y R 3R 5A B CR 4R 2R 1T 3T 4T 2+5VT 11) 输入全为高电平 1 (3.6V)时(2) 工作原理4.3V T 2、T 5饱和导通钳位2.1V E 结反偏截止 0(0.3V)负载电流(灌电流)输入全高 1 输出为低 01VT 1R 1+U cc 3.6V 1T 5 Y R 3R 5AB CR 4R 2R 1T 3T 4T 2+5VT 1(2) 工作原理T 2、T 5截止负载电流(拉电流) (0.3V)1 0 输入有低 0 输出为高 11V 2) 输入端有任一低电平 0 (0.3V)流过 E 结的电流为正向电流5V V Y 5-0.7-0.7 =3.6V有 0 出 1全 1 出 0与非逻辑关系0 0 0 1 0 0 1 1 1 0 1 1 1 1 0 1 1 0 0 1 0 1 1 1 0 1 0 1 111ABYC 与非逻辑状态表 逻辑表达式: Y = A B C 与非 门Y&AB C74LS00、74LS20管脚排列示意图&&12 11109 814133 4 5 6 71 2 &&U CC 4 B 4 A 4 Y 3 B 3 A 3 Y1 B 1 A 1 Y2 B 2 A 2 Y GND(a)74LS001211109 814133 4 5 6 71 2 &&U CC 2 D 3 C 2 B NC 2 A 2 Y1 B 1 A NC 1 D 1 C 1 Y GND74LS20(b)1) 电压传输特性输出电压 U O 与输入电压 U I 的关系。

竭诚为您提供优质文档/双击可除与非门传输特性实验报告篇一:实验1与非门测试实验一TTL与非门的静态参数测试实验报告一、实验数据(一)1.低电平输出电源电流IccL和高电平输出电源电流Icch及静态平均功率??2.输入短路电流IIs和输入漏电流IIh3.输出高电平uoh及关门电平uoFF4.输出低电平uoL及开门电平uon((:与非门传输特性实验报告)二)测试TTL与非门的电压传输特性(三)平均传输延迟时间tpd由示波器测得T=96.00ns,于是??pd=波形如下:??14=9614≈6.8571.二、实验分析1.实验原理图图1测量低电平输出电源电流IccL图2测量高电平输出电源电流Icch图3测量输入短路电流IIs图4输入漏电流IIh图5输出高电平uoh及关门电平uoFF图6测量输出低电平uoL及开门电平uon图7测试TTL与非门的电压传输特性图8测量平均传输延迟时间tpd2.由实验(二)所得参数,运用matlab画出电压传输特性曲线。

uo(V)0.511.52ui(V)2.533.543.实验数据分析a低电平输出电源电流IccL为2.029mA,高电平输出电源电流Icch为0.674mA,且低电平输出电源电流IccL比高电平输出电源电流高,符合理论值。

b输入短路电流IIs为0.168mA,而输入漏电流IIh为微安级,由于仪器精度不够无法测出有效数据,示数为0mA,说明其前级门电路带负载的个数较多。

c由uoh,uoL,uoFF,uon四组数据得,74Ls00的跳变电压在1V左右,从0.955V~1.160V。

高电平为2.418V,低电平在0.330V,整体偏小,但在理论值范围内,说明实验箱内除74Ls00外的部分有一定分压。

d由实验(二)的电压传输特性曲线来看,在输入电压为低电平时,篇二:数字逻辑与数字系统实验报告二篇三:器件集成与非门电路参数的测试实验报告集成与非门电路参数的测试一、实验目的(1)TTL和cmos与非门的电压传输特性的测试(2)TTL 和cmos与非门的主要参数及测试方法二、实验器件(1)hbe硬件基础电路实验箱、双踪示波器、数字万用表(2)元器件:74Ls00、cD4011三、实验内容1.测试与非门74Ls00的电压传输特性测量电路原理如图所示,调节电位器Rw,使Vi从0V向5V变化,逐点测试Vi和Vo,列表记录Vi和Vo值。

实验二 TTL 与非门电路参数测试一、实验目的1.了解TTL 与非门参数的物理意义;2.掌握TTL 与非门参数的测试方法;3.了解TTL 与非门的逻辑功能。

二、实验原理TTL 门电路是一类功能齐全的逻辑电路,其参数可查阅有关参数手册;本实验介绍TTL 与非门常用参数测试。

7400是TTL 型中速二输入端四与非门。

图1为其内部电路原理图和管脚排列图。

1.与非门参数:开门电平V ON 、开门电阻R ON 、关门电平V OFF 、关门电阻R OFF 、平均传输延迟时间t pd2.与非门传输特性与非门的电压传输特性是输出电压VO随输出电压Vi变化的曲线,如图7:3.TTL与非门的逻辑特性:三、实验仪器1.示波器1台2.函数信号发生器1台3.数字万用表1台4.多功能电路实验箱1台四、实验内容1.测量输出高电平VOH 、输入开门电平VOFF、关门电阻ROFF:2.测量输出低电平VOL 、输入开门电平VON、开门电阻RON:表1 TTL 参数 参数 V OH V OL V ON V OFFR ONR OFFt pd测量值3.443V0.195V1.424V0.766V 2.755K Ω 1.011K Ω 7.900ns3.示波器测量方法:测量原理图如图16所示:表3 电压传输曲线参数参数 V OH V OL V ON V OFF 测量值3.89000V60.00mV1.39375V781.25mV4.平均传输延迟时间的测量: 测量电路如图17所示。

五、数据处理实验原始数据已记入表格。

表1中t pd 取2周期长度,测得t 1=10.800ns t 2=58.200nsT pd =6T=(t 2-t 1)/2/6=(58.200-10.800)/2/6=7.9000ns六、实验小结1.电压传输特性曲线如图:2.分析“与非门”的逻辑功能:与非门的逻辑功能是(1)当输入全为高电平时,输出低电平。

(2)当输入有低电平时,输出高电平。

TTL与非门的电压传输特性和主要参数TTL(Transistor-Transistor Logic)是一种数字电路逻辑家族,它使用发射极跟随(emitter-coupled)逻辑门设计。

在TTL电路中,基本的逻辑门是非门(NOT gate),由多个晶体管组成。

TTL电路的电压传输特性可以通过传输特性曲线来描述,该曲线表示输入电压与输出电压之间的关系。

TTL非门的传输特性曲线如下所示:Vcc(供电电压)______________,_______,_____________,__________Vout(输出电压), Vin(输入电压)在TTL电路中,当输入电压低于低电平门限(Low level input voltage)时,输出电压保持高电平状态;当输入电压高于高电平门限(High level input voltage)时,输出电压保持低电平状态。

因此,TTL电路的输入输出电压是离散的。

TTL电路的主要参数包括:1. 低电平门限(Low level input voltage):TTL电路中,输入电压低于该门限时,输出电压保持高电平状态。

2. 高电平门限(High level input voltage):TTL电路中,输入电压高于该门限时,输出电压保持低电平状态。

3. 高电平输出电流(High level output current):输出电压为高电平时,电路可以提供的最大输出电流。

4. 低电平输出电流(Low level output current):输出电压为低电平时,电路可以提供的最大输出电流。

5. 输入电阻(Input resistance):TTL电路对输入电压的接受能力,一般较高。

6. 输出电阻(Output resistance):TTL电路输出的电阻值,一般较低,可以驱动较大负载。

7. 延迟时间(Propagation delay):逻辑门输入的变化到输出的响应需要的时间,一般较短。

【例1】某TTL 与非门电压传输特性如图2-1 (a)所示,输入级电路如图2-1(b )所示;输出高电平时允许的最低高电平V V OH 4.2min =;输出低电平时允许的最高低电平V V OL 7.0max =。

图2-1(a) TTL 与非门电压传输特性 图2-1(b) TTL 与非门输入级电路(1)求该门的关门电平V off 和开门电平V on 各为多少?(2)当该TTL 与非门驱动同类负载门时,求输入高电平抗干扰容限V HN 和输入低电平抗干扰容限V LN ;(3)当该TTL 与非门有一个输入端接电阻R ,其余输入端悬空时,求该门的开门电阻R on 和关门电阻R off 。

解:(1)根据关门电平V off 的定义可知,V off 是使与非门保持关门状态的最大输入电压,从图2-1(a)所示电压传输特性可看出,当V V OH 4.2min =时所对应的输入电压为1.3V ,所以V V off 3.1=根据开门电平V on 的定义可知,V on 是使与非门保持开门状态的最小输入电压,从图2-1(a)所示特性图可看出,当V V OL 7.0max =时所对应的输入电压为1.5V ,所以V V on 5.1=(2)根据抗干扰容限的定义:与非门输入高电平抗干扰容限()V V V V V on OH HN 9.05.14.2min ===-- 与非门输入低电平抗干扰容限()V V V V V OL off LN 6.07.03.1max ===--(3)观察图2-1(b)所示,图中R 与R 1对电源V cc 构成分压器,R 上的降压V R 就成为该门的输入电压。

V R 为RR R V V V B cc R +-11=若V V on R ≥,则与非门输出低电平即处于开门状态,这时所对应的R 临界阻值就是开门电阻R on 。

所以V R R R V V on on ON B cc =+-11,V R R k V V on on5.131.25=+Ω- 求得Ω=k R on 2.3(若需该与非门输出低电平,则应使Ω≥k R 2.3)。

若V V off R ≤,则与非门输出高电平即处于关门状态,这时所对应的R 的临界阻值就是关门电阻R off 。

所以(a )与非门电路(b )与非门内部输入级图2-2 TTL 与非门电路及输入电路V R R R V V off off off B cc =+-11,V R R k V V off off3.137.05=+Ω- 求得Ω=k R off 3.1(若需该非门输出高电平,则应使Ω≤k R 3.1)。

注意:在上述两种情况下代入公式的V B 1值是不同的。

讨论与非门的开门状态时V B 1为2.1V ;讨论与非门的关门状态时V B 1为0.7V 。

【例2】TTL 与非门电路如图2-2(a)所示,TTL 与非门内部输入级电路如图2-2(b)所示,试问:(1)若使与非门输出1=F ,R 阻值应为多少?(2)若使与非门输出0=F ,R 阻值应为多少?解: (1)与非门内部输入级电流几乎全部流过外接电阻R ,设电阻上的压降为V R ,因为要求1=F ,即要求与非门处于关门状态,所以(设关门电平V V off 1=)应有下式成立:V R R R V V V off be cc R ≤⋅+-=11即 V R R k V V V R 137.05≤⋅+Ω-= 求得Ω≤k R 1。

(2)设电路刚接上电源时,流过R 1的电流仍然全部流过外接电阻R ,因为要求0=F ,即要求与非门处于开门状态,所以(设开门电平V V on 2=)应有下式成立:V R R k VV V on R ≥⋅+Ω-=37.05 即 V R Rk V V V R 237.05≥⋅+Ω-=求得Ω≥k R 6.2。

【例3】 电路如图2-3(a)、(b)、(c)、(d)所示,试找出电路中的错误,并说明为什么。

图2-3 电路图解 :图(a):电路中多余输入端接“1”是错误的,或门有一个输入为1,输出即为1。

图(b):电路中多余输入端接“0”电平是错误的,与门输入有一个为0,输出即为0。

图(c):电路中两个与门输出端并接是错误的,会烧坏器件。

因为当两个与非门的输出电平不相等时,两个门的输出级形成了低阻通道,使得电流过大,从而烧坏器件。

图(d):电路中两OC 门输出端虽能并接,但它们没有外接电阻至电源,电路不会有任何输出电压,所以是错误的。

【例4】 在图2-4中有两个接为线与的OC 门G 1、G 2。

它们的输出驱动三个基本TTL 门G 3、G 4、G 5,接入的输入端分别为2、2、3个。

设OC 门输出低电平时允许灌入的最大电流I OL 为14mA ,输出高电平时输出管截止的反向漏电流I OH 为0.25mA ;TTL 与非门的输入短路电流I IL 为1.6mA ,每个输入端的反向漏电流I IH 为0.05mA 。

试求外接负载电阻R L 的取值范围。

(要求V V V V OL OH 3.0,3≤≥。

) 解: 解题时要分OC 门输出是高电平和低电平两种情况。

(1)OC 门输出为高电平V OH此时流过电路中各种电流I R 、I OH 、I IH 的方向如图2-4(a)中箭头所示。

负载电阻R L 上的电流I R 为(a )OC 门输出为高电平 (b )OC 门输出为低电平图2-4 两个OC 门驱动三个与非门()()mA mA I I I IH OH R 85.005.0725.023222=⨯+⨯=+++= 因为R L 的增大会使输出高电平下降,所以R L 应为()Ω=-=-≤k mA VI V V R ROH cc L 35.285.035max 注意:在计算I R 时,对G 3、G 4、G 5 接入电路的每一个输入端的反向漏电流I IH 都要计算在内。

(2)OC 门输出为低电平V OL此时流过电路中各种电流I R 、I OL 、I IL 的方向如图2-4(b)中箭头所示。

负载电阻R L 上的电流I R 为 ()mA mA I I I IL OL R 2.96.13143=⨯-=-=由于R L 的减小会使输出低电平抬高,所以R L 应为()Ω=-=-≥5112.93.05min mA VI V V R ROL CC L故 Ω≤≤Ωk R L 35.2511注意:在计算I R 时,只考虑一个OC 的输出为低电平,因为这是输出低电平时还负载的最不利的情况。

同时G 3、G 4、G 5各个门的输入短电流I IL 的大小与接入电路的输入端个数无关。

【例5】 用增强型NMOS 管构成的电路如图2-5(a)所示。

试写出F 的逻辑式;并用NMOS管画出更加简化而逻辑功能不变的电路。

解: 解题时首先要分清哪些管子是负载管,哪些管子是开关管,只有在一个负载管的源极与开关管的漏极连接节点上才能输出倒相的逻辑函数。

该题电路图中只有T 1是负载管,其余的都是开关管。

在开关管中再看哪些是串接的,哪些是并接的。

对于相互串接的开关管,它们栅极上所加的变量互为与逻辑;对于相互并接的开关管,它们栅极上所加的变量互为或逻辑。

根据以上分析原则,可得函数()()D C B A AD AC B A F ++=++=所得简化电路如图2-5(b)所示。

(a )增强型NMOS 管构成的电路图 (b)简化后的NMOS 管构成的电路图图2-5 电路图思考题和习题解答【题2.1】解:判断TTL 与非门G 1、G 2何者为优,主要考查其重要参数: 与非门输出交电平时的抗干扰容限V V V on OH HN -=min 与非门输出低电平时的抗干扰容限V V V OL off LN max -=V V V ON OH HN 1min 1-=∴,V V V ON OH HN 2min 2-= V V V OL OFF LN max 11-=,V V V OL OFF LN max 22-=故:04.09.15.11221<-=-=-=-V V V V V V V ON ON HN HN V V HN HN 21<∴同理03.01.18.02121<-=-=-=-V V V V V V V OFF OFF LN LNV V LN LN 21<∴可见与非门G 1输出交电平时的抗干扰容限V HN 1及输出低电平时抗干扰容限V LN 1均分别低于非门G 2的V HN 2,故G 2优于G 1。

【题2.2】解:(a)电路中多余的输入端不应接到地,因为与门输入端有一个为0则输出为0,使输出Y 恒为1,无法实现AB Y =。

应将多余输入端接到高电平或任意一个输入端。

修改电路如图2-6(a )所示。

(b)电路中多余的输入端不应接U CC +,因为或门输入端有一个为1则输出为1,使输出Y 恒为0,无法实现B A Y +=。

应将多余输入端接到低电平或任意一个输入端。

修改电路如图2-6(b )所示。

(c)这种接法是错误的,当两个与非门输出电平不相等时,两个门的输出级形成低阻通道,使得电流过大,会烧坏器件。

修改电路如图2-6(c )所示。

(d)虽然一般来说TTL 或CMOS 门输出端不允许并接,但是如图所示接法是正确的,通常将几个相同输入的门电路输出端并接可以增大其驱动能力。

(e)电路中两个OC 门输出端应接上拉电阻至电源。

修改电路如图2-6(e )所示 (f)电路所体现的逻辑关系应为C B A C B A Y ⋅+⋅=,与给定逻辑关系不相符。

请注意:该题中的给定逻辑关系是没有意义的,也不符合三态门的使用规律。

图2-6 修改后的逻辑电路图【题2.3】解:(1)不考虑t pd 时,根据图(a)中逻辑关系B A B A Y +=⋅=,输出波形如图2-7(a)所示。

(2)考虑t pd 时,信号A 到达与非门输入端时的信号C (如图2-7(b)信号C )相对于A 存在3t pd 延时;而信号B 到达与非门输入端时的信号D (如图2-7(b)信号D )相对于B 存在t pd 延时,输出Y 的波形如图2-7(b) 信号Y 所示。

Y∙+U C C 10KΩ+U CC∙∙R【题2.4】 解:(1)(a)B AC B AC Y =+=1 (b)=⊕=B AC Y 2 C B A C B B A ++ (c)C B A C B A Y +=⋅=3(d)()C B A C B A C B A ABC Y ++++=⋅=)(4(2)首先根据上述逻辑函数,列出各输出函数的真值表如表2-1所示,根据表2-1依次画出各逻辑函数的波形图,如图2-8所示。

表2-1 真值表图2-8 题2.4 Y 1-Y 4波形图图2-7 题2.3输出波形(b) 考虑t pd 输出波形图可见,考虑t pd 后输出的逻辑关系发生了变化,这种影响到底有多大呢?在这里对输出波形作一个定量的分析。