verilog实现串并并串转换的代码和仿真结果

- 格式:doc

- 大小:183.50 KB

- 文档页数:15

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

并串/串并转换电路设计一、实验目的:用verilog语言设计一个8:1的并串转换电路、设计一个1:8的串并转换电路。

二、实验原理:实现8位的并行数据转换为串行的数据:并行转串行,只要把每个输入按从高到低的顺序输出即可。

即每个时钟脉冲输出一个数据。

实现8位的串行数据转换为并行的数据:8位串行数据转换为并行数据,需要一个模为8的计数器,当计到8个时钟脉冲时,把之前的8个数据全部输出,然后从新接收。

三、实验内容:用verilog实现8位的并行数据转换为串行的数据:module bingchuan(out,in,rst,clk);output out;reg out;input [7:0] in;input rst,clk;integer i=0;always@(posedge clk)beginif(rst)out<=0;elsebeginif(i==8)beginout<=0;endelseout<=in[i];i<=i+1;endendendmodulemodule textbingchuan;reg [7:0] in;reg rst,clk;wire out;bingchuan bc(out,in,rst,clk);initial clk=1;always #5 clk=~clk;initialbeginrst=1;#100 rst=0;in=8'b11101110;endendmodule仿真后的波形:用verilog实现8位的串行数据转换为并行的数据:module chuanbing(out,in,rst,clk);output [7:0] out;reg [7:0] out;input in,rst,clk;reg[7:0] temout;reg[2:0] cd;always@(posedge clk)beginif(rst)cd=3'b111;elsebegintemout[cd]<=in;cd<=cd-1'b1;if(cd==3'b111)beginout<=temout;endelseout<=8'bz;endendendmodulemodule textchuanbing;reg rst,clk,in;wire [7:0] out; chuanbing ch(out,in,rst,clk); initial clk =0;always#5 clk=~clk;initialbeginrst=1;#10 rst =0;in=1;#10 in=0;#10 in=1;#10 in=1;#10 in=0;#10 in=1;#10 in=0;#10 in=1;#10 in=1;#10 in=1;#10 in=0;#10 in=1;endendmodule仿真后的波形:。

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)Quartus Ⅱ8.1入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

快捷工具●快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

注意以下命名要一致。

第二步:新建工程(file>new Project Wizard)所建工程的1 工程名称:2第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b; assign out2=a | b; endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis ))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location 为您的输入输出配置引脚。

第七步:整体编译(工具栏的按钮(startComplilation))各个端口顶层某块的第八步:功能仿真(直接利用quratus 进行功能仿真)1 将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function )2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist )设置输入接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):观察波形,刚好符合我们的逻辑。

verilog有限状态机实验报告范文(附源代码)有限状态机实验报告一、实验目的进一步学习时序逻辑电路了解有限状态机的工作原理学会使用“三段式”有限状态机设计电路掌握按键去抖动、信号取边沿等处理技巧二、实验内容用三段式有限状态机实现序列检测功能电路a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。

b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如i.ii.输入:1101101101输出:0001000001c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次d)按键按下的瞬间将拨动开关状态锁存i.注意防抖动(按键按下瞬间可能会有多次的电平跳变)三、实验结果1.Rt_n为0时数码管显示0000,led灯不亮,rt_n拨为1,可以开始输入,将输入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1,0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入1101,LED灯亮2.仿真图像刚启动时使用rt_n一段时间后其中Y代表输出,即控制led灯的信号,el表示数码管的选择信号,eg表示数码管信号四、实验分析1、实验基本结构其中状态机部分使用三段式结构:2、整体结构为:建立一下模块:Anti_dither.v输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op这一模块实现思路是利用按钮按下时会持续10m以上而上下抖动时接触时间不超过10m来给向下接触的时间计时,达到上限时间才产生输出。

Num.v输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。

输出的num即为即将在数码管上显示的值Scan.v输入时钟信号,对其降频以产生1m一次的扫描信号。

Trigger.v这一模块即为状态机模块,按三段式书写。

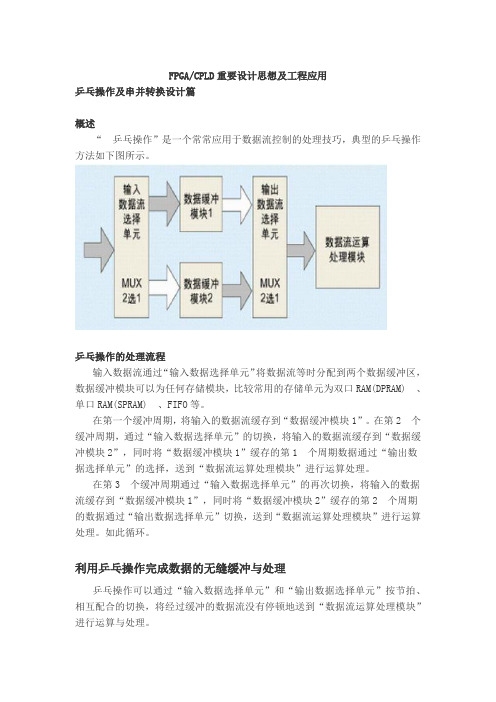

FPGA/CPLD重要设计思想及工程应用乒乓操作及串并转换设计篇概述“乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如下图所示。

乒乓操作的处理流程输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO等。

在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。

在第2 个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1 个周期数据通过“输出数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理。

在第3 个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2 个周期的数据通过“输出数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。

如此循环。

利用乒乓操作完成数据的无缝缓冲与处理乒乓操作可以通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。

把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。

所以乒乓操作常常应用于流水线设计中,完成数据的无缝缓冲与处理。

串并转换串并转换是FPGA 设计的一个重要技巧,它是高速数据流处理的常用手段,串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO 等实现。

若想数据的缓冲区开得很大,可以通过DPRAM 实现了数据流的串并转换,对于数量比较小的设计可以采用寄存器完成串并转换。

如无特殊需求,系统中应该用同步时序设计完成串并之间的转换。

1组合逻辑电路--基本门电路1.1基本门电路1.1.1结构化描述方式代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 and and_inst(oAnd,iA,iB);11 or or_inst(oOr,iA,iB);12 not not_inst(oNot,iA);1314 endmodule最底层的是门级原语and or not RTL级视图testbench如下View Code1 `timescale 1 ns/ 1 ns2 module logics_tb();34 reg ia;5 reg ib;67 wire oAnd;8 wire oOr;9 wire oNot;1011 initial12 begin13 ia=0;14 #40 ia=1;15 #40 ia=0;16 #40 ia=1;17 #40 ia=0;18 end1920 initial21 begin22 ib=0;23 #40 ib=0;24 #40 ib=1;25 #40 ib=1;26 #40 ib=0;27 end2829 logics logics_inst30 (31 .iA(ia),32 .iB(ib),33 .oAnd(oAnd),34 .oOr(oOr),35 .oNot(oNot)36 );3738 endmoduleRTL级仿真图形如下GATE级仿真图如下可见RTL级仿真是理想的,GATE级仿真考虑了延迟和信号开始的不确定。

1.1.2采用流描述方法代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 assign oAnd=iA&iB;11 assign oOr=iA|iB;12 assign oNot=~iA;1314 endmoduleRTL级视图,仿真图形同上。

作业二——串-并转换电路

一.实验内容:

实现一个串-并转换电路,当输入信号A为1时,串行输入D的值,输入4 bit之后,并行输出Z,同时DONT输出为1。

运用状态分析,共三个状态:state0,state1,state2。

设计testbench,检验输出波形。

二.实验代码:

1.修改的core代码如下:

2.设计的testbench代码如下:

其中,输入信号A和D是通过定义寄存器AM和DM,然后寻址获取数值。

a.给复位信号R,时钟信号CLK赋值代码:

b.给输入信号A和D赋值代码:

三.仿真波形

1.总的波形

分析:从这幅图中可以看出,当R=1时,所有的信号复位成0,状态为0,之后当A=1给出ready信号之后,开始串行读数,四个时钟周期后,将数值并行输出到Z,同时DONT变为1,回归状态0。

之后再次等待ready信号A=1,如此循环,实现串-并转换。

波形正确。

2.第一个并行输出放大波形:

分析:从这幅图中可以看出,当时钟上升沿读取到A=1,说明准备好读入D 的数值了,D分别为:1,0,1,1,四个时钟之后,Z并行输出1011,同时DONT输出为1,之后回归到状态0,重新开始准备读数。

3.第二个并行输出波形:

分析:这幅图中,当Z输出1011之后,下一个时钟上升沿,虽然D为1,A 也为1,但是由于此时刚读入状态为0,因此还没有开始读数,而是在下一个时钟沿时开始串行读入D,一次读入D为:0,0,1,1,所以最后输出不是1001,而是0011。

verilog之四位全加器的编译及仿真(⽤开源免费的软件——iverilog+GTKWave)四位全加器的verilog的代码⽐⽐皆是,这⾥上⼀个⽐较简单的:/*4位全加器全加器需要有输⼊输出,需要有下级向上进位的输⼊,需要有向上⼀位进位的输出。

⼤家看⼀下,这个模块已经包含全部的输⼊输出信息。

⼤家都知道,N位加法器得出来的出来的和最多是N+1位因此可以清晰从下⾯代码中看到相关信息。

然后assign⽤的是阻塞赋值。

相加即满⾜相关的需求。

*/module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule在写testbeach⽂件之前,先普及⼀点testbeach的知识:⼀般来讲,在数据类型声明时,和被测模块的输⼊端⼝相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进⾏赋值;和被测模块输出端⼝相连的信号定义为wire类型,便于进⾏检测。

Testbench模块最重要的的任务就是利⽤各种合法的语句,产⽣适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach⽂件如下:/*File Name : test_adder4.vDescription : The testbench of the adder_4.vWritten By : LiMingData : 2011/04/18 20:13modefied : 在仿真的时候,把延时从10ns改为5ns: cout显⽰为2位*///test_adder4 (top-level module)`timescale 1ns/1nsmodule test_adder4;//Declare variableswire[3:0] sum;wire cout;reg[3:0] ina,inb;reg cin;//Instantiate the module adder4adder4 adder4_1(cout,sum,ina,inb,cin);//Stimulate the inputs, Finish the stimulation at 90 time unitsinitialbegin#0 ina = 4'b0001; inb = 4'b1010; cin = 1'b0;#5 ina = 4'b0010; inb = 4'b1010; cin = 1'b1;#5 ina = 4'b0010; inb = 4'b1110; cin = 1'b0;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0111; inb = 4'b1001; cin = 1'b0;#5 ina = 4'b0001; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b0;#5 ina = 4'b0111; inb = 4'b1111; cin = 1'b1;#5 $finish;endinitial$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);initialbegin$dumpfile("test.vcd");$dumpvars(0,test_adder4);endendmodule由于是在windows的cmd下进⾏命令⾏的运⾏,所以有时候每次输⼊⼀个命令显得很费时间,所以我这⾥⼜写了⼀个(批处理⽂件)bat⽂件:go.batECHO OFFECHO *********************************ECHO * Batch fileECHO *********************************ECHO *ECHO ONiverilog -o test adder4.v test_adder4.vvvp -n test -lxt2cp test.vcd test.lxtgtkwave test.lxt(说明⼀下,我在windows下安装了gnuwin的软件,即能在windows下⽤gnu的⼀些⼩的实⽤的⼯具!)哈哈,这⾥就可以⼀键运⾏了,上⾯的⼀些命令的解释可以到我的“wndows下如何⽤Iverilog+GTKWave进⾏verilog的编译和查看仿真波形”的博⽂⾥去看看吧。

fpga串并转换代码摘要:1.FPGA 简介2.串并转换的概念3.FPGA 实现串并转换的方法4.串并转换代码实例5.总结正文:一、FPGA 简介FPGA(现场可编程门阵列)是一种集成电路,用户可以通过编程配置其内部的逻辑门和连线,从而实现特定的功能。

FPGA 具有高度的灵活性和可重构性,广泛应用于数字信号处理、通信、图像处理等领域。

二、串并转换的概念串并转换,顾名思义,是指将串行数据转换为并行数据,或者将并行数据转换为串行数据。

这种转换在数据传输和处理过程中具有重要意义,可以有效地提高数据传输的效率和降低硬件复杂度。

三、FPGA 实现串并转换的方法在FPGA 中实现串并转换,通常采用以下两种方法:1.使用查找表(LUT):通过编程配置查找表,将输入的串行数据转换为对应的并行数据。

2.使用串行到并行转换器(S/P 转换器):这是一种硬件电路,通过移位寄存器和逻辑门实现串行数据到并行数据的转换。

四、串并转换代码实例下面以查找表方法为例,给出一个简单的FPGA 串并转换代码实例。

假设输入串行数据为3 位,需要转换为8 位并行数据。

首先,我们需要配置一个3 位到8 位的查找表。

在Verilog 中,可以这样编写:```verilogmodule s_to_p_conv(input wire clk, input wire rst_n, input wire [2:0] s_in, output reg [7:0] p_out){reg [7:0] lut [7:0];integer i;always @(posedge clk or negedge rst_n)beginif (!rst_n)for (i = 0; i < 8; i = i + 1)lut[i] <= 8"b0;elsefor (i = 0; i < 8; i = i + 1)lut[i] <= s_in[i];endassign p_out = lut[s_in[2:0]];endmodule```在上述代码中,我们定义了一个名为s_to_p_conv 的模块,输入信号包括时钟信号clk、复位信号rst_n、输入串行数据s_in,输出并行数据p_out。

电子科技大学ASIC课程设计报告二学号:201222240937 姓名:周恒课题题目:交换网络32路复用模块设计2013年5月题目要求Develop, verify (before and after synthesis), and synthesize a Verilog module that encapsulates the functionality shown in Fig.2, where the outputs of the A/D converters are inputs to a module that interleaves the sample bytes, with separate sub-modules for the control unit, the mux, the demux, the parallel to serial converter, and the serial to parallel converter. Define additional interface signals as needed to complete the design. Model the multiplexer so that its outputs will be registered. Carefully document your work.图1-2 一个简单的交换控制系统组成本次设计的主要内容为交换网络复用与解复用模块,在下文做出详细设计,包括设计规格书、设计框图、仿真波形和设计结论。

一、设计框图整个系统由5个模块组成,其顶层模块如下图所示:1.控制模块:用于对整个系统的控制,包括复用控制,串并转换控制,并串转换控制和解复用控制。

2.复用模块:对32路输入数据进行复用,依次输入系统。

3.并串转换模块:将8bit的并行数据转换为串行数据。

4.串并转换模块:将对应的串行数据转换为并行数据。