基于门控时钟的CMOS电路低功耗设计

- 格式:pdf

- 大小:112.20 KB

- 文档页数:4

门控时钟低功耗芯片设计方案全文共四篇示例,供读者参考第一篇示例:门控时钟低功耗芯片设计方案随着物联网技术的飞速发展,原本以人类为中心的智能家居和智能办公等应用场景也逐渐普及,门控时钟低功耗芯片成为这些智能设备的重要组成部分。

门控时钟低功耗芯片设计方案要求具有高性能、低功耗、稳定可靠等特点,以满足现代智能设备对芯片性能的需求。

1. 高性能:门控时钟低功耗芯片需要具有高性能的时钟控制功能,能够对设备的时序信号进行准确控制,确保设备的正常运行。

2. 低功耗:门控时钟低功耗芯片需要具有低功耗的特点,以延长设备的使用时间,提高设备的续航能力。

3. 稳定可靠:门控时钟低功耗芯片需要具有稳定可靠的性能,能够在各种工作环境下保持稳定的工作状态,确保设备的正常运行。

4. 外设接口丰富:门控时钟低功耗芯片需要具有丰富的外设接口,以支持设备与其他外部设备的连接和通讯。

5. 易集成:门控时钟低功耗芯片需要具有易于集成的特点,能够方便地与其他组件进行接口连接,实现功能的扩展和定制。

1. 芯片选用:在选择芯片时,可以考虑采用低功耗的CMOS工艺制程,以降低整体功耗。

可以选择具有高性能和稳定可靠性的时钟控制器芯片,以确保时序信号的准确控制。

2. 功耗优化设计:在芯片设计过程中,可以采用功耗优化设计策略,通过降低功耗模块的工作频率、优化电源管理电路等方式,降低整体功耗,延长设备的续航时间。

3. 时钟控制算法优化:通过优化时钟控制算法,可以提高时钟控制的准确性和稳定性,确保设备的正常运行。

可以提供丰富的时序控制功能,以满足不同应用场景对时序信号的需求。

4. 外设接口设计:在芯片设计中,可以设计丰富的外设接口,如UART、SPI、I2C等接口,以支持设备与其他外部设备的连接和通讯。

可以提供GPIO接口和PWM输出等功能,实现设备的功能扩展和定制。

5. 集成设计:在芯片设计中,可以将时钟控制器、功耗管理电路、外设接口等功能集成到同一芯片中,实现功能的集成和有效管理。

ASIC低功耗设计三、低功耗技术1. 功耗分析(1)由于电容的充放电引起的动态功耗V C l i VDDv out图(20)充放电转换图如图(20)所示:PMOS 管向电容LC 充电时,电容的电压从0上升到DDV ,而这些能量来自于电源。

一部分能量消耗在PMOS 管上,而剩余的则保存在电容里。

从高电压向低转换的过程中,电容放电,电容中储存的能量消耗在NMOS 管上。

我们来推导一下:考虑从低电压转换到高电压的情况,NMOS 和PMOS 不同时导通。

在转换过程中电源提供的能量为CE ,而是转换后储存在电容里的能量。

⎰⎰⎰====∞∞VDD DD L out DD L out L DD VDD VDD V C dv V C dt dt dv C V dt t i E 0002)( ⎰⎰⎰====∞∞VDD DD L out out L out out L out VDD C V C dv v C dt v dt dv C dt v t i E 02002)(这两个等式说明电源提供的能量只有一半储我们来计算在翻转周期的能量消耗:peak DD sc sc peak DD sc peak DD dp I V t t I V t I V E ==+22 我们计算平均能量消耗f V C f I V t P D D sc peak D D sc dp 22==V V in V outC L I SC图(21)短路电路示意图短路电流的功耗同电路的翻转率是成正比,sc t 表示器件同时导通的时间, peakI 由器件的饱和电流决定,因此正比于晶体管的尺寸。

峰值电流是输入和输出斜率比率的函数。

其原因说明如下:静态CMOS 反向器的输入从0变化到1,假设负载电容非常大,因此输出信号的下降时间比输入信号的上升时间长得多。

在这种情况下,在输出信号变化以前,输入信号已经完成了瞬态变化,因此NMOS 已经导通,但是输出电容来不及放电。

集成电路的低功耗设计研究与实现近年来,随着智能家居、物联网和移动设备的快速发展,对集成电路的低功耗设计需求越来越大。

低功耗设计不仅能延长电池寿命,降低设备散热难度,还有助于降低使用成本。

因此,如何进行集成电路的低功耗设计研究与实现,成为了当今电子行业的热门话题。

一、低功耗设计的原理和方法低功耗设计通常采用一系列技术,包括时钟门控、可变电压和频率、电源管理、节能睡眠模式等。

其中,时钟门控是最常用的一种技术。

它通过控制时钟信号,使处理器在非必要的时候停止运行或运行在更低的频率,从而降低功耗。

同时,可变电压和频率技术也是一种精细的节能技术,它能根据实时需求动态地调整电压和频率,从而显著降低功耗。

电源管理和节能睡眠模式也是应用广泛的低功耗技术。

电源管理把所有不必要的电路部件关闭,从而降低功耗。

节能睡眠模式则是把系统所有不必要的部件都关闭,这样设备就能进入极低功耗模式。

当需要使用的时候,设备就能快速地从休眠模式中恢复过来,大大降低功耗。

二、低功耗设计的实现集成电路的低功耗设计实现需要在硬件、软件和系统级别上进行协同。

其中,硬件的设计是实现低功耗的基础。

硬件设计要充分考虑电源管理、时钟门控、处理器架构等因素,优化电路功耗,从而实现低功耗要求。

软件设计则是实现低功耗的重要手段。

软件能够控制硬件设备的工作状态,实现功耗的控制。

因此,在软件编程中,应该尽量采用高效的算法和代码打造严谨的逻辑,减少不必要的复杂度,从而降低功耗。

另外,系统级别协同也是实现低功耗的必备条件。

在系统设计中,应该合理安排硬件和软件的协同工作,实现低功耗的目标。

例如,在实现设备的休眠模式时,需要在系统软件层面保留必要的数据和状态,以便快速恢复系统。

三、低功耗设计的未来发展目前,集成电路的低功耗设计已经得到了广泛应用,但是,随着新技术的不断涌现,低功耗设计仍有很大的发展空间。

在新一代通讯技术的推动下,如5G通讯、物联网和智能家居等,低功耗设计将会更加重要。

低功耗CMOS电路设计与优化在当今的电子世界中,低功耗设计已成为集成电路发展的关键需求。

从智能手机到物联网设备,从医疗设备到航空航天,几乎所有的电子系统都在追求更低的功耗以延长电池寿命、提高系统稳定性和可靠性。

CMOS(Complementary MetalOxideSemiconductor)电路作为现代集成电路的主流技术,其低功耗设计与优化具有极其重要的意义。

一、低功耗设计的重要性随着电子设备的广泛应用和功能的不断增强,功耗问题日益凸显。

高功耗不仅会导致电池续航时间缩短,增加设备充电的频率,给用户带来不便,还会产生过多的热量,影响芯片的性能和可靠性。

在一些对功耗要求极为苛刻的应用场景,如植入式医疗设备和无线传感器网络中,有限的能源供应使得低功耗设计成为系统能否正常运行的关键因素。

此外,随着集成电路工艺的不断进步,器件尺寸不断缩小,漏电功耗逐渐成为不可忽视的一部分。

因此,降低功耗不仅可以节省能源,还能降低系统的散热成本,提高芯片的集成度和性能。

二、CMOS 电路功耗的来源要实现低功耗 CMOS 电路设计与优化,首先需要了解功耗的来源。

CMOS 电路的功耗主要包括动态功耗和静态功耗两部分。

动态功耗是在电路工作时,由于对负载电容充放电而产生的功耗。

它由开关功耗和短路功耗组成。

开关功耗是由于电容的充放电引起的,与工作频率、电源电压和负载电容大小成正比。

短路功耗则是在输入信号转换期间,PMOS 和 NMOS 管同时导通时产生的瞬间短路电流引起的功耗。

静态功耗主要包括漏电流引起的功耗。

随着工艺尺寸的缩小,亚阈值漏电流和栅极漏电流显著增加,导致静态功耗在总功耗中的比例逐渐上升。

三、低功耗 CMOS 电路设计技术1、电源电压缩放降低电源电压是降低功耗最直接有效的方法之一。

因为动态功耗与电源电压的平方成正比,所以适当降低电源电压可以显著减少动态功耗。

然而,降低电源电压会导致电路性能下降,如延迟增加。

因此,需要在功耗和性能之间进行权衡。

3—8译码器低功耗设计

1.选择合适的器件:在低功耗设计中,需要选择功耗较低的器件。

例如,使用CMOS工艺制造的器件比使用BJT工艺制造的器件功耗更低。

2.优化电路结构:在电路设计中,可以采用一些优化措施来降低功耗。

例如,使用寄存器代替门电路,减少门电路的数量和复杂度;使用异或门代替与门和或门等。

3.降低电源电压:在低功耗设计中,可以通过降低电源电压来减少功耗。

例如,可以使用低压差线性稳压器(LDO)来降低电源电压。

4.优化时钟频率:在低功耗设计中,可以通过优化时钟频率来减少功耗。

例如,可以使用低功耗定时器来控制时钟频率。

5.使用低功耗模式:在低功耗设计中,可以使用一些低功耗模式来降低功耗。

例如,可以使用待机模式、睡眠模式等。

综上所述,3-8译码器的低功耗设计需要综合考虑以上几个方面,以实现高效的低功耗设计。

电路设计流程如何降低功耗与能耗电路设计在现代科技应用中起着举足轻重的作用,为了提高电路性能和延长电池寿命,降低功耗和能耗是一个非常重要的课题。

本文将介绍几种降低功耗和能耗的常用电路设计流程。

一、优化电路结构电路结构的优化是降低功耗和能耗的基础。

通过分析电路需求和性能指标,合理设计电路结构,可以达到最优的功耗与能耗比。

一些常见的优化方法包括:1.1 降低电压:在不影响电路功能和性能的前提下,尽可能降低电压水平。

电路工作时,功耗与电压的平方成正比,因此适当降低电压可以有效降低功耗和能耗。

但要注意,降低电压可能会引起电路稳定性等问题,需要综合考虑。

1.2 升级器件:选择低功耗和高效能的器件是降低功耗和能耗的重要手段。

比如,使用低功耗的微处理器、低压差线性稳压器等器件,可以显著降低功耗。

此外,优化电路中的晶体管结构和材料选择等也能改善器件性能。

1.3 电源管理:合理的电源管理非常重要。

采用动态电压调整等技术,根据系统需求动态调整供电电压,可以在保证性能的同时节省能耗。

二、功耗优化技术除了优化电路结构,还可以采用一些特殊的技术来降低功耗。

以下是一些常见的功耗优化技术:2.1 动态电压频率调整(DVFS):动态电压频率调整是基于电路的工作负载情况动态调整供电电压和频率,从而降低功耗。

在低负载情况下,降低电压和频率,以减少供电能耗;在高负载情况下,提高电压和频率,以保证电路性能。

2.2 时钟门控:通过时钟门控技术,可以只在需要的时候打开电路,减少非必要的功耗。

比如,在处理器的空闲状态下关闭一些不必要的时钟信号和功能模块。

2.3 电源管理:通过采用开关电源等高效能的电源管理方案,可以提高能量转换的效率,减少功耗损耗。

三、能耗优化技术除了功耗优化技术,还有一些专门用于降低能耗的技术。

以下是一些能耗优化技术:3.1 休眠模式:在电路不工作或者处于空闲状态时,将电路切换到休眠模式,以提高能耗效率。

在休眠模式下,关闭不必要的电源和电路,减少能耗。

《系统级芯片(SoC)设计》课程思政案例(一)教学设计:《系统级芯片(SoC)设计》课程在大四第一学期讲授,教学过程中遇到如下问题:(1)课程难度较高,与考研复习冲突,在学习过程中,学生存在较大的畏难情绪,学习的内生动力不足;(2)课程需要用到学生前三年学习的基础知识,但由于各部分内容分散在不同时间段,学生综合运用这些理论知识解决复杂工程问题的能力不强;(3)为追求学业成绩,大部分学生陷于理论知识的学习,参与实践的意愿不强烈,动手实践和创新能力较弱。

根据《系统级芯片(SoC)设计》的课程特点,在课堂讲授、实验、课后作业、课程设计大作业等环节,从系统级芯片的世情、国情、行情以及设计方法论等层面,深入挖掘课程的思政元素,建设课程思政案例5个,拓展专业课程的广度和深度,教学设计形成以下特色:(1)充分结合中美贸易战、芯片“卡脖子”的时事以及集成电路产业链现状分析,激发学生的学习兴趣与科技报国的家国情怀和使命担当。

(2)以解决系统级芯片设计面临的挑战为主线,分析研讨设计技术的原理,把设计方法论和科学精神的培养结合起来,提高学生正确认识问题、分析问题和解决问题的能力。

(3)在课堂教学和实验环节,融入国内外系统级芯片设计技术的最新进展,在增强民族自豪感的同时,意识到精益求精的重要性,培养学生的工匠精神。

(4)校企协同,将华为课程资源--昇腾310 AI推理SoC作为案例,介绍SoC架构的特点,使学生切身体会到我国集成电路行业的先进技术。

(一)案例名称:SoC低功耗设计(二)案例教学目标理解CMOS电路的功耗来源,掌握低功耗设计技术的原理;了解国内外超级计算机的发展现状,使学生感受我国科技和经济实力的快速发展,增强民族自豪感,培养精益求精的工匠精神。

(三)案例教学实施过程第一节概述为了讲解低功耗技术,首先让学生了解针对不同的应用领域(超级计算机/数据中心,消费类电子设备,移动电子设备,生物芯片等),芯片功耗的区间不同,低功耗的概念是相对的。

门控时钟低功耗芯片设计方案

门控时钟是数字电路中常见的一个模块,它用于控制数据在不

同部件之间的传输和处理。

在低功耗芯片设计方案中,门控时钟的

设计是至关重要的。

首先,我们需要考虑选择合适的门控时钟电路,以确保在低功耗的同时能够稳定地控制数据传输。

一般来说,采用

低功耗的CMOS技术设计门控时钟电路是一个不错的选择,因为CMOS技术具有低静态功耗和高抗干扰能力。

其次,我们需要考虑如何优化门控时钟的工作模式以降低功耗。

这可能涉及到采用动态频率调整、睡眠模式和快速唤醒等技术,以

确保在需要时能够提供足够的性能,而在空闲时能够最大限度地降

低功耗。

另外,对于低功耗芯片设计方案来说,还需要考虑如何合理规

划整个芯片的电源管理。

门控时钟电路需要与其他模块协同工作,

因此在设计时需要考虑到整个芯片的功耗分配和管理,以确保门控

时钟在低功耗的同时能够满足整个芯片的需求。

此外,还有一些其他的技术可以用于降低门控时钟的功耗,比

如采用多级时钟缓冲器来降低时钟信号的传输功耗,采用时钟门控

技术来实现局部时钟门控等。

总的来说,低功耗芯片设计方案中的门控时钟设计涉及到多个方面,包括选择合适的电路技术、优化工作模式、合理规划电源管理等。

在实际设计中,需要综合考虑这些因素,以实现低功耗和稳定性的平衡。

低功耗设计论文(5篇)低功耗设计论文(5篇)低功耗设计论文范文第1篇关键词:低功耗;SoC;CMOS;功耗估量;The Application of Low-Power Methods in SoC DesignAbstract: SOC design occupies an important position in IC design market. The low-power design is an important part in SoC design process. This paper firstly gives a comprehensive analysis of the composed of CMOS circuit power consumption and the related theory of power estimation, then analyzes the SoC low-power design theory of various design levels in detail.Keywords: low-power,SoC,CMOS,power estimation1引言随着工艺水平的不断进展,集成电路设计已经进入超深亚微米(Deep Sub-Micron,DSM)和纳米的SoC时代,设计规模越来越大,单一SoC芯片的集成度已经达到了上亿门。

在之前的集成电路设计中,设计者首要关怀的芯片性能往往是面积与速度,然后才是功耗。

到了深亚微米阶段,功耗设计在芯片设计中所占的比重开头上升到与面积和速度同等重要的程度,设计人员需从功耗、性能和成本三者之间取得折衷。

据统计数据分析,目前市场上的一些功能强大的微处理器芯片功耗可达100-150 W,平均功耗密度可达50-75 W/cm2。

而芯片上某些热点(hot spots)的功耗更是数倍于这一数值。

功耗问题的重要性在便携式数码产品芯片的设计中显现的尤为突出。

基于65nm CMOS工艺的低功耗触发器设计的开题报告概述本文的研究重点在于设计一种基于65nm CMOS工艺的低功耗触发器,旨在降低功耗和提高性能。

触发器是数字电路的基本组成部分,而低功耗是现代技术发展的趋势,因此在这个背景下进行触发器设计具有重要意义。

本文的主要内容包括:介绍触发器的基本原理和工作方式;分析低功耗触发器的设计原则和常见的低功耗技术;阐述基于65nm CMOS工艺的设计流程和注意事项;设计并仿真一种低功耗触发器,并对其性能进行评估和分析;最后进行结论,总结本文的研究成果和展望未来的研究方向。

研究背景和意义随着电子技术的不断发展,芯片的集成度越来越高,功耗也越来越大。

如何在保证性能的前提下降低功耗,成为一个重要的研究课题。

低功耗触发器作为数字电路的基本组成部分之一,对于整个芯片的功耗和性能具有重要的影响。

目前,常见的低功耗技术包括时钟门控和数据保持技术等。

时钟门控技术是通过控制时钟的传播来降低功耗,而数据保持技术则是通过控制电路时序来实现单元状态的保持和变化。

此外,近几年还涌现出一些新型的低功耗技术,如分数时钟技术和混合式技术等。

设计基于65nm CMOS工艺的低功耗触发器,是在这个背景下进行的一项实际应用研究。

目前,65nm CMOS工艺已经广泛应用于数字电路和集成电路的设计和制造中,具有功耗低、速度快和稳定性高等优点。

因此,研究如何在这一工艺下设计低功耗触发器,具有现实意义和广泛应用价值。

研究内容和方法本文的研究内容主要包括以下几个方面:1. 触发器的基本原理和工作方式:介绍触发器的基本原理和工作方式,探讨触发器设计的基本要求和设计方法。

2. 低功耗触发器的设计原则和常见的低功耗技术:分析低功耗触发器的设计原则和常见的低功耗技术,包括时钟门控技术、数据保持技术、分数时钟技术和混合式技术等。

3. 基于65nm CMOS工艺的设计流程和注意事项:介绍基于65nm CMOS工艺的设计流程和注意事项,包括器件选型、电路设计和仿真等方面。

低功耗电路设计与优化在如今电子设备快速发展的时代,低功耗电路设计与优化成为了一个重要的课题。

随着移动设备的普及和人们对能源效率的关注,设计低功耗电路不仅能延长设备的续航时间,还能减少能源消耗,降低对环境的影响。

本文将重点介绍低功耗电路设计的原理和方法,并探讨相关的优化技术。

低功耗电路设计的原理主要包括降低动态功耗和静态功耗两个方面。

动态功耗是指在电路中由于信号的切换而产生的功耗,而静态功耗则是指电路处于稳定状态时产生的功耗。

针对动态功耗,一种常用的方法是采用时钟门控技术,即只在需要的时候打开电路的开关,而在其余时候保持关闭状态。

这样可以有效地降低功耗。

另外,还可以采取电压缩放和频率分析等技术,通过减小电压或者降低频率来降低功耗。

对于静态功耗,常用的方法是采用体效应和自适应电源技术,通过降低门极电流和切断逆变器上的漏电流来降低功耗。

除了降低功耗的原理外,设计低功耗电路还需要考虑相关的优化技术。

一种常见的优化技术是通过优化电路结构来提高功耗效率。

例如,采用模拟前馈技术可以减小电路中的失真,从而提高功耗效率。

另外,还可以通过选择合适的器件和材料来提高功耗效率。

选取具有低阻抗和高频率特性的器件可以降低信号的传输损耗,提高功耗效率。

此外,对于集成电路的设计来说,还可以通过布线优化和电流平衡等技术来提高功耗效率。

在实际应用中,低功耗电路设计与优化涉及多个领域,在不同的应用场景下会有不同的需求和方法。

例如,在移动设备领域,对于续航时间的要求较高,因此需要更加注重动态功耗的降低。

而在物联网领域,由于节点数量较多,对于功耗的限制更加严格,因此需要更加注重静态功耗的降低。

在数字电路设计中,通常采用逻辑优化和时序优化来实现低功耗设计。

在射频电路设计中,则需采取专门的射频优化技术来降低功耗。

综上所述,低功耗电路设计与优化是当今电子设备发展中的重要环节。

通过降低动态功耗和静态功耗,采用优化技术和合适的方法,可以有效提高电路的功耗效率,延长设备续航时间,减少能源消耗。

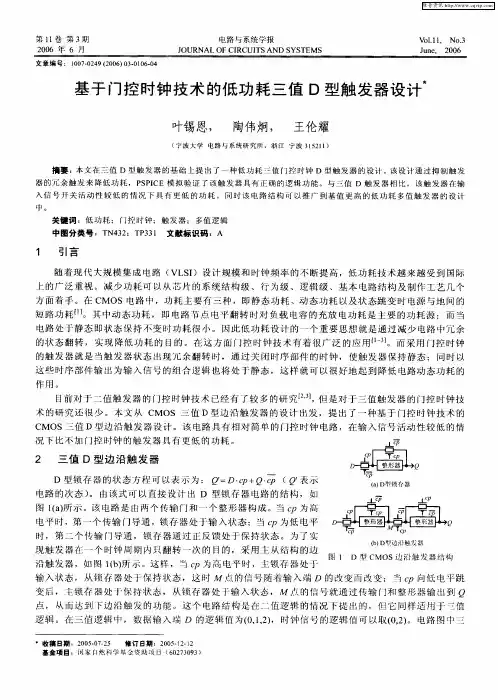

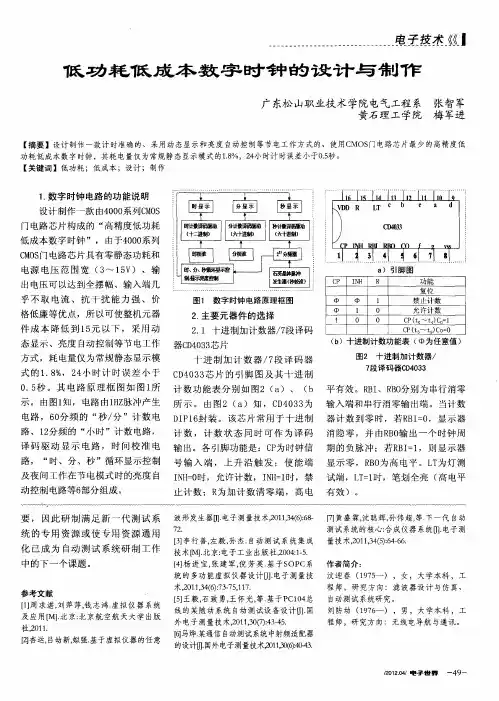

基于门控时钟的C MOS 电路低功耗设计罗 罹(安徽大学计算机科学与技术学院,安徽合肥 230039)摘 要:阐述了如何运用门控时钟来进行C MOS 电路的低功耗设计。

分析了门控时钟的实现方式,如何借助E DA 工具在设计中使用门控时钟,并且附有部分脚本程序,以一个watchdog ti m er模块为例,给出了相关的功耗分析报告和优化结果。

这样,可以借助E DA 工具的帮助,在综合时插入门控时钟,较大幅度地降低功耗,同时附带减小面积,为使用门控时钟进行低功耗设计者提供有益的参考。

关键词:低功耗;门控时钟;泄漏中图分类号:T N431.2 文献标识码:A 文章编号:1000-2162(2005)03-0021-04通常在C MOS 电路设计中,面积和速度是最为重要的性能指标。

目前,随着嵌入式设备和手持设备的普及,由于电池的大小和重量的限制,决定了电池的供电量有限,因此降低功耗成为很紧迫的问题。

设备功耗中的很大一部分是采用C MOS 工艺设计的芯片所引起的。

因此,降低C MOS 电路的功耗很有意义,功耗也成为C MOS 电路设计中一个重要的性能指标。

C MOS 电路的低功耗设计的概念和方法学应运而生,成为目前超大规模集成电路设计中的一个重要方向。

C MOS 电路的低功耗设计有很多方法,主要有:降低供电电压、使用门控时钟等。

但是降低供电电压,会带来很多副作用:首先,降低供电电压,会导致速度下降,减小电容充放电的电流或负载驱动电流;其次,会导致较低的输出功率或较低的信号幅度,从而产生噪声和信号衰减的问题。

相比之下,门控时钟是一个很有效的方法。

门控时钟可以有效地对某些较少使用的时序逻辑进行开关控制,从而大大降低功耗[1]。

本文将以一个watchdog ti m er 模块为例,使用Synop sys 公司的综合工具DesignComp iler,详细阐述如何在设计中插入门控时钟,并且给出了使用的脚本,通过详细的分析报告,特别是使用门控时钟前后的功耗对比,相信可以为工程师使用门控时钟进行低功耗设计提供有益的参考。

1 功耗和门控时钟的的基本概念1.1 功耗的基本概念电路中耗散的能量可以分为静态功耗(static power )和动态功耗(dyna m ic power )。

静态功耗的主要原因是:晶体管中从源到漏的亚阈值泄漏(subthreshold leakage ),就是指阈值电压的降低阻止了栅的关闭。

动态功耗分为开关功耗(s witching power )和内部功耗(internal power )。

开关功耗是由于器件的输出端的负载电容的充放电引起的。

负载电容包括了门和线的电容。

内部功耗指在器件内部耗散的能量,主要由瞬时短路所引起的。

1.2 门控时钟的的基本概念通常,门控时钟的实现方式有4种:基于“与”门、基于“或”门、基于触发器和基于latch 。

以图1中基于latch 的门控时钟为例,基于latch 的门控时钟的实现原理是:在cl ock 为高电平时latch 不会锁存数据,在cl ock 的上升沿捕获enable 信号。

特别需要注意的是,门控时钟的使用可能会带来时序上的问题。

特别当集成电路的设计已经进入深亚微米级时代,线延时占据了总延时的70%。

以基于latch 的门控时钟为例,布局收稿日期:2005-03-18作者简介:罗 罹(19812),男,安徽黄山人,安徽大学助教,中国科技大学硕士研究生.2005年5月第29卷第3期安徽大学学报(自然科学版)Journal of Anhui University Natural Science Editi on May 2005Vol .29No .3布线之后,对应的latch 和寄存器可能会距离很远,造成它们之间的连线延时过大,时序就可能不满足图1 基于latch 的门控时钟要求。

因此,采取的方法是将对应的latch 和寄存器整合在一起,作为一个标准单元来使用。

这样,可以保证的时序满足要求(此时的set_cl ock_gating_style 的设置将会不同)。

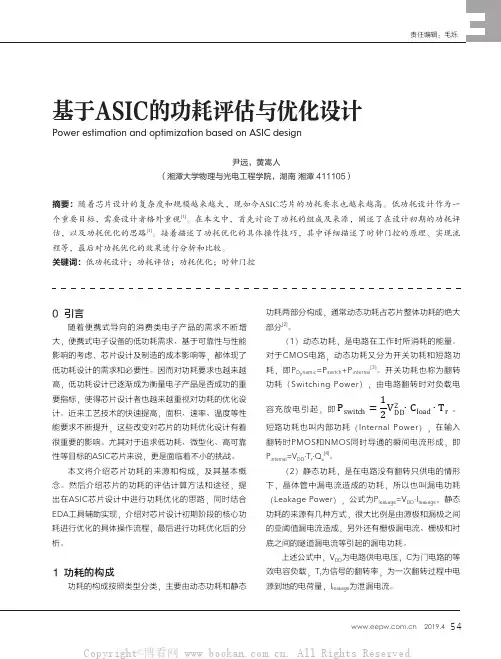

2 在设计中使用门控时钟本文首先给出了综合时使用的脚本,以实际中的一个设计生成的报告文件为例,对比了使用门控时钟前后的面积、时序、功耗方面的差别。

2.1 运行的脚本一般可以采用全定制(full -cust om )的设计方法,手工绘制电路图,确定设计中是否采用门控时钟。

但随着设计规模的日益增大,必须要借助E DA 工具的帮助。

在脚本中可以很灵活地对设计进行如下方面的控制:(1)时钟的实现方式:基于“与”门、基于“或”门、基于触发器、基于latch;(2)“使能”端(enable )进行SET UP 、HOLD 检查;(3)对特定的signal 是否使用门控时钟;(4)门控时钟的最大扇出;(5)是否插入scan 信号。

使用Synop sys 公司的综合工具Design Compp iler,该综合工具支持在设计中使用门控时钟,并可以进行相应的时序分析和功耗分析[2~4]。

下面给出使用Design Comp iler 进行综合时部分脚本:set_cl ock_gating_style -sequential_cell latch -positive_edge_l ogic {and}-negative_edge_l ogic {or}/3基于latch 的门控时钟,如果从工艺库中调用已经做好的具有门控时钟功能的标准单元,对应选项变为-positive_edge_l ogic integrated 3/analyze -f or mat veril og -lib library_na me -define SY NOPSI S/3读入veril og 格式的HDL 文件,并且用指定的library 中的中间格式存储3/Set_cl ock_gating_signals -design design_na me/3控制signal 是否采用门控时钟3/elaborate design_na me -gate_cl ock -update -lib library_na me/3从存储的中间格式中建立对应的设计3/p r opagate_constraints -gate_cl ock/3将底层设计中的约束加到当前设计中3/comp ile -incre mental_mapp ing -map_eff ort high/3映射过程中花费更多的cpu 运行时间3/2.2 报告文件Synopys 公司的Design Comp iler 作为业界最流行的综合工具软件,功能相当强大,可以生成详细的报告文件,将会在时序、功耗、面积三个方面加以比较。

首先必须保证时序满足条件,否则功耗的降低和面积的减小就没有意义。

而门控时钟的引入,常常会造成相应的时序问题。

作者使用Synopys 公司的Pri m eTi m e 进行静态时序分析(Static Ti m ing A 2nalysis )。

表1给出的是Pri m eTi m e 对当前设计的关键路径的时序报告。

data required ti m e 表示理论上最大允许的延迟时间,data arrival ti m e 表示实际数据到达的时间。

表1说明,使用门控时钟后,时序仍22安徽大学学报(自然科学版)第29卷然满足要求。

表1 使用门控时钟前后的时序报告不使用门控时钟Start point:wdt_i pb_interface_wdt_reset_b_reg (rising edge -triggered fli p -fl op cl ocked by i pg_clk )Endpoint:wdt_reset_b (out put port cl ocked by i pg_clk ) ………………………………data required ti m e 10.75 data arrival ti m e -6.33 slack (MET )4.42使用门控时钟Start point:i p s_addr_2(input port cl ocked by i pg_clk )Endpoint:wdt_i pb_interface_clk_gate_wm r_reg/latch (negative level -sensitive latch cl ocked by i pg_clk ) …………………………………………data required ti m e 17.50 data arrival ti m e -14.06 slack (MET )3.44 表2给出的是Design Comp iler 对当前设计的功耗报告。

可以看到,使用门控时钟后,功耗总体下降了45.4%。

其中内部功耗下降了53.9%,开关功率下降了35.3%,但是泄漏功耗只下降了1.8%,由于泄漏功耗在总体功耗中比例可以忽略不计,使用门控时钟后功耗总体有了显著的下降。

同时说明门控时钟的使用,对内部功耗和开关功率的影响较为显著,对泄漏功耗的影响不显著。

值得注意的是,虽然不排除通过牺牲面积来降低功耗。

但在本设计中,降低功耗的同时,面积也有了一定的下降。

总面积下降了7.3%,其中组合逻辑的面积减少了21.5%,非组合逻辑的面积增加了5.5%。

说明门控时钟的使用,减少了组合逻辑的使用,增加了非组合逻辑的使用。

表2 使用门控时钟前后的功耗报告 不使用门控时钟的设计 使用门控时钟的设计降低率(%)功耗Cell I nternal Power =473.7284μW (54%)Cell I nternal Power =218.3035μW (46%)53.9 Net S witching Power =396.8938μW (46%)Net S witching Power =256.8232μW 54%)35.3 Total Dynam ic Power =870.6222μW (100%)Total Dyna m ic Power =475.1267μW (100%)45.4 Cell Leakage Power =106.6267n W Cell Leakage Power =104.6448n W 1.8面积/μm 2Combinati onal area:8282.881836Combinati onal area:6503.04296921.5 Noncombinati onal area:9262.079102Noncombinati onal area:9768.9619145.5 Total cell area:17544.960938Total cell area:16272.0000007.33 结 论门控时钟的使用有很多的优点,可以借助EDA 工具的帮助,在综合时插入门控时钟。