详细讲解cmos反相器的原理及特点

- 格式:doc

- 大小:13.00 KB

- 文档页数:2

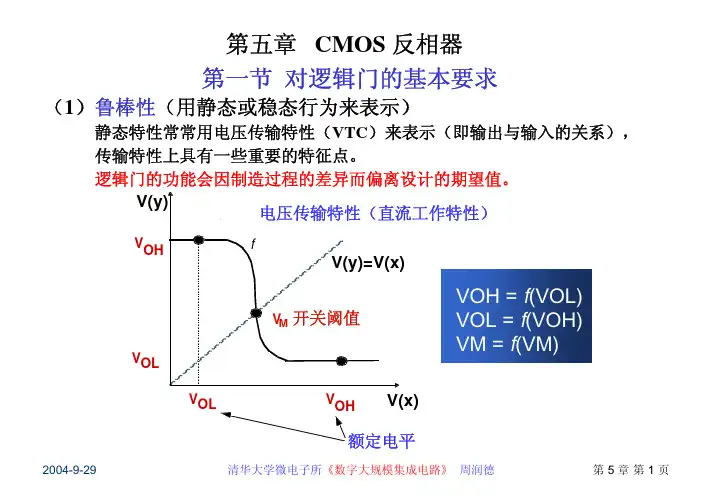

第五章 CMOS 反相器 第一节 对逻辑门的基本要求(1)鲁棒性(用静态或稳态行为来表示)静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

V(y) 电压传输特性(直流工作特性)VOH fV(y)=V(x)VM开关阈值VOL VOL VOHVOH = f(VOL) VOL = f(VOH) VM = f(VM)V(x)额定电平2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第1页(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值 (电感、电容耦合,电源与地线的噪声)。

一个门对于噪声的敏感程度由噪声容限表示。

可靠性―数字集成电路中的噪声v(t) i(t)V DD电感耦合电容耦合电源线与地线噪声噪声来源: (1)串扰 (2)电源与地线噪声 (3)干扰 (4)失调 应当区分: (1)固定噪声源 (2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第2页噪声容限(Noise Margin)V“1” V OH V IHout OH 斜率 = -1V不确定区 斜率 = -1ILV “0” VVOLOL V IL V IH V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第3页噪声容限定义"1"噪声容限(Noise Margin) 容许噪声的限度V IH高电平 噪声容限VOHNM H未定义区 低电平 噪声容限V OL "0" NM L V IL抗噪声能力(Noise Immunity) 抑止噪声的能力门输出门输入2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第4页理想逻辑门V outg=∞Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第5页早期的逻辑门5.0 4.0 3.0 2.0 VM 1.0 NM H NM L0.01.02.03.0 V in (V)4.05.02004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第6页(3) “再生”特性:逻辑门的“再生”特性使被干扰的信号能恢复到名义 的逻辑电平。

图1 CMOS反相器

(a)结构示意图(b)电路图

]

,[)(DD SS I P th GS V V V V ∈+

当V I =V IL =0时

当V I =V IH =V DD 时

⎪⎩⎪⎨⎧<=>=N

th GS GS GS P th GS DD GS V v v V V v )(21)(10)(为负且⎪⎩⎪⎨⎧>=<=N

th GS DD GS P

th GS GS V V v V v )(2)(10输出V=V OH ≈V DD

输出V=V OL ≈0

Vo

静态功耗低

噪声容限高

工作速度快

在CMOS 反相器中,无论电路处于何种状态,T N 、T P 中总有一管截止,所以其静态功耗极低,有微功耗电路之称。

CMOS 反相器的阈值电压U TH =V DD /2,即两管状态在v I =V DD /2处转换,因此其噪声容限接近50%。

CMOS 反相器工作时总有一管导通,且导通电阻较小,为低阻回路,所以带容性负载时,充放电速度很快,CMOS 反相器的t pd ≈10ns 。

cmos反相器工作原理

CMOS反相器是一种基于混合型CMOS技术开发的一种电路,它由一个

主要的反相器和周围电路组成。

它的工作原理是:输入端口输入电压必须

处于某一范围之内,它的输出端口电压高于输入端口的电压值,即输出一

个反向电压值,这就是CMOS反相器的作用原理。

CMOS反相器通常由几个主要的组件组成,这些组件包括p-型晶体管、n-型晶体管和金属氧化物半导体(MOSFET)。

反相器的输入端口会接受一

种电压值,这是输入电压,而晶体管和MOSFET会根据输入电压值来响应,一些形成周围电路的组件会根据所输入的电压来决定电流,最后将得到一

个反向的输出电压。

CMOS反相器的优点在于它的低功耗使得它可以用在节能类的电路中,并且它的体积小,结构简单以及可靠性高。

而且它输出电压的高低可以调节,因此它可以提高电路的灵活性和可靠性,也可以提高电路的稳定性。

什么?CMOS你还搞不明⽩?赶紧看过来!CMOS⼯作原理详解!⼀谈到CMOS,我估计⼤家⾸先想到的就是电脑的CPU,确实,CPU就是⼀个将⼏⼗亿个晶体管集成在⼀起的超级电路,最新报价酷睿I7-7700K太平洋上报价达到了恐怖的2799元,为什么值这么多钱?这与其采⽤了14nm⼯艺,主频达到4.2Ghz是分不开的,想想我笔记本的主频才1.6Ghz,就知道差距有多⼤了,如果你觉得差距不⼤,那我就再说⼀个数字,我买这台笔记本当时的价格还不到这款发烧级CPU价钱的2倍,这样的CPU,再配上顶级主板,顶级显卡,加上顶级内存,以及固态硬盘,再加上电源,机箱,以及⽜逼⼀点风冷后者⽔冷系统,光机箱价格估计就得过万了,这种存在于理想中的东西,想想挺好,哈哈,现实是买不起,买了估计掉价也⽐较快,尤其是显卡,很容易降价。

扯的有点远了,说回到CMOS来,我们没办法理解CPU这么个复杂的东西是怎么⼯作的,但是其最基本单元,MOSFET的⼯作原理是⼀定要懂的,因为⽤到MOSFET的产品可不仅仅只有CPU,⼀般的逻辑电路,数字电路,混合信号电路等等都要⽤到MOSFET,或者CMOS,这个时候如果你还不懂CMOS⼯作原理,就说不过去了,这个可是吃饭的本事啊!想想线上⼀⼤堆活在跑,如果不懂得CMOS⼯作原理,⼯艺中哪个步骤出问题了,会对器件有什么程度的影响不了解,或者最终WAT/PCM数据出来发现异常了,却不知道根据异常结果反推可能出问题的⼯艺步骤,那么分析问题将会是多么的困难啊!搞不好就混不下去了额~~所以说,深⼊理解CMOS的⼯作原理是必须,必要,以及必学的,过程虽然痛苦,结果是好的,所以,打起精神来,跟上我的思路,学起来其实并不难。

学CMOS⼯作原理前,先放⼀张CMOS反相器在这⾥,它的基本原理后⾯再讲,CMOS反相器就是⽆论输⼊端电压正负,都会有输出,相当于0/1切换,⽤处⾮常⼴泛。

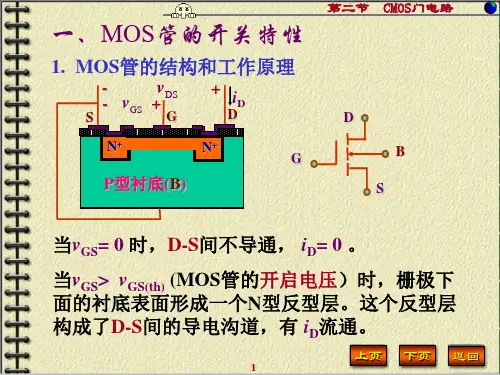

下⾯开始介绍MOSFET:Metal Oxide Semiconductor Field Effect Tranistor,即⾦属氧化物半导体场效应晶体管。

cmos反相器电路结构CMOS反相器电路结构CMOS反相器是一种常见的数字逻辑门电路,用于将输入信号反转输出。

它由一对互补的MOSFET(金属氧化物半导体场效应晶体管)组成,这些MOSFET分别被称为P型MOSFET和N型MOSFET。

CMOS反相器电路结构的设计使其能够实现低功耗、高噪声容限和较高的电压转换速度。

CMOS反相器电路由两个互补的MOSFET组成,一个是P型MOSFET,另一个是N型MOSFET。

P型MOSFET的栅极连接到输入信号,而N型MOSFET的栅极连接到P型MOSFET的反向输入信号。

源极和漏极分别通过电压源和接地连接。

在CMOS反相器中,当输入信号为低电平时,P型MOSFET导通,N型MOSFET截止,输出信号为高电平。

当输入信号为高电平时,P型MOSFET截止,N型MOSFET导通,输出信号为低电平。

因此,CMOS 反相器可以将输入信号反转输出。

CMOS反相器电路的优点之一是功耗较低。

由于只有在输入信号发生变化时,CMOS反相器才会消耗能量。

当输入信号保持不变时,MOSFET处于截止或导通状态,不会消耗能量。

这使得CMOS反相器非常适合用于低功耗应用,如移动设备和电池供电系统。

另一个优点是高噪声容限。

由于CMOS反相器电路中的MOSFET是互补的,当输入信号的电压接近电源电压时,会出现双门限效应。

这种效应可以提高抗噪声干扰的能力,使得CMOS反相器在噪声较多的环境中工作更加可靠。

CMOS反相器电路还具有较高的电压转换速度。

由于P型MOSFET和N 型MOSFET的导通和截止时间非常短,CMOS反相器可以在很短的时间内完成信号的反转。

这使得CMOS反相器非常适合用于高速数字电路中,如微处理器和通信系统。

总结一下,CMOS反相器电路结构由一对互补的MOSFET组成,通过控制MOSFET的导通和截止状态来实现输入信号的反转输出。

它具有低功耗、高噪声容限和较高的电压转换速度等优点,使得它成为数字电路设计中常用的逻辑门电路。

数字集成电路学习总结5CMOS反相器今天开始总结数字集成电路。

这本书其实算是本科最难的⼀本了,细节过多⽆法卒读,涉及到的知识也⾮常全⾯。

实际上本科课程安排中并为将其作为重点,我们的课⾮常⽔,不知道讲了什么。

今天详细总结⼀下。

当时然由于内容过多,⽆法全部涵盖,只能⼤致总结,并着重记录定性的结论。

涉及到计算之类的问题,就只能略过了。

第五章 COMS反相器5.1 引⾔为什么从第五章开始,原因是这章⽐较基础,详细学习CMOS反相器后,才能继续看组合电路和时序电路等等。

研究的对象有如下⼏个指标:成本(复杂性和⾯积)、完整性和稳定性(静态特性)、性能(动态特性)、能量效率(功耗)。

5.2 静态CMOS反相器——直观综述课本上的描述:晶体管只不过是⼀个具有⽆限关断电阻和有限导通电阻的开关。

以开关来理解,可以推导出其他重要特性:1、输出⾼电平和低电平分别为VDD和GND,换⾔之,电压摆幅等于电源电压。

因此噪声容限很⼤。

2、逻辑电平与器件的相对尺⼨⽆关,所以晶体管可以采⽤最⼩尺⼨。

这⾥有⼀个概念叫⽆⽐逻辑3、稳态时,输出和VDD或GND之间总存在有限电阻的通路。

因此⼀个设计良好的CMOS反相器具有低输出阻抗,这使得它对噪声和⼲扰不敏感。

4、输⼊电阻极⾼。

理论上,单个反相器可以驱动⽆穷个门,或者说有⽆穷⼤的扇出。

但很快我们发现增加扇出也会增加传播延时。

因此扇出不会影响稳态特性,会影响瞬态特性。

5、忽略漏电流的话,意味着⽆静态功耗。

之前常⽤的是NMOS电路,静态功耗不为0,限制了集成度。

后来必须转向CMOS。

电压传输特性(VTC)的性质和形状可以通过图解法迭加两管的图像得到。

结果是观察到VTC具有⾮常窄的过渡区。

我们可以把开关特性简化为RC电路,⼀个快速门的设计是通过减⼩输出电容或者减⼩晶体管的导通电阻(增⼤宽长⽐)实现的。

5.3 CMOS反相器稳定性的评估——静态特性5.3.1 开关阈值开关阈值VM定义是Vin=Vout的点,利⽤图解法可以看出。

第五讲 CMOS 反相器一、实现反相器功能的MOS电路有哪些?比较其性能。

答:图(a) 图(b) 图(c)1)电阻负载型反相器:电路结构如图(a)所示,当NMOS器件截止时,电阻将输出上拉到V OH;当NMOS导通时,将和上拉器件一起组成一个电阻分压器,产生一个低输出V OL,从而可以实现基本的反相器功能。

性能:电阻负载占用很大的芯片面积,同时会产生一个很大的上升时间,增大了电路的延迟和功耗,而且很难显著地改善噪声容限。

因此,在MOS数字电路中,几乎不用传统的电阻器作负载,通常要用NMOS执行上拉电阻的功能。

2)饱和负载NMOS反相器:电路结构如图(b)所示,栅漏两极连接在一起的单个NMOS作为上拉负载,使输出节点上拉V OH;另一个NMOS将输出节点下拉,以尽量使其放电。

这两个MOS管的尺寸比例决定了输出电压的大小,因此也被称为有比反相器。

性能:与电阻负载型相同,其输出高电平V OH不等于V DD,最高只能到达V DD - V TL。

因此,在使用低电源电压的时候,很难设计出能够自安全的噪声容限范围内正常工作的电路。

另外,在输出为低电平时,电流直接由电源V DD流到地端,导致电路中存在较大的直流功耗。

3)线性负载NMOS反相器:电路结构如图(c)所示,将负载晶体管的栅极连接到一个高于V DD的直流电压V GG上,可使输出高电平V OH有所提高,即V GG > V DD + V TL(V DD)。

满足这个条件的MOS电路即为E/D线性负载反相器。

性能:当用于静态反相器和逻辑门的时候,线性增强型负载存在几个缺点:由于额外的电压源V GG,所以需要增加互连线,从而占用更多的芯片面积;在输出为低的情况下,电路中存在直流功耗。

4)CMOS反相器:电路结构如图(d)所示,上面的PMOS的栅极和下面的NMOS的栅极连接在一起,PMOS的忖底连接到电源V DD,而NMOS的忖底连接到地Gnd,使漏/源反向偏置。

CMOS反相器原理结构及性能参数CMOS反相器是一种基本的数字逻辑电路元件,由两个互补MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)组成。

它可以实现电信号的反相,并起到信号放大的作用。

CMOS反相器不仅在数字电路中使用广泛,还在模拟电路中应用于放大器和振荡器等电路中。

CMOS反相器的基本原理是利用MOSFET的门电压控制特性,当输入信号为高电平时,NMOS(负材料氧化物半导体场效应晶体管)导通,PMOS (正材料氧化物半导体场效应晶体管)截止;当输入信号为低电平时,NMOS截止,PMOS导通。

这样,通过选取适当的参数,输出信号就可以实现输入信号的反相。

CMOS反相器的结构是由一个PMOS和一个NMOS组成,它们的结构和工作原理有所不同。

PMOS是由P型半导体材料构成的,当门电压低于阈值电压时,导电性较好;NMOS是由N型半导体材料构成的,当门电压高于阈值电压时,导电性较好。

输入电压范围指的是输入信号的电压范围,一般为输入高电平(High Level Input)和输入低电平(Low Level Input)两个阈值电压之间的范围。

输出电压范围指的是输出信号的电压范围,一般为输出高电平(High Level Output)和输出低电平(Low Level Output)两个阈值电压之间的范围。

增益是指输出电压随输入电压的变化率,一般为输出电压变化量与输入电压变化量的比值。

在CMOS反相器中,增益一般很高,可以达到几十倍甚至更高。

功耗是指CMOS反相器消耗的电功率,一般与输入电压和输出电流有关。

CMOS反相器的功耗一般比较低,因为在输入端只需要很小的电流就能控制输出的大电流。

速度是指CMOS反相器的响应时间,即输入信号变化到输出信号变化的时间。

CMOS反相器的速度一般较快,可以达到几纳秒的量级。

除了以上的性能参数,CMOS反相器还有一些其他的性能指标,如输入电容、输出电容、输出阻抗和输入阻抗等。

cmos反相器等效电容解释说明以及概述1. 引言1.1 概述在现代电子领域中,CMOS(互补金属氧化物半导体)技术被广泛应用于数字电路设计中,具有低功耗、高可靠性和较高的集成度等优点。

而反相器作为数字电路的基本构建模块之一,其性能对整个电路系统的稳定性和可靠性起着至关重要的作用。

其中一个重要的因素是反相器的等效电容。

1.2 文章结构本文将深入研究CMOS反相器等效电容及其对于数字电路性能的影响。

文章将分为五个主要部分进行阐述。

首先,在引言部分介绍文章的背景和目标。

然后,在第二部分详细解释CMOS反相器的工作原理,并阐述CMOS反相器结构以及相关术语和概念。

接下来,在第三部分中描述了实验步骤和数据分析方法,并分析讨论了实验结果。

第四部分探讨了CMOS反相器在数字电路中的应用领域以及反相器等效电容对性能的影响及优化策略。

最后,在结论部分对全文内容进行总结,并展望未来可能的研究方向。

1.3 目的本文的目的是深入研究和解释CMOS反相器等效电容的概念,探讨其对数字电路性能的影响,并提出相应的优化策略。

通过本文的阐述,读者将能够全面了解CMOS反相器等效电容以及其在数字电路中的应用。

此外,本文还旨在推动CMOS技术发展并展望未来可能的研究方向,从而促进数字电路技术的持续创新与发展。

2. CMOS反相器等效电容:2.1 反相器工作原理:CMOS反相器是一种基本的数字逻辑门电路,用于将输入信号取反输出。

其工作原理涉及N型和P型金属氧化物半导体场效应管(NMOS和PMOS)的结合使用。

在CMOS反相器中,当输入信号为高电平时,NMOS管导通,PMOS管截断;而当输入信号为低电平时,PMOS管导通,NMOS管截断。

由此可见,在CMOS 反相器中没有直接路径可以让电流从VDD到地,因此功耗很低。

2.2 CMOS反相器结构:CMOS反相器由一个NMOS和一个PMOS管组成。

它们通过共享栅极端口连接在一起,形成了一个交叉连接的结构。

详细讲解cmos反相器的原理及特点

CMOS(cornplementary MOS)由成对的互补p沟道与n沟道MOSFET所组成.CMoS逻辑成为目前集成电路设计最常用技术的缘由,在于其有低功率损耗以及较佳的噪声抑止才干.事实上,由于低功率损耗的需求,目前仅有CMOS技术被运用于ULSI 的制造.

CMOS反相器

如图6. 28所示,CMOS反相器为CMOS逻辑电路的基本单元.在CMOS反相器中,p 与n沟道晶体管的栅极衔接在一同,并作为此反相器的输入端,而此二晶体管的漏极也连接在一同,并作为反相器的输出端.n沟道MOSFET的源极与衬底接点均接地,而p沟道MOSFET的源极与衬底则衔接至电源供应端(VDD),需留意的是p沟道与n沟道MOSFET 均为增强型晶体管,当输入电压为低电压时(即vin=O,VGsn=o|VTp|(VGSp与VTp 为负值),所以p沟道MOSFET.为导通态,

因此,输出端经过p沟道MOSFET充电至VDD,当输入电压逐渐升高,使栅极电压等于VDD时,由于VGSn=VDD>VTn,所以n沟道MOSFET将被导通,而由于|VGSp |≈O

欲更深化天文解CMOS反相器的工作,可先画出晶体管的输出特性,如图6.29所示,其中显现Ip以及In为输出电压(V out)函数.Ip为p沟道MOSFET由源极(衔接至VDD)流向漏极(输出端)的电流;In为n沟道MOSFET由漏极(输出端)流向源极(衔接至接地端)

的电流.需留意的是在固定V out下,增加输入电压(vin)将会增加In而减少Ip,但是在稳态时,In应与Ip相同,关于给定一个Vin可由In(Vin)与Ip(Vin)的截距,计算出相对应的V out如图6. 29所示.如图6.30所示的Vin-V out曲线称为CMOS反相器的传输曲线.

CMOS反相器的一个重要的特性是,当输出处于逻辑稳态(即V out=或VDD)时,仅有一个晶体管导通,因此由电源供应处流到地端的电流非常小,且相当于器件关闭时的漏电流.事实上,只需在两个器件暂时导通时的极短暂态时间内才会有大电流流过,因此与。