SPI协议的Verilog 实现

- 格式:pdf

- 大小:308.13 KB

- 文档页数:10

应用笔记487利用MAX II CPLD 实现SPI 至I 2S 的接口引言本应用笔记介绍怎样使用Altera ®MAX ®II CPLD 来实现协议转换,通过串行外设接口(SPI)控制inter-IC 声音(I 2S)总线上的音频设备数据流。

I 2S 和SPI 接口I 2S 是3线半双工串行接口,常用于通过被称为I 2S 总线的3线总线来连接系统中的音频设备。

I 2S 设备和总线使用3条线:串行数据(SDA ),承载了对应于每一个音频通道的两路时分复用音频数据;串行时钟(SCK )和字选择(WS ),控制数字音频数据在I 2S 总线上不同设备之间的传输。

I 2S 系统能够处理和串行时钟分开的串行音频数据,以消除抖动。

SPI 是4线全双工串行接口,常用于连接系统内部和外部的系统处理器(主机)和外设(从机)。

SPI 利用单独的数据输出信号线(主机输出从机输入,即MOSI )和数据输入信号线(主机输入从机输出,即MISO ) 以及时钟(SCLK )和从机选择或者片选信号(CS )来进行通信。

本设计支持SPI 接口主机对其他设备的数据流控制,包括A/D 转换器、数字信号处理器、数字滤波器、音频处理器、PC 多媒体音频转换器等 I 2S 总线设备。

有的嵌入式系统并没有为音频数据通信提供I 2S 接口,但是有SPI 接口。

您可以在和这些接口相似的环境中有效地使用本设计。

利用MAX IICPLD 实现SPI 至I 2S 的接口SPI 主机的桥接接口是SPI 从机,它有四条信号线(CS , SCLK , MISO 和MOSI )。

I 2S 总线一侧接口是I 2S 主机,它有三条信号线(I2S_ SCK , I2S_SDA 和I2S_WS )。

CLK 是主机时钟,位于I 2S 主机外部。

图1所示为采用 MAX II CPLD 来实现SPI 至I 2S 接口。

2007年12月,1.0版图1.利用MAX II CPLD实现SPI至I2S接口本设计提供协议转换功能,通过SPI 接口(更常用的4线串行接口,用于连接串行外设接口和微处理器或者主机)来控制I2S 总线(带宽相对较窄的协议,用于连接系统中的数字音频设备)上音频设备的数据流。

基于UVM的APB-SPI验证平台的设计方法与实现技术基于UVM的APB-SPI验证平台的设计方法与实现技术一、引言随着数字集成电路的高度发展,可编程逻辑设备(PLD)在各种电子设备中的应用不断增加。

为确保这些 PLD 设备的功能正确性和稳定性,需要进行严格的验证工作。

本文将介绍一种基于Universal Verification Methodology(UVM)的Advanced Peripheral Bus(APB)与Serial Peripheral Interface(SPI)的验证平台设计方法与实现技术。

二、APB和SPI协议简介APB和SPI是两种常用的串行通信协议,用于连接微处理器和外设。

APB是一种低功耗和高性能的总线协议,它通过统一的地址和数据线,实现了对外围设备的读写操作。

SPI是一种简单的同步串行通信协议,每个外围设备都有一个片选线,可以通过与微处理器交互进行数据传输。

三、UVM测试平台设计方法1. 环境架构设计在设计UVM测试平台时,需要考虑到测试环境和被测设计的互动。

首先,创建一个环境类来模拟测试环境,包括实例化被测设计以及其他必要的外设模块。

然后,使用相关接口将测试环境与被测设计连接起来。

2. 驱动和监控器设计驱动和监控器是验证平台中的核心组件。

驱动负责向被测设计发送有效的数据包,并处理相关时序。

监控器负责监听被测设计发送的数据包,并进行校验。

3. 配置和注入错误为了确保被测设计的稳定性和鲁棒性,需要在测试平台中配置和注入错误。

这可以通过配置寄存器值或注入故障来实现。

例如,可以向被测设计发送错误的数据包,观察其响应是否正确。

四、UVM实现技术1. 类和对象UVM基于SystemVerilog语言实现,通过使用类和对象来描述和组织验证平台中的各个组件。

类是UVM中最基本的单位,对象是类的实例。

2. UVM构建块UVM提供了一系列的构建块,用于创建而不是定义测试平台的各个组件。

![[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序](https://uimg.taocdn.com/1221e485ec3a87c24028c428.webp)

FPGA实现SPIFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现不同的数字电路功能。

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于连接外围设备和主控制器。

在本文中,将介绍如何使用FPGA实现SPI。

1.确定硬件资源:首先,需要确定FPGA中可用的IO资源。

SPI需要至少4个IO口,分别是主设备的时钟引脚(SCK),主设备输出的数据引脚(MOSI),主设备输入的数据引脚(MISO)和片选引脚(SS)。

根据所用的FPGA型号,可以查找对应的引脚定义。

2.确定SPI时序:SPI的时序是非常重要的,不同设备可能有不同的时序规范。

一般情况下,SPI的时序包括时钟下降沿数据采样、时钟上升沿数据输出等。

SPI的时序图可以在设备的数据手册中找到。

3. 编写SPI控制器:SPI控制器可以用硬件描述语言如VHDL或Verilog编写。

控制器的功能包括生成时钟、控制数据的发送和接收、以及处理片选信号。

a.时钟生成:SPI通信需要一个时钟信号来驱动数据的传输。

可以通过计数器模块来生成控制器的时钟信号。

计数器的频率一般是SPI时钟频率的若干倍。

b. 数据发送:对于主设备(Master),要发送数据给外设,可以使用移位寄存器(Shift Register)来存储要发送的数据。

可以使用计数器生成移位寄存器的时钟信号,通过串行输入数据,并在时钟的上升沿时将数据发送到MOSI引脚。

c.数据接收:对于主设备,要接收外设发送的数据,可以使用另一个移位寄存器来接收MISO引脚传输的数据。

可以使用计数器生成移位寄存器的时钟信号,通过MISO引脚接收数据,并在时钟的下降沿时将数据存储到接收寄存器。

d.片选控制:SPI通信需要一个片选信号来选择要与主设备通信的外设。

可以通过一个时序控制器实现片选信号的生成。

在与一些外设通信时,使能片选信号,否则禁用片选信号。

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

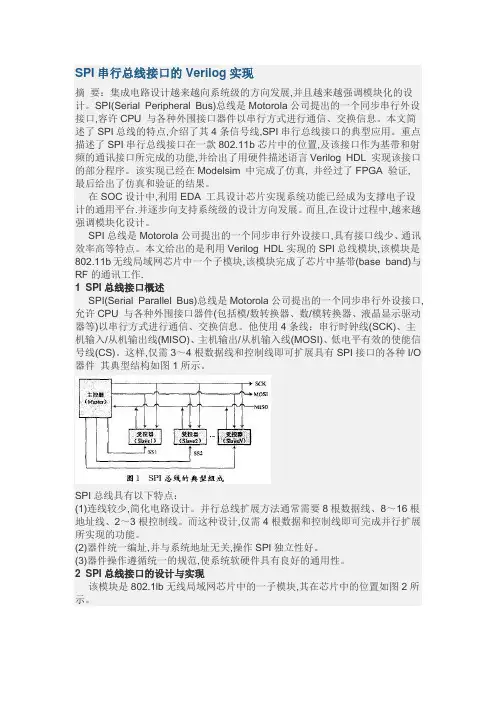

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

基于APB总线的SPI接口设计与实现刘梦影;王芬芬【摘要】基于高性能外设总线(APB,Advance Peripheral Bus)接口,设计了一个支持多样化工作模式和通信格式的SPI接口.为实现高速通信,该SPI采用一个复用移位寄存器.用硬件描述语言Verilog HDL设计并实现了SPI模块.仿真结果表明,该SPI接口能够支持多种工作模式和通信方式,同时确保数据传输有效.【期刊名称】《电子与封装》【年(卷),期】2018(018)005【总页数】5页(P28-32)【关键词】SPI;APB总线;多样化;复用【作者】刘梦影;王芬芬【作者单位】中国电子科技集团公司第五十八研究所,江苏无锡214072;中国电子科技集团公司第五十八研究所,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言现如今,数字技术高速发展,许多芯片或作为核心器件用于数据交换,具有承上启下的数据交换枢纽作用,或用于集成电路之间进行数据存储和显示等[1]。

为适应通信环境和高速的通信速率要求,通常使用多个微处理器完成信号的收发处理,因此需要一种高效的数据总线快速有效地完成它们之间大量的数据交换。

因此,设计一个高效快速的通信接口是至关重要的[2]。

串行外围设备接口SPI总线技术是Motorola公司推出的一种微处理器、微控制器以及外设间的串行数据接口标准[3],主要用于扩展外设和进行数据交换[4]。

SPI接口连线简单,配置灵活,传输效率高[5],因此应用广泛,很多器件如E2PROM、FLASH、实时时钟、A/D转换器等都用到了SPI接口[6]。

郭艾华[7]设计了一种可灵活配置为主/从设备,设置传输速率,支持DMA功能并适用于多种时钟模式的SPI协议IP核,但从机片选信号只可由主机输出,存在一定的局限性。

李琦、贺明等[8]以微处理器S3C2440和嵌入式Linux操作系统组成的嵌入式系统作为开发平台,设计了一款基于ARM嵌入式系统的SPI驱动程序,该设计存在两组8位移位寄存器,支持传输8位数据,但未有效地运用硬件资源。

十二SPI总线接口的verilog的实现1.实验目的项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,本实验根据SPI协议,编写了一个简单的SPI读写程序,可以进行32位数据的读写,可以设置SPI SCLK相对于主时钟的分频比。

2.实验原理SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就是负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

SPI串行总线接口的Verilog实现摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。

SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。

本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。

重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。

该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。

在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。

而且,在设计过程中,越来越强调模块化设计。

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。

本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作.1 SPI总线接口概述SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。

他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。

这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O 器件其典型结构如图1所示。

SPI总线具有以下特点:(1)连线较少,简化电路设计。

并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。

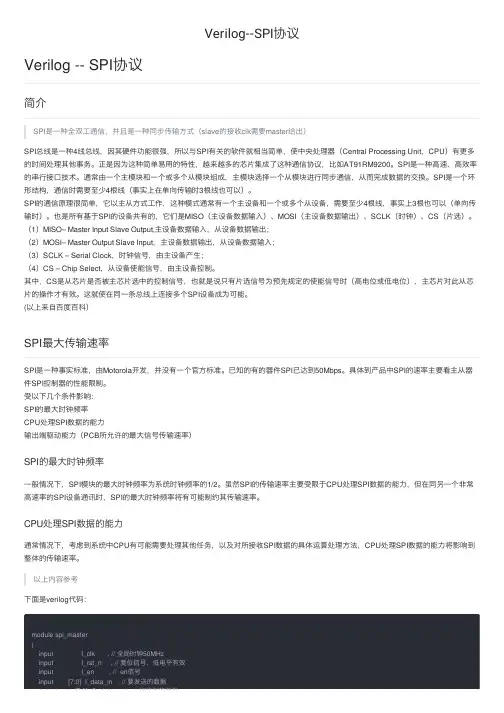

Verilog--SPI协议Verilog -- SPI协议简介SPI是⼀种全双⼯通信,并且是⼀种同步传输⽅式(slave的接收clk需要master给出)SPI总线是⼀种4线总线,因其硬件功能很强,所以与SPI有关的软件就相当简单,使中央处理器(Central Processing Unit,CPU)有更多的时间处理其他事务。

正是因为这种简单易⽤的特性,越来越多的芯⽚集成了这种通信协议,⽐如AT91RM9200。

SPI是⼀种⾼速、⾼效率的串⾏接⼝技术。

通常由⼀个主模块和⼀个或多个从模块组成,主模块选择⼀个从模块进⾏同步通信,从⽽完成数据的交换。

SPI是⼀个环形结构,通信时需要⾄少4根线(事实上在单向传输时3根线也可以)。

SPI的通信原理很简单,它以主从⽅式⼯作,这种模式通常有⼀个主设备和⼀个或多个从设备,需要⾄少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是MISO(主设备数据输⼊)、MOSI(主设备数据输出)、SCLK(时钟)、CS(⽚选)。

(1)MISO– Master Input Slave Output,主设备数据输⼊,从设备数据输出;(2)MOSI– Master Output Slave Input,主设备数据输出,从设备数据输⼊;(3)SCLK – Serial Clock,时钟信号,由主设备产⽣;(4)CS – Chip Select,从设备使能信号,由主设备控制。

其中,CS是从芯⽚是否被主芯⽚选中的控制信号,也就是说只有⽚选信号为预先规定的使能信号时(⾼电位或低电位),主芯⽚对此从芯⽚的操作才有效。

这就使在同⼀条总线上连接多个SPI设备成为可能。

(以上来⾃百度百科)SPI最⼤传输速率SPI是⼀种事实标准,由Motorola开发,并没有⼀个官⽅标准。

已知的有的器件SPI已达到50Mbps。

具体到产品中SPI的速率主要看主从器件SPI控制器的性能限制。

S PI 总线接口的FPG A 设计与实现 杨承富1,徐志军2(1.解放军理工大学通信工程学院研究生2队,江苏南京210007;2.解放军理工大学通信工程学院电子信息工程系)摘 要:文中介绍了采用Alter ea 公司F LEX 10K 型的F PG A 器件实现串行外设接口(SPI)的原理与过程,给出了逻辑框图以及部分V erilog代码。

用此种方法实现的接口与专用接口芯片相比,具有使用灵活,系统配置方便的优点。

关键词:串行外设接口;现场可编程门阵列;V erilog 硬件描述语言中图分类号:T P336文献标识码:A 文章编号:0032-1289(2004)02-0072-05Design and Implemen t SPI Bus Interface with FPGAYAN G Cheng -fu 1,X U Zhi -jun 2(1.Postg raduate T ea m 2ICE,P L AU S T,Na njing 210007,China;2.Depar tment of Eelc tro nic Info r ma tio n Eng nee ring ICE,PL A U ST )Abstract :The theo ry and the wa y of im plementing a SPI interface w ith FPGA areintroduced,and the blo ck diag ram a nd som e Verilog code are presented.The chip implemented in this way has mo re agility and is m ore conv enient to co nfigure than others.Key words :SPI interface ;FPGA ;Verilog HDL串行外设接口SPI(Serial Peripheral Interface)是Mo to ro la 公司推出的一种同步串行接口。

电子与电气工程系课程设计、专题(综合)实验报告课题名称__串行接口IP核的设计与验证(spi)_专业____ 电子信息工程________班级_____ 08电子1班__________学号__0806012103_ 0806012104_姓名___ 高江柯____吴冠雄__ ______成绩________________________指导教师_______袁江南____________2011年 6 月 15 日串行接口IP核的设计与验证(SPI)(FPGA作为主机)一、实验目的:通过本实验的学习,使学生掌握使用VHDL 设计一个实用数字系统的能力,以及单片机串行接口编程等知识,训练 VHDL以及单片机的编程与综合使用能力,培养工程设计的基本技能,为今后毕业设计以及实际工作奠定基础。

二、实验原理SPI 接口是在CPU 和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C 总线要快,速度可达到几Mbps。

SPI 接口是以主从方式工作的,这种模式通常有一个主器件和一个或多个从器件,其接口包括以下四种信号:(1)MOSI –主器件数据输出,从器件数据输入(2)MISO –主器件数据输入,从器件数据输出(3)SCLK –时钟信号,由主器件产生(4)/CS –从器件使能信号,由主器件控制在点对点的通信中,SPI 接口不需要进行寻址操作,且为全双工通信,显得简单高效。

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

下图所示,在SCLK 的下降沿上数据改变,同时一位数据被存入移位寄存器。

三、实验步骤:1、查找关于SPI的资料,认识理解SPI。

2、根据SPI传输数据的时序图构建出SPI的框图。

3、利用自顶向下的方法根据框图分模块进行程序的编写。

板级通信总线之SPI及其Verilog实现打算写⼏篇专题,系统总结下常⽤的⽚上总线、现场总线,就先从最常⽤的SPI开始吧。

1. SPI是⼲什么的?除了SPI还有那些其它电路板及的通讯总线?有何差别?相信接触过MCU的同学对SPI都不陌⽣,详细定义就不罗嗦了。

SPI常⽤的场合包括ADC读写、存储芯⽚读写、MCU间通讯等等。

可以⼀主多从(通过⽚选来选择Slave),也可以做成菊花链等等形式的拓扑。

与SPI类似的总线还有IIC、UART等,甚⾄还有很多单根线的总线,原理都是基于简单的串⾏通信,区别在于收发时序和连接拓扑。

要熟练使⽤这些总线,关键在于理解其时序图,在此基础上创造各种变种的总线形式也不是难事(当然为了设计的通⽤性不建议这么做)。

以下维基百科的SPI词条介绍⾮常全⾯,推荐阅读。

2. SPI是什么样的?在此借⽤⼀张维基百科上的图,SPI通常有4根线,SS⽤于选定当前通信的slave,SCLK为通信的基准时钟,采样/发送都在时钟边沿执⾏,MOSI、MISO为串⾏的数据线。

以下是⼀个典型的SPI时序图,Master和Slave均在时钟上升沿采样,下降沿发送数据。

数据从最⾼位(MSB)开始发送。

需要注意图中所有的时序关系都要被满⾜,包括CS下降沿到第1个时钟上升沿间隔(t sclk_su)、数据的建⽴时间(t SU)、保持时间(t HD)等等。

通常这些参数由具体的器件决定,如果不满⾜则有通信失败的风险。

3. 如何使⽤SPI?SPI有哪⼏种配置模式(相位、极性)?根据SPI时钟信号的空闲状态、是上升沿采样还是下降沿采样,SPI有四种模式。

CPOL=0表⽰时钟空闲时为低电平,反之为⾼电平;CPHA=0表⽰时钟信号第⼀个边沿是采样边沿,反之表⽰第2个边沿是采样边沿。

对于带SPI接⼝的MCU⽽⾔,通常可由软件配置CPOL(Clock Polarity)、CPHA(Clock Phase),以适应和不同类型器件的通信。

What is SPI?SPI is a simple interface that allows one chip to communicate with one or more other chips.How does it look?Let's start with a simple example where only two chips have to communicate together.SPI requires 4 wires to be used in between the two chips.As you can see, the wires are called SCK, MOSI, MISO and SSEL, and one of the chip is called the SPI master, while the other the SPI slave.SPI fundamentalsBasically:1.It is synchronous.2.It is serial.3.It is full-duplex.4.It is not plug-and-play.5.There is one (and only one) master, and one (or more) slaves.In more details:1. A clock is generated by the master, and one bit of data is transferred each time the clock toggles.2.Data is serialized before being transmitted, so that it fits on a single wire.3.There are two wires for data, one for each direction.4.The master and slave know beforehand the details of the communication (bit order, length of data words exchanged,etc...)5.The master is always the one who initiates communication.Because SPI is synchronous and full-duplex, every time the clock toggles, two bits are actually transmitted (one in each direction).Simple transferLet's assume that the master and slave expect 8-bits data transfers, with MSB transmitted first.Here's how would look a single 8-bits data transfer.The line MOSI is the "master output" while MISO is the "slave output". Since SPI is full-duplex, both lines toggles simultaneously, with different data going from master-to-slave, and slave-to-master.In more datails:1.The master pulls SSEL down to indicate to the slave that communication is starting (SSEL is active low).2.The master toggles the clock eight times and sends eight data bits on its MOSI line. At the same time it receives eightdata bits from the slave on the MISO line.3.The master pulls SSEL up to indicate that the transfer is over.If the master had more than one 8-bits data to send/receive, it could keep sending/receiving and de-assert SSEL only when it is done.Multiple slavesAn SPI master can communicate with multiples slaves by connecting most signals in parallel and adding SSEL lines, or by chaining the slaves.With the multiple SSEL lines technique, only one SSEL line is actived at a time, and slaves that are not selected must not drive the MISO line.How fast is it?SPI can easily achieve a few Mbps (mega-bits-per-seconds). That means it can be used for uncompressed audio, or compressed video.ARM processorTo get an opportunity to test our newly acquired SPI knowledge, we use a Saxo-L board. It has an ARM7 processor (LPC2138) and a Cyclone FPGA (EP1C3), connected by a SPI bus.The ARM is used as a SPI master, while the FPGA is used as a SPI slave. The Saxo-L ARM processor has actually two SPI interfaces, one called SPI0, and a more advanced one called SPI1/SSP. They are both equally easy to use. We are using SPI1/SSP on Saxo-L, as it is pre-wired on the board.SPI master - C ARM codeUsing SSP is just a matter of initializing a few registers, and then writing/reading data to send/receive automatically.void main(void){// initialize SSPSSP0CPSR = 0x02; // SSP max speedSSP0CR0 = 0x07; // SSP max speed, 8 bitsSSP0CR1 = 0x02; // SSP master modePINSEL1 = 0x2A8; // SSP mode for pins P0.17 to P0.20while(1){// send two bytesSSP0DR = 0x55; // one nice thing about the SSP is that it has a 8-words deep FIFOSSP0DR = 0x54; // so here we write the data to be sent without worrying// now wait until both bytes are sentwhile(!(SSP0SR & 0x01));// now we can read the two bytes received... and do anything with themint data1 = SSP0DR;int data2 = SSP0DR;// ...}} SPI slave - HDL FPGA codeNow for the SPI slave in the FPGA.Since the SPI bus is typically much slower than the FPGA operating clock speed, we choose to over-sample the SPI bus using the FPGA clock. That makes the slave code slightly more complicated, but has the advantage of having the SPI logic run in the FPGA clock domain, which will make things easier afterwards.First the module declaration. module SPI_slave(clk, SCK, MOSI, MISO, SSEL, LED);input clk;input SCK, SSEL, MOSI;output MISO;output LED;Note that we have "clk" (the FPGA clock) and an LED output... a nice little debug tool. "clk" needs to be faster than the SPIWe sample/synchronize the SPI signals (SCK, SSEL and MOSI) using the FPGA clock and shift registers.本页已使用福昕阅读器进行编辑。

FPGA实现SPIFPGA(Field-Programmable Gate Array)是一种可编程的逻辑芯片,可以通过编程实现不同的功能。

SPI(Serial Peripheral Interface)是一种通信协议,可以在芯片之间进行数据传输。

要在FPGA上实现SPI,首先需要了解SPI的基本原理和通信方式。

SPI使用主从模式,由一个主设备控制多个从设备。

主设备通过时钟信号(SCLK)控制数据的传输,同时使用一个片选信号(SS)来选择目标从设备。

主设备通过MOSI(Master Out Serial In)线将数据发送给从设备,从设备则通过MISO(Master In Serial Out)线将数据回传给主设备。

为了实现SPI通信,需要在FPGA内部设计SPI控制器。

SPI控制器的主要功能包括时钟生成、数据发送和接收、片选信号控制等。

在FPGA中,可以使用可编程逻辑单元(PL)和可编程输入/输出单元(IOB)来实现SPI控制器。

首先,需要使用PL来生成时钟信号。

可以使用计数器和状态机来实现时钟分频和时序控制。

通过控制计数器以及时钟信号的边沿来生成SPI所需的SCLK信号。

接下来,需要使用IOB来进行数据的发送和接收。

可以将MOSI线和MISO线分别连接到适当的IOB引脚。

对于数据的发送,可以通过内部存储器或寄存器来存储要发送的数据,并通过控制逻辑将数据发送到MOSI线上。

对于数据的接收,从MISO线上获取到的数据需要经过逻辑电平转换,并存储或传递给其他组件。

最后,需要使用逻辑电平转换器来生成SPI的片选信号。

可以使用门电路或者专门的逻辑转换芯片来控制片选信号的逻辑电平。

通常情况下,只有在特定的片选信号处于逻辑低电平时,相关的从设备才能接收和响应数据。

在设计完成后,可以使用硬件描述语言(HDL)如Verilog或VHDL来描述SPI控制器,并使用FPGA开发工具进行综合、布局和编程。

在开发工具中,可以了解到FPGA的资源占用情况,时序约束和时钟分频等设置,以及进行仿真和调试。

FPGA作为从机与STM32进行SPI协议通信Verilog实现一.SPI协议简要介绍SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU 与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设时钟相位和极性应该一致。

以下是SPI时序图:主要讲解一下广泛使用的两种方式设置:SPI0方式:CPOL=0,CPHA=0;SCK空闲状态为低电平,第一个跳变沿(上升沿)采样数据,无论对Master还是Slaver都是如此。

SPI3方式:CPOL=1,CPHA=1;SCK空闲状态为高电平,第二个跳变沿(上升沿采样数据,无论对Master还是Slaver都是如此。

基于SPI 总线FLASH 时序控制的FPGA 实现薛宏亮 合肥工业大学仪器科学与光电工程学院 安徽合肥 2300090 引言FLASH 存储器作为一类新型存储器,因具有功耗低、速度快、容量大、成本低和非易失性等优点在各种嵌入式系统中得到越来越广泛地应用。

随着技术的发展和需求的提高,数据的处理日益向着高速化的趋势发展,此时,通过普通的处理器来读取FLASH 中的数据已经达不到要求。

而利用FPGA 控制FLASH 存储器的读取可以达到较高的处理速度,所以在高速数据处理领域,利用FPGA 实现FLASH 存储系统控制的工程应用相当广泛。

本文以winbond 公司的SPI 接口FLAH 芯片W25Q128BV 和Altera 公司的Cyclone 系列FPGA 芯片EP4CE6F17C8为例,用Verilog 硬件描述语言实现了以SPI 总线协议为基础的FLASH 读取控制时序,实现了FPGA 和FLASH 存储器的接口操作。

1 SPI 总线协议和W25Q128BV 芯片介绍1.1 SPI 总线协议SPI(Serial Peripheral Interface)是一种高速的、全双工、同步的通信总线。

由于其在芯片管脚上只占用4根线,节约了管脚资源的同时也为PCB 布局节省了空间,因而越来越多的芯片集成了这种通信协议。

SPI 的通信原理简单,它以主从模式工作,通常需要一个主设备和一个或者多个从设备,需要至少4根线,分别是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。

其中SDI 用于主设备数据输入,从设备数据输出;SDO 用于主设备数据输出,从设备数据输入;SCLK 为时钟信号,必须由主设备提供;CS 为从设备使能信号,由主设备控制。

SPI 是串行通信协议,SDI 和SDO 与SCLK 同步,是基于SCLK 提供的时钟脉冲完成数据的逐位传输。

1.2 W25Q128BV 芯片介绍W25Q128BV 是winbond 公司开发的128Mbit SPI 接口的串行FLASH 存储芯片,由于它所需引脚少,功耗低,所以通常作为空间、引脚和功耗有限的系统的存储设备。

/****************************************************************************** ****************** SPI MASTER* January 2007******************************************************************************* *****************/`timescale 10ns/1nsmodule SPI_Master ( miso, mosi, sclk, ss, data_bus, CS, addr, pro_clk, WR, RD);inout [7:0] data_bus; // 8 bit bidirectional data businput pro_clk; // Host Processor clockinput miso; // Master in slave outinput [1:0] addr; // A1 and A0, lower bits of address businput CS; // Chip Selectinput WR, RD; // Write and read enablesoutput mosi; // Master out slave inoutput sclk; // SPI clockoutput [7:0] ss; // 8 slave select linesreg [7:0] shift_register; // Shift registerreg [7:0] txdata; // Transmit bufferreg [7:0] rxdata; // Receive bufferreg [7:0] data_out; // Data output registerreg [7:0] data_out_en; // Data output enablereg [7:0] control, status; // Control Register COntrols things like ss, CPOL, CPHA, clock divider// Status Register is a dummy register never used.reg [7:0] clk_divide; // Clock divide counterreg [3:0] count; // SPI word length counterreg sclk;reg slave_cs; // Slave cs flagreg mosi; // Master out slave inreg spi_word_send; // Will send a new spi word.wire [7:0] data_bus;wire [7:0] data_in = data_bus;wire spi_clk_gen;wire [2:0] divide_factor = control[2:0];wire CPOL = control[3];wire CPHA = control[4];wire [7:0]ss;/* Slave Select lines */assign ss[7] = ~( control[7] & control[6] & control[5] & (~slave_cs)); assign ss[6] = ~( control[7] & control[6] & ~control[5] & (~slave_cs)); assign ss[5] = ~( control[7] & ~control[6] & control[5] & (~slave_cs)); assign ss[4] = ~( control[7] & ~control[6] & ~control[5] & (~slave_cs)); assign ss[3] = ~(~control[7] & control[6] & control[5] & (~slave_cs)); assign ss[2] = ~(~control[7] & control[6] & ~control[5] & (~slave_cs)); assign ss[1] = ~(~control[7] & ~control[6] & control[5] & (~slave_cs)); assign ss[0] = ~(~control[7] & ~control[6] & ~control[5] & (~slave_cs));/* clock divide */assign spi_clk_gen = clk_divide[divide_factor];/* Clock Divider */always @ (negedge pro_clk) beginclk_divide = clk_divide + 1;end/* Reading the miso line and shifting */always @ (posedge (sclk ^ (CPHA ^ CPOL)) or posedge spi_word_send) begin if (spi_word_send) beginshift_register[7:0] = txdata;end else beginshift_register = shift_register << 1;shift_register[0] <= miso;endend/* Writing the mosi */always @ (negedge (sclk ^ (CPHA ^ CPOL)) or posedge spi_word_send) begin if (spi_word_send) beginmosi = txdata[7];end else beginmosi = shift_register[7];endend/* Contolling the interrupt bit in the status bit */always @ (posedge slave_cs or posedge spi_word_send) begin if (spi_word_send) beginstatus[0] = 0;end else beginstatus = 8'h01;rxdata = shift_register; // updating read buffer endend/* New SPI wrod starts when the transmit buffer is updated */ always @ (posedge pro_clk) beginif (spi_word_send) beginslave_cs <= 0;end else if ((count == 8) & ~(sclk ^ CPOL)) beginslave_cs <= 1;endend/* New Spi word is intiated when transmit buffer is updated */ always @ (posedge pro_clk) beginif (CS & WR & addr[1] & ~addr[0]) beginspi_word_send <=1;end else beginspi_word_send <=0;endend/* Generating the SPI clock */always @ (posedge spi_clk_gen) beginif (~slave_cs) beginsclk = ~sclk;end else if (~CPOL) beginsclk = 0;end else beginsclk = 1;endend/* Counting SPI word length */always @ (posedge sclk or posedge slave_cs) beginif (slave_cs) begincount = 0;end else begincount = count + 1;endend/* Reading, writing SPI registers */always @ (posedge pro_clk) beginif (CS) begincase (addr)2'b00 : if (WR) control <= data_in;2'b01 : if (RD) data_out <= status; // Void2'b10 : if (WR) txdata <= data_in;2'b11 : if (RD) data_out <= rxdata;endcaseendend/* Controlling the data out enable */always @ (RD or data_out) beginif (RD)data_out_en = data_out;elsedata_out_en = 8'bz;endassign data_bus = data_out_en;initialbeginmosi = 0;//sclk = 0;control = 0;count = 0;slave_cs = 1;txdata = 0;rxdata = 0;clk_divide = 0;data_out = 0;endendmodule/********************************************** END ******************************************************************/。