一位二进制全加器

- 格式:doc

- 大小:186.50 KB

- 文档页数:2

1. 导言在数字电路中,全加器是一种常用的逻辑电路,用于将两个输入的二进制数和一个进位输入相加,得到一个输出和一个进位输出。

在本文中,我们将深入探讨全加器的功能和原理。

2. 全加器的功能全加器可以将两个输入的二进制数和一个进位输入相加,得到一个输出和一个进位输出。

具体来说,全加器有三个输入(A、B、Cin)和两个输出(S、Cout),其中A和B分别表示要相加的两个二进制位,Cin表示上一位相加的进位,S表示相加结果的低位,Cout表示相加结果的进位。

3. 全加器电路的原理全加器电路由多个逻辑门组成,包括与门、或门和异或门。

具体而言,全加器电路可以分为两个部分:逻辑部分和进位部分。

逻辑部分通过异或门实现相加的结果,进位部分通过与门和或门实现进位的计算。

4. 从简到繁:如何实现全加器功能为了更好地理解全加器的功能,我们可以先从简单的一位全加器开始。

一位全加器可以通过组合逻辑电路构建,主要由异或门、与门和或门组成。

我们可以进一步扩展到多位全加器,从而实现对更大数字的加法运算。

5. 全加器的应用全加器作为数字电路中的重要组成部分,已经广泛应用于各种领域,包括计算机、通信系统等。

它可以用于实现数字信号的加法运算,从而提供更多的计算和控制功能。

6. 个人观点和总结在我看来,全加器作为一种重要的数字电路,其功能和原理对于理解数字信号处理和计算机系统至关重要。

通过深入研究全加器的功能和原理,我们可以更好地理解数字电路的工作原理,为其在各种应用中提供更加灵活和高效的支持。

7. 结语通过本文的探讨,我们对全加器的功能和原理有了更深入的理解。

全加器作为数字电路中的重要组成部分,其理论和应用价值不可忽视。

希望本文能为读者对全加器有更深入的了解提供帮助。

全加器是数字电路中的重要组成部分,其功能和原理对于理解数字信号处理和计算机系统至关重要。

在本文中,我们对全加器的功能和原理进行了深入探讨,了解了全加器的作用以及其在数字电路中的应用。

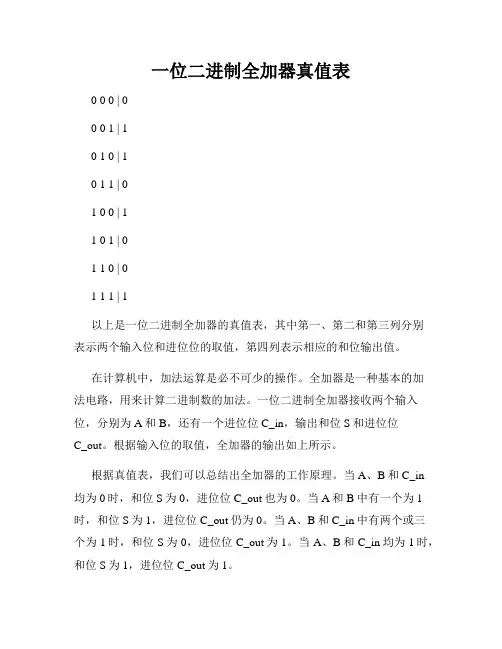

一位二进制全加器真值表0 0 0 | 00 0 1 | 10 1 0 | 10 1 1 | 01 0 0 | 11 0 1 | 01 1 0 | 01 1 1 | 1以上是一位二进制全加器的真值表,其中第一、第二和第三列分别表示两个输入位和进位位的取值,第四列表示相应的和位输出值。

在计算机中,加法运算是必不可少的操作。

全加器是一种基本的加法电路,用来计算二进制数的加法。

一位二进制全加器接收两个输入位,分别为A和B,还有一个进位位C_in,输出和位S和进位位C_out。

根据输入位的取值,全加器的输出如上所示。

根据真值表,我们可以总结出全加器的工作原理。

当A、B和C_in均为0时,和位S为0,进位位C_out也为0。

当A和B中有一个为1时,和位S为1,进位位C_out仍为0。

当A、B和C_in中有两个或三个为1时,和位S为0,进位位C_out为1。

当A、B和C_in均为1时,和位S为1,进位位C_out为1。

全加器的真值表非常重要,因为它可以帮助我们了解加法电路的逻辑运算结果。

在计算机中,多个全加器可以组合成加法器电路,实现更复杂的二进制加法运算。

通过合理设计电路,我们可以用全加器实现多位二进制数的加法,以及其他算术运算,如减法、乘法和除法。

总结一位二进制全加器的真值表及其工作原理,对于理解计算机中的加法运算及其相关电路非常重要。

这个简单的真值表是理解更复杂的二进制加法器的基础,也是学习计算机原理和数字电路设计的必备知识。

通过深入研究和理解真值表,我们可以更好地掌握计算机底层的数学和逻辑运算原理。

整理人 尼克 实验一一位二进制全加器设计实验目录实验一Protel DXP 2004认识实验 (1)实验二两级阻容耦合三极管放大电路原理图设计 (1)实验三原理图元件库建立与调用 (3)实验四两级阻容耦合三极管放大电路PCB图设计 (5)实验五集成电路的逻辑功能测试 (7)实验六组合逻辑电路分析与设计 (12)实验七Quartus II 的使用 (17)实验八组合逻辑器件设计 (17)实验九组合电路设计 (25)实验一 Protel DXP 2004 认识实验一、实验目的1.掌握Prot e l DXP 2004 的安装、启动和关闭。

2.了解Protel DXP 2004 主窗口的组成和各部分的作用。

3.掌握Prot e l DXP 2004 工程和文件的新建、保存、打开。

二、实验内容与步骤1、Protel_DXP_2004 的安装(1)用虚拟光驱软件打开Protel_DXP_2004.iso 文件(2)运行setup\Setup.exe 文件,安装Protel DXP 2004(3) 运行破解程序后,点击“导入模版”,先导入一个ini文件模版(如果要生成单机版的License选择Unified Nexar-Protel License.ini;要生成网络版的License选择Unified Nexar-Protel Network License.ini),然后修改里面的参数:TransactorName=Your Name(将“Your Name”替换为你想要注册的用户名);SerialNumber=0000000(如果你只有一台计算机,那么这个可以不用修改,如果有两台以上的计算机且连成局域网,那么请保证每个License文件中的SerialNumber=为不同的值。

修改完成后点击“生成协议文件”,任意输入一个文件名(文件后缀为.alf)保存,程序会在相应目录中生成1个License文件。

点击“替换密钥”,选取DXP.exe (在DXP 2004安装目录里,默认路径为C:\Program Files\Altium2004\),程序会自动替换文件中的公开密钥。

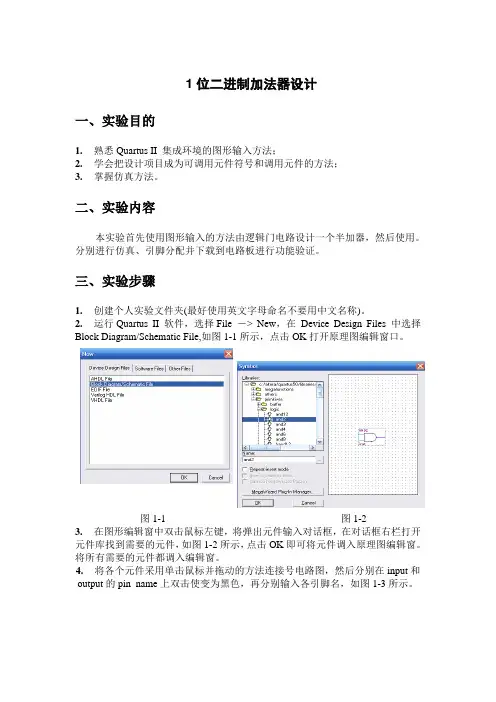

1位二进制加法器设计一、实验目的1.熟悉Quartus II 集成环境的图形输入方法;2.学会把设计项目成为可调用元件符号和调用元件的方法;3.掌握仿真方法。

二、实验内容本实验首先使用图形输入的方法由逻辑门电路设计一个半加器,然后使用。

分别进行仿真、引脚分配并下载到电路板进行功能验证。

三、实验步骤1.创建个人实验文件夹(最好使用英文字母命名不要用中文名称)。

2.运行Quartus II 软件,选择File -> New,在Device Design Files 中选择Block Diagram/Schematic File,如图1-1所示,点击OK打开原理图编辑窗口。

图1-1 图1-23.在图形编辑窗中双击鼠标左键,将弹出元件输入对话框,在对话框右栏打开元件库找到需要的元件,如图1-2所示,点击OK即可将元件调入原理图编辑窗。

将所有需要的元件都调入编辑窗。

4.将各个元件采用单击鼠标并拖动的方法连接号电路图,然后分别在input和output的pin_name上双击使变为黑色,再分别输入各引脚名,如图1-3所示。

图1-35.选择File—>Save As命令,选择为此工程已建好目录,将设计好的原理图文件取名为h_adder.bdf同时使下方小框内出现“√”,点击保存会弹出“是否创建新工程”提示信息如图1-4所示。

图1-4图1-56.创建一个新工程:点击图1-4中“是”可进入创建工程向导(也可以File -> New project Wizard进入向导),此时看到的默认工程名、顶层实体名都为h_adder,此时将工程名换为f_adder顶层实体名不变,如图1-5所示。

点击NEXT,再在弹出窗中点击NEXT,选择目标器件:MAXII 系列EPMT1005C芯片。

按照下列的方法完成半加器的编译、仿真。

7.7. 创建一个仿真波形文件:File -> New,在Other Files 中选择Vector Waveform File,如图1-6,进入波形编辑窗口。

d电路功能为1位二进制数全加器在数码世界中,电路功能为1位二进制数的全加器扮演着至关重要的角色。

全加器是计算机和其他电子设备中常用的逻辑电路,用于将两个二进制数相加,并考虑到进位。

本文旨在通过深入探讨全加器的功能和原理,帮助读者更好地理解其在电子领域的重要性。

一、全加器的基本功能全加器是一种具有三个输入(A、B和进位Cin)和两个输出(和S以及进位Cout)的逻辑电路。

其主要功能是将两个单独的二进制数相加,并考虑到可能存在的进位。

当我们需要将两个数字相加时,全加器可以提供一个完整的解决方案,确保计算的准确性和完整性。

二、全加器的原理解析1. 输入部分:全加器有三个输入引脚,分别对应要相加的两个二进制数(A和B),以及从上一位传递过来的进位(Cin)。

2. 处理部分:通过逻辑门电路的组合和运算,全加器能够按照规定的运算法则,将输入的二进制数进行相加,并输出相加的结果和可能的进位。

3. 输出部分:全加器有两个输出引脚,分别用来输出相加的结果(和S)和可能的进位(Cout)。

通过以上原理解析,我们可以更清晰地理解全加器的工作方式和实现原理。

三、全加器的应用领域全加器是计算机及电子设备中的基本组成部分,广泛应用于各类数字电路中,如ALU(算术逻辑单元)、加法器和减法器等。

在进行数字运算的过程中,全加器能够提供准确的计算结果,并保证数字的正确性和可靠性。

全加器在信息处理、通信、控制系统等领域都有着重要的应用价值。

四、个人观点和理解全加器作为计算机及电子设备中的基本组成部分,扮演着至关重要的角色。

它不仅提供了数字运算的基础支持,还为数字系统的稳定运行和高效计算提供了坚实的基础。

在未来的发展中,随着数字化技术的不断进步,全加器的功能和作用将变得愈发重要,对于计算机科学和工程技术也将产生深远的影响。

总结回顾通过本文的阐述,我们对全加器的功能和原理有了更深入的理解。

全加器作为一种基本的逻辑电路,在数字系统中有着广泛的应用,并为数字运算提供了可靠的基础支持。

一位二进制全加器电路设计设计一个二进制全加器电路,听上去是不是有点高深?别担心,让我们轻松聊聊这个话题!全加器,顾名思义,就是用来加数字的。

我们知道,二进制就是零和一,简单又直接。

想象一下,如果你有两个数字,比如说 0 和 1,想把它们加在一起,全加器就像是你身边的小助手,轻松搞定。

你可能会问,全加器到底怎么工作的呢?其实很简单,它有三个输入,两个是要加的数字,另一个是进位。

然后,它会输出一个和以及可能的进位。

就像你在朋友家聚会,大家一起分享食物,有时候多出来的盘子得另找地方放。

怎么设计一个全加器电路呢?首先得搞清楚真值表,这是一个神奇的表格,它把所有可能的输入和对应的输出都列出来。

就像是你的购物清单,列出你要买的每一样东西。

比如说,如果两个输入都是 0,进位也是 0,输出当然是 0。

再比如,输入是 1 和 0,进位为 0,那输出就会是 1。

再往下看,如果两个输入都是 1,那就得看看进位了。

这就像是在厨房忙碌,偶尔得看看烤箱里的蛋糕,确保它不会烤焦。

设计电路的时候,你得选用逻辑门。

常见的有与门、或门和非门。

想象一下,逻辑门就像是开关,你可以通过这些开关来控制电流的流动。

与门就像是要求所有的朋友都到齐才能开始聚会,而或门则是只要一个人到就行,非门就是调皮的那位朋友,总是反着来。

通过组合这些逻辑门,就能实现我们的全加器。

接下来是连接这些门,得小心翼翼,不然就像你在拼积木,拼错了就没法再玩了。

我们把两个输入连接到与门和或门,进位也得适当地连接上。

这样一来,所有的开关就齐齐整整,准备好接受输入,输出你期待的结果。

别忘了,布局得整齐,这样电路才能正常工作。

就像你的书桌,整洁才能专注。

还有一个小秘诀,利用Karnaugh图简化逻辑表达式。

这个图就像是拼图游戏,把复杂的逻辑关系变得简单明了,帮助我们找到最优的电路设计。

你看,设计电路并不复杂,只要一步一步来,就像学骑自行车,摔几次之后就能掌握平衡。

测试电路是非常重要的。

一位全加器的实验报告一位全加器的实验报告摘要:本实验旨在通过搭建一位全加器电路,探究数字电路中的加法运算原理。

通过实验,我们成功验证了全加器的功能,并观察到了其在二进制加法中的作用。

实验结果表明,全加器是一种重要的数字电路元件,能够实现多位二进制数的相加运算。

引言:全加器是一种常见的数字电路元件,用于实现二进制数的相加运算。

它能够处理两个输入位和一个进位位,并输出一个和位和一个进位位。

全加器的设计和实现对于数字电路的理解和应用具有重要意义。

本实验将通过搭建一位全加器电路,探究其工作原理和应用。

材料与方法:1. 逻辑门:与门、或门、异或门、非门2. 连线材料:导线、电源线3. 电源:直流电源4. 示波器:用于观察电路输出波形实验步骤:1. 按照电路图搭建一位全加器电路,包括两个输入位A和B,一个进位位Cin,一个和位S和一个进位位Cout。

2. 将电源线连接至电路,确保电路正常供电。

3. 分别将输入位A和B的电平信号输入到与门和异或门中,将进位位Cin的电平信号输入到与门中。

4. 将与门和异或门的输出信号输入到或门中,得到和位S的输出信号。

5. 将与门的输出信号输入到与非门中,得到进位位Cout的输出信号。

6. 使用示波器观察和位S和进位位Cout的波形。

结果与讨论:通过实验观察,我们得到了一位全加器的输出波形。

当输入位A和B均为0时,和位S和进位位Cout均为0;当输入位A和B均为1时,和位S为0,进位位Cout为1;当输入位A和B中有一个为1时,和位S为1,进位位Cout为0;当输入位A和B均为1时,和位S和进位位Cout均为1。

这一结果与全加器的逻辑运算规则相符,验证了全加器电路的正确性。

全加器在二进制加法中起到了关键作用。

通过将多个全加器连接起来,我们可以实现多位二进制数的相加运算。

在实际应用中,全加器被广泛应用于计算机的算术逻辑单元(ALU)中,用于实现加法和其他运算。

结论:通过本实验,我们成功搭建了一位全加器电路,并验证了其在二进制加法中的功能。

实验一基于原理图输入法的1位二进制全加器的设计一、实验目的1、学习、掌握QuartusⅡ开发平台的基本使用。

2、学习基于原理图输入设计法设计数字电路的方法,能用原理图输入设计法设计1位二进制半加器、1位二进制全加器。

3、学习EDA-V型实验系统的基本使用方法。

二、实验内容1、根据1位二进制半加器、1位二进制全加器的真值表,设计并画出1位二进制半加器的原理框图,由半加器及门电路设计并画出1位二进制全加器的原理框图(最终设计的是1位二进制全加器)。

2、用QuartusⅡ原理图输入输入法输入1位二进制半加器的原理框图,并进行编译。

如有输入错误,修改后再进行编译。

4、根据1位二进制半加器的工作原理,选择输入合适的输入信号和波形及其输出信号,进行仿真,得到器件的输入与输出波形,验证设计是否正确。

5、创建1位二进制半加器的的元件图形符号。

6、用QuartusⅡ原理图输入输入法输入1位二进制半加器的原理框图(要求用半加器及门电路设计),并进行编译,仿真。

7、确定实验箱电源关闭的情况下,连接好下载线,然后打开实验箱电源,对器件进行编程下载。

8、编程下载成功后,关闭实验箱电源,拆除下载线,按器件引脚设定及功能要求,连接好各测试线,进行硬件测试验证。

三、实验预习要求1、学习、掌握QuartusⅡ的基本使用,学习本EDA-V实验开发系统。

2、根据1位二进制半加器、1位二进制全加器的真值表,设计并画出1位二进制半加器的原理框图,由半加器及门电路设计并画出1位二进制全加器的原理框图。

3、根据1位二进制半加器、1位二进制全加器的工作原理,设计并画出它们的输入、输出的理论工作波形。

4、初步制定全加器的引脚锁定。

四、实验要求1、实验原理中详细写出1位二进制半加器、1位二进制全加器的设计过程,及它们的输入、输出的理论工作波形。

2、根据实验内容,详细写出实验的各个步骤,方法。

3、记录实验现象或波形,并与理论值比较、分析。

(如仿真波形与理论工作波形的比较分析,硬件测试与理论真值表的比较分析)。

1.只用一个1位二进制全加器为基本元件和一些辅助的时序电路,设计一个8位串行二进制全加器半加器(VHDL)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_adder ISPORT ( a , b : IN STD_LOGIC ;co, so : OUT STD_LOGIC );END ENTITY h_adder;ARCHITECTURE one OF h_adder ISBEGINso<=NOT(a XOR (NOT b)); co <= a AND b ;END ARCHITECTURE one;D触发器(VHDL)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DFF1 ISPORT ( CLK : IN STD_LOGIC;D : IN STD_LOGIC;Q : OUT STD_LOGIC); END;ARCHITECTURE bhv OF DFF1 IS SIGNAL Q1 : STD_LOGIC; BEGINPROCESS( CLK,D)BEGINIF CLK='1'THEN Q1<=D;END IF;END PROCESS;Q<=Q1;END bhv;串并移位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHFRT1 ISPORT (CLK,LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR( 7 DOWNTO 0);QB : OUT STD_LOGIC );END SHFRT1;ARCHITECTURE behav OF SHFRT1 ISBEGINPROCESS( CLK, LOAD)VARIABLE REG8 : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGINIF CLK'EVENT AND CLK = '1' THENIF LOAD='1' THEN REG8 :=DIN;ELSE REG8(6 DOWNTO 0) :=REG8 (7 DOWNTO 1); END IF;END IF;QB <=REG8(0);END PROCESS;END behav;并串移位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHFRT ISPORT (CLK : IN STD_LOGIC;DIN : OUT STD_LOGIC_VECTOR( 15 DOWNTO 8);QB : IN STD_LOGIC );END SHFRT;ARCHITECTURE behav OF SHFRT ISBEGINPROCESS( CLK )VARIABLE REG8 : STD_LOGIC_VECTOR(15 DOWNTO 8); BEGINIF CLK'EVENT AND CLK = '1'THEN REG8(8) := QB;REG8(15 DOWNTO 9) :=REG8 (14 DOWNTO 8); END IF;END PROCESS;END behav;2.用一位全加器为基本单元设计8位并行的全加器程序2:一位二进制全加器设计顶层描述功能:程序功能简介程序3:8位并行二进制全加器顶层文件功能:程序功能简介。

大学实验报告学生: 学 号: 专业班级: 中兴101实验类型:■ 验证 □ 综合 □设计 □ 创新 实验日期: 2012 9 28 实验成绩:实验一 一位二进制全加器设计实验一.实验目的(1)掌握Quartus II 的VHDL 文本设计和原理图输入方法设计全过程; (2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果; (3) 熟悉设备和软件,掌握实验操作。

二.实验容与要求(1)在利用VHDL 编辑程序实现半加器和或门,再利用原理图连接半加器和或门完成全加器的设计,熟悉层次设计概念;(2)给出此项设计的仿真波形;(3)参照实验板1K100的引脚号,选定和锁定引脚,编程下载,进行硬件测试。

三.设计思路一个1位全加器可以用两个1位半加器及一个或门连接而成。

而一个1位半加器可由基本门电路组成。

(1) 半加器设计原理能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

图1为半加器原理图。

其中:a 、b 分别为被加数与加数,作为电路的输入端;so 为两数相加产生的本位和,它和两数相加产生的向高位的进位co 一起作为电路的输出。

半加器的真值表为表1 半加器真值表absoco0 0 0 0 0 1 1 0 1 0 1 0 111由真值表可分别写出和数so ,进位数co 的逻辑函数表达式为:b a b a b a so ⊕=+=--(1)ab co = (2)图1半加器原理图(2) 全加器设计原理除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

图2全加器原理图。

全加器的真值表如下:表2全加器真值表c a b co so0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 1其中a为加数,b为加数,c为低位向本位的进位,co为本位向高位的进位,so为本位和。

一位全加器工作原理

一位全加器的工作原理是:全加器是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

一位全加器可以处理低位进位,并输出本位加法进位。

多个一位全加器进行级联可以得到多位全加器。

全加器有两个输入和两个输出:输入是加数A、加数B和进位输入Cin;输出是和数Sum和进位输出Cout。

其中,和数Sum是A和B 相加的结果,进位输出Cout表示向高位的进位。

一位全加器的逻辑表达式为:Sum=A⊕B⊕Cin;Cout=(A∧B)∨(B ∧Cin)∨(A∧Cin),其中⊕表示异或运算,∧表示与运算,∨表示或运算。

一位全加器可以用两个一位半加器和一个或门连接而成。

而一个一位半加器可由基本门电路组成。

半加器只能实现和数的运算,对于1+1=10的进位运算,需要用到全加器。

全加器在设计时需要考虑到电路的功能、性能和可靠性等方面。

在实际应用中,全加器被广泛用于计算机和其他数字系统中,是实现数字电路的重要基础之一。

实验⼆:⼀位⼆进制全加器的设计实验2:Quartus II的⽂本输⼊设计练习——⼀位⼆进制全加器的设计⼀、实验⽬的(1)学习Quartus II软件的基本使⽤⽅法;(2)学习EDA实验开发系统的基本使⽤⽅法;(3)了解VHDL程序的基本结构。

⼆、实验内容设计并调试好⼀个1位⼆进制全加器,并⽤EL—EDA—V型EDA实验开发系统(拟采⽤的实验芯⽚的型号为EP1K100QC208—3)进⾏系统仿真、硬件验证。

设计1位⼆进制全加器结构体时要求采⽤结构描述、数据流描述和⾏为描述三种⽅式。

附加内容:以1位⼆进制全加器为基本元件,⽤元件例化语句写出4位⼆进制全加器的顶层⽂件。

三、实验条件(1)电脑。

(2)开发软件:Quartus II(3)开发设备:EL —EDA—V型;EDA实验开发系统。

(4)拟⽤芯⽚:ACEX1K;EP1K100QC208-3。

四、实验设计1)数据流描述library IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity NO2 isport(A,B,C : in STD_LOGIC;S,CO : out STD_LOGIC);end NO2;-- Use Clause(s) (optional)architecture G of NO2 isSIGNAL TEMP:STD_LOGIC;beginTEMP<=A XOR B;S <= TEMP XOR C;CO<=(TEMP AND C)OR(A AND B);end G;2)⾏为描述- LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity F_ ADDER isport( A,B,C :in STD_LOGIC;S,CO :out STD_LOGIC);end F_ADDER;ARCHITECTURE a OF F_ADDER_1 ISSIGNAL SUM,A1,B1,C1:STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN A1<=’0’&AB1<=’0’&BC1<=’0’&CSUM<=SUM(0);CO<=SUM(1);END a;3)结构描述顶层LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity F_ ADDER isport( A,B,C :in STD_LOGIC;S,CO :out STD_LOGIC);end F_ADDER;ARCHITECTURE a OF F_ADDER_1 ISCOMPINENT XOR_1PORT (A1,B1: IN STD_KOGIC;C1: OUT STD_LOGIC);END COMPONENT;COMPINENT NAND_2PORT (A1,B1: IN STD_KOGIC;C1: OUT STD_LOGIC);END COMPONENT;SIGNAL S1,S2,S3:STD_LOGIC;BEGINU1:XOR_1 PORT MAR(A,B,S1);U2:XOR_1 PORT MAR(S1,C,S);U3:NAND_2 PORT MAR(A1=>S1,B1=>C,C1=>S2); U4:NAND_2 PORT MAR(A1=>A,B1=>B,C1=>S3); U5:NAND_2 PORT MAR(A1=>S2,B1=>S3,CO); END a;底层LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity XOR_1 isport( A1,B1 :in STD_LOGIC;C1 :out STD_LOGIC);end XOR_1;ARCHITECTURE b OF XOR_1 ISBEGINC1<=A1 XOR B1;END b;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity NAND_2 isport( A1,B1 :in STD_LOGIC;C1 :out STD_LOGIC);end NAND_2;ARCHITECTURE c OF NAND_2 IS BEGINC1<=A1 NAND B1;END c;4)仿真波形5)管脚锁定全加器引脚 A B C S COPin7 Pin8 Pin9 Pin37 Pin36 EP1K100QC208-3芯⽚EDA实验开发d2 d1 d0 LED1 LED0 系统五、实验结果及总结1)系统仿真情况从系统仿真结果可以看出,本系统完全符合设计要求,同时从系统时序仿真结果可以看出符合实验。

什么是全加器全加器工作原理

什么是全加器全加器工作原理

全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出

和的组合线路,称为一位全加器。

一位全加器可以处理低位进位,并输出本位加法进位。

多个一位全加器进行级联可以得到多位全加器。

常用二进制四位全加器74LS283。

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。

而其功能设计可以根据组合逻辑电路的设计方法来完成。

通过逻辑门、74LS138译码器、74LS153D 数据选择器来实现一位全加器的电路设计,并且实现扩展的两位全加器电路。

并且Multisim是一个专门用于电路设计与仿真的工具软件。

它以界面形象直观、操作方便、分析功能强大、易学易用等突出优点,迅速被推广应用。

全加器工作原理

全加器是能够计算低位进位的二进制加法电路。

与半加器相比,全加器不

只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.。

一位全加器原理

一位全加器原理是一种电子电路,用于将两个二进制数码相加,并生成一个和值和一个进位值。

这种电路在数字逻辑电路中非常常见,通常用于构建更复杂的算术和逻辑操作单元。

一位全加器的输入包括两个二进制数码(A和B)和上一个加

法进位(Cin),输出包括和值(S)和当前进位(Cout)。

这种电路通过使用异或门(XOR)、与门(AND)和或门(OR)来实现。

在实际电路中,异或门用于计算和值,而使用与门和或门进行进位计算。

具体地,输入A和B与异或门相连,输出连接到

和值输出端。

输入A和B还与一个与门相连,输出连接到进

位计算中的或门。

另外,A和B还通过一个与门和前一位的

进位输入Cin连接到另一个与门,输出连接到进位输出端。

通过这种方式,一位全加器可以在一个时钟周期内完成两个二进制数码的相加操作,并生成和值和进位。

这种电路可以通过级联多个一位全加器来实现更大规模的二进制数码相加。

需要注意的是,一位全加器只能进行单位数字相加,对于多位数的加法操作,需要使用多个一位全加器级联起来。

这样,多位数的加法操作可以拆分成多个一位数的相加操作。

一位二进制全加器

对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”的逻辑电路称为全加器。

由此可知,全加器有三个输入端,二个输出端,其真值表如表8-15所示。

其中Ai、Bi分别是被加数、加数,Ci-1是低位进位,Si为本位全加和,C i为本位向高位的进位方法是由真值表列逻辑表达式画电路图值表如下

A i

B i

C i-1S i C i

0 0000

00110

01010

01101

10010

10101

11001

11111

由真值表可分别写出输出端Si和Ci的逻辑表达式

Si=Ai BiCi-1+AiBiCi-1+ AiBi Ci-1+ AiBiCi-1

= Ai(BiCi-1+ BiCi-1)+ Ai(BiCi-1+ BiCi-1)

= Ai(Bi⊕Ci-1 )+ Ai(Bi⊕Ci-1)

=Ai⊕Bi⊕Ci-1

Ci= Ai BiCi-1+ AiBiCi-1+Ai BiCi-1+ AiBiCi-1

= Ai( Bi⊕Ci-1)+BiCi-1(Ai+ Ai)

= Ai( Bi⊕Ci-1)+BiCi-1

= Ai( Bi⊕Ci-1) BiCi-1由逻辑表达式可设计电路Si和Ci加的逻辑表达式中有公用项,因此,在组成电路时,可令其共享同一异或门,从而使整体得到进一步简化。

一

位全加器的逻辑电路图和逻辑符此为异或门芯片为74ls86

此为或非门芯片为74ls00从上至下

号如图所示。