实验十进制加减法计数器

- 格式:doc

- 大小:99.00 KB

- 文档页数:3

时序电路逻辑设计实验人:周铮班级:中法1202班学号:U201215676一实验目的1.掌握用SSI实现简单组合逻辑电路的方法。

2.掌握简单数字电路的安装与测试技术。

3.熟悉使用Verilog HDL描述组合逻辑电路的方法,以及EDA仿真技术。

二实验器件计算机,可编程实验板三实验内容十进制加减可逆计数器设计功能要求:拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9—8—7—...0—1...的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。

即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9——0—1...的模十加计数结果;当SW0为LOW时,计数器实现模十减计数功能,即4个七段数码管上几乎同步显示9—8—7—...—1—0— (9)—8—7…的模十减计数结果。

四实验设计1.原理设计脉冲发生电路采用555定时器组成的多谐振荡器振荡产生周期为1s的矩形脉冲,从而为计数器提供触发信号。

其中,可以通过R1,R2,C来控制充放电的时间。

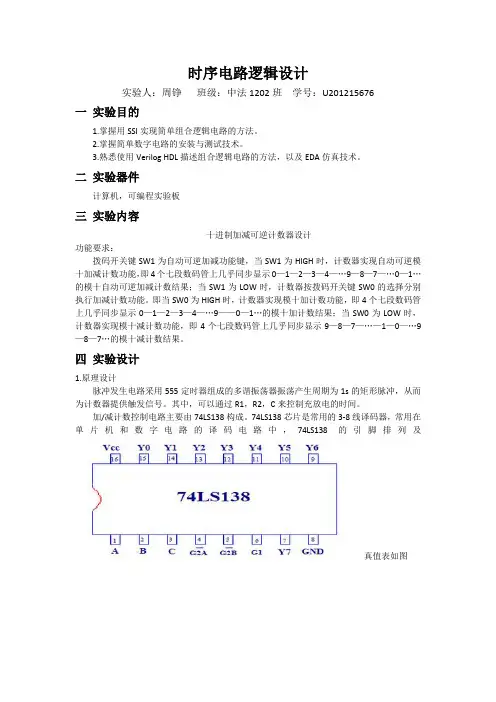

加/减计数控制电路主要由74LS138构成。

74LS138芯片是常用的3-8线译码器,常用在单片机和数字电路的译码电路中,74LS138的引脚排列及真值表如图计数单元电路主要由十进制计数器74LS192构成。

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列图如图功能表如图2.模拟仿真用Verilog HDL语言设计二通道数据选择器实验程序如下:①实验代码module a(input clk,input SW1,input SW0,input clear,input reset,output reg[3:0] s1_reg,output reg[6:0] segdat_reg);reg[26:0] counter;reg[3:0]q;reg x;always@(posedge clk)beginif(clear) begins1_reg<=0;counter<=0;endelsecounter<=counter+1;endalways@(posedge counter[26])beginif (reset) beginq<=0;x<=0;endelsebegincase(SW1)1'd1:begincase(x)1'd0: beginif(q==4'd8)x<=1;q<=q+1;end1'd1: beginif(q==4'd1)x<=0;q<=q-1;endendcaseend1'd0:begincase(SW0)1'd0:beginif(q==4'd0)q<=4'd9;elseq<=q-1;end1'd1:beginif(q==4'd9)q<=4'd0;elseq<=q+1;endendcaseendendcaseendendalways@(q) // 数码管显示处理begincase(q)4'h0:segdat_reg = 7'b0000001; //04'h1:segdat_reg = 7'b1001111; //14'h2:segdat_reg = 7'b0010010; //24'h3:segdat_reg = 7'b0000110; //34'h4:segdat_reg = 7'b1001100; //44'h5:segdat_reg = 7'b0100100; //54'h6:segdat_reg = 7'b0100000; //64'h7:segdat_reg = 7'b0001111; //74'h8:segdat_reg = 7'b0000000; //84'h9:segdat_reg = 7'b0000100; //9default:segdat_reg=7'b0111000; //Fendcaseendendmodule②测试文件test代码module test;// Inputsreg clk;reg SW1;reg SW0;reg clear;reg reset;// Outputswire [3:0] s1_reg;wire [6:0] segdat_reg;// Instantiate the Unit Under Test (UUT)a uut (.clk(clk),.SW1(SW1),.SW0(SW0),.clear(clear),.reset(reset),.s1_reg(s1_reg),.segdat_reg(segdat_reg));initial begin// Initialize Inputsclk = 0;SW1 = 0;SW0 = 1;clear = 1;reset = 1;// Wait 100 ns for global reset to finish#100;// Add stimulus hereendendmodule③管脚设置ucf文件代码# PlanAhead Generated physical constraintsNET "SW0" LOC = P11;NET "SW1" LOC = L3;NET "clear" LOC = K3;NET "clk" LOC = B8;NET "reset" LOC = B4;NET "segdat_reg[0]" LOC = M12;NET "segdat_reg[1]" LOC = L13;NET "segdat_reg[2]" LOC = P12;NET "segdat_reg[3]" LOC = N11;NET "segdat_reg[4]" LOC = N14;NET "segdat_reg[5]" LOC = H12;NET "segdat_reg[6]" LOC = L14;NET "s1_reg[0]" LOC = F12;NET "s1_reg[1]" LOC = J12;NET "s1_reg[2]" LOC = M13;NET "s1_reg[3]" LOC = K14;# PlanAhead Generated IO constraintsNET "clk" SLEW = FAST;④模拟仿真顶层原理图⑤模拟仿真波形图五实验心得本次实验要求用Verilog HDL语言做出十进制可逆加减计数器并进行模拟仿真,其中在代码部分出现多次bug,后经过仔细检查发现是测试文件未加限制的原因,最终做出了模拟仿真。

十进制加减计数器集成电路软件设计实验二:十进制加减计数器实验地点实验时间学院班级姓名学号成绩指导老师年月日一、设计任务1、设计十进制加减计数器;2、练习使用Modelsim软件和Synopsys公司的Design Compiler软件。

二、设计要求1、十进制加减计数器;2、控制端口控制加与减的计数;3、输入时钟的频率自定,符合设计即可三、预习要求编写加减计数器的VHDL代码; library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity counter isport(clk ,up: in std_logic; q: outinteger ); end ;architecture one of counter issignal count :integer range 0 to 99; beginprocess(clk) beginif clk'event and clk='1' then if up='1' thenif count=99 then count<=0; else count<=count+1; end if ;elsif up='0' thenif count=0 then count<=29; else count<=count-1; end if ; end if; end if; end process ;q<=count; end ;四、实验报告使用Modelsim软件编译并仿真加减计数器的VHDL代码,编写Testbench,给出仿真结果;LIBRARY ieee ;USE ieee.std_logic_1164.all ; USE ieee.std_logic_unsigned.all ; ENTITY testbench ISEND ;ARCHITECTURE counter_tb_arch OF testbench IS SIGNAL q :integer range 0to 99 ; SIGNAL up:std_logic :='1'; SIGNAL clk:std_logic :='0'; COMPONENT counterPORT (clk,up: in std_logic;q:out integer range 0 to 99 ); END COMPONENT ; BEGINDUT : counterPORT MAP ( q=> q ,up=> up ,clk => clk ) ; process(clk)begin clk <= not clk after 20ns; end process;up <= '0' after 1000ns; END ;五、仿真波形通过VHDL代码的编译成功和testbench的编写并对其编译、仿真,其仿真结果如下图所示:六、网表电路使用Design Compiler软件将加减计数器的VHDL代码综合成网表电路;七、对比综合后的网表电路与前期VHDL代码,检查一致性。

74ls193十进制加减减法计数器电路74LS193是一种十进制加减计数器电路,它具有广泛的应用。

本文将详细介绍74LS193的工作原理和功能特点。

1.74LS193的工作原理74LS193是一种四位二进制计数器,它可以实现十进制的加减减法操作。

通过在输入端接入由控制信号和时钟信号控制的二进制数据输入,74LS193可以根据输入信号的变化实现不同的计数操作。

2.74LS193的功能特点(1)四位计数器:74LS193是一种四位计数器,可以用来计算0到9之间的数字。

(2)加减减法功能:74LS193不仅可以进行加法运算,还可以实现减法运算。

通过控制端的输入信号,可以选择进行加法或减法操作。

(3)同步计数:74LS193采用同步计数方式,即在时钟信号的控制下,所有计数位同时进行计数,确保了计数的准确性。

(4)输出显示:74LS193的输出端有四个计数位和进位输出位,可以实时显示计数结果。

3.74LS193的应用领域(1)计数器:由于其计数功能,74LS193广泛应用于各类计数器电路中,如频率计数器、电子表、工业自动化等。

(2)加减器:由于其加减减法功能,74LS193也可以应用于数字加减运算器中,如数字计算机、计算器等。

(3)时序控制:74LS193也可以用于时序控制电路中,通过对计数信号的控制,实现时序操作,如时钟分频、频率分析等。

本文介绍了74LS193十进制加减减法计数器电路的工作原理和功能特点。

74LS193是一种四位二进制计数器,具有加减减法功能,采用同步计数方式,输出结果准确可靠。

它在计数器、加减器和时序控制电路等领域有着广泛的应用。

通过深入理解和熟练运用74LS193,我们可以设计出高效、稳定的数字电路系统,满足不同应用的需求。

总结用74ls192集成计数器组成n位十进制加减法器

方法

74ls192集成计数器是一种常用的数字电路元件,可以用来组成n位

十进制加减法器。

其原理是通过将多个74ls192集成计数器连接起来,实现对数字的计数和加减运算。

具体实现方法如下:

1. 对于n位十进制加法器,需要使用n个74ls192集成计数器。

每个74ls192集成计数器都可以实现对一个十进制数位的计数,因此需要

将它们连接起来,形成一个n位的计数器。

2. 对于加法运算,需要将两个n位的十进制数相加。

可以将它们分别

输入到两个n位十进制加法器中,然后将它们的输出相加,得到最终

的和。

3. 对于减法运算,需要将两个n位的十进制数相减。

可以将它们分别

输入到两个n位十进制加法器中,然后将其中一个数取反,再将它们

的输出相加,得到最终的差。

4. 在实现加减法运算时,需要考虑进位和借位的问题。

可以使用

74ls192集成计数器的进位和借位输出来实现。

5. 在连接多个74ls192集成计数器时,需要注意它们的时钟信号和复位信号的连接方式。

可以使用串行连接或并行连接的方式。

总之,使用74ls192集成计数器组成n位十进制加减法器是一种简单而有效的方法,可以实现对数字的计数和加减运算。

在实际应用中,需要根据具体的需求和电路设计来选择合适的连接方式和电路元件,以实现最佳的性能和可靠性。

摘要计数器是数字电路中最为基本的一个单元电路。

本次基础强化的目标是要我们熟悉常用MSI集成计数器的功能和应用;掌握利用集成计数器构成不同功能的计数器的设计方法;学会利用EDA软件(Proteus)对模M的可逆计数器电路进行仿真;掌握可逆计数器电路的安装及调试方法。

本次课设报告先是说明了十进制加/减可逆计数器的技术指标,简要地陈述了设计方案和设计思路,然后就对其有关理论知识作了一些简要的介绍,然后在性能指标分析基础上进行单元电路设计,设计出整体电路图并且在软件Proteus中进行仿真,最后通过protel 做出电路板验证是否达到技术要求,总结课设体会。

关键词:手动控制,自动控制,计数器,加减可逆目录摘要 (1)1设计任务与要求 (3)2设计方案及其比较 (3)2.1 设计方案 (3)2.2设计思路 (4)2.2.1手控自动加、减计数器设计思路 (4)2.2.2自控可逆方式计数器设计思路 (4)2.2.3手动脉冲设计思路 (5)2.3集成电路及元件选择 (6)3实现方案 (6)3.1 脉冲发生电路实现方案 (6)3.1.1 基本原理 (6)3.1.2 有关参数及计算 (7)3.2 加/减/计数器控制电路实现方案 (7)3.3 自动控制可逆计数器实现方案 (9)3.4译码显示单元电路设计实现方案 (10)3.4.1译码显示单元电路设计 (10)3.4.2译码器74LS48 (11)3.4.3显示器LG5011AH (12)3.4.4译码显示电路 (13)3.5 手动脉冲发生电路实现方案 (14)3.6 清零功能实现方案 (15)3.7 总原理图的设计实现方案 (16)4 Proteus仿真 (17)5 制版与调试 (18)5.1 DXP注意事项 (18)5.2 制作PCB板的流程 (19)5.3 注意事项 (19)5.4 调试结果与分析 (19)6 课设总结 (20)谢辞 (21)参考文献 (22)附录 (23)1设计任务与要求设计一个十进制加/减可逆计数器。

实验报告课程名称:EDA技术与FPGA应用设计课设题目:2位十进制计数器实验地点:信息学院楼CPLD实验室专业班级:学号:学生姓名:指导教师:张文爱2016年4月1日实验二2位十进制计数器一、实验目的1.熟悉ispDesignEXPERT System、QuartusII的原理图设计流程的全过程。

2.学习简单时序电路的设计方法。

3.学习EDA设计的仿真和硬件测试方法。

二、实验原理2位十进制计数器参考原理图如图1所示,也可以采用其他元件实现。

图1.用74LS390设计一个有时钟使能的2位十进制计数器三、实验任务(1)设计2位十进制计数器电路。

(2)在EDA环境中输入原理图。

(3)对计数器进行仿真分析、引脚锁定、硬件测试。

四、实验步骤1、设计电路原理图设计含有时钟使能及进位扩展输出的十进制计数器。

可以选用双十进制计数器74LS390或者十进制计数器74LS160和其他一些辅助元件来完成。

2、计数器电路的实现。

绘制过程中应特别注意图形设计规则中信号标号和总线的表达方式。

若将一根细线变成一粗线显示的总线,可以先单机使其变红,再选Option选项中的Line Style;若在某线上加信号标号,也应该点击该线某处使其变成红色,然后键入标号名称,标有相同标号的线段可视为连接线段,不必直接连接。

总线可以以标号方式进行连接。

3、编程测试。

五、实验结果图2.用74LS390设计一个有时钟使能的2位十进制计数器六、实验感想通过本次实验学会了简单时序电路的设计方法。

学会了使用QuartusII软件调用元器件库进行原理图设计的方法和设计流程。

这次实验让我学会了用FPGA设计电路并且学会了FPGA的设计过程和实现方法。

提高了动手能力,加深了对所学知识的理解。

这次EDA实验,提高了动手能力,加深了对所学知识的理解。

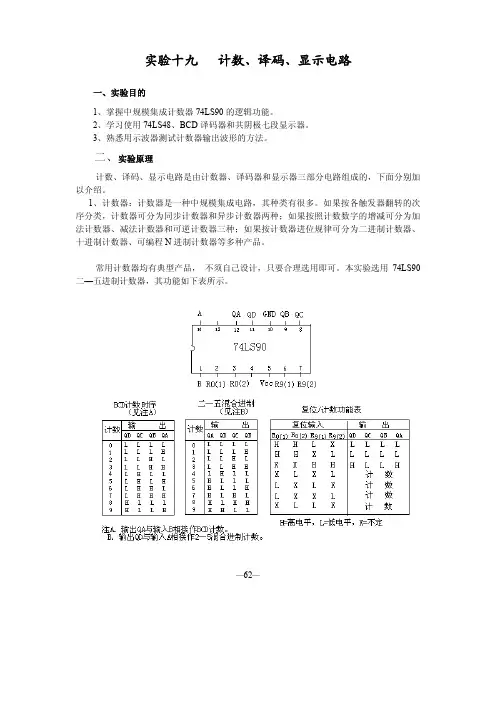

实验十九 计数、译码、显示电路一、实验目的1、掌握中规模集成计数器74LS90的逻辑功能。

2、学习使用74LS48、BCD译码器和共阴极七段显示器。

3、熟悉用示波器测试计数器输出波形的方法。

二、 实验原理计数、译码、显示电路是由计数器、译码器和显示器三部分电路组成的,下面分别加以介绍。

1、计数器:计数器是一种中规模集成电路,其种类有很多。

如果按各触发器翻转的次序分类,计数器可分为同步计数器和异步计数器两种;如果按照计数数字的增减可分为加法计数器、减法计数器和可逆计数器三种;如果按计数器进位规律可分为二进制计数器、十进制计数器、可编程N进制计数器等多种产品。

常用计数器均有典型产品,不须自己设计,只要合理选用即可。

本实验选用74LS90二—五进制计数器,其功能如下表所示。

6263(1) R 0(1)和R 0(2)为直接复位端,R 9(1)和R 9(2)为直接置位端,可以预置数字“9”(Q D = Q A = 1,Q B = Q C = 0)。

(2) A 为二分频计数器的输入,Q A 的输出频率为CP A 的1/2。

B 为五进制计数器的输入,把Q A 输出作为五进制计数器B 的输入,即构成8421BCD 码十进制计数器。

2、 译码器:这里所说的译码器是将二进制数译成十进制数的器件。

我们选用的74LS48是BCD 码七段译码器兼驱动器。

其外引线排列图和功能表如下所示。

1234567891011121314GNDVCC 74LS48B1615CLTBI/RBORBIDAgabcdef十进制数 或功能输 入LT RBI D C B A 0123H H H H H X X X L L L L L L L H L L H L L L H H BI/RBO H H H H 输 出a b c d e f g H H H H H H L L H H L L L L H H L H H L H H H H H L L H 字 型注4567H H H H X X X X L H L L L H L H L H H L L H H H H H H H L H H L L H H H L H H L H H L L H H H H H H H H L L L L H H H X X X H L L L H L L H H L H L H H H H H H H H H H H H H L L H H L L L H H L H L L H H L L H 891011H X H L H H H H H H X X X H H L L H H L H H H H L H H H L H L L L H H H L L H L H H L L L H H H H L L L L L L L 12131415H X H H H H H 1BI RBI LTX H LX XL X X X X X X X XL L L L L L HL L L L L L L L L L L L L L H H H H H H H2 34(1) 要求输出数字0~15时,“灭灯输入”(BI )必须开路或保持高电平。

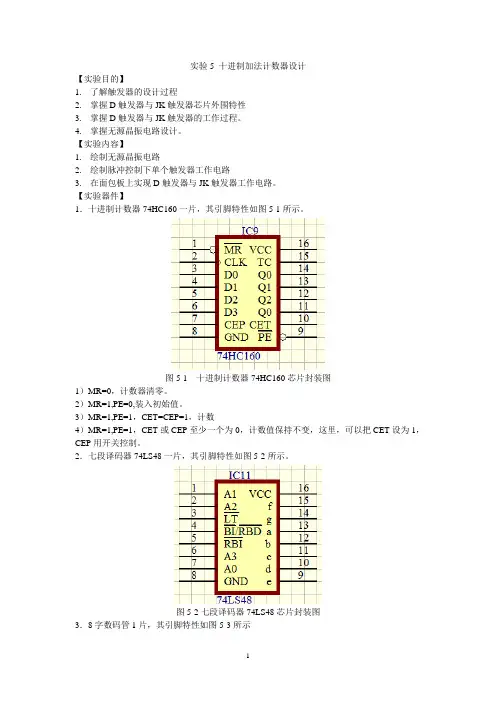

实验5 十进制加法计数器设计

【实验目的】

1.了解触发器的设计过程

2.掌握D触发器与JK触发器芯片外围特性

3.掌握D触发器与JK触发器的工作过程。

4.掌握无源晶振电路设计。

【实验内容】

1.绘制无源晶振电路

2.绘制脉冲控制下单个触发器工作电路

3.在面包板上实现D触发器与JK触发器工作电路。

【实验器件】

1.十进制计数器74HC160一片,其引脚特性如图5-1所示。

图5-1 十进制计数器74HC160芯片封装图

1)MR=0,计数器清零。

2)MR=1,PE=0,装入初始值。

3)MR=1,PE=1,CET=CEP=1,计数

4)MR=1,PE=1,CET或CEP至少一个为0,计数值保持不变,这里,可以把CET设为1,CEP用开关控制。

2.七段译码器74LS48一片,其引脚特性如图5-2所示。

图5-2七段译码器74LS48芯片封装图

3.8字数码管1片,其引脚特性如图5-3所示

图5-3 8字数码管芯片封装图

4.12个10k的电阻和8个发光二极管,一个8路开关,5v电源,面包板一块,导线若干条。

5.晶振电路与CD4060

【实验步骤】

1.在Cadence中绘制如图5-4所示的原理图

图5-4 十进制计数电路图

3.在面包板上实现该电路

根据实验器件的芯片引脚图在面包板上实现图2-2所示的电路。

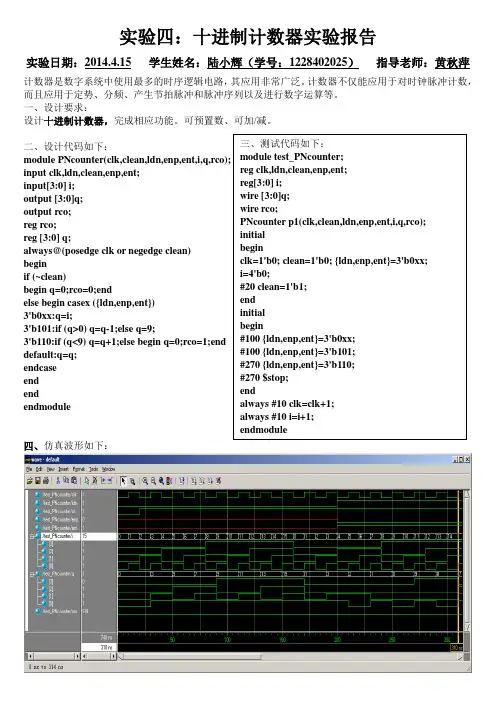

实验四:十进制计数器实验报告

实验日期:2014.4.15 学生姓名:陆小辉(学号:1228402025) 指导老师:黄秋萍 计数器是数字系统中使用最多的时序逻辑电路,其应用非常广泛。

计数器不仅能应用于对时钟脉冲计数,而且应用于定势、分频、产生节拍脉冲和脉冲序列以及进行数字运算等。

一、设计要求:

设计十进制计数器,完成相应功能。

可预置数、可加/减。

二、设计代码如下:

input clk,ldn,clean,enp,ent; input[3:0] i; output [3:0]q; output rco; reg rco; reg [3:0] q; always@(posedge clk or negedge clean) begin if (~clean) begin q=0;rco=0;end else begin casex ({ldn,enp,ent}) 3'b0xx:q=i; 3'b101:if (q>0) q=q-1;else q=9;

3'b110:if (q<9) q=q+1;else begin q=0;rco=1;end default:q=q; endcase end end endmodule

四、仿真波形如下:

续图。

十进制加法计数器实验遇到的问题及解决

在进行十进制加法计数器实验时,可能会遇到以下问题及其解决方法:

1. 计数器无法正常计数:这可能是由于电源电压不稳定或者连接错误导致的。

解决方法是检查电源电压稳定性并确保正确连接。

2. 计数器显示不正确:可能是由于数码管连接错误或者显示模块故障导致的。

解决方法是仔细检查数码管和显示模块的连接,并排除故障。

3. 计数器溢出问题:当计数器超过其位数限制时,可能会发生溢出问题。

解决方法是增加计数器的位数或者采取溢出处理措施,如自动清零。

4. 输入错误:输入错误的加数可能导致计数结果不正确。

解决方法是检查输入的加数是否正确,并进行纠正。

5. 电路连接问题:当电路连接错误或者松动时,计数器可能无法正常工作。

解决方法是检查电路连接是否正确,并确保连接牢固。

如果上述解决方法无法解决问题,建议咨询相关教师或专业人士寻求更进一步的帮助。

计数器的设计实验报告一、实验目的本次实验的目的是设计并实现一个简单的计数器,通过对计数器的设计和调试,深入理解数字电路的基本原理和逻辑设计方法,掌握计数器的工作原理、功能和应用,提高自己的电路设计和调试能力。

二、实验原理计数器是一种能够对输入脉冲进行计数,并在达到设定计数值时产生输出信号的数字电路。

计数器按照计数方式可以分为加法计数器、减法计数器和可逆计数器;按照计数进制可以分为二进制计数器、十进制计数器和任意进制计数器。

本次实验设计的是一个简单的十进制加法计数器,采用同步时序逻辑电路设计方法。

计数器由触发器、门电路等组成,通过对触发器的时钟信号和输入信号的控制,实现计数功能。

三、实验设备与器材1、数字电路实验箱2、集成电路芯片:74LS160(十进制同步加法计数器)、74LS00(二输入与非门)、74LS04(六反相器)3、示波器4、直流电源5、导线若干四、实验内容与步骤1、设计电路根据实验要求,选择合适的计数器芯片 74LS160,并确定其引脚功能。

设计计数器的清零、置数和计数控制电路,使用与非门和反相器实现。

画出完整的电路原理图。

2、连接电路在数字电路实验箱上,按照电路原理图连接芯片和导线。

仔细检查电路连接是否正确,确保无短路和断路现象。

3、调试电路接通直流电源,观察计数器的初始状态。

输入计数脉冲,用示波器观察计数器的输出波形,检查计数是否正确。

若计数不正确,逐步排查故障,如检查芯片引脚连接、电源电压等,直至计数器正常工作。

4、功能测试测试计数器的清零功能,观察计数器是否能在清零信号作用下回到初始状态。

测试计数器的置数功能,设置不同的预置数,观察计数器是否能按照预置数开始计数。

五、实验结果与分析1、实验结果成功实现了十进制加法计数器的设计,计数器能够在输入脉冲的作用下进行正确计数。

清零和置数功能正常,能够满足实验要求。

2、结果分析通过对计数器输出波形的观察和分析,验证了计数器的工作原理和逻辑功能。

eda实验报告十进制计数器设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!EDA实验报告:十进制计数器设计流程详解一、实验背景与目的在电子设计自动化(EDA)领域,计数器是一种常见的数字逻辑电路,用于实现数字系统的计数功能。

实验1 十进制加减法计数器实验地点:电子楼218 实验时间:2012年10月19日指导老师:黄秋萍、陈虞苏实验要求:设计十进制加减法计数器,保留测试程序、设计程序、仿真结果1.设计程序:module count(EN,CLK,DOUT,F,RST);input EN,CLK,F,RST;output [3:0]DOUT;reg [3:0]DOUT;always@(posedge CLK)begin :abcif(EN)if(!RST)if(F)begin :aDOUT=DOUT+1;if(DOUT==10)DOUT=0;end //END Aelsebegin :bDOUT=DOUT-1;if(DOUT==15)DOUT=9;endelseDOUT=0;elseDOUT=DOUT;endendmodule2.测试程序`timescale 10ns/1nsmodule test_count;wire [3:0] DOUT;reg EN,F,RST,CLK;count M(EN,CLK,DOUT,F,RST);initialbegin :ABCCLK=0;EN=0;RST=1;F=1;#100 EN=1;#200 RST=0;#1500 F=0;#3000 $stop;endalways#50 CLK=~CLK;initial$monitor("EN=%b,F=%b,RST=%b,DOUT%D",EN,F,RST,DOUT); endmodule3.测试结果# EN=0,F=1,RST=1,DOUT x# EN=1,F=1,RST=1,DOUT x# EN=1,F=1,RST=1,DOUT 0# EN=1,F=1,RST=0,DOUT 0# EN=1,F=1,RST=0,DOUT 1# EN=1,F=1,RST=0,DOUT 2# EN=1,F=1,RST=0,DOUT 3# EN=1,F=1,RST=0,DOUT 4# EN=1,F=1,RST=0,DOUT 5# EN=1,F=1,RST=0,DOUT 6# EN=1,F=1,RST=0,DOUT 7# EN=1,F=1,RST=0,DOUT 8# EN=1,F=1,RST=0,DOUT 9# EN=1,F=1,RST=0,DOUT 0# EN=1,F=1,RST=0,DOUT 1# EN=1,F=1,RST=0,DOUT 2# EN=1,F=1,RST=0,DOUT 3# EN=1,F=1,RST=0,DOUT 4# EN=1,F=1,RST=0,DOUT 5# EN=1,F=0,RST=0,DOUT 5# EN=1,F=0,RST=0,DOUT 4# EN=1,F=0,RST=0,DOUT 3# EN=1,F=0,RST=0,DOUT 2# EN=1,F=0,RST=0,DOUT 1# EN=1,F=0,RST=0,DOUT 0# EN=1,F=0,RST=0,DOUT 9# EN=1,F=0,RST=0,DOUT 8# EN=1,F=0,RST=0,DOUT 7# EN=1,F=0,RST=0,DOUT 6# EN=1,F=0,RST=0,DOUT 5# EN=1,F=0,RST=0,DOUT 4# EN=1,F=0,RST=0,DOUT 3# EN=1,F=0,RST=0,DOUT 2# EN=1,F=0,RST=0,DOUT 1# EN=1,F=0,RST=0,DOUT 0# EN=1,F=0,RST=0,DOUT 9# EN=1,F=0,RST=0,DOUT 8# EN=1,F=0,RST=0,DOUT 7# EN=1,F=0,RST=0,DOUT 6# EN=1,F=0,RST=0,DOUT 5# EN=1,F=0,RST=0,DOUT 4# EN=1,F=0,RST=0,DOUT 3# EN=1,F=0,RST=0,DOUT 2# EN=1,F=0,RST=0,DOUT 1# EN=1,F=0,RST=0,DOUT 0# EN=1,F=0,RST=0,DOUT 9# EN=1,F=0,RST=0,DOUT 8# EN=1,F=0,RST=0,DOUT 7# EN=1,F=0,RST=0,DOUT 6# EN=1,F=0,RST=0,DOUT 54.波形显示5.实验结果分析RST为1是清零信号,CLK是时钟信号,当EN为1时使能信号,F为1时,加法计数,F=0时减法计数。

微机原理十进制减法实验程序一、十进制数相减程序设计实验DATA SEGMENTDATA1 DB 33H,39H,31H,37H,38H ;第一个数据(作为被减数)DATA2 DB 36H,35H,30H,38H,32H ;第二个数据(作为减数)MES1 DB '-','$'MES2 DB '=','$'DATA ENDSSTACK SEGMENT ;堆栈段STA DB 20 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AXMOV ES,AXMOV AX,STACKMOV SS,AXMOV AX,TOPMOV SP,AXMOV SI,OFFSET DATA1MOV BX,05CALL DISPL ;显示被减数MOV AH,09HLEA DX,MES1INT 21HMOV SI,OFFSET DATA2MOV BX,05 ;显示减数CALL DISPLMOV AH,09HLEA DX,MES2INT 21HMOV SI,OFFSET DATA1MOV DI,OFFSET DATA2CALL SUBA ;减法运算MOV SI,OFFSET DATA1MOV BX,05 ;显示结果CALL DISPLMOV DL,0DHMOV AH,02HINT 21HMOV DL,0AHMOV AH,02HINT 21HINT 21HMOV AX,4C00HINT 21HDISPL PROC NEAR ;显示子功能DSI: MOV AH,02MOV DL,[SI+BX-1] ;显示字符串中一字符INT 21HDEC BX ;修改偏移量JNZ DSIRETDISPL ENDPSUBA PROC NEARMOV DX,SIMOV BP,DIMOV BX,05SU1: SUB BYTE PTR[SI+BX-1],30HSUB BYTE PTR[DI+BX-1],30HDEC BX ;将ASCII 码表示的数字串 JNZ SU1 ;转化为十六进制的数字串 MOV SI,DXMOV DI,BPMOV CX,05 ;包括进位,共5位CLC ;清进单位SU2: MOV AL,[SI]MOV BL,[DI]SBB AL,BL ;带进位相减AAS ;非组合BCD码的减法调整 MOV [SI],AL ;结果送被减数区INC SIINC DI ;指向下一位LOOP SU2 ;循环MOV SI,DXMOV DI,BPMOV BX,05SU3: ADD BYTE PTR [SI+BX-1],30HADD BYTE PTR [DI+BX-1],30HDEC BX ;十六进制的数字串转化ASCII码表示的数字串 JNZ SU3 RETSUBA ENDPCODE ENDSEND START二、十进制数排序程序设计实验;;;;;功能:冒泡排序服务程序;;;;;;DATA SEGMENTWORD DB 'Input numbers:',0DH,0AH,'$'BUF DB 100 DUP('$')DATA1 DB 0DH,0AH,'The result is:',0DH,0AH,'$' COUNT DB 0 DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART:;;;;;;;;;;;;;;初始化;;;;;;;;;;;;;MOV AX,DATAMOV DS,AXLEA DX,WORDMOV AH,09HINT 21HLEA DX,BUFMOV AH,0AH ;输入字符到缓冲区INT 21H ;输入数据(0~99),每个数据空格隔开;;;;;;功能:计算键入数字个数;;;;;;;;;;;;;H1: MOV AL,DI[BUF+2]CMP AL,' ' ;是否为空格JNZ H2INC [COUNT] ;有数字,数量+1JMP H3H2: CMP AL,0DH ;是否为CRJZ H4H3: INC DIJMP H1H4: INC [COUNT];存放需要比较的个数;;;;;;;功能:冒泡排序服务程序;;;;;;;;;;;;; MOV CX,0MOV CL,BYTE PTR [COUNT];循环次数L1: PUSH CXMOV CL,BYTE PTR [COUNT]MOV DI,0;取首位数据L4: CALL COUNT1;调用判断数据位数子程序CMP BL,DL;比较位数的大小JA L5;前一个数比后一个数大的情况JNE L6CMP BL,1JNZ L7CALL XCH3;同为一位数的比较JMP L5L7: CALL XCH2;同为两位数的比较JMP L5L6: CALL XCH1;前一个数比后一个数位数少的情况L5: LOOP L4POP CXLOOP L1;;;;;;;;显示排序结果;;;;;;;;;;DISPLAY:LEA DX,[DATA1]MOV AH,09HINT 21H;显示提示信息LEA DX,[BUF+2]MOV AH,09HINT 21H;显示结果MOV AH,4CHINT 21H;返回结束;;;;;;;;判断数据位数;;;;;;;;;;COUNT1:MOV DX,0MOV BX,0J1: MOV AL,DI[BUF+2]CMP AL,' 'JZ J2CMP AL,0DHJZ J3INC BLINC DIJMP J1J2: MOV AL,DI[BUF+3]CMP AL,' 'JZ J3CMP AL,0DHJZ J3INC DLINC DIJMP J2J3: SUB DI,DXINC DIRET;;;前一个数比后一个数位数少的情况;;XCH1:MOV AL,DI[BUF] ;第一个数装入ALMOV BX,WORD PTR DI[BUF+2] ;第二个数装入BX MOV WORD PTR DI[BUF],BXMOV BL,20HMOV DI[BUF+2],BLMOV DI[BUF+3],ALINC DIRET;;;;;;;;;;同为两位数比较;;;;;;;;;XCH2:MOV BX,WORD PTR DI[BUF-1] ;第一个数装入BX MOVDX,WORD PTR DI[BUF+2] ;第二个数装入DX CMP BX,DX JAE L9 ;>=不交换MOV WORD PTR DI[BUF-1],DXMOV WORD PTR DI[BUF+2],BXL9: RET;;;;;;;;;;同为一位数的比较;;;;;;;;XCH3:MOV DL,DI[BUF] ;第一个数装入DLMOV DH,DI[BUF+2];第二个数装入DHCMP DL,DHJAE L10 ;>=不交换MOV DI[BUF],DHMOV DI[BUF+2],DLL10: RETCODE ENDSEND START三、8255输入输出实验;//***************************************************** ;文件名: 8255IO for 8088;功能: 8255输入、输出实验;接线: 用导线连接8255模块的CS_8255到CPU模块的200H;; 8255模块的JD3C到八位逻辑电平输出模块的JD1E。

实验1 十进制加减法计数器

实验地点:电子楼218 实验时间:2012年10月19日指导老师:黄秋萍、陈虞苏

实验要求:设计十进制加减法计数器,保留测试程序、设计程序、仿真结果

1.设计程序:

module count(EN,CLK,DOUT,F,RST);

input EN,CLK,F,RST;

output [3:0]DOUT;

reg [3:0]DOUT;

always@(posedge CLK)

begin :abc

if(EN)

if(!RST)

if(F)

begin :a

DOUT=DOUT+1;

if(DOUT==10)

DOUT=0;

end //END A

else

begin :b

DOUT=DOUT-1;

if(DOUT==15)

DOUT=9;

end

else

DOUT=0;

else

DOUT=DOUT;

end

endmodule

2.测试程序

`timescale 10ns/1ns

module test_count;

wire [3:0] DOUT;

reg EN,F,RST,CLK;

count M(EN,CLK,DOUT,F,RST);

initial

begin :ABC

CLK=0;

EN=0;

RST=1;

F=1;

#100 EN=1;

#200 RST=0;

#1500 F=0;

#3000 $stop;

end

always

#50 CLK=~CLK;

initial

$monitor("EN=%b,F=%b,RST=%b,DOUT%D",EN,F,RST,DOUT); endmodule

3.测试结果

# EN=0,F=1,RST=1,DOUT x

# EN=1,F=1,RST=1,DOUT x

# EN=1,F=1,RST=1,DOUT 0

# EN=1,F=1,RST=0,DOUT 0

# EN=1,F=1,RST=0,DOUT 1

# EN=1,F=1,RST=0,DOUT 2

# EN=1,F=1,RST=0,DOUT 3

# EN=1,F=1,RST=0,DOUT 4

# EN=1,F=1,RST=0,DOUT 5

# EN=1,F=1,RST=0,DOUT 6

# EN=1,F=1,RST=0,DOUT 7

# EN=1,F=1,RST=0,DOUT 8

# EN=1,F=1,RST=0,DOUT 9

# EN=1,F=1,RST=0,DOUT 0

# EN=1,F=1,RST=0,DOUT 1

# EN=1,F=1,RST=0,DOUT 2

# EN=1,F=1,RST=0,DOUT 3

# EN=1,F=1,RST=0,DOUT 4

# EN=1,F=1,RST=0,DOUT 5

# EN=1,F=0,RST=0,DOUT 5

# EN=1,F=0,RST=0,DOUT 4

# EN=1,F=0,RST=0,DOUT 3

# EN=1,F=0,RST=0,DOUT 2

# EN=1,F=0,RST=0,DOUT 1

# EN=1,F=0,RST=0,DOUT 0

# EN=1,F=0,RST=0,DOUT 9

# EN=1,F=0,RST=0,DOUT 8

# EN=1,F=0,RST=0,DOUT 7

# EN=1,F=0,RST=0,DOUT 6

# EN=1,F=0,RST=0,DOUT 5

# EN=1,F=0,RST=0,DOUT 4

# EN=1,F=0,RST=0,DOUT 3

# EN=1,F=0,RST=0,DOUT 2

# EN=1,F=0,RST=0,DOUT 1

# EN=1,F=0,RST=0,DOUT 0

# EN=1,F=0,RST=0,DOUT 9

# EN=1,F=0,RST=0,DOUT 8

# EN=1,F=0,RST=0,DOUT 7

# EN=1,F=0,RST=0,DOUT 6

# EN=1,F=0,RST=0,DOUT 5

# EN=1,F=0,RST=0,DOUT 4

# EN=1,F=0,RST=0,DOUT 3

# EN=1,F=0,RST=0,DOUT 2

# EN=1,F=0,RST=0,DOUT 1

# EN=1,F=0,RST=0,DOUT 0

# EN=1,F=0,RST=0,DOUT 9

# EN=1,F=0,RST=0,DOUT 8

# EN=1,F=0,RST=0,DOUT 7

# EN=1,F=0,RST=0,DOUT 6

# EN=1,F=0,RST=0,DOUT 5

4.波形显示

5.实验结果分析

RST为1是清零信号,CLK是时钟信号,当EN为1时使能信号,F为1时,加法计数,F=0时减法计数。

实验结果与设计一致。