计算机组成与设计第三版第七章课后答案

- 格式:ppt

- 大小:87.00 KB

- 文档页数:17

《计算机组成原理》各章练习题参考答案第一章思考练习题一.填空1.电子数字计算机可以分为专用计算机和通用计算机两类。

2.硬件采用LSI或VLSI的电子计算机属于计算机发展过程中的第四代。

3.存储器中存放数据和程序。

4.一台计算机包括运算、存储、控制、输入及输出五个单元。

5.完成算术运算和逻辑运算的部件是运算器(或ALU);运算器的核心是加法器;控制、指挥程序和数据的输入、运行以及处理运算结果的部件是控制器。

6.CPU内部连接各寄存器及运算部件之间的总线是内部总线;CPU同存储器、通道等互相连接的总线是系统总线;中、低速I/O设备之间互相连接的总线是I/O总线。

7.在多总路线结构中,CPU总线、系统总线和高速总线相连通过桥实现。

8.计算机软件一般分为系统软件和应用软件。

9.完整的计算机系统由硬件系统和软件系统构成。

10.机器字长是指一台计算机一次所能够处理的二进制位数量。

11.数据分类、统计、分析属于计算机在数据处理方面的应用。

12.计算机是一种信息处理机,它最能准确地反映计算机的主要功能。

13.个人台式商用机属于微型机。

14.对计算机软硬件进行管理,是操作系统的功能。

15.用于科学技术的计算机中,标志系统性能的主要参数是MFLOPS。

16.通用计算机又可以分为超级机、大型机、服务器、工作站、微型机和单片机六类。

17.“存储程序控制”原理是冯.诺依曼提出的。

18.运算器和控制器构成CPU,CPU和主存构成主机。

19.取指令所用的时间叫取指周期,执行指令所用的时间叫执行周期。

20.每个存储单元都有一个编号,该编号称为地址。

21.现代计算机存储系统一般由高速缓存、主存和辅存构成。

22.计算机能够自动完成运算或处理过程的基础是存储程序和程序控制原理。

二.单选1.存储器用来存放( C )。

A.数据B.程序C.数据和程序D.正在被执行的数据和程序2.下面的描述中,正确的是( B )A.控制器能够理解、解释并执行所有的指令及存储结果。

单片微型计算机与接口技术思考与习题77.1 8XX51单片机内部设有几个定时/计数器?它们是由哪些专用寄存器组成的?答:(1)8XX51单片机内部设有2个定时/计数器。

(2)定时/计数器T1由寄存器TH1、TL1组成,定时/计数器T0由寄存器TH0、TL0组成。

7.3定时/计数器用作定时时,其定时时间与哪些因素有关?用作计数时,对外界计数频率有何限制?答:设置为定时工作方式时,定时器计数的脉冲是由51单片机片内振荡器经12分频后产生的。

每经过一个机器周期定时器(T0或T1)的数值加1直至计数满产生溢出。

设置为计数工作方式时,通过引脚T0(P3.4)和T1(P3.5)对外部脉冲信号计数。

当输入脉冲信号产生由1至0的下降沿时,定时器的值加1, 在每个机器周期CPU采样T0和T1的输入电平。

若前一个机器周期采样值为高,下一个机器周期采样值为低,则计数器加1。

由于检测一个1至0的跳变需要二个机器周期,故最高计数频率为振荡频率的二十四分之一。

7.5利用8XX51的T0计数。

每计10个脉冲,P1.0变反一次,用查询和中断两种方式编程。

使用方式2,计数初值C=100H—0AH=F6H查询方式:ORG 0000HMOV TMOD,#06HMOV TH0,#0F6HMOV TL0,#0F6HSETB TR0ABC:JNB TF0,$CLR TF0CPL P1.0SJMP ABC中断方式:ORG 0000HAJMP MAINORG 0000BHCPL P1.0RETIMAIN:MOV TMOD,#06HMOV THO,#0F6HSETB EASETB ET0SETB TR0SJMP $7.7已知8XX51单片机系统时钟频率为6MHz,利用定时器T0使P1.2每隔350us,输出一个50us脉宽的正脉冲。

解:fosc=6MHz,MC=2us,方式2的最大定时为512us,合乎题目的要求。

50us时,计数初值为C1=256-25=E7H,350us时,计数初值为C2=256-175=51HORG 0000HMOV TMOD,#02HNEXT:MOV TH0,#51HMOV TL0,51HCLR P1.2SETB TR0AB1:JBC TF0,EXTSJMP AB1EXT:SETB P1.2MOV TH0,#0E7HMOV TL0,#0E7HAB2:JBC TF0,NEXTSJMP AB27.9设系统时钟频率为6MHz,试用定时器T0作为外部计数器,编程实现每计到1000个脉冲后,使T1定时2ms,然后T0又开始计数,这样反复循环。

1.控制器有哪几种控制方式?各有何特点?解:控制器的控制方式可以分为3种:同步控制方式、异步控制方式和联合控制方式。

同步控制方式的各项操作都由统一的时序信号控制,在每个机器周期中产生统一数目的节拍电位和工作脉冲。

这种控制方式设计简单,容易实现;但是对于许多简单指令来说会有较多的空闲时间,造成较大数量的时间浪费,从而影响了指令的执行速度。

异步控制方式的各项操作不采用统一的时序信号控制,而根据指令或部件的具体情况决定,需要多少时间,就占用多少时间。

异步控制方式没有时间上的浪费,因而提高了机器的效率,但是控制比较复杂。

联合控制方式是同步控制和异步控制相结合的方式。

2.什么是三级时序系统?解:三级时序系统是指机器周期、节拍和工作脉冲。

计算机中每个指令周期划分为若干个机器周期,每个机器周期划分为若干个节拍,每个节拍中设置一个或几个工作脉冲。

3.控制器有哪些基本功能?它可分为哪几类?分类的依据是什么?解:控制器的基本功能有:(1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

(2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

(3)指挥并控制CPU 、主存和输入输出设备之间的数据流动。

控制器可分为组合逻辑型、存储逻辑型、组合逻辑与存储逻辑结合型3类,分类的依据在于控制器的核心———微操作信号发生器(控制单元CU)的实现方法不同。

4.中央处理器有哪些功能?它由哪些基本部件所组成?解:从程序运行的角度来看,CPU 的基本功能就是对指令流和数据流在时间与空间上实施正确的控制。

对于冯? 诺依曼结构的计算机而言,数据流是根据指令流的操作而形成的,也就是说数据流是由指令流来驱动的。

5.中央处理器中有哪几个主要寄存器?试说明它们的结构和功能。

解:CPU 中的寄存器是用来暂时保存运算和控制过程中的中间结果、最终结果及控制、状态信息的,它可分为通用寄存器和专用寄存器两大类。

通用寄存器可用来存放原始数据和运算结果,有的还可以作为变址寄存器、计数器、地址指针等。

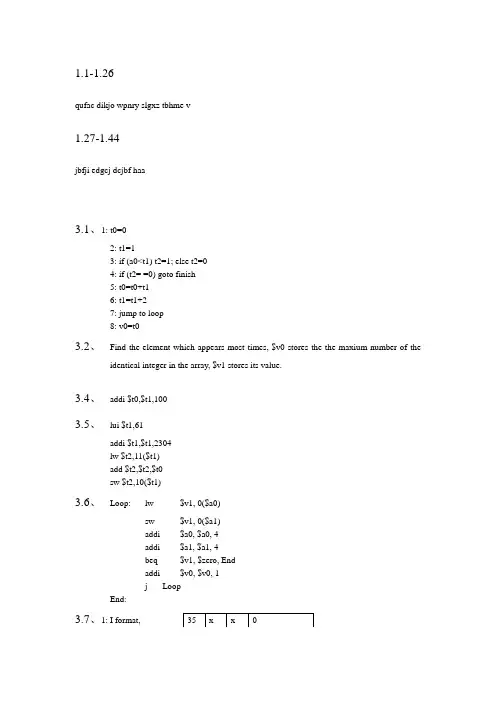

1.1-1.26qufac dikjo wpnry slgxz tbhme v1.27-1.44jbfji edgcj dcjbf haa3.1、1: t0=02: t1=13: if (a0<t1) t2=1; else t2=04: if (t2= =0) goto finish5: t0=t0+t16: t1=t1+27: jump to loop8: v0=t03.2、Find the element which appears most times, $v0 stores the the maxium number of theidentical integer in the array, $v1 stores its value.3.4、addi $t0,$t1,1003.5、lui $t1,61addi $t1,$t1,2304lw $t2,11($t1)add $t2,$t2,$t0sw $t2,10($t1)3.6、Loop: lw $v1, 0($a0)sw $v1, 0($a1)addi $a0, $a0, 4addi $a1, $a1, 4beq $v1, $zero, Endaddi $v0, $v0, 1j LoopEnd:3.7、1: I format,3: I format,4: I format,5: I format,6: I format,3.8、v0=0;v1=a0;v0++;a1=v1;a0++;a1++;if(v1= =0) goto loop;v0--;3.9、bne $t0,$s5,exitloop: add $t1,$s3,$s3add $t1,$t1,$t1add $s3,$s3,$s6lw $t0,0(t1)beq $t0,$s5,loop exit:3.11、slti $t5,$t0,1bne $t0,1,exitloop: addi $t0,$zero,0add $t4,$t0,$t0add $t4,$t4,$t4lw $t1,0($a0)add $t2,$t4,$t1add $t3,$a1,$t1sw $t2,0($t3)addi $t0,$t0,1slti $t5,$t0,101beq $t5,1,loopexit:3.23、loop: addi $t0,$zero,98lb $t1,0($a0)addi $a0,$a0,1beq $t1,$zero,exitbne $t1,$t0,loopbeq $t1,$t0,nextsub $v0,$a0,1exit: add $v0,$zero,$zeronext:3.24、bcount: addi $sp,$sp,-12sw $ra,8($sp)sw $a0,4($sp)sw $s0,0($sp)add $s0,$zero,$zeroNext: jal bfindadd $a0,$v0,$zerolb $t0,0($a0)beq $t0,$zero,End #encounter nulladdi $s0,$s0,1addi $v0,$v0,1j NextEnd: add $v0,$s0,$zerolw $s0,0($sp)lw $a0,4($sp)lw $ra,8($sp)addi $sp,$sp,12jr $ra4.1、000000000000000000000010000000004.2、111111111111111111111100000000014.4、-5004.5、-14.6、21474836474.10、loop: sub $t3,$zero,$t3slt $t0,$t3,$zerobeq $t0,$zero,loopadd $t2,$t3,$zero how to use 3 instructions?4.13、If A_lower is positive, A_upper_adjusted equals to A_upper.If A_lower is negative, A_upper_adjusted equals to A_upper+1.4.17、addu $t0, $t3,$t4sltu $t2,$t0,$t34.22、srl $t0,$s0,8andi $s1,$t0,40954.23、when it overflew , set should be converted .4.40、xor $s0,$s0,$s1xor $s1,$s1,$s0xor $s0,$s0,$s14.46、ripple carry c1=a0*c0+b0*c0+a0*b0 2Tc2=a1*c1+b1*c1+a1*b1 4Tc3=a2*c2+b2*c2+a2*b2 6TThe worst case : c4=a3*c3+b3*c3+a3*b3 8TCarry look ahead : gi=ai*bi T pi=ai+bi Tc1=c2=c3=c4=3T4.53、4.54、step1 6.42*101=0.642*102step2 9.51*102+0.642*102=10.152*102step3 10.152*102=1.0152*102step4 1.0152*103 is rounded to three significant digits 1.015*1034.55、6.42X101=0.642X1020.642+9.51=10.1526.42X101+9.51X102=10.152X102=1.0152X103so the answer is 1.02X1035.1、RegDst=0 lw sw and branchAluSrc=0 R-format beqMemtoReg=0 R-format sw and beqZero=0 R-format sw and lw5.2、RegDst=1 R-format sw and beqAluSrc=1 lw and swMemtoReg=1 lw sw and beqZero=1 R-format lw and sw5.6、修改两个信号:MemtoReg: 00 :Alu result01 :From Mem data10 :PC+4RegDst: 00 : Instruction[20-16]01 :Instruction[15-11]10 :$ra寄存器5.8、lw $t0 ,$t1,$t25.14、P374页图Instruction a b cR-formatlwswbeqjlongest8 10 10time5.165.17、5.22、jr rsIt is an R-type instruction.So the changes can be made like following .5.24、M1=5*22%+4*11%+4*49%+3*16%+3*2%=4.04M2=4*22%+4*11%+3*49%+3*16%+3*2%=3.33M3=3*22%+3*11%+3*49%+3*16%+3*2%=3So the CPU excution time isT1=CPI*Clockcycletime=4.04/(500*106 )=8.08nsT2=3.33/(400*106 )=8.325nsT3=3/(250*106 )=12nsHence M1 is the fastest machine.5.26、beq $t3,$zero,Exitadd $t3,$t3,$t3add $t3,$t3,$t3 #get 4*$t3add $t3,$t3,$t2 #caculate the address of destination[$t3] loop: lw $t4,0($t1)sw $t4,0($t2)addi $t1,$t1,4addi $t2,$t2,4bne $t2,$t3,loopExit:branch 3 lw 5 and the rest are 4The number of executed instructions is 4+5*100=504The nmber of cycles is3+3*4+(5+4*3+3)*100=20155.27、1. According to the figure above there will be two changes.1>Extend the multiplexor for ALUSrcA by adding ALUout to it .We mark it with 102> We add a multiplexor between B and Memory write data ,connect memory dataregister with the multiplexor and mark it with 1.The multi is controled by the ]signal bcp.2. By making these changes ,we can directly increase the address $t1,$t2,in ALUout by 4When the memory data loading from $t1is read into memory data register, we canquickly write it into memory by setting bcp to 0.3. By estination ,we can cut down clock cycles distinctively by implementing theinstruction in hardware above .The performance increase comes from adding internal registers.7.7、7.8、7.9、212*(32*4+16+1)=580Kb7.11、a. 1+16*10+16*1=177 clock cyclesb. 1+4*10+4*1=45 clock cyclesc. 1+4*10+16*1=57 clock cycles7.12、The CPI of a is 1.2+0.5%*177=2.085The CPI of b is 1.2+0.5%*45=1.425The CPI of c is 1.2+0.5%*57=1.485The processor using wide memory is 2.085/1,425=1.46 times faster than using nerrowand 1.04 times faster than the one using interleaved memories.7.15、AMAT=(1+0.05*20)*2ns=4ns7.20、7.22、7.24、The number of sets in the cache: S/ABThe number of index bits in the address: log2(S/AB)The number of bits needed to implement the cache : Tag =k- log2(S/AB)-log2B7.27、Cache1: X+(4%+0.5*8%)*7=2So,X=1.44Cache2: 1.44+(2%+0.5*5%)*10=1.85Cache3: 1.44+(2%+0.5*4%)*10=1.84Thus,machine1spemds the most cycles on cache mises.7.32、Page size is 16-KB=214B240/214=226Total size of bits 226*(36-14+4)=208MB7.33、Virtual addressCache hit8.1 A 200 1000/5B 150 750/58.2 (1)n*5*(1/1000)+n*(1/10)*(20/1000)=1 n=142(2)5*n*(1/750)+500/5*(1/10)*18*(1/1000)+(5n-500)/5/5/10*25/1000 =1 n=1168.3 7和8距离近的那张图,原因是路程短8.10 a=1+19.7ms/5ns+2+2=3.9*10^6 cyclesb=3.94*10^6*128/4=1.26*10^8cycles) 32/b=50.798/a=12.750.79 12.78.18 17.84。

计算机组成原理(第三版)课后答案计算机是⼀种能⾃动地、⾼速地对各种数字化信息进⾏运算处理的电⼦设备。

1.2冯诺依曼计算机体系结构的基本思想是存储程序,也就是将⽤指令序列描述的解题程序与原始数据⼀起存储到计算机中。

计算机只要⼀启动,就能⾃动地取出⼀条条指令并执⾏之,直⾄程序执⾏完毕,得到计算结果为⽌。

按此思想设计的计算机硬件系统包含:运算器、控制器、存储器、输⼊设备和输出设备。

各部分的作⽤见教材:P10—P121.3计算机的发展经历了四代。

第⼀代:见教材P1第⼆代:见教材P2第三代:见教材P2第四代:见教材P21.4系统软件定义见教材:P12—13,应⽤软件定义见教材:P121.5见教材:P14—151.6见教材:P111.7见教材:P6—81.8硬件定义见教材:P9软件定义见教材:P12固件定义见教材:P131.91)听觉、⽂字、图像、⾳频、视频2)图像、声⾳、压缩、解压、DSP1.10处理程度按从易到难是:⽂本→图形→图像→⾳频→视频27/64=00011011/01000000=0.0110110=0.11011×2-1规格化浮点表⽰为:[27/64]原=101,011011000[27/64]反=110,011011000[27/64]补=111,011011000[27/64]反=110,100100111[27/64]补=111,1001010002.3 模为:29=10000000002.4 不对,8421码是⼗进制的编码2.5浮点数的正负看尾数的符号位是1还是0浮点数能表⽰的数值范围取决于阶码的⼤⼩。

浮点数数值的精确度取决于尾数的长度。

2.61)不⼀定有N1>N2 2)正确2.7 最⼤的正数:0111 01111111 ⼗进制数:(1-2-7)×27最⼩的正数:1 ⼗进制数:2-7×2-7最⼤的负数:1 ⼗进制数:--2-7×2-7最⼩的负数:0111 10000001 ⼗进制数:--(1-2-7)×272.81)[x]补=00.1101 [y]补=11.0010[x+y]补=[x]补+[y]补=11.1111⽆溢出x+y= -0.0001[x]补=00.1101 [--y]补=00.1110[x-y]补=[x]补+[--y]补=01.1011 正向溢出2)[x]补=11.0101 [y]补=00.1111[x+y]补=[x]补+[y]补=00.0100 ⽆溢出x+y= 0.0100[x]补=11.0101 [--y]补=11.0001[x-y]补=[x]补+[--y]补=10.0110 负向溢出3) [x]补=11.0001 [y]补=11.0100[x+y]补=[x]补+[y]补=10.0101 负向溢出[x]补=11.0001 [--y]补=00.1100[x-y]补=[x]补+[--y]补=11.1101 ⽆溢出X-y=-0.00112.91)原码⼀位乘法|x|=00.1111 |y|=0.1110部分积乘数y n00.0000 0.1110+00.000000.0000+00.111100.11110→00.011110 0.11+00.111101.011010→00.1011010 0.1+00.111101.1010010→00.11010010P f=x f⊕y f=1 |p|=|x|×|y|=0.11010010所以[x×y]原=1.11010010补码⼀位乘法[x]补=11.0001 [y]补=0.1110 [--x]补=11.0001 部分积y n y n+1 00.0000 0.11100→00.00000 0.1110+00.111100.11110→00.011110 0.111→00.0011110 0.11→00.0 0.1+11.000111.00101110[x×y]补=11.001011102)原码⼀位乘法|x|=00.110 |y|=0.010部分积乘数y n00.000 0.010+00.00000.000→00.0000 0.01+00.11000.1100→00.01100 0.0+00.00000.01100 0所以[x×y]原=0.001100补码⼀位乘法[x]补=11.010 [y]补=1.110 [--x]补=00.110部分积y n y n+100.000 1.1100→00.0000 1.110+00.11000.1100→00.01100 1.11→00.001100 1.1所以[x×y]补=0.0011002.101)原码两位乘法|x|=000.1011 |y|=00.0001 2|x|=001.0110部分积乘数 c000.0000 00.00010+000.1011000.1011→000.001011 0.000→000.00001011 00.0P f=x f⊕y f=1 |p|=|x|×|y|=0.00001011所以[x×y]原=1.00001011补码两位乘法[x]补=000.1011 [y]补=11.1111 [--x]补=111.0101部分积乘数y n+1000.0000 11.11110+111.0101111.0101→111.110101 11.111→111.11110101 11.1所以[x×y]补=111.11110101 x×y=--0.000010112)原码两位乘法|x|=000.101 |y|=0.111 2|x|=001.010 [--|x| ]补=111.011 部分积乘数 c 000.000 0.1110+111.011111.011→111.11011 0.11+001.010→000.100011P f=x⊕y f=0 |p|=|x|×|y|=0.100011所以[x×y]原=0.100011补码两位乘法[x]补=111.011 [y]补=1.001 [--x]补=000.101 2[--x]补=001.010 部分积乘数y n+1 000.000 1.0010+111.011111.011→111.111011 1.00+001.010001.00011→000.100011所以[x×y]补=0.1000112.111) 原码不恢复余数法|x|=00.1010 |y|=00.1101 [--|y| ]补=11.0011部分积商数00.1010+11.0011←11.1010+00.110100.0111 0.1←00.1110+11.001100.0001 0.11←00.0010+11.001111.0101 0.110←01.1010+00.110111.0111 0.1100+00.110100.0100所以[x/y]原=0.1100 余数[r]原=0.0100×2—4补码不恢复余数法[x]补=00.1010 [y]补=00.1101 [--y]补=11.0011 部分积商数00.101000.0111 0.1←00.1110+11.001100.0001 0.11←00.0010+11.001111.0101 0.110←10.1010+00.110111.0111 0.1100+00.110100.0100所以[x/y]补=0.1100 余数[r]补=0.0100×2—42)原码不恢复余数法|x|=00.101 |y|=00.110 [--|y| ]补=11.010 部分积商数00.101+11.01011.111 0←11.110+00.11000.100 0.1←01.000+11.01000.010 0.11←00.100+11.01011.110 0.110+00.11000. 100所以[x/y]原=1.110 余数[r]原=1.100×2—3补码不恢复余数法[x]补=11.011 [y]补=00.110 [--y]补=11.010 部分积商数11.01111.100 1.0←11.000+00.11011.110 1.00←11.100+00.11000.010 1.001+11.01011.100所以[x/y]补=1.001+2—3=1.010 余数[r]补=1.100×2—32.121)[x]补=21101×00.100100 [y]补=21110×11.100110⼩阶向⼤阶看齐:[x]补=21110×00.010010求和:[x+y]补=21110×(00.010010+11.100110)=21110×11.111000 [x-y]补=21110×(00.010010+00.011010)=21110×00.101100 规格化:[x+y]补=21011×11.000000 浮点表⽰:1011,11.000000规格化:[x-y]补=21110×00.101100 浮点表⽰:1110,0.101100 2)[x]补=20101×11.011110 [y]补=20100×00.010110⼩阶向⼤阶看齐:[y]补=20101×00.001011求和:[x+y]补=20101×(11.011110+00.001011)=20101×11.101001 [x-y]补=20101×(11.011110+11.110101)=20101×00.010011 规格化:[x+y]补=21010×11.010010 浮点表⽰:1010,11. 010010规格化:[x-y]补=21010×00.100110 浮点表⽰:1010,00.1001102.13见教材:P702.141)1.0001011×262)0.110111*×2-62.151)串⾏进位⽅式C1=G1+P1C0G1=A1B1,P1=A1⊕B1C2=G2+P2C1G2=A2B2,P2=A2⊕B2C3=G3+P3C2G3=A3B3,P3=A3⊕B3C4=G4+P4C3G4=A4B4,P4=A4⊕B4C2=G2+P2G1+P2P1C0C3=G3+P3G2+P3P2G1+P3P2P1C0C4= G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C02.16参考教材P62 32位两重进位⽅式的ALU和32位三重进位⽅式的ALU 2.17C n“1”“1”3.1见教材:P79 3.2 见教材:P833.3与SRAM 相⽐,DRAM 在电路组成上有以下不同之处:1)地址线的引脚⼀般只有⼀半,因此,增加了两根控制线RAS 、CAS ,分别控制接受⾏地址和列地址。

计算机组成与系统结构习题答案第1章计算机系统概述1-1 见教材1.1.2。

1-2 见教材1.2.1。

1-3 见教材1.2.1。

1-4 见教材1.2.3。

1-5 见教材1.3.1。

1-6 各需KN ns 、KN 2 ns 、KN 3 ns 的时间。

1-7 需要K M N s 、K 22M N s 和K 33MN s 的时间。

1-8 透明的有:指令缓冲器、时序发生器、乘法器、主存地址寄存器、先行进位链、移位器。

1-9 见教材1.4.2。

1-1053.01910==F1-11 CPI=1.55, 运算速度≈25.81MIPS程序执行时间=3.875×10-3s 1-12 (1)平均CPI=2.28。

(2)MIPS 速率≈43.86MIPS 。

1-13 第二种方法效果就好。

第2章数据的机器层次表示2-1 (725.6875)10=(1325.54)8=(2D5.B)16=(1011010101.1011)22-2 (111010.011)2=(72.3)8=(3A.6)16。

(1000101.1001)2=(105.44)8=(45.9)16。

2-3 真值 原码 补码 反码 0 -0 0.1000 -0.1000 0.1111 -0.1111 1101 -110100000000 10000000 0.1000000 1.1000000 0.1111000 1.1111000 00001101 1000110100000000 00000000 0.1000000 1.1000000 0.1111000 1.0001000 00001101 1111001100000000 11111111 0.1000000 1.0111111 0.1111000 1.0000111 00001101 111100102-4真值原码补码反码1670.0111 0.0111 0.01111640.0100 0.0100 0.01001610.0001 0.0001 0.00010 0.0000 0.0000 0.0000-0 1.0000 0.0000 1.1111-161 1.0001 1.1111 1.1110-164 1.0100 1.1100 1.1011-167 1.0111 1.1001 1.10002-5[X1]补=0.10100,[X2]补=1.01001。

第一章1.模拟计算机的特点是数值由连续量来表示,运算过程也是连续的。

数字计算机的主要特点是按位运算,并且不连续地跳动计算。

模拟计算机用电压表示数据,采用电压组合和测量值的计算方式,盘上连线的控制方式,而数字计算机用数字0和1表示数据,采用数字计数的计算方式,程序控制的控制方式。

数字计算机与模拟计算机相比,精度高,数据存储量大,逻辑判断能力强。

2.数字计算机可分为专用计算机和通用计算机,是根据计算机的效率、速度、价格、运行的经济性和适应性来划分的。

3.科学计算、自动控制、测量和测试、信息处理、教育和卫生、家用电器、人工智能。

4.主要设计思想是:存储程序通用电子计算机方案,主要组成部分有:运算器、逻辑控制装置、存储器、输入和输出设备5.存储器所有存储单元的总数称为存储器的存储容量。

每个存储单元都有编号,称为单元地址。

如果某字代表要处理的数据,称为数据字。

如果某字为一条指令,称为指令字。

6.每一个基本操作称为一条指令,而解算某一问题的一串指令序列,称为程序。

7.取指周期中从内存读出的信息流是指令流,而在执行器周期中从内存读出的信息流是指令流。

8.半导体存储器称为内存,存储容量更大的磁盘存储器和光盘存储器称为外存,内存和外存共同用来保存二进制数据。

运算器和控制器合在一起称为中央处理器,简称CPU,它用来控制计算机及进行算术逻辑运算。

适配器是外围设备与主机联系的桥梁,它的作用相当于一个转换器,使主机和外围设备并行协调地工作。

9.计算机的系统软件包括系统程序和应用程序。

系统程序用来简化程序设计,简化使用方法,提高计算机的使用效率,发挥和扩大计算机的功能用用途;应用程序是用户利用计算机来解决某些问题而编制的程序。

10.在早期的计算机中,人们是直接用机器语言来编写程序的,这种程序称为手编程序或目的程序;后来,为了编写程序方便和提高使用效率,人们使用汇编语言来编写程序,称为汇编程序;为了进一步实现程序自动化和便于程序交流,使不熟悉具体计算机的人也能很方便地使用计算机,人们又创造了算法语言,用算法语言编写的程序称为源程序,源程序通过编译系统产生编译程序,也可通过解释系统进行解释执行;随着计算机技术的日益发展,人们又创造出操作系统;随着计算机在信息处理、情报检索及各种管理系统中应用的发展,要求大量处理某些数据,建立和检索大量的表格,于是产生了数据库管理系统。