实验三 频率计

- 格式:doc

- 大小:325.00 KB

- 文档页数:7

实验三--微波波导波长与频率的测量实验三微波波导波长与频率的测量、分析和计算一、实验目的(1)熟悉微波测量线的使用;(2)学会测量微波波导波长和信号源频率;(3)分析和计算波导波长及微波频率。

二、实验原理测量线的基本测量原理是基于无耗均匀传输线理论,当终端负载与测量线匹配时测量线内是行波;当终端负载为短路或开路时,传输线上为纯驻波,能量全部反射。

根据驻波分布的特性,在波导系统终端短路时,传输系统中会形成纯驻波分布状态,在这种情况下,两个驻波波节点之间的距离即为波导波长的1/2 ,所以只要测量出两个驻波波节点之间的距离,就可以得到信号源工作频率所对应的波导波长。

方法一:通过测量线上的驻波比,然后换算出反射系数模值,再利用驻波最小点位置d min 便可得到反射系数的幅角以及微波信号特性、网络特性等。

根据这一原理,在测得一组驻波最小点位置d1,d2,d3,d4… 后,由于相邻波节点的距离是波导波长的1/2,这样便可通过下式算出波导波长。

⎥⎦⎤⎢⎣⎡-+-+-+-=0min 10min 20min 30min 423421d d d d d d d d g λ(3-1)方法二:交叉读数法测量波导波长,如图 3-1 所示。

图 3-1 交叉读数法测量波节点位置为了使测量波导波长的精度较高(接近实际的波导波长),采用交叉读数法测量波导波长。

在测试系统调整良好状态下,通过测定一个驻波波节点两侧相等的电流指示值 I 0 (可选取最大值的 20%)所对应的两个位置 d 1、d 2,则取 d 1、d 2 之和的平均值,得到对应驻波波节点的位置 d min1 。

用同样的方法测定另一个相邻波节点的位置 d min2 ,如图 3-1 所示,则 d min1 、 d mi n2 与系统中波导波长之间的关系为:)(21);(21432min 211min d d d d d d +=+= (3-2)1min 2min 2d d g -=λ(3-3)在波导中,还可利用下面公式计算波导波长: ()a g 2100λλλ-= (3-4) 式中,λ0为真空中自由空间的波长。

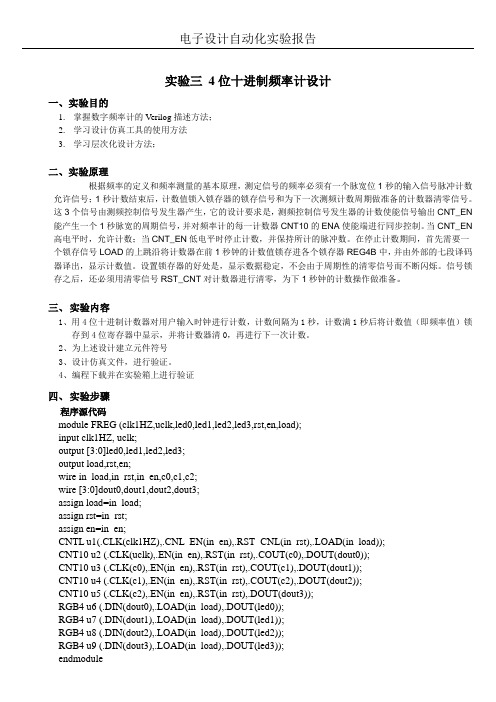

实验三4位十进制频率计设计一、实验目的1.掌握数字频率计的Verilog描述方法;2.学习设计仿真工具的使用方法3.学习层次化设计方法;二、实验原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽位1秒的输入信号脉冲计数允许信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一次测频计数周期做准备的计数器清零信号。

这3个信号由测频控制信号发生器产生,它的设计要求是,测频控制信号发生器的计数使能信号输出CNT_EN 能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN 高电平时,允许计数;当CNT_EN低电平时停止计数,并保持所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进各个锁存器REG4B中,并由外部的七段译码器译出,显示计数值。

设置锁存器的好处是,显示数据稳定,不会由于周期性的清零信号而不断闪烁。

信号锁存之后,还必须用清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作做准备。

三、实验内容1、用4位十进制计数器对用户输入时钟进行计数,计数间隔为1秒,计数满1秒后将计数值(即频率值)锁存到4位寄存器中显示,并将计数器清0,再进行下一次计数。

2、为上述设计建立元件符号3、设计仿真文件,进行验证。

4、编程下载并在实验箱上进行验证四、实验步骤程序源代码module FREG (clk1HZ,uclk,led0,led1,led2,led3,rst,en,load);input clk1HZ, uclk;output [3:0]led0,led1,led2,led3;output load,rst,en;wire in_load,in_rst,in_en,c0,c1,c2;wire [3:0]dout0,dout1,dout2,dout3;assign load=in_load;assign rst=in_rst;assign en=in_en;CNTL u1(.CLK(clk1HZ),.CNL_EN(in_en),.RST_CNL(in_rst),.LOAD(in_load));CNT10 u2 (.CLK(uclk),.EN(in_en),.RST(in_rst),.COUT(c0),.DOUT(dout0));CNT10 u3 (.CLK(c0),.EN(in_en),.RST(in_rst),.COUT(c1),.DOUT(dout1));CNT10 u4 (.CLK(c1),.EN(in_en),.RST(in_rst),.COUT(c2),.DOUT(dout2));CNT10 u5 (.CLK(c2),.EN(in_en),.RST(in_rst),.DOUT(dout3));RGB4 u6 (.DIN(dout0),.LOAD(in_load),.DOUT(led0));RGB4 u7 (.DIN(dout1),.LOAD(in_load),.DOUT(led1));RGB4 u8 (.DIN(dout2),.LOAD(in_load),.DOUT(led2));RGB4 u9 (.DIN(dout3),.LOAD(in_load),.DOUT(led3));endmodulemodule CNT10(CLK,RST,EN,COUT,DOUT); //4位计数器input CLK,RST,EN;output COUT;output[3:0] DOUT;reg[3:0] Q; reg COUT;always @ (posedge CLK or posedge RST)beginif(RST) Q=0;else if(EN) beginif(Q<9) Q=Q+1;else Q=0;endendalways @ (Q)if(Q==4'b1001) COUT=1;else COUT=0;assign DOUT=Q;endmodulemodule RGB4(DIN,LOAD,DOUT); //数据缓存器input LOAD;input[3:0] DIN;output[3:0] DOUT;reg[3:0] DOUT;always @ (posedge LOAD)DOUT=DIN;endmodulemodule CNTL(CLK,CNL_EN,RST_CNL,LOAD);//控制部分input CLK;output CNL_EN,RST_CNL,LOAD;reg CLKDIV,CNL_EN,LOAD,RST_CNL;always @ (posedge CLK)CLKDIV=~CLKDIV;always @ (posedge CLK) beginCNL_EN=CLKDIV;LOAD=~CLKDIV;endalways @ (CLK) beginif(CLK==1'b0&&CNL_EN==1'b0)RST_CNL=1;elseRST_CNL=0; endendmoduleRTL视图仿真结果功能分析:在波形中,CLK1HZ的频率为1HZ,以CLK1HZ为输入,产生en,rst,load的输出波形。

实验三微波波导波长与频率的测量摘要:本实验通过使用微波频率计和波导滑动短路板等设备,测量了微波波导的波长与频率之间的关系。

实验结果表明,微波波导的波长与频率呈线性关系,可以通过一定的测量方法确定微波波导的波长。

1.引言微波波导是一种广泛应用于微波通信和微波器件中的传输线路。

波导的基本特点是信号可以在其中以电磁波的形式传输,并且波导参数可以影响波导的传输性能。

其中,波导的波长和频率是两个重要的参数。

测量波导的波长和频率可以有效地评估波导的传输性能和应用范围。

2.实验原理微波波导内的电磁波的波长与频率之间存在一定的关系。

一般而言,波导的波长lambda可以通过以下公式计算得出:lambda = c/f其中,c为光速,f为波导的频率。

在实际测量中,可以通过使用微波频率计和波导滑动短路板来测量波导的频率和波长。

微波频率计可以根据输入的信号频率,直接测量得到波导的频率。

而波导滑动短路板则可以控制波导中的波长,通过移动短路板的位置,可以观察到引起的驻波现象。

当波导中存在驻波时,滑动短路板所移动的距离正好等于半个波长。

3.实验步骤3.1连接实验设备:将微波频率计与波导滑动短路板连接起来,确保连接正确并稳定。

3.2设置微波频率计:根据实验要求,设置微波频率计的工作频率范围,并将其调整到合适的工作状态。

3.3移动滑动短路板:在波导的一端,将滑动短路板移动到适当的位置,观察到波导中的驻波现象。

3.4测量驻波位置:通过滑动短路板的移动距离,准确测量驻波的位置,并记录下来。

3.5 计算波导的波长:根据实验数据,计算出波导的波长,使用公式lambda = 2 * d,其中d为驻波位置和波导起点之间的距离。

4.实验结果与分析通过实验测量得到的驻波位置数据,可以计算得到波导的波长。

将波导的波长与实际频率计测得的频率数据进行对比,可以观察到波导的波长与频率之间的线性关系。

实验结果表明,波导的波长与频率之间存在着确定的关系。

5.结论本实验通过测量微波波导的波长和频率,得出了波长与频率之间的线性关系。

电子测量实验报告实验三频率测量及其误差分析院系:信息工程学院班级:08电子信息工程一班学号:**********姓名:***实验三频率测量及其误差分析一、实验目的1 掌握数字式频率计的工作原理;2 熟悉并掌握各种频率测量方法;3 理解频率测量误差的成因和减小测量误差的方法。

二、实验内容1用示波器测量信号频率,分析测量误差;2用虚拟频率计测量频率。

三、实验仪器及器材1信号发生器 1台2 虚拟频率计 1台3 示波器 1台4 UT39E型数字万用表 1块四、实验要求1 查阅有关频率测量的方法及其原理;2 理解示波器测量频率的方法,了解示波器各旋钮的作用;3 了解虚拟频率计测量的原理;4 比较示波器测频和虚拟频率计测频的区别。

五.实验步骤1 用示波器测量信号频率用信号发生器输出Vp-p=1V、频率为100Hz—1MHz的正弦波加到示波器,适当调节示波器各旋钮,读取波形周期,填表3-1,并以信号源指示的频率为准,计算频率测量的相对误差。

操作步骤:1、将信号发生器与示波器用线连接好。

其中CH1为输出通信,设置信号发生器为正弦波,输出Vp-p=1V,起始频率为2Hz,观察并记录各个信号的频率,周期和测量误差。

2、保持幅度不变,改变输出频率,最好设置为2Hz—100MHz之间,同样计算并记录频率,周期,和测量误差。

如下表:表3-1“周期法”测量信号频率分析结果:如上表,我们发现,当频率从2Hz—100MHz之间变化时,其相对误差的大小会发生变化。

当频率为特别小或者特别大时,误差相对会比较大一些。

如上表的2Hz和100MHz。

原因在于,当频率特别小的时候,受到的外界干扰信号影响对其比较大,相当于把原信号给淹没了。

当频率特别大的时候,高频干扰同样会对它产生比较大的影响。

2 用虚拟频率计测量频率用标准信号发生器输出正弦信号作为被测信号,送到DSO2902的CH-A1通道,按表3-2进行实验。

并以信号发生器指示的频率为准,计算测频误差。

频率计实验报告一、实验目的本次实验的目的是通过设计和搭建频率计电路,掌握频率测量的基本原理和方法,熟悉相关电子元器件的使用,提高电路设计和调试的能力,并深入理解数字电路中计数器、定时器等模块的工作原理。

二、实验原理频率是指周期性信号在单位时间内重复的次数。

频率计的基本原理是通过对输入信号的周期进行测量,并将其转换为频率值进行显示。

常见的频率测量方法有直接测频法和间接测频法。

直接测频法是在给定的闸门时间内,对输入信号的脉冲个数进行计数,从而得到信号的频率。

间接测频法则是先测量信号的周期,然后通过倒数计算出频率。

在本次实验中,我们采用直接测频法。

使用计数器对输入信号的脉冲进行计数,同时使用定时器产生固定的闸门时间。

在闸门时间结束后,读取计数器的值,并通过计算得到输入信号的频率。

三、实验设备与器材1、数字电路实验箱2、示波器3、函数信号发生器4、集成电路芯片(如计数器芯片、定时器芯片等)5、电阻、电容、导线等若干四、实验步骤1、设计电路原理图根据实验要求和原理,选择合适的计数器芯片和定时器芯片,并设计出相应的电路连接图。

确定芯片的引脚连接方式,以及与外部输入输出信号的连接关系。

2、搭建实验电路在数字电路实验箱上,按照设计好的电路原理图,插入相应的芯片和元器件,并使用导线进行连接。

仔细检查电路连接是否正确,确保无短路和断路现象。

3、调试电路接通实验箱电源,使用示波器观察输入信号和输出信号的波形,检查电路是否正常工作。

调整函数信号发生器的输出频率和幅度,观察频率计的测量结果是否准确。

4、记录实验数据在不同的输入信号频率下,记录频率计的测量值,并与函数信号发生器的设定值进行比较。

分析测量误差产生的原因,并尝试采取相应的措施进行改进。

五、实验数据与分析以下是在实验中记录的部分数据:|输入信号频率(Hz)|测量值(Hz)|误差(%)||||||100|98|2||500|495|1||1000|990|1||2000|1980|1|从数据中可以看出,测量值与输入信号的实际频率存在一定的误差。

频率计实验报告(二)引言概述:本文是关于频率计实验报告的第二篇。

在上一篇实验报告中,我们介绍了频率计的原理和使用方法。

在本文中,我们将继续讨论频率计的准确性、稳定性以及实验中可能遇到的问题和解决方法。

通过本次实验,我们将深入了解频率计的性能和应用情况。

正文:一、频率计的准确性1. 选择合适的输入信号:合适的输入信号能够提高频率计的准确性。

应根据实际需求选择合适的信号源,例如使用稳定的标准信号源进行校准,或者根据被测信号的特点进行合理选择。

2. 校准频率计:频率计应定期进行校准,确保准确性。

校准过程中需注意输入电平、信号形状等因素对准确性的影响,及时进行调整和校准,提高频率计的准确性。

二、频率计的稳定性1. 加强电源管理:频率计的稳定性与供电电压、电源干扰等因素密切相关。

合理管理电源,选择稳定的供电电压,避免电源波动对频率计稳定性的影响。

2. 提高抗干扰能力:频率计应具备一定的抗干扰能力,可以通过加装滤波器、进行屏蔽等方式减小外部干扰对频率计的影响,提高稳定性。

3. 保持恒温环境:频率计对环境温度敏感,应保持恒温环境,避免温度变化对频率计稳定性的影响。

三、实验中可能遇到的问题及解决方法1. 频率计读数不稳定:可能是由于输入信号波动引起的,可以尝试增加信号源的稳定性或调整信号输入方式。

2. 频率计误差较大:可能是由于输入电平过高或过低导致的,可以通过减小或增大输入信号电平进行调整。

3. 频率计显示故障:可能是由于设备故障引起的,可以检查设备连接是否正常、是否存在损坏等问题,并进行相应维修或更换操作。

四、实验中的注意事项1. 注意输入信号的频率范围:在实验中应选择适合频率范围的输入信号,避免超出频率计的测量范围。

2. 避免过高电压输入:过高的输入电压可能导致频率计损坏或显示异常,需根据设备的额定电压进行输入控制。

3. 防止外界干扰:实验时需注意周围环境的电磁干扰,如尽量远离其他电磁辐射源,以确保测量准确性和稳定性。

图1 拍频波场在某一时刻t 的空间分布 光拍法测量光速 【实验目的】1. 掌握光拍频法测量光速的原理和实验方法。

2. 通过测量光拍的波长和频率来确定光速。

【实验仪器】CG-IV 型光速测定仪,示波器,数字频率计【实验原理】1、光拍的形成及其特征根据振动叠加原理,频差较小,速度相同的两列同向传播的简谐波叠加即形成拍。

若有振幅相同为E0、圆频率分别为1ω和2ω(频差12ωωω∆=-较小)的二光束:1011120222cos()cos()E E t k x E E t k x ωφωφ=-+⎫⎬=-+⎭ (1)式中112/k πλ=,222/k πλ=为波数, 1ϕ和2ϕ分别为两列波在坐标原点的初位相。

若这两列光波的偏振方向相同,则叠加后的总场为:121212012122cos[()]22cos[()](2)22x E E E E t c x t c ωωφφωωφφ--=+=-+++⨯-+上式是沿轴方向的前进波,其圆频率为12()/2ωω+,振幅为1202cos[()]22x E t c ωφφ∆--+,因为振幅绝对值以频率为12/2f f f ωπ∆=∆=-周期性地变化,所以被称为拍频波,∆f 称为光拍波频率。

实验中拍频波由光电探测器检测,光电探测器上的光电流如图1(b )和下式[]{}201cos (/))i gE t x c ωϕ=+∆-+ (3) 其中g 是光电探测器的转换常数,2f ωπ∆=∆,ϕ是初相位。

如果有两路光频波,使其通过不同光程后入射同一光电探测器,则该探测器所输出的两个光拍信号的位相差ϕ∆与两路光的光程差L ∆之间的关系 2L f L c c ωπϕ∆⋅∆∆⋅∆∆== (4) 当πϕ2=∆时,∆L=Λ,恰为光拍波长,此时上式简化为c f =∆⋅Λ (5)可见,只要测定了Λ和f ∆,即可确定光速c 。

2.光拍信号的检测用光电检测器(如光电倍增管等)接收光拍频波,可把光拍信号变为电信号。

频率计的制作实验报告实验目的:本实验的目的是通过制作一个简单的频率计,了解频率计的工作原理以及实际应用。

实验仪器与材料:1. 模块化电子实验箱2. 函数信号发生器3. 示波器4. 电压表5. 电阻、电容等基本元件实验原理:频率计是用于测量信号频率的一种仪器。

其基本原理是利用周期性信号的周期长度与频率之间的倒数关系,通过计算周期长度来确定信号的频率。

实验步骤:第一步:搭建电路1. 将函数信号发生器的输出接入电路板上的输入端,作为输入信号源。

2. 将电路板上的元件按照电路图连接,包括电容、电阻等。

确保电路连接正确。

第二步:调试电路1. 将函数信号发生器的频率设置为一个已知的数值,例如1000Hz。

2. 使用示波器测量电路输出端信号的周期长度。

3. 使用计算器计算出信号的频率。

4. 调整电路参数,直到测量到的频率与设定的频率相等。

第三步:验证测量准确性1. 将函数信号发生器的频率调整到其他已知值,例如2000Hz。

2. 重复上述步骤,测量并计算信号的频率。

3. 比较测量到的频率与设定的频率,验证测量准确性。

实验结果与分析:通过实验,我们成功制作了一个简单的频率计。

在调试电路的过程中,我们可以通过测量输出信号的周期长度,并利用频率的倒数与周期长度的关系计算出信号的频率。

通过与设定的频率进行比较,验证了测量的准确性。

实验中可能存在的误差主要来自于电路元件的稳定性以及测量设备的精度。

为了提高测量准确性,可以选择更稳定的元件,并使用更精确的测量设备。

实验结论:本实验通过制作一个简单的频率计,深入了解了频率计的工作原理和实际应用。

通过测量信号的周期长度并计算出频率,我们可以准确地测量信号的频率。

实验结果验证了测量的准确性,并提出了进一步提高准确性的建议。

频率计在电子测量中具有重要的应用价值,可以广泛应用于通信、电子设备维修等领域。

频率计实验报告频率计实验报告xx011014 数字逻辑与处理器基础实验三频率计实验实验目的:掌握频率计的原理和设计方法。

实验工具:1 Verilog语言2 Quartus II 9.03 DE2实验板实验设计:1 总体思路以及模块总述设计的基本思路是按照实验指导书上给出的原理图划分模块。

①待测信号产生模块signalinput.v :由指导书给出,用于产生待测信号sigin ;② 1Hz 时钟产生模块clk_1hz.v:通过实验板50MHz 产生1Hz 时钟clk_1hz;③控制信号产生模块control.v :通过1Hz 时钟,产生频率计所需的使能信号en ,同步清零信号reset ,锁存信号la ,生成一个3秒钟的频率计数周期;④十分频模块div_10.v:若量程选择信号sw_2为高电平,则待测信号需进行十分频;⑤计数器模块counter.v :频率计的核心部分,包括四位十进制计数器,以及对应七段译码器的译码器。

这里我把实验指导书中的译码模块整合在了里面,原因是认为在这个设计中单做一个译码模块意义不大,整合在里面翻倒方便一些;⑥信号锁存模块lat.v :当锁存信号la 为高电平时,锁存输出持续显示;⑦顶层模块div.v :进行各分立模块的功能综合;2 模块分述(1) 待测信号产生模块代码:module signalinput(testmode,sysclk,sigin);input [1:0] testmode;//00,01,10,11分别代表4种频率,分别为3125,6250,50,12500Hz ,使用SW1~SW0来控制input sysclk;//系统时钟50Moutput sigin;//输出待测信号reg[20:0] state;reg[20:0] divide;reg sigin;initialbeginsigin=0;state=21"b[***********]000;divide=21"b000000_1111_1010_0000000; endalways@(testmode)begincase(testmode[1:0])2"b00:divide=21"d16000; //3125Hz2"b01:divide=21"d8000; //6250Hz2"b10:divide=21"d1000000; //50Hz2"b11:divide=21"d4000; //12500Hzendcaseendalways@(posedge sysclk)//按divide 分频beginif(state==0)sigin=~sigin;state=state+21"b0_00__0000_0000_0000_0000_10; if(state==divide)state=27"b000_0000_0000_0000_0000_0000_0000; endendmodule可以看出大致由两部分构成:频率选择、分频。

实验三数字频率计的设计一、实验目的1.掌握VHDL语言的基本结构。

2.掌握VHDL层次化的设计方法。

3.掌握VHDL基本逻辑电路的综合设计应用。

二、实验原理图1是8位十进制数字频率计的电路逻辑图,它由一个测频控制信号发生器CNTEN、8个有时钟使能的十进制计数器CNT10、一个32位锁存器REG32B组成。

以下分别叙述频率计各逻辑模块的功能与设计方法。

图18位十进制数字频率计逻辑图1)测频控制信号发生器设计频率测量的基本原理是计算每秒钟内待测信号的脉冲个数。

这就要求CNTEN的计数使能信号TSTEN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA 使能端进行同步控制。

当TSTEN高电平时,允许计数;低电平时,停止计数,并保持其所计的数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进32位锁存器REG32B中,并由外部的7段译码器译出并稳定显示。

锁存信号之后,必须有一清零信号CLR_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

测频控制信号发生器的工作时序如图2所示。

为了产生这个时序图,需首先建立一个由D 触发器构成的二分频器,在每次时钟CLK上沿到来时其值翻转。

其中控制信号时钟CLK的频率取1 Hz,而信号TSTEN的脉宽恰好为1 s,可以用作闸门信号。

此时,根据测频的时序要求,可得出信号LOAD和CLR_CNT的逻辑描述。

由图1可见,在计数完成后,即计数使能信号TSTEN在1 s的高电平后,利用其反相值的上跳沿产生一个锁存信号LOAD,0.5 s后,CLR_CNT产生一个清零信号上跳沿。

高质量的测频控制信号发生器的设计十分重要,设计中要对其进行仔细的实时仿真(TIMING SIMULATION),防止可能产生的毛刺。

图2 测频控制信号发生器工作时序2) 寄存器REG32B 设计设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

若已有32位BCD 码存在于此模块的输入口,在信号LOAD 的上升沿后即被锁存到寄存器REG32B 的内部,并由REG32B 的输出端输出,然后由实验板上的7段译码器译成能在数码管上显示输出的相对应的数值。

3) 十进制计数器CNT10的设计如图1所示,此十进制计数器的特殊之处是,有一时钟使能输入端ENA ,用于锁定计数值。

当高电平时计数允许,低电平时禁止计数。

三、实验设备计算机软件:Quartus IIEDA 实验箱。

主芯片:EPM7128SLC84-15或EP1K100QC208-3。

下载电缆,导线等。

四、实验内容及步骤设计并调试好一个8位十进制数字频率计。

要求编写上述8位十进制数字频率计逻辑图中的各个模块的VHDL 语言程序,并完成8位十进制数字频率计的顶层设计,然后利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

(一)测频控制器CTL 的设计1.根据测频控制信号发生器的基本原理编写CTL 模块的VHDL 程序,并对其进行编译和仿真,初步验证设计的正确性。

VHDL 参考源程序: (1)--程序包 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; PACKAGE PAKG ISSUBTYPE DIGIT_T IS INTEGER RANGE 0 TO 9; TYPE DISP_T IS ARRAY (7 DOWNTO 0) OF DIGIT_T; END PACKAGE PAKG; (2)CTL 模块 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CTLIS PORT (CLK: IN STD_LOGIC; --1 Hz 测频控制时钟 CNTEN: OUT STD_LOGIC; --计数器时钟使能 CLR_CNT: OUT STD_LOGIC; --计数器清零 LOAD: OUT STD_LOGIC); --输出锁存信号END ENTITY CTL;[I] RST [I] CLK [O] TSTEN [O] LOAD [O] CLR_CNTARCHITECTURE ART OF CTL ISSIGNAL DIV2CLK: STD_LOGIC;BEGINPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THEN -- 1 Hz时钟二分频DIV2CLK<=NOT DIV2CLK;END IF ;END PROCESS;PROCESS (CLK, DIV2CLK ) ISBEGINIF CLK='0' AND DIV2CLK ='0' THEN --产生计数器清零信号CLR_CNT<='1';ELSE CLR_CNT<='0' ;END IF;END PROCESS;LOAD<=NOT DIV2CLK;CNTEN<=DIV2CLK;END ARCHITECTURE ART;(二)十进制计数器的设计编写十进制计数器CNT10模块的VHDL程序,并对其进行编译和仿真,初步验证设计的正确性。

VHDL参考源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE work.pakg.ALL;ENTITY CNT10 ISPORT(CLK: IN STD_LOGIC;CLR: IN STD_LOGIC;ENA: IN STD_LOGIC;CQ: OUT DIGIT_T;CO: OUT STD_LOGIC);END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI: INTEGER RANGE 0 TO 15;BEGINPROCESS(CLK, CLR, ENA) ISBEGINIF CLR='1' THEN CQI<=0; --计数器异步清零ELSIF CLK'EVENT AND CLK= '1' THENIF ENA='1' THENIF CQI<9 THEN CQI<=CQI+1;ELSE CQI<=0; END IF; --等于9, 则计数器清零END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CQI=9 THEN CO<= '1'; --进位输出ELSE CO<= '0'; END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;(三)32位寄存器的设计编写寄存器REG32模块的VHDL程序,并对其进行编译和仿真,初步验证设计的正确性。

VHDL参考源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE work.pakg.ALL;ENTITY REG32 ISPORT (CLK: IN STD_LOGIC;DIN: IN DISP_T;DOUT: OUT DISP_T);END ENTITY REG32;ARCHITECTURE ART2 OF REG32 ISBEGINPROCESS( CLK,DIN ) ISBEGINIF(CLK'EVENT AND CLK='1')THENDOUT<=DIN;END IF;END PROCESS;END ARCHITECTURE ART2;(四)数码管动态扫描显示电路设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE WORK.PAKG.ALL;ENTITY disp_scan ISPORT(CLK: IN STD_LOGIC;num: IN DISP_T;LEDW: OUT STD_LOGIC_VECTOR(2 DOWNTO 0);SEG7: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY disp_scan;ARCHITECTURE ART OF disp_scan ISsignal temp:DIGIT_T;signal cnt:STD_LOGIC_VECTOR(2 DOWNTO 0);beginPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CNT="111" THENCNT<="000";ELSECNT<=CNT+'1';END IF;END IF;END PROCESS;LEDW<=CNT;PROCESS(CNT,num,temp) ISBEGINCASE CNT ISWHEN "000" => TEMP<=num(0);WHEN "001" => TEMP<=num(1);WHEN "010" => TEMP<=num(2);WHEN "011" => TEMP<=num(3);WHEN "100" => TEMP<=num(4);WHEN "101" => TEMP<=num(5);WHEN "110" => TEMP<=num(6);WHEN "111" => TEMP<=num(7);WHEN OTHERS=> TEMP<=0;END CASE;CASE TEMP ISWHEN 0=> SEG7<="00111111";WHEN 1=> SEG7<="00000110";WHEN 2=> SEG7<="01011011";WHEN 3=> SEG7<="01001111";WHEN 4=> SEG7<="01100110";WHEN 5=> SEG7<="01101101";WHEN 6=> SEG7<="01111101";WHEN 7=> SEG7<="00000111";WHEN 8=> SEG7<="01111111";WHEN 9=> SEG7<="01101111";WHEN OTHERS=> SEG7<="00111111";END CASE;END PROCESS;END ARCHITECTURE ART;(五)分频器模块设计分频器模块将输入1KHZ时钟转换为1HZ时钟输出。