硬件描述语言2

- 格式:ppt

- 大小:579.00 KB

- 文档页数:34

fpga的编程方法FPGA(Field-Programmable Gate Array)是一种可编程的逻辑器件,能够根据用户的需求进行编程,实现各种不同的功能。

FPGA的编程方法有多种,包括硬件描述语言和图形化编程工具。

本文将介绍几种常用的FPGA编程方法,并对其特点和应用进行详细阐述。

一、硬件描述语言(HDL)硬件描述语言是一种用于描述数字电路的语言,常用的HDL有VHDL (VHSIC Hardware Description Language)和Verilog。

这种编程方法将硬件电路抽象为逻辑门、寄存器等基本元素,并通过编写代码来描述它们之间的连接关系和功能。

HDL具有描述精确、灵活性强的特点,适用于复杂的电路设计和开发。

使用HDL进行FPGA编程的过程大致包括以下几个步骤:1. 设计电路结构:根据需求和功能设计电路的逻辑结构,包括各个模块的功能和连接关系。

2. 编写HDL代码:使用VHDL或Verilog编写描述电路结构和功能的代码,包括模块实例化、信号赋值、时序控制等。

3. 综合与布局:将HDL代码综合为门级网表,然后进行布局布线,生成可配置的FPGA逻辑电路。

4. 下载与调试:将生成的逻辑电路下载到FPGA芯片中,并进行功能验证和调试。

二、图形化编程工具除了使用HDL进行编程,FPGA的编程方法还包括使用图形化编程工具,如LabVIEW FPGA和Xilinx System Generator等。

这些工具提供了可视化的界面,用户只需通过拖拽和连接图形元件,即可完成对FPGA的编程。

图形化编程工具的使用过程相对简单,适合初学者或对硬件电路编程不熟悉的人。

用户只需选择所需的功能模块,将其拖入工作区域,并通过连接线将各个模块连接起来。

然后,通过配置模块的参数和时序,即可生成对应的FPGA逻辑电路。

三、特殊领域的FPGA编程方法除了传统的HDL和图形化编程工具,还有一些特殊领域的FPGA编程方法。

VHDL与Verilog语言VHDL(VHSIC hardware description language)和Verilog是用于电子系统设计的硬件描述语言(HDL)。

这两种语言被广泛应用于数字逻辑设计和仿真,以及硬件描述、验证和综合。

1. VHDL(VHSIC hardware description language)VHDL是一种结构化的硬件描述语言,最初由美国国防部高速集成电路计划办公室(VHSIC,Very High Speed Integrated Circuits)开发。

VHDL以其强大的功能和灵活性而闻名,并被广泛用于数字系统的设计和验证。

VHDL的编写包括实体(Entity)和体(Architecture)两个主要部分。

实体部分描述了数字系统的输入输出接口、信号和组件的声明,而体部分描述了实体的内部结构、信号处理和逻辑功能。

VHDL具有丰富的数据类型、运算符和控制结构,可以方便地描述数字电路的行为和结构。

它还提供了强大的仿真和验证功能,使设计人员能够在开发和测试阶段快速迭代和调试设计。

2. VerilogVerilog是一种硬件描述语言,最初由Gateway Design Automation公司(现在是Cadence Design Systems的一部分)开发。

Verilog以其简洁的语法和易学易用的特性而受到广泛欢迎,并成为工业界标准。

Verilog的设计由模块(Module)组成,每个模块描述了一个黑盒子,包含输入和输出端口以及内部的逻辑功能。

模块可以进行层次化组合,从而实现较复杂的系统级设计。

Verilog的语法类似于C语言,具有类似的数据类型、运算符和控制结构。

它还提供了时序建模的能力,使设计人员能够描述数字电路的时序行为。

3. VHDL与Verilog的比较VHDL和Verilog在语法和功能上有一些区别,但它们都可以用于数字电路的设计和仿真。

以下是它们之间的一些比较:3.1 语法风格VHDL采用结构化的编程风格,需要明确的体、过程和信号声明,可以更好地控制和描述系统的结构和行为。

verilog的三种描述方式

Verilog是一种硬件描述语言,用于描述和设计数字电路。

在Verilog中,有三种不同的描述方式:

1. 行为描述方式(Behavioral Modeling):行为描述方式是一

种基于事件的描述方法,用于描述数字电路的行为和功能。

在行为描述方式中,使用进程或函数来描述电路的操作和行为。

例如,使用if-else语句、for循环和并行块等来描述数字电路

的行为。

行为描述方式更接近于编程语言,可以方便地实现复杂的逻辑和算法。

2. 数据流描述方式(Dataflow Modeling):数据流描述方式是

一种基于信号流动的描述方法,用于描述数字电路的数据流和信号传递。

在数据流描述方式中,使用逻辑运算符(如AND、OR、NOT等)和信号赋值等来描述数字电路的数据流。

数据

流描述方式更接近于电路的物理结构,可以方便地实现组合逻辑。

3. 结构描述方式(Structural Modeling):结构描述方式是一

种基于模块和组件的描述方法,用于描述数字电路的结构和组成。

在结构描述方式中,使用模块实例化、端口连接和网表等来描述数字电路的结构。

结构描述方式更接近于电路的布局和连接,可以方便地进行模块化设计和层次化设计。

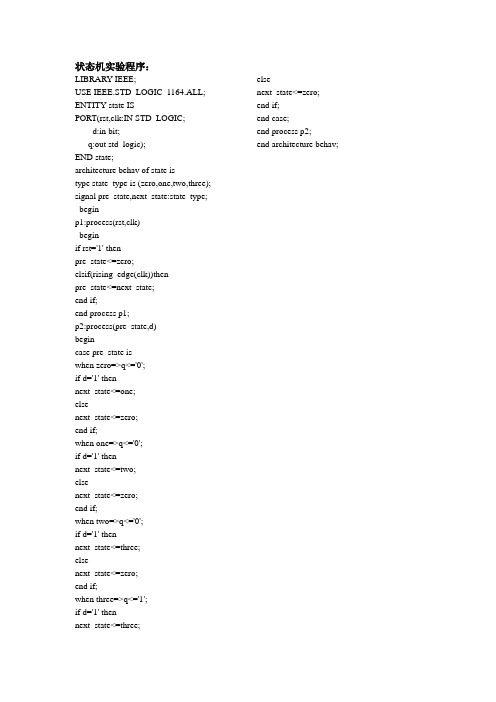

状态机实验程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY state ISPORT(rst,clk:IN STD_LOGIC;d:in bit;q:out std_logic);END state;architecture behav of state istype state_type is (zero,one,two,three); signal pre_state,next_state:state_type; beginp1:process(rst,clk)beginif rst='1' thenpre_state<=zero;elsif(rising_edge(clk))thenpre_state<=next_state;end if;end process p1;p2:process(pre_state,d)begincase pre_state iswhen zero=>q<='0';if d='1' thennext_state<=one;elsenext_state<=zero;end if;when one=>q<='0';if d='1' thennext_state<=two;elsenext_state<=zero;end if;when two=>q<='0';if d='1' thennext_state<=three;elsenext_state<=zero;end if;when three=>q<='1';if d='1' thennext_state<=three; elsenext_state<=zero;end if;end case;end process p2;end architecture behav;四位移位寄存器的程序:元件例化程序:library ieee;use ieee.std_logic_1164.all;--use ieee.std_logic_unsigned.all;--use ieee.std_logic_arith.all;entity shift4 isport(ain,clk,rst:in std_logic; b:out std_logic);end entity shift4;architecture behav of shift4 iscomponent d_ff isport(clk,clr,d:in std_logic;q:out std_logic);end component d_ff;signal z:std_logic_vector(0 to 4);beginz(0)<=ain;u1:for i in 0 to 3 generatedff:d_ff port map(clk,rst,z(i),z(i+1));end generate;b<=z(4);end behav;--D触发器程序:library ieee;use ieee.std_logic_1164.all;entity d_ff isport(clk,clr,d:in std_logic;q:out std_logic);end entity d_ff;architecture one of d_ff issignal q_temp:std_logic;beginprocess(clk,clr)beginif clr='0'thenq_temp<='0';elsif(clk'event and clk='1')thenq_temp<=d;end if;end process;q<=q_temp;end architecture one;信号传递程序:library ieee;use ieee.std_logic_1164.all;--use ieee.std_logic_unsigned.all;--use ieee.std_logic_arith.all;entity shift4_unit isport(ain,clk:in std_logic;y:out std_logic);end entity shift4_unit; architecture behav of shift4_unit isbeginprocess(clk)variable a,b,c,d:std_logic;beginif(clk'event and clk='1')theny<=a;a:=b;b:=c;c:=d;d:=ain;end if;end process;end architecture behav;实验程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY hadd ISPORT(a,b: IN STD_LOGIC;co,so: OUT STD_LOGIC); END ENTITY hadd; ARCHITECTURE behav OF hadd IS BEGINPROCESS(a,b) ISBEGINco<=a and b;so<=a xor b;END PROCESS ;END ARCHITECTURE behav; LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT(a,b: IN STD_LOGIC;c: OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE beh OF or2a ISBEGINPROCESS (a,b) ISBEGINC<=a or b ;END PROCESS;END ARCHITECTURE beh;实验仿真图如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fadd ISPORT(ain,bin,cin:IN STD_LOGIC;cout,sum: OUT STD_LOGIC);END fadd;ARCHITECTURE behavior OF fadd ISCOMPONENT haddPORT(a,b:IN STD_LOGIC;co,so: OUT STD_LOGIC);END COMPONENT hadd;COMPONENT or2aPORT(a,b: IN STD_LOGIC;c: OUT STD_LOGIC);END COMPONENT or2a;SIGNAL d,e,f: STD_LOGIC;BEGINU1: hadd PORT MAP(a=>ain,b=>bin,co=>d,so=>e);U2: hadd PORT MAP(a=>e,b=>cin,co=>f,so=>sum);U3: or2a PORT MAP(a=>d,b=>f,c=>cout);END ARCHITECTURE behavior;。

verilog and语句摘要:一、Verilog简介1.Verilog是一种硬件描述语言2.用于描述数字电路和模拟混合信号电路3.设计人员可以用它来描述电路的结构和功能二、And语句在Verilog中的作用1.And语句用于连接两个或多个信号2.实现逻辑与操作3.常见于组合逻辑电路的设计三、And语句的语法1.基本语法2.示例四、And语句的注意事项1.保持信号宽度一致2.避免出现“X”信号3.使用合适的括号正文:Verilog是一种硬件描述语言,广泛应用于数字电路和模拟混合信号电路的设计领域。

设计人员可以用它来描述电路的结构和功能,从而实现对电路的控制。

在Verilog中,And语句是一种重要的逻辑连接方式,用于实现逻辑与操作。

下面,我们将详细介绍And语句的语法和使用注意事项。

首先,我们来看一下And语句的基本语法。

在Verilog中,And语句用于连接两个或多个信号。

它的基本语法如下:```A & B;```其中,A和B是需要连接的信号名。

在实际应用中,还可以使用括号来改变优先级,如下所示:```A & (B | C);```接下来,我们通过一个示例来演示如何使用And语句。

假设我们有一个4位全加器,其输入为A、B、Cin,输出为SUM和Cout。

我们可以用Verilog 代码来描述这个全加器,如下所示:```module full_adder(input A,input B,input Cin,output SUM,output Cout);assign SUM = A ^ B ^ Cin; // 异或操作实现和assign Cout = (A & B) | (A & Cin) | (B & Cin); // 与操作实现进位endmodule```最后,我们需要注意使用And语句时的一些事项。

首先,保持信号宽度一致。

例如,如果A和B是4位信号,那么Cin也应该是4位信号。