一种低噪声高线性度CMOS上变频混频器

- 格式:pdf

- 大小:334.37 KB

- 文档页数:5

一种高线性低噪声CMOS混频器设计王琳;冷令【期刊名称】《信息技术》【年(卷),期】2017(000)009【摘要】混频器应用在多标准领域中,对混频器的线性度和噪声性能提出了严格的要求.文中提出了一种新型的高线性、低噪声CMOS混频器.该混频器同时采用了三阶失真抵消技术和噪声抵消技术.采用TSMC 0.13μm CMOS工艺进行设计并流片实现,测试结果表明,较之传统的吉尔伯特混频器而言,文中混频器的输入三阶交调点IIP3增加了6.18dBm,噪声系数下降了3.5dB,而用于三阶失真抵消技术和噪声抵消技术的电路部分仅使混频器多消耗了0.85mA的电流.%The linearity and noise requirements in multistandard applications make the design of mixers so challenging.In this paper a new high-linear and low-noise CMOS mixer is proposed that utilizes thirdorder distortion cancellation technology and noise cancellation technology.The implementation using TSMC 0.13μm CMOS technology demonstrated that IIP3 and noise figure of the proposed mixer have 6.18 dBm and 3.5 dB improvements in comparison with the conventional Gilbert-type mixer while the additional circuits used for the third-order distortion and noise cancellation mechanisms have a total current consumption of 0.85 mA.【总页数】5页(P154-158)【作者】王琳;冷令【作者单位】中山市中等专业学校,广东中山528458;中山职业技术学院,广东中山528404【正文语种】中文【中图分类】TN432【相关文献】1.一种高增益低噪声CMOS混频器设计 [J], 程知群;李进;傅开红;朱雪芳;高俊君2.0.18μm CMOS高线性低噪声混频器设计 [J], 张照锋; 徐结海; 张长春3.一种低噪声高线性度CMOS上变频混频器 [J], 金黎明;倪熔华;唐长文;闵昊4.一种低噪声高增益CMOS混频器设计 [J], 高丽娜;庞建丽5.一种低噪声高电源抑制比CMOS低压差线性稳压器 [J], 阴亚东;阎跃鹏因版权原因,仅展示原文概要,查看原文内容请购买。

一种高增益低噪声CMOS混频器设计程知群;李进;傅开红;朱雪芳;高俊君【期刊名称】《电子器件》【年(卷),期】2009(032)004【摘要】设计了一种基于跨导互补结构的电流注入混频器,通过在吉尔伯特混频器电路的本振开关管源极增加PMOS管形成电流注入电路减小本振端的偏置电流,改善电路的闪烁噪声和增大电路的增益.采用SMIC 0.18μm标准CMOS工艺设计.在本振(LO)信号的频率为1.571 GHz,射频(RF)信号频率为1.575 GHz时,混频器的增益为17.5 dB,噪声系数(NF)为8.35 dB,三阶交调截止点输入功率(IIP3)为-4.6 dBm.混频器工作电压1.8 V.直流电流为8.8 mA,版图总面积为0.63 mm × 0.78 mm.【总页数】5页(P737-741)【作者】程知群;李进;傅开红;朱雪芳;高俊君【作者单位】杭州电子科技大学射频电路与系统教育部重点实验室,杭州,310018;杭州电子科技大学射频电路与系统教育部重点实验室,杭州,310018;杭州电子科技大学射频电路与系统教育部重点实验室,杭州,310018;杭州电子科技大学射频电路与系统教育部重点实验室,杭州,310018;杭州电子科技大学射频电路与系统教育部重点实验室,杭州,310018【正文语种】中文【中图分类】TN4【相关文献】1.一种高线性低噪声CMOS混频器设计 [J], 王琳;冷令2.基于CMOS工艺的低噪声、高增益混频器 [J], 吕瑛;康星朝3.低噪声和高增益CMOS下变频混频器设计 [J], 王良坤;马成炎;叶甜春4.一种低电压、低噪声、高增益CMOS折叠式混频器 [J], 韦保林;戴宇杰;张小兴;吕英杰;刘慧敏5.一种低噪声高增益CMOS混频器设计 [J], 高丽娜;庞建丽因版权原因,仅展示原文概要,查看原文内容请购买。

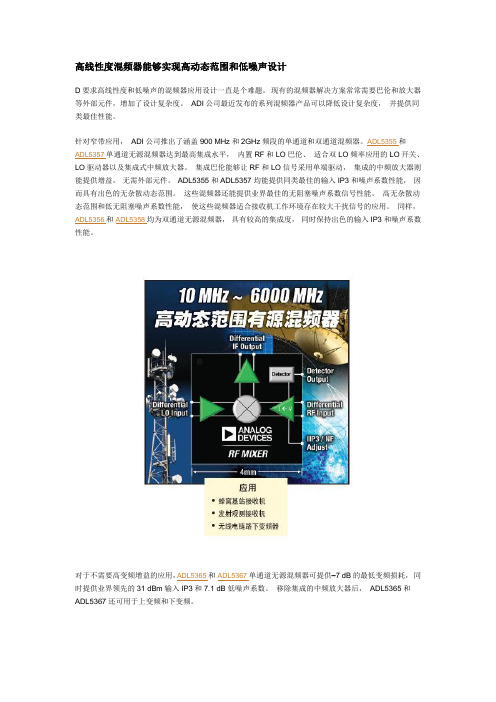

高线性度混频器能够实现高动态范围和低噪声设计D要求高线性度和低噪声的混频器应用设计一直是个难题。

现有的混频器解决方案常常需要巴伦和放大器等外部元件,增加了设计复杂度。

ADI公司最近发布的系列混频器产品可以降低设计复杂度,并提供同类最佳性能。

针对窄带应用,ADI公司推出了涵盖900 MHz和2GHz频段的单通道和双通道混频器。

ADL5355和ADL5357单通道无源混频器达到最高集成水平,内置RF和LO巴伦、适合双LO频率应用的LO开关、LO驱动器以及集成式中频放大器。

集成巴伦能够让RF和LO信号采用单端驱动,集成的中频放大器则能提供增益,无需外部元件。

ADL5355和ADL5357均能提供同类最佳的输入IP3和噪声系数性能,因而具有出色的无杂散动态范围。

这些混频器还能提供业界最佳的无阻塞噪声系数信号性能。

高无杂散动态范围和低无阻塞噪声系数性能,使这些混频器适合接收机工作环境存在较大干扰信号的应用。

同样,ADL5356和ADL5358均为双通道无源混频器,具有较高的集成度,同时保持出色的输入IP3和噪声系数性能。

对于不需要高变频增益的应用,ADL5365和ADL5367单通道无源混频器可提供–7 dB的最低变频损耗,同时提供业界领先的31 dBm输入IP3和7.1 dB低噪声系数。

移除集成的中频放大器后,ADL5365和ADL5367还可用于上变频和下变频。

这些无源单、双通道混频器设计采用3.3 V ~ 5 V电源供电,并采用先进的SiGe双极性工艺制造,提供2000 V人体模型ESD保护,因此与敏感的GaAs混频器相比能简化处理程序。

对于宽带混频器应用,ADI公司最近推出了ADL5801和ADL5802宽带有源混频器,其工作频率范围为10 MHz ~ 6000 MHz,在现有混频器中最宽。

这两款混频器均提供1.5 dB的变频增益,无需附加中频放大器。

这些有源混频器提供同类最佳的无阻塞噪声系数信号性能和无杂散动态范围。

基于CMOS工艺的低噪声放大器与混频器设计的开题报告摘要:本文旨在设计一个基于CMOS工艺的低噪声放大器与混频器,用于射频接收系统中,以实现高度灵敏和有效的信号传输。

本文介绍了当前低噪声放大器和混频器设计的相关研究,并分析了它们的利弊和限制。

基于这些分析结果,本文提出了一种基于CMOS工艺的低噪声放大器与混频器的设计方法,包括电路结构、参数选择、电路分析和模拟结果。

最后,进行了性能评估和对未来工作的展望。

关键词:CMOS工艺,低噪声放大器,混频器,射频接收系统引言:随着无线通信和射频技术的发展,射频接收系统已经成为现代通信系统中重要的组成部分。

其中,低噪声放大器和混频器是射频接收系统中关键的基础模块,用于提高灵敏度和增强信号质量。

在过去几十年中,随着半导体技术的不断进步,各种低噪声放大器和混频器的设计方法和实现技术不断更新迭代。

在这些设计方法中,CMOS工艺因其低成本、低功耗、可靠性高等优点,成为一种常用的设计方法。

本文旨在设计一个基于CMOS工艺的低噪声放大器与混频器,以提高射频接收系统的性能。

本文首先介绍了当前低噪声放大器和混频器设计的相关研究,并分析了它们的利弊和限制。

然后,本文提出了一种基于CMOS工艺的低噪声放大器与混频器的设计方法,包括电路结构、参数选择、电路分析和模拟结果。

最后,进行了性能评估和对未来工作的展望。

一、低噪声放大器和混频器的研究现状1.1 低噪声放大器低噪声放大器是射频接收系统中关键的基础模块,用于放大微弱的射频信号。

在过去几十年中,出现了许多基于不同技术的低噪声放大器设计方法,包括Bipolar工艺、GaAs、SiGe、CMOS等。

其中,CMOS工艺因其低成本、低功耗、可靠性高等优点,成为一种常用的设计方法。

1.2 混频器混频器是射频接收系统中关键的基础模块,用于将高频信号转换成中频信号。

在过去几十年中,出现了许多基于不同技术的混频器设计方法,包括多种被动混频器、有源混频器和集成混频器等。

低功耗高线性度的低噪声放大器及混频器设计与实现的开题报告一、研究背景和意义随着现代通信技术的不断发展,高性能的射频电路的需求不断提高。

低噪声放大器(Low Noise Amplifier,LNA)和混频器(Mixer)是射频电路中两个非常重要的模块,它们的性能直接影响整个射频电路的性能。

为了实现高速率和广带的通信,现代无线通信系统采用了高频率的信号传输,这就需要放大器和混频器在高频率范围内具有很高的增益和线性度。

其中,低噪声放大器是用来放大射频信号并提高信噪比的,而混频器则是将射频信号和本地振荡器(Local Oscillator,LO)结合起来产生中频信号(Intermediate Frequency,IF)的重要模块。

因此,低功耗高线性度的低噪声放大器和混频器的研究具有重要的理论意义和实际应用价值。

二、研究内容和方法本课题旨在设计和实现一种低功耗高线性度的低噪声放大器和混频器,主要涉及以下内容:1. 低噪声放大器设计:采用双极性晶体管作为放大器的工作元件,并采用共源极电路结构。

使用微波电路仿真软件ADS进行电路设计和优化,同时结合模拟仿真和数字仿真的方法进行电路的性能分析和测试。

2. 混频器设计:采用双平衡混频器结构,并采用有源混频器的设计方法。

通过改进混频器的电路结构和参数设计,实现低功耗和高线性度的需求。

3. 电路实现与测试:设计出低功耗高线性度的低噪声放大器和混频器的电路,并在射频测试台上进行实际测试和性能评估。

结果分析和总结。

本课题主要采用模拟仿真和数字仿真的方法进行电路设计和性能分析,并在实验室中利用射频测试台对电路进行测试和性能评估,得到较为准确的实验数据和性能指标。

同时,结合文献研究和理论分析,进行深入探究和总结。

三、预期成果和意义通过本课题的研究,预期可以实现低功耗高线性度的低噪声放大器和混频器的设计和实现,并获得较好的性能表现,为高频率射频电路的研究和发展提供重要支持。

这一研究成果将具有以下意义:1. 对高性能射频电路的研究和应用具有重要推动作用,为现代通信技术的发展做出积极贡献。

第17卷第4期 湖南工程学院学报 Vo1.17.No .42007年12月 Jour na lof Hunan I nstitute of Engineering Dec .2007收稿日期6基金项目国家自然科学基金资助项目(666)作者简介邓桂萍(),女,硕士研究生,研究方向射频集成电路设计一种高线性的C MOS 低噪声放大器结构邓桂萍1,王春华2(1.湘潭大学信息工程学院,湖南湘潭411105;2.湖南大学计算机与通信学院,湖南长沙410082) 摘 要:采用TS MC0.35μmC MOS 工艺,设计了一个5.7G Hz 可用于无线局域网的低噪声放大器,电路在采用单端共源共栅结构的基础上为改善线性度而引进低频陷波网络(Low -frequency -trap Net 2work),用ADS 软件仿真与优化.仿真结果表明,在电源电压1.5V 情况下,噪声系数NF 为1.22dB ,输入反射系数S 11为-15dB ,反向隔离性能S12为-32.9dB ,增益S21为17.8d B ,三阶交截点II P3为+12.7dBm ,功耗为8mW.关键词:低噪声放大器;无线局域网;线性度中图分类号:T M76 文献标识码:A 文章编号:1671-119X (2007)04-0005-040 引言随着无线通信事业的不断发展,人们对无线通信系统的要求越来越高,比如低电压低功耗、低噪声、大动态范围、高灵敏度和高线性度等,而处于接收机前端的低噪声放大器(l ow noise amplifier,简称LNA )对于提高整个系统的线性度起着关键作用.这就意味着我们在设计低噪声放大器中必须在增益、噪声、线性度及功耗等性能指标中要合理的折衷.近年来出现了大量关于提高线性度的文献[1-11],文献[1]采用中等反型区偏置的方法,利用MOSFET 的转移特性及高阶跨导特性,将其偏置在强反型与亚阈区之间的一个最佳栅源偏置电压,此处MOSFET 的三阶跨导为零,理论上电路的三阶非线性为零.但是,这个最佳偏置点对工作频率、负载阻抗、源极电感大小、工艺参数特别是阈值电压涨落等的变化非常敏感.因而实际中一般都是采用线性化技术来提高线性度.文献[2]采用直接补偿法,这种方法为了降低三阶交调,需要付出较大的功耗,而且增益和噪声性能还有所损失.文献[3]采用前馈补偿方法,这种方法实现的前馈补偿电路,电路的增益性能不会损失,但是也仍然需要付出较大的功耗代价.文献[4]采用亚阈区MO SFET 补偿法,利用亚阈区器件的三阶跨导与强反型器件的三阶跨导相抵消来提高LNA 的线性度,但是亚阈区MOSFET 的截止频率f T 很低,当信号频率较高时,补偿效果有可能下降,不适合频率比较高的情况.文献[5]改进文献[4]中的方法,在主支路和补偿支路使用了不同的负反馈电感,文献[6]把文献[4]中的亚阈区MOSFET 换成BJT,但是,因为标准C MOS 工艺中很难获得高性能的BJT,所以这样的改进有较大的局限性.文献[7]采用线性区MOSFET 补偿,这种方法与亚阈区MOSFET 补偿类似,只是用不同的方法去实现三阶跨导的“峰”.文献[8-9]根据Volterr a 级数分析对双极型晶体管BJT 放大器利用不同的带内和带外阻抗特性来提高电路的线性度.前面所提到的文献中只有文献[11]是针对5G HzC MOS LNA 的线性度而做的研究,提出采用前馈失真补偿方法(Feedf or ward D istorti on Cancella tion ),文献中的这种方法虽然对噪声影响不大,但是结构比较复杂,功耗增加许多.其它的文献基本上都是针对5G Hz 以下的电路而提出的线性化技术.本文将根据对单端C MOS 共源共栅结构进行Volterr a 级数分析的结果,提出一个采用低频陷波网络来提高线性度的工作于5.7G Hz C MOS 低噪声放大器,结构简单,用ADS 软件进行仿真优化验证.:2007-0-27:07021:1981-:.1 共源共栅结构的Volterra 级数分析首先对共源级进行Volterr a 级数分析[10].用来推导C MOS 低噪声放大器共源级交调表达式的电路模型如图1,v s 是源电压,Z g 是栅极阻抗,包括栅极电感及寄生电阻,Z s 是源极阻抗,C gs1是栅源电容,v gs 1是栅源电压,i d1是漏极电流,在这里我们忽略场效应管的输出电阻和栅漏电容.共源级的输入参考I M 3可以通过令s 1=j ω1,s 2=j ω2,s 3=j ω3得到,假定s ≈s 1≈s 2并且△s =(s 1-s 2)νs,那么我们可以把输入参考I M 3表示为:I M 3=34A 3(s 1,s 1,-s 2)A 1(2s 1-s 2)v s2≈12Kg 5mA 1(s )32A 1(2s )Z s (2s )+A 1(△s )1+sC gs (Z g +Z s )v s2(1)式中,k =μn C ox 2WL.u n 是电子迁移率,C o x 是栅氧化层电容,W 是管子宽度,L 是管子长度,g m 是跨导,A 1(s),A 2(s),A 3(s )是Volte rra 级数的系数[10].图1 共源级模型 图2 级联共栅级的模型 再来看级联共栅级的Volte rra 级数分析[10].为了把级联场效应管的影响加入三阶交调表达式中,我们使用由图2示出的级联共栅级电路模型.其中i d1是共源级的输出电流.g m 2和C gs2分别为M 2的跨导和栅源电容,假定场效应管M 2的输出电阻很大以致可以忽略.采用与推导共源级非线性方程相似的方法,我们可以得到:I M 2tota l=34g m 2K 21g4m1A 2s (S)[A 1(2s)Z s (2s)+A 1(△s)Z s (△s)][1-A 1(s )Z s ]1g m2+sC gs2-K 1K 23g 2m 1A 21(s )[1-A 1(△s )Z s (△s )]1g m2+sC gs21g m 2+△sC gs2-2K 1K 23g 2m1A 21(s)[1-A 1(2s)Z s (2s)]1g m2-sC gs21g m 2+△sC gs2v s2-K 1K 23g 2m1A 21(s )[1-A 1(△s )Z s (△s )]1g m 2+sC g s21g m 2+△sC gs2-2K 1K 23g2m 1A 21(s )[1-A 1(2s )Z s (2s )]1g m 2-sC gs21g m 2+△sC gs2(2) 然而这个表达式太复杂,我们无法直接从(2)式得出结论而提供对设计的指导,必须借助其他的数学工具,这里就不再详述. 提出的提高线性度方法由于整个放大器的非线性主要由第一级的非线性决定,在这里我们暂不考虑第二级的非线性.从(1)式我们可以看出,三阶交调项与1+sC gs (Z s +Z g )的模相关,对于感性负反馈,s C gs Z s 项为一个负实数而部分抵消了“1”这一项,但是对于阻性和容性负反馈就没有这样的抵消作用,因为阻性负反馈中该项为纯虚数,而容性负反馈中该项为正实数另外,三阶交调项还与()Z ()+(6 湖南工程学院学报 2007年2.2A 12s s 2s A 1△s)Z s (△s)的模相关,这一项由二阶互扰而产生.二阶互扰项表明,三阶交调的大小不光与工作频率相关,也与干扰频率的差和相关.因此,我们要想提高整个放大器的线性度,要么尽可能的减小二阶互扰项2A 1(2s )Z s (2s )+A 1(s )Z s (s )的模,要么尽可能的减小1+s C gs (Z s +Z g )的模.如果我们能使1+s C gs (Z s +Z g )的模趋于0,那么我们就能获得最佳线性度.在前面我们知道,如果是感性负反馈,sCgsZ s 项为一个负实数而可以部分抵消“1”这一项,但这是毕竟有限的.我们还注意到,sC gs Z g 中也有一部分为负实数而可以部分抵消“1”,实际上sC gs Z g 中产生负实数的是Z g 中的感性部分,猜想如果我们能使这一部分增大,那么能抵消“1”的部分又增大了,因而1+sC gs (Z s +Z g )的模减小而达到提高线性度的目的,但是Z g 中的感性部分L g 过大的话不利于我们整个放大器的片上集成,而且在源极电感负反馈结构中为满足输入匹配L g 还受谐振频率和阻抗匹配50Ω的限制.于是在这里我们引入低频陷波网络[8],如图3所示.图3 低噪声放大器结构3 提出的C MOS LNA 电路结构提出的C MOS LNA 电路结构如图3所示,其中M 1、M 2为共源共栅结构,M 1为输入器件,产生与输入电压成正比的小信号漏电流;共栅晶体管M 2用于减小输入与输出之间的相互作用提供良好的隔离性能并抑制了M 1的M ille r 效应;输入匹配仍采用源极电感负反馈结构并由L g 和L s 实现,这种结构在提供很低的噪声系数的同时容易得到50Ω的输入阻抗;L 2和C 2构成调谐电路实现输出匹配;直流工作时晶体管M 3与M 形成电流镜,M 3的宽度相对很小,这里取为M 宽度的十分之一,从而偏置电路消耗的电流最小;电阻R 要取足够的阻值以减小偏置电路的噪声电流;电阻R 1用来调节输入级晶体管M 1的栅源电压和漏极电流以决定静态功耗;C 1用于将射频与直流隔离,选择适当的电容(如10nF ),使其电抗值对于信号频率可忽略不计;L t 和C t 构成了低频陷波网络,为提高电路的线性度.表1 C MOS 低噪声放大器详细模拟结果参数模拟结果参数模拟结果电源电压 1.5V S 11-15dB 频率 5.7GHz S 12-32.9dB 噪声系数 1.22dB S 2117.8dB 功耗8m WII P3+12.7d Bm4 仿真结果根据图3所示电路原理结构,采用TS MC0135μmC MOS 工艺,使用A DS 软件对该LNA 进行模拟与分析优化.表1给出了本文提出的LNA 详细模拟结果,图4(a )~(d )给出了噪声系数NF,输入反射系数S 11,反向传输系数S 12及增益S 21随频率变化的趋势的仿真结果,图5.14(e)给出了线性度II P3仿真结果.7第4期 邓桂萍等:一种高线性的C MOS 低噪声放大器结构112图4 仿真结果5 结 论本文在根据对单端C MOS 共源共栅结构进行Vol 2terra 级数分析的结果的基础上,提出了一个采用低频陷波网络来提高线性度的工作于517G Hz C MOS 低噪声放大器,结构简单.采用TS MC0135μmC MOS 工艺使用A DS 软件进行仿真,仿真结果表明,该低噪声放大器结构具有良好的性能:在电源电压1.5V 情况下,噪声系数NF 为1122d B ,输入反射系数S 11为-15d B ,反向隔离性能S 12为-3219d B,增益S 21为1718dB,三阶交截点II P3为+1217d Bm ,功耗为8mW .参 考 文 献[1] T ool e B,Plett C,CloutierM.RF Circuit I m plica ti onsof Mod 2erat e Inv ersi on Enhanced Li near Regi on in MOSFETs [J ].I EEE T RA NS .C I RC U IT S AN D SY ST E MS —I :REG U LAR PAPE RS,2004,51(2):319-328.[2] D ing Y,Ha ryani R.A +18d Bm IIP3LNA in 0.35u mC MOS[C ].I n:P r oceedings of I EEE ISSCC,2001:161-162.[3] Aparin V,B r own G,Lars on L E .L I NE AR IZ ATI ON OFC MOS LNA ’S V I A OPTI M U M G ATE B I A S -IN G[C ].In:Proceedings of the 2004I nterna ti ona l Sy mposiu m onC ircuits and System s,2004,4:748-751.[4] Ki m TW ,Ki m B,L ee K .Highly Linea r Rece iv e r Front-end Adop ting MOSFET Transconductance L i neariza -ti on by Multi p le Ga ted Tran sist ors[J ].IEEE J.S o lid -St a te C ircuits,2004,39(1):223-229.[5] Aparin V,Lars on L E .Modi fied Deriv a tiv e SuperpositionM eth od for Linearizati on FET Lo w -Noise Amp lifi e rs [J ].IEEE T .M icro wav e T heory and Technique,2005,53(2):571-581.[6] Xin C,Sanchez S E .A L inearization Technique For RFLo w Noise Amp lifier [C ].In:Proceedings of IEEEIS CAS,2004.[7] Tanaka S,Behbahani F,Abidi A A.A Linea riza ti onTechnique For C MOS RF Powe r Amp lifie rs [C ].In:Proceedings of IEEE Sy mposiu m on VLS I Circuits,1997:93-94.[8] Keng L F .High 2frequency Analysis of Linearity I mp r ove 2ment Technique of Com mon 2e m itter Transconductance stag e Using a Lo w 2Frequency 2Trap Net w ork[J ].I EEE J .S OL I D 2ST ATE CIRCUITS,2000,35(8):1249-1252.[9] Keng L F,Robert G .H igh 2frequency Nonlinear ityAnaly 2sis of Co mmon 2e m itte r and Differential 2pair Transcon Ductance Stages [J ].IEEE J.S OL I D -ST A T E C I R 2CU ITS,1998,33(4):548-555.[10]Z hang WC,Chen KS .Nonli nearity ana l ysis of C MOS LNA based on Volterra se ri e s[C ].The 3rd C ross Stra it Tri 2R egi ona l R adio Science and W ire less Technology Conference,2002.[11]L in M,W ang H,L i Y,Chen H.A Novel IP3BoostingT echnique U sing Feedfor wa rd D istorti on Cance lla ti on Me th od f o r 5G Hz C MOS LN A [J ].Ana l og Integrated Circuits and Si gnal P r ocessing,2006.A H i ghly L i n ea r CMO S Low Noise Am pli f i erDENG Gui -p ing 1,WANG Chun -hua2(1.Collage of Infor ma tion Engineering,Xiangtan University,Xiangtan 411105,Chi na;2.School of Co mpute r and Co mm unicati on,Hunan Univ e rsit y,Changsha 410082,Chi na)Abstrac t:A 5.7G Hz C MOS low noise a mp lifier (LNA )i mplemented with TS MC 0.35um standa r d C MOS tech 2nol ogy is p r e sented .The pr oposed LNA intr oduce s the l ow 2frequency 2tra p ne t w ork int o the single 2end common 2source common 2ga te cascade topology .Si m ulated and analyzed by the A D S s oft wa r e,the f oll owing pa r ame ters are y f 5V ,f B ,f 25B ,ff 23B ,B ,II 3+B W K y f ;;y8 湖南工程学院学报 2007年achieved:unde r the suppl v oltag e o 1.the n oise ig ure is 1.22d the input r e lecti on is 1d the reverse trans mitted coe icient is 2.9d the gain is 17.8d the P is 12.7d m and the po wer is 8m .e wor ds:lo w n oise a mpli ier wir e less l ocal net work linea rit。

基于CMOS模拟开关实现平衡混频器1 引言近年来,无线通信技术得到了迅猛地发展。

它对收发信机前端电路提出的新要求是:高线性,低电压,低功耗,高度集成。

混频器作为无线通信系统射频前端的核心部分之一,其性能的好坏将直接影响整个系统的性能。

从频域角度看,混频器是频谱的线性搬移。

实现频谱搬移的基本方法是将两个信号相乘。

混频器利用器件的非线性特性来实现信号载波频率的变化,产生输入频率的和频和差频分量。

文章基于Gilbert 乘法器平衡混频器的工作原理,提出了一个新型混频器的结构,采用COMS 开关实现了一种平衡混频器,根据实测其性能完全满足工程需要且有低成本、高线性度、大动态等优点。

2 单平衡混频器的工作原理常用有源单平衡混频器为Gilbert 单平衡混频器,其实质为一可变互导乘法器,见图1 所示。

它由三部分组成,一是由本振信号VLO(t)激励的差分对管Q2、Q3; 二是输出电流受射频信号VRF(t)控制的晶体管Q1;三是中频负载RL。

如图1 所示。

Q1 是射频小信号线性放大器(也称输入跨导级);差分对Q2、Q3 在本振大信号作用下可看作轮流导通的双向开关;当双端输出时,输出电流i 是两电流i2和i3 的差。

图1 单平衡混频器原理图为保证Q1 工作于放大区,必须加上偏置电路给它设置合适的工作点。

设其直流工作点电流是ICQ1在信号VRF(t)作用下,Q1 的集电极电流为(设Re短路)由以上分析,有源单平衡混频器是通过本振开关电路(Q2、Q3) 对跨导级电路(Q1) 形成的射频电流信号进行开关调制, 实现混频功能。

负载级电路把混频产生的中频电流信号转换成电压信号。

3 CMOS 模拟开关实现平衡混频器吉尔伯特单平衡混频器的基本结构框图如图2 所示,组成单元为放大器、开关和负载。

混频器的最终输出等于输入信号与一个开关函数相乘,此开关函数与本振信号频率相同。

图2 单平衡混频器等效电路综上所述,得到一混频器设计思路一一寻找一个放大器,然后在输出之前,寻找一合适位置,设一开关级,使用平衡结构,再通过选择合适的负载输出信号。