AX88178_Marvell-88E1111_DemoBoard_Schematic_V212

- 格式:pdf

- 大小:111.76 KB

- 文档页数:4

PHY芯片88EE1111 MDIO接口调试-Lufy-189******** 本次调试88EE1111 PHY芯片之主要目的主要对应为了将其默认的GMII接口通过配置成RGMII接口。

因此,可能本文档涉及到的内容并没有涉及到PHY芯片的88EE1111所有内容。

PHY芯片管理接口:88EE1111芯片可通过硬件设置成两种管理接口,一种就是本文所提的MDIO接口。

一种对应的就是Two_Wire_Serial_Interface(TWSI),也就是I2c接口,这不做讨论。

主要硬件选择是通过88EE1111的CONFIG[6:0]中的CONFIG[6]配置的Bit2选择,为1,表示配置为TWSI 接口,否则为MDIO接口。

下面讲述对应CONFIG[6:0]硬件配置。

88EE1111芯片可通过CONFIG[6:0]这些IO硬件配置一些基本模式。

可配置PHY Address、PHY Operate Mode(操作模式)、Auto-Negotiation(自适应模式)。

具体见88EE1111的Hardware Configuration部分。

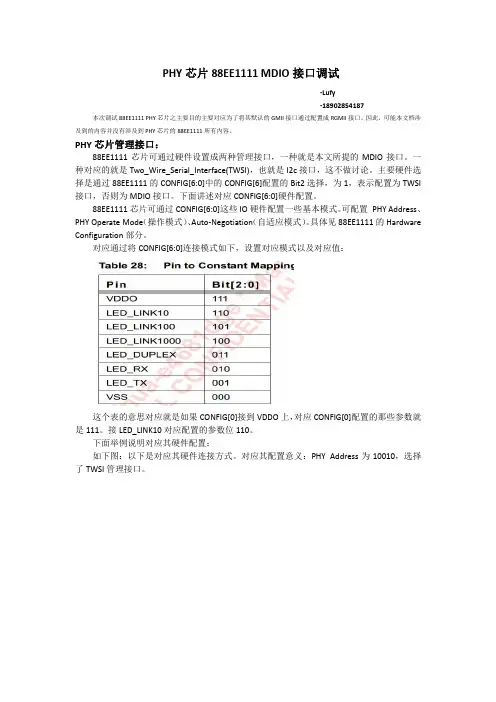

对应通过将CONFIG[6:0]连接模式如下,设置对应模式以及对应值:这个表的意思对应就是如果CONFIG[0]接到VDDO上,对应CONFIG[0]配置的那些参数就是111。

接LED_LINK10对应配置的参数位110。

下面举例说明对应其硬件配置:如下图:以下是对应其硬件连接方式。

对应其配置意义:PHY Address为10010,选择了TWSI管理接口。

下面对应是我们的实际硬件原理图:(对应为Xilinx的SP601开发板)对应图中CONFIG[0]配置为VDDO(111),CONFIG[1]配置为VSS(000),CONFIG[2:5]配置为VDDO(111),CONFIG[6]配置为LED_RX)(010)。

对应其配置PHY ADDRESS为00111,其选择的管理接口为MDIO接口。

![AX88179_Product_Introduction_v020[1]](https://uimg.taocdn.com/32cab7b5b0717fd5360cdc4c.webp)

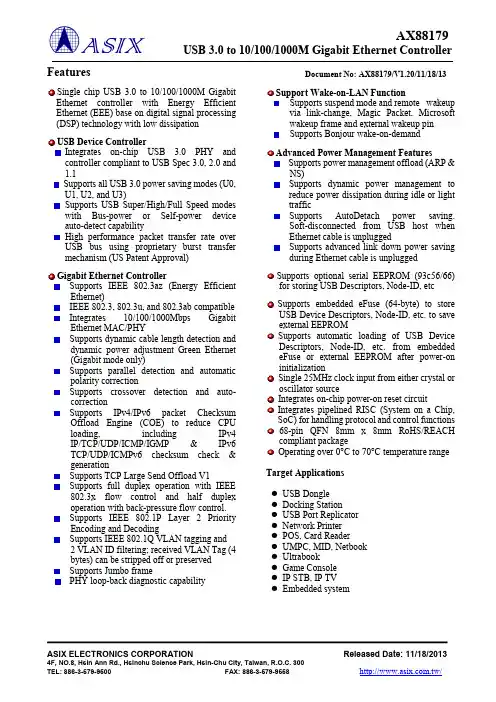

AX88179 Product IntroductionRevision 0.20Jan. 3rd, 2012Revision HistoryTable of Contents1.Introduction (4)2.Block Diagram (5)2-1.Typical System Block Diagram (6)3.Selection Guide (7)4.Ordering Information (8)5.Target Applications (9)6.Related Technical Archives (10)List of FiguresFigure 1.Block Diagram (5)Figure B 3.0 to Gigabit Ethernet Adaptor (6)Figure 3.Selection Guide (7)Figure 4.Ordering Information (8)Figure 5.Target Applications (9)Figure 6.Related Technical Archives (10)1.IntroductionThe AX88179 USB 3.0 to 10/100/1000M Gigabit Ethernet controller is a high performance and highly integrated ASIC which enables low cost, small form factor, and simple plug-and-play Gigabit Ethernet network connection capability for desktops, notebook PC’s, Ultrabook’s, docking stations, game consoles, digital-home appliances, and any embedded system using a standard USB port.The following URL provides detailed online resource of ASIX Electronics USB-to-LANsolutions: (Refer to /products.php?op=ProductList&PLine=71.)This Application Design Note applies specifically to the following AX88179 USB 3.0 toGigabit Ethernet controller.AX88179– USB3.0 to 10/100/1000M Gigabit Ethernet ControllerThis document provides an overview of AX88179 USB3.0 to 10/100/1000M Gigabit Ethernet Controller product.2.Block DiagramThe following is AX88179 block diagram,Figure 1.Block Diagram2-1.Typical System Block DiagramFigure B 3.0 to Gigabit Ethernet Adaptor3.Selection GuideThe following is the selection guide of ASIX Electronics USB to Ethernet family for different requirement applications. Please visit ASIX Electronics USB-to-LAN solutions web pages /products.php?op=ProductList&PLine=71 and contact ASIX's Sales (sales@) for details.Figure 3.Selection Guide4.Ordering InformationThe following are the ordering information of AX88179 silicon and AX88179 demo boards.Please contact ASIX's Sales (sales@) for more details.Figure 4.Ordering Information5.Target ApplicationsThe following are some PC/Internet and consumer electronics target applications for your reference.PC/InternetConsumer ElectronicsFigure 5.Target Applications6.Related Technical ArchivesThe following are AX88179 related technical archives list for your reference. Please contact ASIX's Sales (sales@) for more details.11Copyright (C) 2011-2012 Reserved by ASIX Electronics Corporation4F, No.8, Hsin Ann Rd., Hsinchu Science Park,Hsinchu, Taiwan, R.O.C.TEL: +886-3-5799500 FAX: +886-3-5799558Email: support@Web: 。

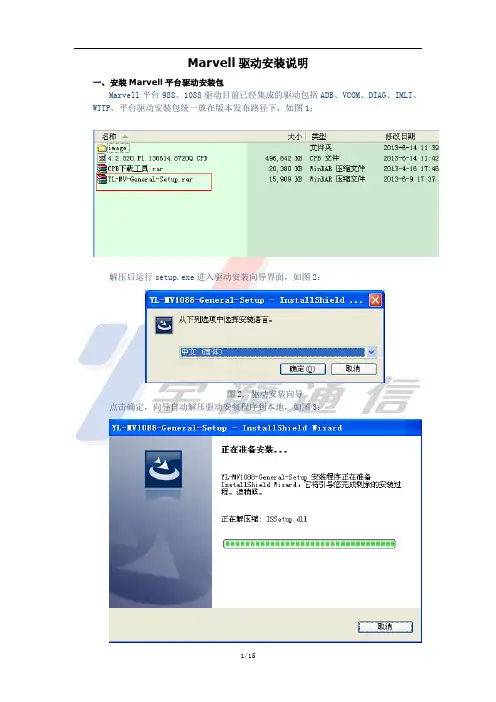

Marvell驱动安装说明一、安装Marvell平台驱动安装包Marvell平台988、1088驱动目前已经集成的驱动包括ADB、VCOM、DIAG、IMLT、WTTP,平台驱动安装包统一放在版本发布路径下,如图1:解压后运行setup.exe进入驱动安装向导界面,如图2:图2. 驱动安装向导点击确定,向导自动解压驱动安装程序到本地,如图3:图3. 自动解压安装程序解压缩完后,一直点击【下一步】,如图4、5所示:图4. 安装向导图5. 安装向导点击【安装】,安装向导将自动完成驱动安装和注册过程,如图6所示:图6. 安装驱动程序点击完成,驱动安装成功,如图7所示:图7. 驱动安装成功二、过签的驱动直接使用经过数字签名的驱动在驱动安装成功后,连接USB手机驱动就可以直接使用了,如图8所示:图8. 经过签名的驱动三、烧写驱动安装由于Marvell驱动WTTP没有经过数字签名,所以经过上述步骤后,烧写驱动只是在windows下生成cache没有进行注册,所以第一次使用时要进过安装才能使用,操作过程很简单,关机状态下插入USB,会弹出驱动安装提示,如图9和图10所示:图1. 驱动安装包在发布路径下图9. 提示发现烧写端口图10. 提示安装驱动弹出提示后,只需要点击【下一步】,向导会找到之前生成的驱动cache实现自动安装,如图11和图12所示:图11.向导自动安装驱动图12. 驱动安装完成驱动安装成功后,在设备管理器下看到烧写驱动端口,如图13所示:图13. 烧写驱动端口特别需要提示的是,插入USB后,如果没有开启烧写软件,或者没有点击下载,3秒端口后将消失,进入到关机充电。

四、D iag口驱动安装由于Marvell驱动WTTP没有经过数字签名,所以经过上述步骤后,烧写驱动只是在windows下生成cache没有进行注册,所以第一次使用时要进过安装才能使用,操作过程很简单,手机切换到nogui或者acat模式后插入USB,系统会提示安装驱动如图14所示,驱动安装操作过程和烧写驱动WTTP类似图14. 提示安装Diag驱动弹出提示后,只需要点击【下一步】,向导会找到之前生成的驱动cache实现自动安装,如图15和图16所示:图15. 向导自动安装驱动图16. Diag驱动安装成功驱动成功安装后,在设备管理器下可以看到Diag端口设备,如图17所示:图17. Diag端口设备五、常见问题1.第一次使用或换端口烧写时会提示安装驱动一般情况下执行完驱动自动安装包setup.exe后,在windows\inf\下会为每个驱动生成一对oemxx.inf和oemxx.pnf,比如oem19.inf和oem19.pnf文件。

在连续两个平台的uboot和Linux系统移植过程中,在千兆网口调试这块都遇到了很大的麻烦。

由于寄存器数量庞大,千兆网口MAC和PHY内部结构复杂,MAC和PHY接口种类多,千兆以太网驱动的调试成了系统移植过程中最让人烦心的一个环节。

就像火箭队,每次都让球迷无比揪心,不是输的窝囊,就是伤兵满营,现在新赛季又两连败了,打的比勇士还勇士,后场两个比我还瘦的家伙,怎么防守。

算了,不扯这么多了,今天要说的是网口MAC+PHY的一些原理和代码分析。

(以Freescale的ETSEC和Marvell的88E1111为例。

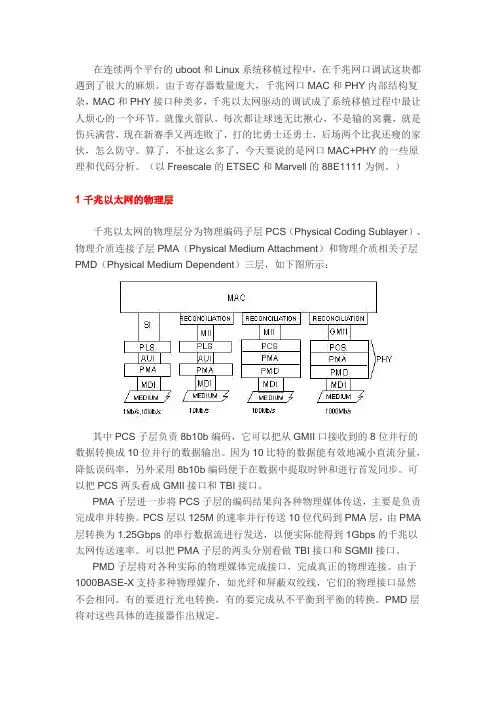

)1 千兆以太网的物理层千兆以太网的物理层分为物理编码子层PCS(Physical Coding Sublayer)、物理介质连接子层PMA(Physical Medium Attachment)和物理介质相关子层PMD(Physical Medium Dependent)三层,如下图所示:其中PCS子层负责8b10b编码,它可以把从GMII口接收到的8位并行的数据转换成10位并行的数据输出。

因为10比特的数据能有效地减小直流分量,降低误码率,另外采用8b10b编码便于在数据中提取时钟和进行首发同步。

可以把PCS两头看成GMII接口和TBI接口。

PMA子层进一步将PCS子层的编码结果向各种物理媒体传送,主要是负责完成串并转换。

PCS层以125M的速率并行传送10位代码到PMA层,由PMA 层转换为1.25Gbps的串行数据流进行发送,以便实际能得到1Gbps的千兆以太网传送速率。

可以把PMA子层的两头分别看做TBI接口和SGMII接口。

PMD子层将对各种实际的物理媒体完成接口,完成真正的物理连接。

由于1000BASE-X支持多种物理媒介,如光纤和屏蔽双绞线,它们的物理接口显然不会相同。

有的要进行光电转换,有的要完成从不平衡到平衡的转换。

PMD层将对这些具体的连接器作出规定。

2 Freescale 的ETSEC与PHY之间的接口Freescale的MPC8314和P2020都自带了三速以太网控制器ETSEC,可以提供10M,100M,1000M三种速率的接口。

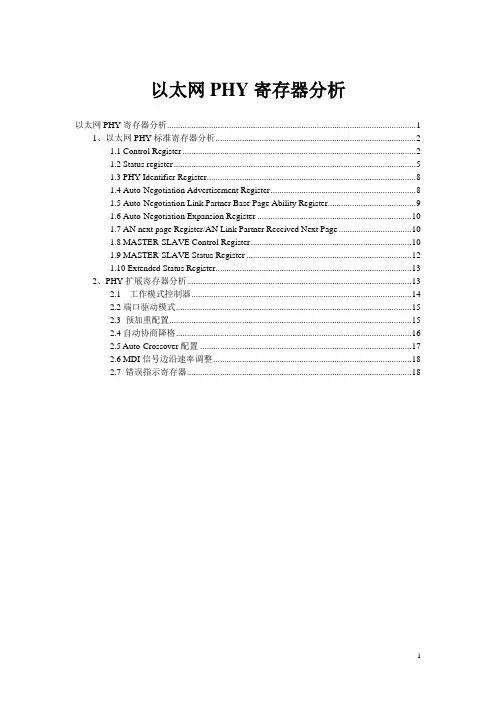

以太网PHY寄存器分析以太网PHY寄存器分析 (1)1、以太网PHY标准寄存器分析 (2)1.1 Control Register (2)1.2 Status register (5)1.3 PHY Identifier Register (8)1.4 Auto-Negotiation Advertisement Register (8)1.5 Auto-Negotiation Link Partner Base Page Ability Register (9)1.6 Auto-Negotiation Expansion Register (10)1.7 AN next page Register/AN Link Partner Received Next Page (10)1.8 MASTER-SLAVE Control Register (10)1.9 MASTER-SLAVE Status Register (12)1.10 Extended Status Register (13)2、PHY扩展寄存器分析 (13)2.1 工作模式控制器 (14)2.2端口驱动模式 (15)2.3 预加重配置 (15)2.4自动协商降格 (16)2.5 Auto-Crossover配置 (17)2.6 MDI信号边沿速率调整 (18)2.7 错误指示寄存器 (18)1、以太网PHY标准寄存器分析PHY是IEEE802.3中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC或CPU)通过SMI(Serial Manage Interface)对PHY 的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。

PHY寄存器的地址空间为5位,从0到31最多可以定义32个寄存器(随着芯片功能不断增加,很多PHY芯片采用分页技术来扩展地址空间以定义更多的寄存器,在此不作讨论),IEEE802.3定义了地址为0-15这16个寄存器的功能,地址16-31的寄存器留给芯片制造商自由定义,如表1所示。

为了让大家能更深层次的了解8813,特在此开帖介绍下8813的系统详细结构。

(由于本人能力有限只能提供一部分系统文件解读,没提及的欢迎各位回帖补充或发站内信给我我会尽快添加)时间有限,只能一步一步来,就弄一点更新一点吧,还请各位有兴趣的机油经常关注!我们先着重介绍systemsystemapp【系统程序目录】delapp 【内置应用】bin 【Linux系统自带组件】lib 【系统底层库】etc 【系统配置文件】fonts 【字体文件】media 【系统资源】usr 【用户文件夹】framework 【系统平台框架】wifi 【wifi配置文件】cdrom 【虚拟光驱】build.prop【系统配置文件】system/app目录详解ApkBatchInstall.apk Apk批量安装器不可删ApplicationsProvider.apk 搜索应用程序提供商不可删AutoRegSms.apk自动短信注册可删BackupRestoreConfirmation.apk 备份还原确认不可删Bluetooth.apk 蓝牙不可删Browser.apk 系统自带浏览器可删Calculator.apk 系统自带计算器可删Calendar.apk 系统自带日历可删CalendarProvider.apk 自带日历储存器可删CertInstaller.apk 证书安装程序不可删Contacts.apk 系统自带联系人不可删ContactsExt.apk 联系人相关组件不可删ContactsProvider.apk 系统自带联系人存储不可删CWService.apk 网络联网服务不可删DefaultContainerService.apk 软件包访问帮助不可删DownloadProvider.apk 下载管理器不可删DownloadProviderUi.apk 下载内容不可删Email.apk 系统自带电子邮件可删EPush.apk 天翼推送可删Exchange2.apk 推送和发送电子邮件服务可删FaceLock.apk 人脸识别可删Galaxy4.apk 黑洞动态壁纸可删Gallery2.apk 图库和相机可替换GoogleServicesFramework.apk 谷歌服务框架可删---建议保留HandWritingSimpPack.apk 手写输入可删HoloSpiralWallpaper.apk 光环螺旋动态壁纸可删HTMLViewer.apk HTML查看器不可删HwAllBackup.apk 华为全备份可删HwBluetoothImport.apk 蓝牙导入通讯录不可删HwDeskClock.apk 时钟闹钟不可删HwDLNA.apk DLNA服务可删HwFileManager.apk 华为文件管理器可删HwFlashlight.apk 华为手电筒可删HwFMRadio.apk 华为收音机可删HwGPMS.apk 认证服务不可删HwIME.apk 华为输入法可删HwLauncher6.apk EMUI桌面可删---需要先安装第三方桌面HwLockScreen.apk 华为锁屏可删HwMediaCenter.apk 华为音乐播放器可删HwMeWidget.apk EMUI桌面插件可删HwNotepad.apk 记事本可删HwNumLocation.apk 来电归属地可删HwOUC.apk 系统在线更新不可删HwProfileSwitcher.apk 华为情景模式不可删HwPushService.apk 推送服务可删HwSoundRecorder.apk 录音机可删HwStartupGuide.apk EMUI使用向导可删HwThemeManager.apk 华为主题可删HwToolBox.apk 下拉快捷控制栏不可删HwWeatherClock.apk 华为天气时钟可删HwWiFiHotspot.apk Wi-fi热点不可删KeyChain.apk 密钥链不可删LiveWallpapers.apk 动态壁纸不可删LiveWallpapersPicker.apk 动态壁纸拾取不可删MagicSmokeWallpapers.apk 魔幻烟雾动态壁纸可删MediaProvider.apk 媒体储存不可删MMITest_II.apk 工程模式不可删MMITest_record.apk 工程模式测试不可删Mms.apk 短信不可删MyCalendar.apk 我的日历窗口小部件可删MyEmail.apk 我的邮件可删NoiseField.apk 气泡动态壁纸可删PackageInstaller.apk Apk安装器不可删PhaseBeam.apk 动态壁纸可删Phone.apk 拨号盘不可删PicoTts.apk 微型TTS 不可删PinyinPack.apk 拼音补丁包可删ProjectMenuAct.apk 工程模式列表不可删Protips.apk 使用提示不可删Settings.apk 系统设置不可删SettingsProvider.apk 设置储存不可删SharedStorageBackup.apk 共享存储备份不可删SmartcardService.apk 智能卡服务可删Stk.apk UIM卡管理程序可删StkLauncher.apk uim卡应用可删SystemUI.apk 系统界面不可删TelecomWallpaper.apk 天翼壁纸库可删TelephonyProvider.apk 通话信息存储服务不可删UserDictionaryprovider.apk 通讯支持程序不可删VpnDialogs.apk VPN局域网服务可删WAPPushManager.apk WAP推送服务可删web.apk天翼自带浏览器可删system/ bin目录解读app_process 系统进程dalvikvm 虚拟机宿主dbus-daemon 系统BUS总线监控debuggerd 调试器dexopt DEX选项dhcpcd DHCP服务器dumpstate 状态抓取器dumpsys 系统抓取器logcat 日志打印mount 存储挂载器netcfg 网络设置ping Ping程序pm 包管理器rild RIL组件servicemanager 服务管理器surfaceflinger 触摸感应驱动svc 服务system/cdrom目录解读autorun.iso 虚拟光驱镜像删除后连接电脑不会加载虚拟光驱有兴趣的可以放个其它虚拟光驱镜像进去做其它用途system /delapp目录详解【此为官方169固件内置程序,后续更新后可能会有版本差异请去除版本号查看即可】20121112163921937_G510CQQ_2012_3.0_rp_release.apk QQ2012 Alipay_for_huawei_0920_1600.apk 支付宝Alipay_msp_huawei_1000003.apk 支付宝快捷支付服务Android_UCBrowser_8.5.1.179_12092410_33571_huawei_G510.apk UC浏览器AnZhi_Huawei_C8951D_VER_3_4.apk 安智市场ApplicationForCustomize.apk 桌面上的四个书签图标BaiduMap_andr_4.0.1.202_10000a_20121213.apk 百度地图BaiduSearch_Android_1-0-9-236_942c_tianyi.apk 百度搜索天翼版Besttone_v3.1.0.0_20121121_4.0_bst002.apk 号码百事通ChinaTelecomCustomize.apk 客户服务ChinaTelecomFancy_v1.1.0build4216-OEM1.apk 天翼云桌面CtClient_C8730_V2.0.5_7107_20121107.apk 电信营业厅DianPing_Huawei_V4.7.1_Tianyi_20121115.apk 点评ECP_C8813_2_1_9_s9306_20121129.apk 翼聊eGame_Huawei_V5.2.1_01345337_20121109.apk 爱游戏elocal_Huawei_V1.2_2000_20121129.apk 翼周边eStock-HBJT_1.2.0_bywang_20120929AM1000.apk 股票财经eStore_huawei_G510C_V3.6.0.1_20121024.apk 天翼空间Esurfing_Huawei_V3.1.0.2_00000020_20121227.apk 天翼视讯esurfing_WiFi_1.1.1.13027beta_huawei.apk 天翼宽带 wifi hiCDMAShoppingCommon_4.0_V1.0.7.apk 天翼手机HiSpace.apk 智慧云HuaweiSecurityGuard.apk 华为安全管家iCartoon_Huawei_C8951D_v1.1.16_20121207.apk 爱动漫iMusic_V4.301.158.1319_Huawei_C8951D_T_QAS.apk 爱音乐iReader_V2000_hwC8813_1212.apk iReader电子书阅读器JJLord.20207.40011.apk JJ斗地主kwplayer_ar_4.2.6.2_huawei_C8813.apk 酷我音乐mail189_C8813_V3.2.1_102_20121130.apk 189邮箱PeopleClients_C8813D_V1.4.1_88_20121109.apk 人民新闻pim2_2.0_0.2.0_0106.apk 号薄助手pre_enavi2.2.3.120926.apk 天翼导航QGHBNPZZCVH2.7.01_PRE.apk 号百彩票Quickoffice_HUAWEI_5.7.154_V.apk 办公软件SohuNewsClient_v3.1.6_huawei_7025.apk 搜狐新闻SohuTV_2.3_28_201211101341.apk 搜狐TVTaobao_C8813_V3.2.1_700829_20130109.apk 淘宝TYYD_Android_4_1_480_854_HW_C8813_JAVA_2_6_1_20121105.apk 天翼阅读v1.5.5.3_SearchNum_COMMON_20120914_p.apk 查号v1.6.2.9_HighRail_android4.0_20120919_P.apk 114火车票v2.5.1.3_TravelSky_android4.0_20120920_P.apk 号百商旅v3.5.1.3_Restaurant_Android4.0_20120828_0_p_P.apk 订餐system/etc目录解读此目录中存储的是系统配置文件apns-conf.xml APN接入点配置文件AudioFilter.csv 音频过滤器配置文件dbus.conf 总线监视配置文件gps.conf GPS设置文件hosts 网络DNS缓存NOTICE.html.gz 提示网页\system\etc\wifi\wpa_supplicant.conf WPA验证组件system/fonts目录解读此目录中存储的为字体文件system/framework目录解读此目录中存储的是系统框架JAVA虚拟机等相关文件com.google.android.maps.jar 电子地图库core.jar 核心库,启动桌面时首先加载这个framework-res.apk 系统界面布局input.jar 输入库pm.jar 包管理库svc.jar 系统服务system/lib目录解读此目录中存放的主要是系统底层库,如平台运行时库。

千兆以太网芯片88E1111 RGMII模式的驱动88E1111可工作在10Mb/s,100Mb/s,1000Mb/s下,由于DE2-115开发板在设计的时候只采用了4位数据端口,因此只能采用MII模式(100Mb/s),或者RGMII模式(1000Mb/s),看了官方的DATASHEET后,几乎得到什么,于是就想到了一个办法,就是将官方所给的关于RGMII的例程下到开发板上,然后将88E1111的配置寄存器里面的数据用NIOS II读出来,这样就获得了正确的配置数据,然后就将配置数据用NIOS II 配置给芯片,然后就遇到了很奇怪的事情:当我把配置的那几行代码都注释掉以后居然88E1111还可以继续正常运行,后来发现,只要给芯片的硬复位引脚Reset_n一个较长的复位即可,大概10~20ms就可以了。

具体如何将芯片通过CONFIG引脚配置成RGMII 模式,可以参考DE2-115的原理图。

下面就谈谈如何利用时钟的上升和下降沿收发数据。

以下两个图是连接图和时序图。

先谈输出端Tx:Tx端有三个信号,Txd_RGM,Tx_ctrl,Tx_clk,其中Tx_clk是由FPGA提供的125MHz 的时钟,Tx_RGM是发送的数据,Tx_ctrl在Tx_clk时钟上升沿发送的是Tx_en,在下降沿发送的是Tx_en和Tx_er的异或值。

Rx端也有三个信号:Rxd_RGM,Rx_ctrl,Rx_clk,其中Rx_clk是由88E1111提供的125MHz的时钟,Rx_RGM表示接收到的数据,Rx_ctrl在Rx_clk的上升沿收到的是Rx_en,在下降沿收到的是Rx_en和Rx_er的异或值。

由于一个always模块中不能同时使用时钟的上升和下降沿,可以调用DDIO模块,当然,也可以不用,下图就是不采用DDIO的一个示意图,这个是用来设计DDR SDRAM的,可以借鉴module rgmii_io(input Tx_clk,input Rx_clk,output Tx_clk_RGM,input[7:0] Txd,output [3:0] Txd_RGM,input Tx_en,input Tx_er,output Tx_ctrl,input[3:0] Rxd_RGM,output reg[7:0] Rxd,input Rx_ctrl,output reg Rx_dv,output reg Rx_er);assign Tx_clk_RGM = ~Tx_clk;//******************************************************************************//Tx control //******************************************************************************wire Tx_err;reg[3:0] Txd_low,Txd_high;reg Tx_en_d1,Tx_err_d1;assign Tx_err=Tx_en^Tx_er;assign Txd_RGM = Tx_clk ? Txd_low : Txd_high;assign Tx_ctrl = Tx_clk ? Tx_en_d1 : Tx_err_d1;always@(posedge Tx_clk)beginTxd_low <= Txd[3:0];Txd_high <= Txd[7:4];Tx_en_d1 <= Tx_en;Tx_err_d1 <= Tx_err;end//******************************************************************************//Rx control //******************************************************************************wire Rx_er_d1;reg[3:0] Rxd_low,Rxd_high;reg Rx_dv_d1,Rx_err_d1,Rx_dv_d2,Rx_er_d2;reg[7:0] Rxd_d1;assign Rx_er_d1=Rx_dv_d1^Rx_err_d1;wire Rx_clk_n;assign Rx_clk_n=~Rx_clk;always@(posedge Rx_clk_n)beginRxd_low<=Rxd_RGM;Rx_dv_d1<=Rx_ctrl;endalways@(posedge Rx_clk)beginRxd_high<=Rxd_RGM;Rx_err_d1<=Rx_ctrl;endalways@(posedge Rx_clk_n)beginRxd_d1<={Rxd_high,Rxd_low};Rx_dv_d2<=Rx_dv_d1;Rx_er_d2<=Rx_er_d1;endalways@(posedge Rx_clk)beginRxd<=Rxd_d1;Rx_dv<=Rx_dv_d2;Rx_er<=Rx_er_d2;end。

RTL8811RTL8812RT...随着WiFi的广泛集成应用,在一些高流量高带宽的领域,有11ac 标准的需求,支持11ac,其实就是符合无线标准:IEEE 802.11ac(一般是向下兼容11a/n),这个标准的最大特点就是单通道速率可高达433.3Mbps,信道带宽可以支持20/40/80/160MHz;RTL8811系列是USB接口单通道双频方案(MT7610功能类似),一些是主要共性:通信接口:USB2.0;无线标准:IEEE 802.11a/b/g/n/ac;频带:ISM 2.4G&ISM 5G;带宽:HT20/HT40/HT80;传输速率:433.3Mbps/1T1R;主要版本有RTL8811AU、RTL8811BU和RTL8811CU;RTL8811AU主要有以下型号:RL-UM02SP-8811 尺寸:27*17.8mm;可兼容替代:F11AUUM23-W1、F11AUUM23-W2、BL-R8811AF1;RL-UM02R-8811 尺寸:28.1*14.2mm;RL-UD02M-8811AU 尺寸:29.9*13.4mm;RTL8811BU主要有以下型号:RL-UM02SP-8811BU 尺寸:27*17.8mm;还有带I-pex座的版本型号是:RL-UM02SPC-8811BU;RTL8821系列主要是双通,速率带宽更强!其中USB接口的有RTL8821AU和RTL8821CU,SDIO接口的有RTL8821CS;一些是主要共性:无线标准:IEEE 802.11a/b/g/n/ac;频带:ISM 2.4G&ISM 5G;带宽:HT20/HT40/HT80;传输速率:866.7Mbps/2T2R;RTL8821AU方案模块型号主要有(通信接口USB):RL-UM02WBD-8821 尺寸:27*13mm;RL-UM02N-8821 尺寸:19.0*17.0mm;可兼容替代:F21AUUM13-W1;RTL8821CU方案模块型号主要有(通信接口USB):RL-UM02N-8821CU尺寸:13.0*12.2mm;可兼容替代:6221E-UUC、BL-M8821CU1;这是硬件兼容性最好的封装;RTL8821CS方案模块型号主要有(通信接口SDIO):RL-UM02N-8821CS 尺寸:19.0*17.0mm;RL-SM02D-8821CS 尺寸:12*12mm;可兼容替代:6221A-SRC、BL-M8821CS1;硬件兼容性强,可以替代AP6255和SD30;RTL8812系列是USB接口单通道蓝牙WiFi二合一双频方案(MT7612功能类似),一些是主要共性:通信接口:USB2.0;无线标准:IEEE 802.11a/b/g/n/ac;频带:ISM 2.4G&ISM 5G +BT;带宽:HT20/HT40/HT80;传输速率:433.3Mbps/1T1R;主要版本有RTL8812AU和RTL8812BU;RTL8812AU主要有以下型号:RL-UM02F-8812 尺寸:46.4*40mm;这主要针对广告机和高清电视领域设计;RL-UM02SPC-8812 尺寸:27.2*17.5mm;可兼容替代:BL-M8812AU1;不带板载Ipex座子型号是:RL-UM02SP-8812;RTL8812BU主要有以下型号:RL-UM02SPC-8812BU 尺寸:27.2*17.5mm;不带板载Ipex座子型号是:RL-UM02SP-8812BU;RTL8822系列是双通道蓝牙WiFi二合一双频方案(MT7662和MT7668功能类似),一些是主要共性:无线标准:IEEE 802.11a/b/g/n/ac;频带:ISM 2.4G&ISM 5G +BT;带宽:HT20/HT40/HT80;传输速率:866.7Mbps/2T2R;RTL8822BU方案模块型号主要有(通信接口USB)RL-UM02SPC-8822BU 尺寸:27.2*17.5mm;可兼容替代:6222D-UUB、AP6269LV、AP62X8、UB38、8279D-UU、WL-UM01WBD-7662、WL-UM01SPC-7662T、WL-UM01SP-7662T;不带板载Ipex座子型号是:RL-UM02SP-8822BU;RTL8822BU方案模块型号主要有(通信接口SDIO)RL-SM02F-8822BS 尺寸:15*13mm;可兼容替代:RL-SM01F-7668S、6222B-SRB、AP6356S、AP6359S、AP6398S、AP6398SR3 ;RTL8822BU方案模块型号主要有(通信接口PCIe)RL-EM02F-8822BEH 尺寸:15*13mm;可兼容替代:6222B-PRB针对这种高端领域,产品升级不会很频繁,所以尺寸基本以15*13mm、12*12mm、27*18mm三种为主,不同方案可以硬件兼容,只需要调试对应的软件,蓝牙方便基本是支持的BT版本不一样。

Win8.1出现蓝屏(wificlass.sys )后的临时解决方案我的美版's ɜːfɪs pr əʊ θriː (这是音标,俗称“苏菲婆3代”,但不能写明,否则百度文库说我在为's ɜːfɪs 做宣传,这文章就无法公开,只有我自己能看见),刚买来就有任务栏闪烁的问题,后来又频繁蓝屏,错误内容为IRQL_NOT_LESS_OR_EQUAL 或SYSTEM_THREAD_EXCEPTION_NOT_HANDLED ,没办法,到网上找了64bit 的PE ,用UltraISO 制作了启动U 盘,重装了64bit 的中文企业版。

这样一来,不再出现以上两种错误的蓝屏,任务栏也不再闪烁。

但是音量键无法调节音量,只能在开机时按住进入高级启动或进UEFI 固件设置(说明不是音量键硬件故障),电源键只能开关机,不能睡眠(也不是硬件故障),Home 键无效,仅有震感(估计又不是硬件故障)。

这些键失效都应该是缺少驱动(我格式化硬盘之前忘记备份驱动了,失误失误),用驱动精灵、驱动人生、鲁大师都解决不了。

更麻烦的是,一个软件说某个设备的驱动是最新的,另一个软件说这个设备的驱动可以更新;一个说所有设备的驱动都已正常安装,另一个说有几个未知设备无法安装驱动。

平静的日子没过多久,又起波澜,一大波蓝屏再度袭来,这次内容为SYSTEM_THREAD_EXCEPTION_NOT_HANDLED(wificlass.sys),之前那个……NOT_HANDLED 后面没有wificlass.sys. 在无数次wificlass.sys 蓝屏之中还出现过一次CRITICAL_PROCESS_DIED我的蓝屏提示本是中文,由于我没拍下来,就用的别人的图片。

国外的一些网站也提到wificlass.sys 这个问题,参见/index.php/2014/08/01/blue-screen-crash-on-surface-pro-3-with-wificlass-sys/但没给出解决方案。

KH0818 八防区全无线防盗报警器一、工作原理KH0818(Y/B/BY)型无线报警器,是由报警主机、红外探测器和无线遥控器组成。

当红外探测器一旦探测到非法入侵,立即把报警入侵信号无线密码传输到报警主机,报警主机接收到信号后,立即启动高分贝警笛现场报警。

同时主机面板上相应防区的LED指示灯启亮,明确显示非法入侵方位。

报警主机在声、光报警的同时,还可立即启动警灯系统,照亮入侵现场。

KH0818(Y/B/BY)型无线报警器,采用国际先进的微电脑芯片控制系统,探测距离远,误报率低并且多套报警器相邻安装不会相互窜扰,停电时,可由4节5号电池供电,用户使用起来更加方便、经济。

二、适用范围住宅、楼房、庭院、工厂、车库、办公室、财务室、商店等场所。

三、主要功能八个无线防区,变音识别报警入侵方位;内置警号高分贝现场报警,音量可调;红外探测器和主机采用密码无线传输,安全性更强;红外探测器和主机无线传输工作距离>600米;配有警灯(摄像机控制)输出接口;主机交直流两用,停电照常工作,主要可独立布防,也可配置遥控器布防/撤防;有紧急防抢按钮。

四、主要技术指标1.主机工作电流:交流220V 直流6V静态电流:<3.5mA 报警声级:>100dB(可调)防区显示:八路(1、3、5、7路防区为消防车声,2、4、6、8路防区为警车声。

)2.红外探测器:探测范围:>8—15米,角度>110度工作电压:普通五号电池为直流6V,层叠电池为直流9V静态电流:<60uA 发射频率315MHz无线发射距离:>600米(开阔地)3.无线遥控器:无线发射距离:<100米(开阔地)工作电压:直流12V 发射频率:315MHz五.使用方法先把探头装上电池,(装电池时,把电池扣扣在电池上即可),挂在约2米高的地方,使其向下方倾斜,以获得较高的灵敏度。

打开探头开关,约一分钟左右,有人进入探头的监控区(以横切探头走动时灵敏度较高),主要即刻报警,报警时间约为一分钟,而后重新处于警戒状态,有人再进入监控区,再次报警。

Marvell.Moving Forward FasterDoc. No. MV-S105540-00, Rev. --March 4, 2009Document Classification: Proprietary Information88E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDocument ConventionsNote: Provides related information or information of special importance.Caution: Indicates potential damage to hardware or software, or loss of data.Warning: Indicates a risk of personal injury.Document StatusAdvance Information This document contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.Preliminary InformationThis document contains preliminary data, and a revision of this document will be published at a later date. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.Final Information This document contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.Doc Status: AdvanceTechnical Publications: 1.00For more information, visit our website at: DisclaimerNo part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.Copyright © 2009. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective owners.88E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00 Rev. -- Copyright © 2009 Marvell Page 2Document Classification: Proprietary InformationMarch 4, 2009, Advance88E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverCopyright © 2009 MarvellDoc. No. MV-S105540-00, Rev. --March 4, 2009, AdvanceDocument Classification: Proprietary InformationPage 3O VERVIEWThe Alaska ® Ultra 88E1111 Gigabit Ethernet Trans-ceiver is a physical layer device for Ethernet1000BASE-T, 100BASE-TX, and 10BASE-T applica-tions. It is manufactured using standard digital CMOS process and contains all the active circuitry required to implement the physical layer functions to transmit and receive data on standard CAT 5 unshielded twisted pair.The 88E1111 device incorporates the Marvell Virtual Cable Tester ® (VCT™) feature, which uses TimeDomain Reflectometry (TDR) technology for the remote identification of potential cable malfunctions, thus reducing equipment returns and service calls. Using VCT, the Alaska 88E1111 device detects and reports potential cabling issues such as pair swaps, pair polar-ity and excessive pair skew. The device will also detect cable opens, shorts or any impedance mismatch in the cable and report accurately within one meter the dis-tance to the fault.The 88E1111 device supports the Gigabit Media Inde-pendent Interface (GMII), Reduced GMII (RGMII), Serial Gigabit Media Independent Interface (SGMII), the Ten-Bit Interface (TBI), and Reduced TBI (RTBI) for direct connection to a MAC/Switch port.The 88E1111 device incorporates an optional 1.25 GHz SERDES (Serializer/Deserializer). The serial interface may be connected directly to a fiber-optic transceiver for 1000BASE-T/1000BASE-X media conversion appli-cations. Additionally, the 88E1111 device may be used to implement 1000BASE-T Gigabit Interface Converter (GBIC) or Small Form Factor Pluggable (SFP) modules.The 88E1111 device uses advanced mixed-signal pro-cessing to perform equalization, echo and crosstalk cancellation, data recovery, and error correction at a gigabit per second data rate. The device achievesrobust performance in noisy environments with very low power dissipation.The 88E1111 device is offered in three different pack-age options including a 117-Pin TFBGA, a 96-pin BCC featuring a body size of only 9 x 9 mm, and a 128 PQFP package.F EATURES•10/100/1000BASE-T IEEE 802.3 compliant •Supports GMII, TBI, reduced pin count GMII(RGMII), reduced pin count TBI (RTBI), and serial GMII (SGMII) interfaces•Integrated 1.25 GHz SERDES for 1000BASE-X fiber applications •Four RGMII timing modes•Energy Detect and Energy Detect+ low power modes•Three loopback modes for diagnostics•“Downshift” mode for two-pair cable installations •Fully integrated digital adaptive equalizers, echo cancellers, and crosstalk cancellers •Advanced digital baseline wander correction •Automatic MDI/MDIX crossover at all speeds of operation•Automatic polarity correction•IEEE 802.3u compliant Auto-Negotiation•Software programmable LED modes including LED testing•Automatic detection of fiber or copper operation •Supports IEEE 1149.1 JTAG•Two-Wire Serial Interface (TWSI) and MDC/MDIO •CRC checker, packet counter •Packet generation •Virtual Cable Tester (VCT)•Auto-Calibration for MAC Interface outputs •Requires only two supplies: 2.5V and 1.0V (with 1.2V option for the 1.0V supply)•I/Os are 3.3V tolerant•Low power dissipation Pave = 0.75W •117-Pin TFBGA, 96-Pin BCC, and 128 PQFP package options•117-Pin TFBGA and 96-Pin BCC packages avail-able in Commercial or Industrial grade •RoHS 6/6 compliant packages available88E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. -- Copyright © 2009 Marvell Page 4Document Classification: Proprietary InformationMarch 4, 2009, Advance88E1111 Device used in Copper Application88E1111 Device used in Fiber Application88E1111 RGMII/GMII MAC to SGMII MAC ConversionTable of Contents1.1117-Pin TFBGA Package (6)1.2 96-Pin BCC Package (7)1.3128-Pin PQFP Package (8)1.4Pin Description (9)1.4.1Pin Type Definitions (9)1.5I/O State at Various Test or Reset Modes (33)1.6117-Pin TFBGA Pin Assignment List - Alphabetical by Signal Name (34)1.796-Pin BCC Pin Assignment List - Alphabetical by Signal Name (36)1.8128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name (38)2.1117-pin TFBGA Package (40)2.296-pin BCC Package - Top View (42)2.396-Pin BCC Package - Bottom View (43)2.4128-Pin PQFP Package (44)3.1Ordering Part Numbers and Package Markings (45)3.1.1RoHS 5/6 Compliant Marking Examples (46)3.1.2RoHS 6/6 Compliant Marking Examples (49)Copyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --March 4, 2009, Advance Document Classification: Proprietary Information Page 588E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. -- Copyright © 2009 Marvell Page 6Document Classification: Proprietary InformationMarch 4, 2009, AdvanceSection 1. Signal DescriptionThe 88E1111 device is a 10/100/1000BASE-T/1000BASE-X Gigabit Ethernet transceiver.1.1117-Pin TFBGA PackageFigure 1:88E1111 Device 117-Pin TFBGA Package (Top View)Figure 2:Pin A1 Location123456789A RXD5RXD6S_IN+S_IN-S_CLK+S_CLK-S_OUT+S_OUT-LED_LINK1000AB RX_DV RXD0RXD3VDDO CRS COL AVDD LED_LINK100VDDOHBC RX_CLK VDDO RXD2RXD4RXD7DVDD DVDD LED_LINK10LED_RX CD TX_CLK RX_ER RXD1VSS VSS VSS DVDD CONFIG[0]LED_TX DE TX_EN GTX_CLK DVDD VSS VSS VSS DVDD LED_DUPLEX CONFIG[1]EF TXD0TX_ER DVDD VSS VSS VSS VDDOH CONFIG[2]CONFIG[4]FG NC TXD1TXD2VSS VSS VSS CONFIG[3]CONFIG[6]CONFIG[5]GH TXD4TXD3TXD5VSS VSS VSS VSSC SEL_FREQ XTAL1HJ TXD6TXD7DVDD VSS VSS VSS DVDD VDDOHXTAL2JK VDDO 125CLK RESETn VSS VSS VSS NC TDO VDDOX KL INTn VDDOX MDC COMA VSS VSS TDI TMS TCK LM MDIO RSET AVDD AVDD HSDAC+HSDAC-AVDD AVDD TRSTn MN MDI[0]+MDI[0]-MDI[1]+MDI[1]-AVDD MDI[2]+MDI[2]-MDI[3]+MDI[3]-N12345678988E1111-BABSignal Description96-Pin BCC Package1.2 96-Pin BCC PackageFigure 3:88E1111 Device 96-Pin BCC Package (Top View)88E1111 - CAACopyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --March 4, 2009, Advance Document Classification: Proprietary Information Page 788E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. --Copyright © 2009 Marvell Page 8Document Classification: Proprietary InformationMarch 4, 2009, Advance1.3128-Pin PQFP PackageFigure 4:88E1111 Device 128-Pin PQFP Package (Top View)78910111213141516171819202122232425262728293031323388E1111 - RCJTop ViewR X _C L K R X _E R V S S T X _C L K V D D O D V D D T X _E R G T X _C L K V S S T X _E N D V D D T X D 0T X D 1T X D 2V S S V S S D V D D T X D 3T X D 4T X D 5D V D D T X D 6T X D 7V D D O 125C L K I N T n M D I OSignal DescriptionPin Description1.4Pin Description1.4.1Pin Type DefinitionsPin Type DefinitionH Input with hysteresisI/O Input and outputI Input onlyO Output onlyPU Internal pull upPD Internal pull downD Open drain outputZ Tri-state outputmA DC sink capabilityCopyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --March 4, 2009, Advance Document Classification: Proprietary Information Page 988E1111 Product BriefIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. --Copyright © 2009 Marvell Page 10Document Classification: Proprietary InformationMarch 4, 2009, AdvanceTable 1:Media Dependent Interface117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name Pin TypeDescriptionN1N229314142MDI[0]+MDI[0]-I/O, DMedia Dependent Interface[0].In 1000BASE-T mode in MDI configuration, MDI[0]± correspond to BI_DA±.In MDIX configuration, MDI[0]± correspond to BI_DB±.In 100BASE-TX and 10BASE-T modes in MDI configuration, MDI[0]± are used for the transmit pair. In MDIX configuration, MDI[0]± are used for the receive pair. MDI[0]± should be tied to ground if not used.N3N433344647MDI[1]+MDI[1]-I/O, D Media Dependent Interface[1].In 1000BASE-T mode in MDI configuration, MDI[1]± correspond to BI_DB±.In MDIX configuration, MDI[1]± correspond to BI_DA±.In 100BASE-TX and 10BASE-T modes in MDI configuration, MDI[1]± are used for the receive pair. In MDIX configuration, MDI[1]± are used for the transmit pair.MDI[1]± should be tied to ground if not used.N6 N739415657MDI[2]+MDI[2]-I/O, D Media Dependent Interface[2].In 1000BASE-T mode in MDI configuration,MDI[2]±correspond to BI_DC±.In MDIX configuration, MDI[2]± correspondsto BI_DD±.In 100BASE-TX and 10BASE-T modes,MDI[2]±are not used.MDI[2]± should be tied to ground if not used.N8 N942436162MDI[3]+MDI[3]-I/O, D Media Dependent Interface[3].In 1000BASE-T mode in MDI configuration,MDI[3]± correspond to BI_DD±.In MDIX configuration, MDI[3]± correspondto BI_DC±.In 100BASE-TX and 10BASE-T modes,MDI[3]± are not used.MDI[3]± should be tied to ground if not used.Table 1:Media Dependent Interface (Continued)117-TFBGA Pin #96-BCCPin #128-PQFPPin #Pin Name PinTypeDescriptionCopyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. -- Copyright © 2009 Marvell The GMII interface supports both 1000BASE-T and 1000BASE-X modes of operation. The GMII interface pins are also used for the TBI interface. See Table 3 for TBI pin definitions. The MAC interface pins are 3.3V tolerant. Table 2:GMII/MII Interfaces117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name PinTypeDescriptionE2814GTX_CLKIGMII Transmit Clock. GTX_CLK provides a 125 MHz clock reference for TX_EN, TX_ER, and TXD[7:0]. This clock can be stopped when the device is in 10/100BASE-T modes, and also during Auto-Negotiation.D1410TX_CLK O, ZMII Transmit Clock. TX_CLK provides a 25 MHz clock reference for TX_EN, TX_ER, and TXD[3:0] in 100BASE-TX mode, and a 2.5 MHz clock reference in 10BASE-T mode.TX_CLK provides a 25 MHz, 2.5 MHz, or 0 MHz clock during 1000 Mbps Good Link, Auto-Negotiation, and Link Lost statesdepending on the setting of register 20.6:4.The 2.5 MHz clock is the default rate, which may be programmed to another frequency by writing to register 20.6:4.E1916TX_EN IGMII and MII Transmit Enable. In GMII/MII mode when TX_EN is asserted, data on TXD[7:0] along with TX_ER is encoded and transmitted onto the cable.TX_EN is synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.F2713TX_ER IGMII and MII Transmit Error. In GMII/MII mode when TX_ER and TX_EN are both asserted, the transmit error symbol is trans-mitted onto the cable. When TX_ER is asserted with TX_EN de-asserted, carrier extension symbol is transmitted onto the cable.TX_ER is synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.Copyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --J2J1H3H1H2G3G2F120191817161412112928262524201918TXD[7]TXD[6]TXD[5]TXD[4]TXD[3]/TXD[3]TXD[2]/TXD[2]TXD[1]/TXD[1]TXD[0]/TXD[0]IGMII and MII Transmit Data. In GMII mode, TXD[7:0] present the data byte to be trans-mitted onto the cable in 1000BASE-T mode. In MII mode, TXD[3:0] present the data nib-ble to be transmitted onto the cable in 100BASE-TX and 10BASE-T modes. TXD[7:4] are ignored in these modes, but should be driven either high or low. These pins must not float.TXD[7:0] are synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.Inputs TXD[7:4] should be tied low if not used (e.g., RGMII mode).C127RX_CLK O, ZGMII and MII Receive Clock. RX_CLK pro-vides a 125 MHz clock reference for RX_DV, RX_ER, and RXD[7:0] in 1000BASE-T mode, a 25 MHz clock reference in100BASE-TX mode, and a 2.5 MHz clock reference in 10BASE-T mode.TX_TCLK comes from the RX_CLK pins used in jitter testing. Refer to Register 9 for jitter test modes.B1944RX_DV O, ZGMII and MII Receive Data Valid. When RX_DV is asserted, data received on the cable is decoded and presented on RXD[7:0] and RX_ER.RX_DV is synchronous to RX_CLK.D238RX_ER O, ZGMII and MII Receive Error. When RX_ER and RX_DV are both asserted, the signals indicate an error symbol is detected on the cable.When RX_ER is asserted with RX_DV de-asserted, a false carrier or carrier extension symbol is detected on the cable. RX_ER is synchronous to RX_CLK.Table 2:GMII/MII Interfaces (Continued)117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name Pin TypeDescriptionIntegrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. --Copyright © 2009 Marvell C5A2A1C4B3C3D3B286878990919392951201211231241251261283RXD[7]RXD[6]RXD[5]RXD[4]RXD[3]/RXD[3]RXD[2]/RXD[2]RXD[1]/RXD[1]RXD[0]/RXD[0]O, ZGMII and MII Receive Data. Symbolsreceived on the cable are decoded and pre-sented on RXD[7:0] in 1000BASE-T mode. In MII mode, RXD[3:0] are used in100BASE-TX and 10BASE-T modes. In MII mode, RXD[7:4] are driven low. RXD[7:0] is synchronous to RX_CLK.B584115CRSO, ZGMII and MII Carrier Sense. CRS asserts when the receive medium is non-idle. In half-duplex mode, CRS is also asserted during transmission. CRS assertion during half-duplex transmit can be disabled by program-ming register 16.11 to 0.CRS is asynchronous to RX_CLK, GTX_CLK, and TX_CLK.B683114COL O, ZGMII and MII Collision. In 10/100/1000BASE-T full-duplex modes, COL is always low. In 10/100/1000BASE-T half-duplex modes, COL asserts only when both the transmit and receive media are non-idle. In 10BASE-T half-duplex mode, COL is asserted to indicate signal quality error(SQE). SQE can be disabled by clearing reg-ister 16.2 to zero.COL is asynchronous to RX_CLK, GTX_CLK, and TX_CLK.Table 2:GMII/MII Interfaces (Continued)117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name Pin TypeDescriptionThe TBI interface supports 1000BASE-T mode of operation. The TBI interface uses the same pins as the GMII interface. The MAC interface pins are 3.3V tolerant.Table 3:TBI Interface117-TFBGA Pin #96-BCCPin #128-PQFPPin #Pin Name PinTypeDescriptionE2814GTX_CLK/TBI_TXCLK I TBI Transmit Clock. In TBI mode, GTX_CLKis used as TBI_TXCLK. TBI_TXCLK is a 125MHz transmit clock.TBI_TXCLK provides a 125 MHz clock refer-ence for TX_EN, TX_ER, and TXD[7:0].D1410TX_CLK/RCLK1O, Z TBI 62.5 MHz Receive Clock- even codegroup. In TBI mode, TX_CLK is used asRCLK1.J2 J1 H3 H1 H2 G3 G2 F120191817161412112928262524201918TXD[7]TXD[6]TXD[5]TXD[4]TXD[3]TXD[2]TXD[1]TXD[0]I TBI Transmit Data. TXD[7:0] presents thedata byte to be transmitted onto the cable.TXD[9:0] are synchronous to GTX_CLK.Inputs TXD[7:4] should be tied low if notused (e.g., RTBI mode).E1916TX_EN/TXD8I TBI Transmit Data. In TBI mode, TX_EN isused as TXD8.TXD[9:0] are synchronous to GTX_CLK.F2713TX_ER/TXD9I TBI Transmit Data. In TBI mode, TX_ER isused as TXD9.TXD[9:0] are synchronous to GTX_CLK.TX_ER should be tied low if not used (e.g.,RTBI mode).C127RX_CLK/RCLK0O, Z TBI 62.5 MHz Receive Clock- odd code group. In the TBI mode, RX_CLK is usedas RCLK0.C5 A2 A1 C4 B3 C3 D3 B286878990919392951201211231241251261283RXD[7]RXD[6]RXD[5]RXD[4]RXD[3]RXD[2]RXD[1]RXD[0]O, Z TBI Receive Data code group [7:0]. In theTBI mode, RXD[7:0] present the data byte tobe transmitted to the MAC. Symbolsreceived on the cable are decoded and pre-sented on RXD[7:0].RXD[7:0] are synchronous to RCLK0 andRCLK1.B1944RX_DV/RXD8O, Z TBI Receive Data code group bit 8. In the TBI mode, RX_DV is used as RXD8.RXD[9:0] are synchronous to RCLK0 andRCLK1.Copyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. -- Copyright © 2009 Marvell D238RX_ER/RXD9O, ZTBI Receive Data code group bit 9. In the TBI mode, RX_ER is used as RXD9. RXD[9:0] are synchronous to RCLK0 and RCLK1.B584115CRS/COMMA O, Z TBI Valid Comma Detect. In the TBI mode, CRS is used as COMMA.B683114COL/LPBKITBI Mode Loopback. In the TBI mode, COL is used to indicate loopback on the TBI. When a “0 - 1" transition is sampled on this pin, bit 0.14 is set to 1.When a “1 - 0" is sampled on this pin, bit 0.14 is reset to 0.If this feature is not used, the COL pinshould be driven low on the board. This pin should not be left floating in TBI mode.Table 3:TBI Interface (Continued)117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name PinTypeDescriptionThe RGMII interface supports 10/100/1000BASE-T and 1000BASE-X modes of operation.The RGMII interface pins are also used for the RTBI interface. See Table5 for RTBI pin definitions. The MAC interface pins are 3.3V tolerant.Table 4:RGMII Interface117-TFBGA Pin #96-BCCPin #128-PQFPPin #Pin Name PinTypeDescriptionE2814GTX_CLK/TXC I RGMII Transmit Clock provides a 125 MHz,25 MHz, or 2.5 MHz reference clock with ±50 ppm tolerance depending on speed. InRGMII mode, GTX_CLK is used as TXC.H2 G3 G2 F11614121124201918TXD[3]/TD[3]TXD[2]/TD[2]TXD[1]/TD[1]TXD[0]/TD[0]I RGMII Transmit Data. In RGMII mode,TXD[3:0] are used as TD[3:0].In RGMII mode, TXD[3:0] run at double datarate with bits [3:0] presented on the risingedge of GTX_CLK, and bits [7:4] presentedon the falling edge of GTX_CLK. In thismode, TXD[7:4] are ignored.In RGMII 10/100BASE-T modes, the trans-mit data nibble is presented on TXD[3:0] onthe rising edge of GTX_CLK.E1916TX_EN/TX_CTL I RGMII Transmit Control. In RGMII mode,TX_EN is used as TX_CTL. TX_EN is pre-sented on the rising edge of GTX_CLK.A logical derivative of TX_EN and TX_ER ispresented on the falling edge of GTX_CLK.C127RX_CLK/RXC O, Z RGMII Receive Clock provides a 125 MHz,25 MHz, or 2.5 MHz reference clock with ±50 ppm tolerance derived from the receiveddata stream depending on speed. In RGMIImode, RX_CLK is used as RXC.B1944RX_DV/RX_CTL O, Z RGMII Receive Control. In RGMII mode,RX_DV is used as RX_CTL. RX_DV is pre-sented on the rising edge of RX_CLK.A logical derivative of RX_DV and RX_ER ispresented on the falling edge of RX_CLK.B3 C3 D3 B2919392951251261283RXD[3]/RD[3]RXD[2]/RD[2]RXD[1]/RD[1]RXD[0]/RD[0]O, Z RGMII Receive Data. In RGMII mode,RXD[3:0] are used as RD[3:0]. In RGMIImode, RXD[3:0] run at double data rate withbits [3:0] presented on the rising edge ofRX_CLK, and bits [7:4] presented on the fall-ing edge of RX_CLK. In this mode, RXD[7:4]are ignored.In RGMII 10/100BASE-T modes, the receivedata nibble is presented on RXD[3:0] on therising edge of RX_CLK.RXD[3:0] are synchronous to RX_CLK.Copyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. -- Copyright © 2009 Marvell The RTBI interface supports 1000BASE-T mode of operation. The RTBI interface uses the same pins as the RGMII interface. The MAC interface pins are 3.3V tolerant. Table 5:RTBI Interface117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name PinTypeDescriptionE2814GTX _CLK/TXC IRGMII Transmit Clock provides a 125 MHz reference clock with ± 50 ppm tolerance. In RTBI mode, GTX_CLK is used as TXC. H2G3G2F11614121124201918TXD[3]/TD[3]TXD[2]/TD[2]TXD[1]/TD[1]TXD[0]/TD[0]IRTBI Transmit Data.In RTBI mode, TXD[3:0] are used asTD[3:0]. TD[3:0] run at double data rate with bits [3:0] presented on the rising edge of GTX_CLK, and bits [8:5] presented on the falling edge of GTX_CLK. In this mode, TXD[7:4] are ignored.E1916TX_EN/TD4_TD9IRTBI Transmit Data.In RTBI mode, TX_EN is used as TD4_TD9. TD4_TD9 runs at a double data rate with bit 4 presented on the rising edge of GTX_CLK, and bit 9 presented on the falling edge of GTX_CLK.C127RX_CLK/RXCO, ZRTBI Receive Clock provides a 125 MHz ref-erence clock with ± 50 ppm tolerance derived from the received data stream. In RTBI mode, RX_CLK is used as RXC.B3C3D3B2919392951251261283RXD[3]/RD[3]RXD[2]/RD[2]RXD[1]/RD[1]RXD[0]/RD[0]O, ZRTBI Receive Data.In RTBI mode, RXD[3:0] are used as RD[3:0]. RD[3:0] runs at double data rate with bits [3:0] presented on the rising edge of RX_CLK, and bits [8:5] presented on the fall-ing edge of RX_CLK. In this mode, RXD[7:4] are ignored.B1944RX_DV/RD4_RD9O, ZRTBI Receive Data.In RTBI mode, RX_DV is used asRD4_RD9. RD4_RD9 runs at a double data rate with bit 4 presented on the rising edge of RX_CLK, and bit 9 presented on the fall-ing edge of RX_CLK.Table 6:SGMII Interface117-TFBGA Pin #96-BCCPin #128-PQFPPin #Pin Name PinTypeDescriptionA3 A48281113112S_IN+S_IN-I SGMII Transmit Data. 1.25 GBaud input -Positive and Negative.Input impedance on the S_IN± pins may beprogrammed for 50 ohm or 75 ohm imped-ance by setting register 26.6. The inputimpedance default setting is determined bythe 75/50 OHM configuration pin.A5 A67980110109S_CLK+S_CLK-I/O SGMII 625 MHz Receive Clock.For Serial Interface modes(HWCFG_MODE[3:0] = 1x00) the S_CLK±pins become Signal Detect± (SD±) inputs.A7 A87775107105S_OUT+S_OUT-O, Z SGMII Receive Data. 1.25 GBaud output -Positive and Negative.Output impedance on the S_OUT± pins maybe programmed for 50 ohm or 75 ohmimpedance by setting register 26.5. Outputamplitude can be adjusted via register26.2:0. The output impedance default settingis determined by the 75/50 OHM configura-tion pin.Copyright © 2009 Marvell Doc. No. MV-S105540-00, Rev. --Integrated 10/100/1000 Ultra Gigabit Ethernet TransceiverDoc. No. MV-S105540-00, Rev. --Copyright © 2009 Marvell Table 7: 1.25 GHz Serial High Speed Interface117-TFBGA Pin #96-BCC Pin #128-PQFP Pin #Pin Name Pin TypeDescriptionA3A48281113112S_IN+S_IN-I1.25 GHz input - Positive and Negative. When this interface is used as a MAC inter-face, the MAC transmitter’s positive output connects to the S_IN+. The MAC transmit-ter’s negative output connects to the S_IN-. When this interface is used as a fiber inter-face, the fiber-optic transceiver’s positive output connects to the S_IN+. The fiber-optic transceiver’s negative output connects to the S_IN-.Input impedance on the S_IN± pins may be programmed for 50 ohm or 75 ohm imped-ance by setting register 26.6. The input impedance default setting is determined by the 75/50 OHM configuration pin.A5A67980110109S_CLK+/SD+S_CLK-/SD-I Signal Detect input.For Serial Interface modes the S_CLK± pins become Signal Detect± (SD±) inputs.A7A87775107105S_OUT+S_OUT-O, Z1.25 GHz output − Positive and Negative. When this interface is used as a MAC inter-face, S_OUT+ connects to the MACreceiver’s positive input. S_OUT- connects to the MAC receiver’s negative input. When this interface is used as a fiber inter-face, S_OUT+ connects to the fiber-optic transceiver’s positive input. S_OUT- con-nects to the fiber-optic transceiver’s negative input.Output impedance on the S_OUT± pins may be programmed for 50 ohm or 75 ohm impedance by setting register 26.5. Output amplitude can be adjusted via register26.2:0. The output impedance default setting is determined by the 75/50 OHM configura-tion pin.B391125RXD[3]O, ZSerial MAC interface Copper Link Status[1] connection.1 = Copper link up 0 = Copper link down。

8K88主板软件调试说明一、工厂菜单调试说明1、进入工厂菜单的方法:a)用工厂遥控器按工厂调试键(3FH键)进入工厂模式b)先将伴音减到0,然后按住键控板“伴音-”键不放,再按遥控器上的“返回”键进入工厂模式2、在工厂调试菜单下,按下遥控器“返回”键,或再按一次工厂调试键(3F键)可以退出工厂调试菜单。

3、在老化模式下,按下遥控器“老化模式”键(39H键)或待机键退出老化模式。

4、白平衡调整:进入工厂,选择白平衡调节这一项,按右键进入白平衡调整子菜单,用白平衡仪检测,如发现有偏差,请按频道+/-键选择下面的a)R Gainb)G Gainc) B Gaind)R Offsete)G Offsetf) B Offset再按音量+/-键进行调整来达到最佳效果5、设置子菜单a、开机画面,按左/右键可以设置开机LOGO为“开”或“关”,设为“开”时开机显示LOGO,设为“关”时开机不显示LOGOb、单键模式,按左/右键可以设置单键模式为“开”或“关”;c、搜台导航,按左/右键可以设置开机时是否显示搜台导航菜单;d、复位,按右键开始进行复位动作,对EEPROM进行初始化,完成后会自动待机并再次开机,复位时对HDMI KEY和条码信息不作复位。

e、生产频道,在此处按右键可以把频道表重置为生产频道表。

二、版本信息显示如下版本信息 VERx.x机型 47E82RD (显示当前的机型)屏 LGD IPS 3D LEDCPU 8K88-VERx.x-xxxxxxEEP 8K88-xxxxxx显示当前使用的软件程序版本信息(机芯+软件版本+软件日期)和当前使用的存储器版本信息(机芯+日期)。

BARCODE信息显示按工厂遥控器的F3键(22H),或者把音量减到0,按住键控板的音量减键,同时按住遥控器的确定键,则会显示BARCODE信息。

信息内容如下:BARCODE: XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX (显示工厂的条码信息)MAC : 00:1A:9A:E8:00:00 (显示网卡的MAC地址)Panel LG IPS 3D LED (显示屏的型号)Resolution 1920x1080 (显示屏的分辨率)Refresh Rate 240Hz (显示屏的刷新频率)Color Depth 10bit (显示屏的显示颜色位深是8bit还是10bit的)Processor VII Engine (表示当前使用了VII引擎)注:如果没有用条码仪进行BARCODE和MAC地址写入,则BARCODE和MAC 这两行显示为空。