数字电路课内实验讲义201004

- 格式:doc

- 大小:2.03 MB

- 文档页数:19

数字电路实验讲义课题:实验一门电路逻辑功能及测试课型:验证性实验教学目标:熟悉门电路逻辑功能,熟悉数字电路实验箱及示波器使用方法重点:熟悉门电路逻辑功能。

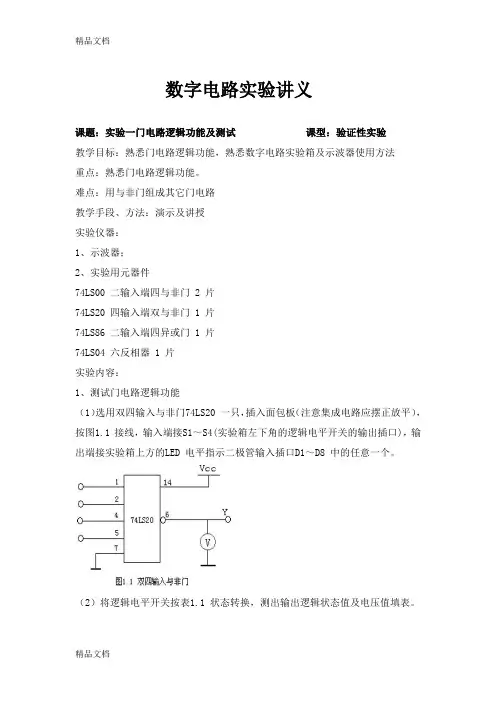

难点:用与非门组成其它门电路教学手段、方法:演示及讲授实验仪器:1、示波器;2、实验用元器件74LS00 二输入端四与非门 2 片74LS20 四输入端双与非门 1 片74LS86 二输入端四异或门 1 片74LS04 六反相器 1 片实验内容:1、测试门电路逻辑功能(1)选用双四输入与非门74LS20 一只,插入面包板(注意集成电路应摆正放平),按图1.1接线,输入端接S1~S4(实验箱左下角的逻辑电平开关的输出插口),输出端接实验箱上方的LED 电平指示二极管输入插口D1~D8 中的任意一个。

(2)将逻辑电平开关按表1.1 状态转换,测出输出逻辑状态值及电压值填表。

2、逻辑电路的逻辑关系(1)用74LS00 双输入四与非门电路,按图1.2、图1.3 接线,将输入输出逻辑关系分别填入表1.2,表1.3 中。

(2)写出两个电路的逻辑表达式。

3、利用与非门控制输出用一片74LS00 按图1.4 接线。

S 分别接高、低电平开关,用示波器观察S 对输出脉冲的控制作用。

4、用与非门组成其它门电路并测试验证。

(1)组成或非门:用一片二输入端四与非门组成或非门B+=,画出电路图,测试并填=AABY∙表1.4。

(2)组成异或门:①将异或门表达式转化为与非门表达式;②画出逻辑电路图;③测试并填表1.5。

5、异或门逻辑功能测试(1)选二输入四异或门电路74LS86,按图1.5 接线,输入端1、2、4、5 接电平开关输出插口,输出端A、B、Y 接电平显示发光二极管。

(2)将电平开关按表1.6 的状态转换,将结果填入表中。

6、逻辑门传输延迟时间的测量用六反相器74LS04 逻辑电路按图1.6 接线,输入200Hz 连续脉冲(实验箱脉冲源),将输入脉冲和输出脉冲分别接入双踪示波器Y1、Y2 轴,观察输入、输出相位差。

实验一 门电路逻辑功能测试及逻辑变换一、实验目的:1.掌握TTL 与非门、或非门和异或门输入与输出之间的逻辑关系。

2.熟悉TTL 中、小规模集成电路的外型、管脚和使用方法。

3. 熟悉逻辑功能的变换。

二、实验仪器及器件:1.数字电路实验箱 1台 2.二输入四与非门74LS00 1片 3. 二输入四或非门74LS28 1片 4. 二输入四异或门74LS86 1片 5.数字万用表 1块三、实验预习:1.复习各种门电路的逻辑符号、逻辑函数式、真值表。

2.查出实验所用集成电路的外引脚线排列图,熟悉其引脚线位置及各引脚线用途。

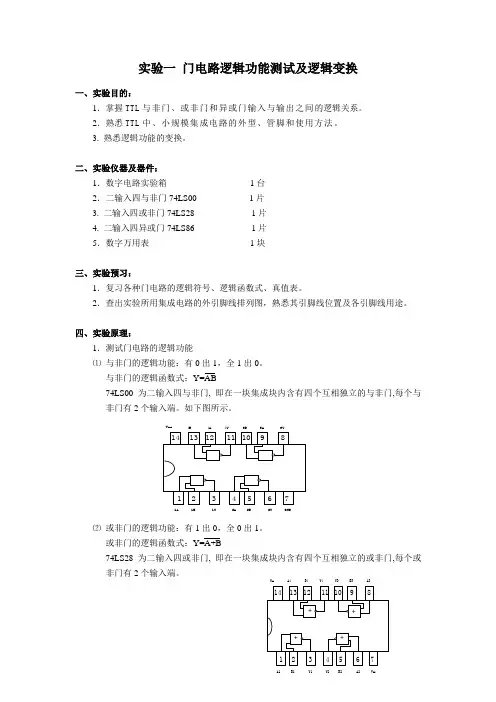

四、实验原理:1.测试门电路的逻辑功能⑴ 与非门的逻辑功能:有0出1,全1出0。

与非门的逻辑函数式:Y=AB74LS00为二输入四与非门, 即在一块集成块内含有四个互相独立的与非门,每个与非门有2个输入端。

如下图所示。

⑵ 或非门的逻辑功能:有1出0,全0出1。

或非门的逻辑函数式:Y=A+B74LS28为二输入四或非门, 即在一块集成块内含有四个互相独立的或非门,每个或非门有2个输入端。

Vcc 4B 4A 4Y 3B 3A 3Y1A1B1Y2A2B2YGND00 四2输入与非门V DDA4B4Y4Y3B3A3A1B1Y1Y2B2A2V SS4001 四2入或非门⑶异或门的逻辑功能:相同出0,相反出1。

异或门的逻辑函数式:Y=A⊕B=AB+AB74LS86为二输入四异或门,即在一块集成块内含有四个互相独立的异或门,每个异或门有2个输入端。

如图(c)所示。

2.门电路的逻辑变换:就是用与非门等组成其它门电路。

方法:先对其它门电路的函数式用摩根定理等公式变换成与非式,再画出相应逻辑图,然后用与非门实现之。

五、实验内容:实验前先检查实验箱电源是否正常,然后选择实验用的集成电路,按接线图连线。

特别注意V cc及地线不能接错。

线接好后经指导教师检查无误方可通电。

实验中改动接线必须先断开电源,接好线后再通电实验。

数字电路实验讲义目录1 数字电路实验箱简介2 实验一基本门电路和触发器的逻辑功能测试3 实验二常用集成组合逻辑电路(MSI)的功能测试及应用4 实验三常用中规模集成时序逻辑电路的功能及应用5 实验四组合逻辑电路的设计6 实验五时序逻辑电路的设计7 实验六综合设计实验8 附录功能常用芯片引脚图数字电路实验箱简介TPE系列数字电路实验箱是清华大学科教仪器厂的产品,该实验箱提供了数字电路实验所必需的基本条件。

如电源,集成电路接线板,逻辑电平产生电路,单脉冲产生电路和逻辑电平测量显示电路,实验箱还为复杂实验提供了一些其他功能。

下面以JK触发器测试为例说明最典型的测试电路,图1为74LS112双JK触发器的测试电路。

其中Sd、Rd 、J、K为电平有效的较入信号,由实验箱的逻辑电平产生电路提供。

CP为边沿有效的触发信号,由单脉冲产生电路提供。

Q和为电路的输出,接至逻辑电平测量显示电路,改变不同输入的组合和触发条件,记录对应的输出,即可测试该触发器的功能。

逻辑电平测量显示图1. JK触发器测试电路实验一 基本门电路和触发器的逻辑功能测试一、 实验目的1、掌握集成芯片管脚识别方法。

2、掌握门电路逻辑功能的测试方法。

3、掌握RS 触发器、JK 触发器的工作原理和功能测试方法。

二、实验设备与器件 1、数字电路实验箱 2、万用表 3、双列直插式组件 74LS00:四—2输入与非门 74LS86:四—2输入异或门 74LS112:双J-K 触发器三、实验原理与内容 1、测试与非门的逻辑功能74LS00为四—2输入与非门,在一个双列直插14引脚的芯片里封装了四个2输入与非门,引脚图见附录。

14脚为电源端,工作时接5V,7脚为接地端,1A ,113和1Y 组成一个与非门,B A Y 111⋅=。

剩余三个与非门类似。

按图1—1连接实验电路。

改变输信号,测量对应输出,填入表1—1中,验证其逻辑功能。

测 量 显示逻 辑 电平图1—1 74LS00测试电路2、测试基本RS 触发器功能两个与非门相接可构成基本RS 触发器,R 、S 为触发器的清0和置1输入端。

数字电路课内实验实验⼀组合逻辑电路⼀、实验⽬的熟悉简单组合电路的设计和分析过程。

⼆、实验要求:熟悉⼀位数值⽐较器、全减器逻辑功能,复习组合逻辑电路的分析和设计的步骤;熟悉74LS00 、74LS02、74LS04、74LS08管脚。

三、实验仪器设备及材料数字电路实验箱 1台,74LS00 三块,74LS02、74LS04、74LS08各⼀块四、实验⽅案1、设计⼀个能⽐较⼀位⼆进制A 与 B ⼤⼩的⽐较电路,⽤X1、X2、X3分别表⽰三种状态:A>B 时,X1=1;A(2)写出函数逻辑表达式;(3) 画出逻辑电路图,并画出实验连线图;(4)验证电路设计的正确性。

2、测量组合电路的逻辑关系:(1)图3-2电路⽤3块74LS00组成。

按逻辑图接好实验电路,输⼊端A 、B 、C 分别接“逻辑电平”,输出端D 、J 接LED“电平显⽰”;图3-2(2)按表3-2要求,将测得的输出状态和LED 显⽰分别填⼊表内;(3)根据测得的逻辑电路真值表,写出电路的逻辑函数式,判断该电路的功能。

表3-2五、实验报告主要内容包括,对实验步骤,实验数据、实验中的特殊现象、实验操作的成败、实验的关键点等内容进⾏整理、解释、分析总结,回答思考题,提出实验结论或提出⾃⼰的看法等。

六、思考题总结组合逻辑电路分析和设计步骤。

实验⼆译码器及其应⽤研究⼀、实验⽬的(1)测试3线-8线译码器74LS138的逻辑功能;(2)研究⽤译码器设计组合电路。

⼆、实验要求:熟悉译码器的逻辑功能,复习⽤译码器设计组合电路的步骤,了解74LS138、74LS30管脚。

三、实验仪器设备及材料数字电路实验箱 1台,74LS138、74LS30各⼀块四、实验⽅案1、74LS138逻辑功能测试对照74LS138引脚图连接实验连线图,使能端S 1、S 2′、S 3′和地址输⼊端A 2、A 1、A 0分别接“逻辑电平”,输出端接LED“电平显⽰”;将测试结果填⼊功能表4-1。

实验箱简介一、实验箱的组成及特点1.实验箱的供电实验箱的后方设有带保险丝管(0.5A)的220V单相交流三芯电源插座(配有三芯插头电源线一根)。

箱内设有一只降压变压器,供直流稳压电源。

2.两块大型(433 mm×323mm)单面散敷铜印刷线路板,正面丝印有清晰的各部件、元器件的图形、线条和字符;反面则是装接其相应的实际元器件。

该板上包含着以下各部分内容:(1)左下角装有带灯电源总开关一只。

(2)高性能双列直插式圆脚集成电路插座41只(其中40P 3只,28P 2只,24P,2只,20P 4只,16P 17只,14P 9只,8P 4只)。

(3)900多只高可靠的自锁紧式、防转、叠插式插座。

它们与集成电路插座、镀银针管座以及其它固定器件,线路等已在印制板面连接好。

正面板上有黑线条连接的地方,表示内部(反面)已接好。

采用高性弹性插件,这类插件,其插头与插座之间的导电接触面很大,接触电阻极其微小(接触电阻<Ω,使用寿命>10000次以上),而且插头之间可以叠插,从而可形成一个立体布线空间,使用起来极为方便。

(4)90多根镀银长(15mm)紫铜针管插座,供实验接插小型电位器、电阻、电容等分立元件之用(它们与相应的锁紧插座已在印刷面连通)。

(5)2只无译码LED数码管,其中“共阴”,“共阳”各一只。

¥八个显示段的管脚均已与相应的锁紧插座相连。

(6)6位十六进制七段译码器与LED数码显示器每一位译码器均采用可编程器件GAL设计而成,具有十六进制全译码功能。

显示器采用LED共阴极红色数码管(与译码器在反面已连接好),可显示四位BCD码十六进制的全译码代号:0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F。

(7)4位BCD码十进制码拔码开关组每一位的显示窗指示出0~9中的一个十进制数字,在A、B、C、D四个输出插口处输出相对应的BCD 码。

每按一次“+”或“-”键,将顺序地进行加1计数或减1计数。

实验一:集成逻辑门电路的测试与使用一. 实验目的:1.学会检测常用集成门电路的好坏的简易方法;2.掌握TTL 与非门逻辑功能和主要参数的测试方法; 3.掌握TTL 门电路与CMOS 门电路的主要区别; 4.掌握三态门的特点及应用。

二. 实验仪器与器件:1.实验仪器:稳压电源、万用表、数字逻辑实验测试台。

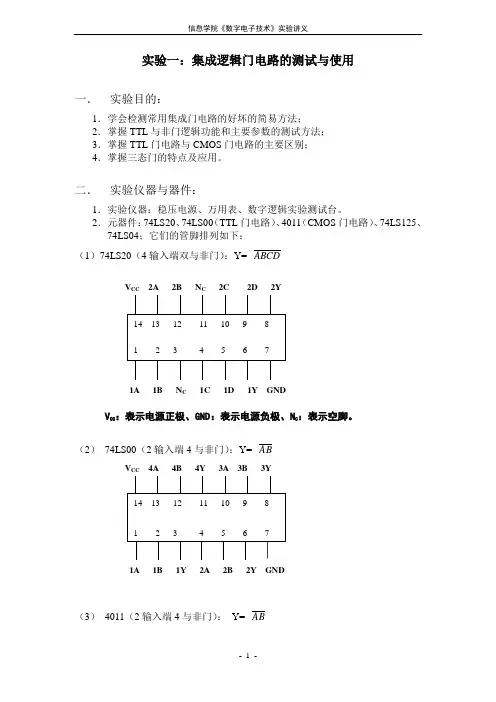

2.元器件:74LS20、74LS00(TTL 门电路)、4011(CMOS 门电路)、74LS125、74LS04;它们的管脚排列如下: (1)74LS20(4输入端双与非门):Y= ABCDV2A 2B N 2C 2D 2Y1A 1B N C 1C 1D 1Y GNDV CC :表示电源正极、GND :表示电源负极、N C :表示空脚。

(2) 74LS00(2输入端4与非门):Y= AB V 4A 4B 4Y 3A 3B 3Y1A 1B 1Y 2A 2B 2Y GND(3) 4011(2输入端4与非门): Y= ABV4A 4B 4Y 3Y 3B 3A1A 1B 1Y 2Y 2B 2A GND(4)74LS125(三态缓冲器):Y=A (C=0)、Y 为高阻(C=1)V CC 4C 4A 4Y 3C 3A 3Y(5)74LS04(非门): Y= A1A 1Y 2A 2Y 3A 3Y GND集成门电路管脚的识别方法:将集成门电路的文字标注正对着自己,左下角为1,然后逆时针方向数管脚。

三. 实验原理:1.TTL 与非门的主要参数有:导通电源电流I CCL 、低电平输入电流I IL 、高电平输入电流I IH 、输出高电平V OH 、输出低电平V OL 、阈值电压V TH 等。

注意:不同型号的集成门电路其测试条件及规范值是不同的。

2.检测集成门电路的好坏的简易方法:(1)在未加电源时,利用万用表的电阻档检查各管脚之间是否有短路现象;(2)加电源:利用万用表的电压档首先检查集成电路上是否有电,然后再利用门电路的逻辑功能检查电路。

数字电路实验讲义实验一KHD-2型数字电路实验装置的使用和集成门电路逻辑功能的测试一、实验目的1.熟悉和掌握KHD-2型数字电路实验装置的使用。

2.熟悉74LS20和74LS00集成门电路的外形和管脚引线。

3.掌握与门、或门、非门、与非门、或非门和异或门逻辑功能的测试。

二、实验器材及设备1.KHD-2数字电路实验台2.4输入2与非门74LS20(1块)3.2输入4与非门74LS00或CC4011(1块)三、实验原理(一)KHD-2型数字电路实验台KHD-2型数字电路实验台由实验控制屏与实验桌组成。

实验控制屏主要由两块单面敷铜印刷线路板与相应电源、仪器仪表等组成。

控制屏由两块相同的数电实验功能板组成,其控制屏两侧均装有交流电压220V的单相三芯电源插座。

每块实验功能板上均包含以下各部分内容:1.实验板上装有一只电源总开关及一只熔断器(额定电流为1A)作为短路保护用。

2.实验板上共装有600多个高可靠的自锁紧式、防转、叠插式插座。

它们与集成电路插座、镀银针管座以及其他固定器件、线路的连线已设计在印刷线路板上。

板正面印有黑线条连接的器件,表示反面已装上器件并接通。

3.实验板上共装有200多根镀银长15mm的紫铜针管插座,供实验时接插小型电位器、电阻、电容、三极管及其他电子器件使用。

4.实验板上装有四路直流稳压电源(±5V、1A及两路0~18V、0.75A可调的直流稳压电源)。

实验板上标有处,是指实验时需用导线将直流电源+5V引入该处,是+5V 电源的输入插口。

5.高性能双列直插式圆集成电路插座18只(其中40P 1只、28P 1只、24P 1只、20P 1只、16P 5只、14P 6只、8P 2只、40P锁紧座1只)。

6.6位十六进制七段译码器与LED数码显示器:每一位译码器均采用可编程器件GAL 设计而成,具有十六进制全译码功能。

显示器采用LED共阴极红色数码管(与译码器在反面已连接好),可显示四位BCD十六进制的全译码代号:0、1、2、3、4、5、6、7、8、9、A、B、C、D、E和F。

实验二:TTL集成逻辑门的逻辑功能与参数测试一、实验目的1、掌握TTL集成与非门的逻辑功能。

2、掌握TTL器件的使用规则。

3、熟悉数字电路实验装置的结构,基本功能和使用方法。

二、实验原理本实验采用四输入双与非门74LS20和二输入四与非门74LS00,四输入双与非门是在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图2-1(a)、(b)、(c)所示。

(b)(a) (c)图2-1 74LS20逻辑框图、逻辑符号及引脚排列与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=三、实验设备与器件1、+5V直流电源。

2、逻辑电平开关。

3、逻辑电平显示器。

4、直流数字电压表。

5、74LS20、74LS006、1KΩ电阻器(0.5W)四、实验内容、步骤及数据记录在合适的位置选取一个14P插座,按定位标记插好74LS20集成块。

1、验证TTL集成与非门74LS20的逻辑功能按图2-2接线,门的四个输入端接逻辑开关输出插口,以提供“0”与“1”电平信号,开关向上,输出逻辑“1”,向下为逻辑“0”。

门的输出端接由 LED发光二极管组成的逻辑电平显示器(又称0-1指示器)的显示插口,LED亮为逻辑“1”,不亮为逻辑“0”。

按表2-2的真值表逐个测试集成块中两个与非门的逻辑功能。

74LS20有4个输入端,有16个最小项,在实际测试时,只要通过对输入1111、0111、1011、1101、1110五项进行检测就可判断其逻辑功能是否正常。

图2-2 与非门逻辑功能测试电路表2-22、利用与非门组成其他门电路并测试其逻辑功能 (1)组成与门电路用与非门74LS00组成与门Z=A ﹒B ,画出测试电路(并注明芯片的引线端口),并完成表2-3。

表2-3(2)组成或门电路用与非门74LS00组成或门Z=A+B ,画出测试电路,并完成表2-4。

第一部分实验教学部分基本原理实验实验一门电路逻辑功能测试及应用一、实验目的1.熟悉数字电路学习机和双踪示波器的使用方法;2.熟悉门电路的逻辑功能;3.掌握TTL门电路、CMOS门电路功能及外特性的测试方法;4.掌握基本集成逻辑芯片的正确使用与应用。

二、实验器材1.数字电路学习机1台2.双踪示波器1台3.万用表1台4.集成芯片74LS00四2输入TTL与非门1片74LS02四2输入TTL或非门1片TC4011四2输入COMS与非门1片5.0~10KΩ电位器1只6.导线若干三、预习要求1.了解数字电路学习机和双踪示波器的使用方法(见附录);2.熟悉所用集成芯片的引线位置及各引线用途;3.复习门电路工作原理及相应逻辑表达式;4.复习门电路主要特性及参数的意义。

四、实验内容及步骤实验前按学习机使用说明书先检查学习机电源是否正常,然后选择实验用的集成芯片,按自己设计的实验接线图接好连线,特别注意V CC及地线不能接错。

线接好后经实验指导老师检查无误方可通电实验。

实验中改动接线须先断开电源,接好线后再通电实验。

1.测试门电路的逻辑功能分别将集成芯片74LS00、TC4011、74LS02插入面包板,接好V CC和地线,输入端接S1~S8(电平开关输出插口)任意两个,输出端接电平显示发光二极管(D1~D8)任意一个,列出各自的真值表,写出逻辑表达式。

(集成芯片引脚图见图1-9、图1-10、图1-11)2.TTL门电路(74LS00)主要参数的测试(1)输出高电平V OH与输出低电平V OL的测定。

V OH—是指输入端有一个或一个以上为低电平时的输出高电平值,其测试图如图1-1所示。

V OL —是指输入端全部接高电平时的输出低电平值,其测试图如图1-2所示。

(2)输入短路电流I IS 的测定。

I IS —是指输入端有一个接地,其余输入端接高电平(或TTL 门输入端的开路)时,流入接地输入端的电流。

有时也把V I =0时的输入电流叫输入短路电流I IS 。

实验一TTL集成逻辑门的逻辑功能与参数测试一、实验目的1、掌握TTL集成与非门的逻辑功能和主要参数的测试方法2、掌握TTL器件的使用规则3、进一步熟悉数字电路实验装置的结构,基本功能和使用方法二、实验原理本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图1-1(a)、(b)、(c)所示。

(b)(a) (c)图1-1 74LS20逻辑框图、逻辑符号及引脚排列1、与非门的逻辑功能与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=2、TTL与非门的主要参数(1)低电平输出电源电流ICCL 和高电平输出电源电流ICCH与非门处于不同的工作状态,电源提供的电流是不同的。

ICCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。

ICCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。

通常ICCL>I CCH ,它们的大小标志着器件静态功耗的大小。

器件的最大功耗为P CCL =V CC I CCL 。

手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。

I CCL 和I CCH 测试电路如图1-2(a)、(b)所示。

[注意]:TTL 电路对电源电压要求较严,电源电压V CC 只允许在+5V ±10%的范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

(a) (b) (c) (d)图1-2 TTL 与非门静态参数测试电路图(2)低电平输入电流I iL 和高电平输入电流I iH 。

I iL 是指被测输入端接地,其余输入端悬空,输出端空载时,由被测输入端流出的电流值。

在多级门电路中,I iL 相当于前级门输出低电平时,后级向前级门灌入的电流,因此它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此希望I iL 小些。

数字电路实验讲义杭州电子科技大学2010.04实验1 数据选择器的应用1 实验目的1.了解数据选择器的电路结构和特点。

2.掌握数据选择器的逻辑功能和测试方法。

3.掌握数据选择器的基本应用。

2 实验仪器与器件3 实验原理数据选择器又称为多路开关,是一种重要的组合逻辑部件。

它是一个多路输入、单路输出的组合电路,能在通道选择信号(或称地址码)的控制下,从多路数据传输中选择任何一路信号输出。

在数字系统中,经常利用数据选择器将多条传输线上的不同数字信号,按要求选择其中之一送到公共数据线上。

另外,数据选择器还可以完成其它的逻辑功能,例如函数发生器、桶形移位器、并串转换器、波形产生器等。

(一)用门电路设计四选一数据选择器四选一数据选择器表达式为301201101001d A A d A A d A A d A A Y +++=,由表达式可以得到当A 1A 0=00时,Y=d 0;A 1A 0=01时,Y=d 1; A 1A 0=10时,Y=d 2;A 1A 0=11时,Y=d 3,这样就起到数据选择的作用。

同时由表达式可以直接用门电路设计出数据选择器电路,该电路如图2.4.1所示。

(二)双四选一数据选择器74LS153的应用74LS153数据选择器集成了两个四选一数据选择器,外形为双列直插,引脚排列如图2.4.2所示,逻辑符号如图2.4.3所示,其中D 0、D 1、D 2、D 3为数据输入端,Q 为输出端,A 0、A 1为数据选择器的控制端(地址码),同时控制两个数据选择器的输出,S 为工作状态控制端(使能端),74LS153的功能表见表2.4.1。

用数据选择器74LS153实现组合逻辑函数设计举例:当变量数等于地址端的数目时,则直接可以用数据选择器来实现逻辑函数。

现设逻辑函数F (X ,Y )=∑m (1,2),则可用一个四选一完成,根据数据选择器的定义:30120110100101D A A D A A D A A D A A )A ,Q(A +++=,令A 1=X ,A 0=Y ,1S =0(使能信号,低电平有效),1D 0=1D 3=0,1D 1=1D 2=1,那么输出Q=F 。

11≥1A 1A 0d 0d 1d 2d 3&&&&Y......910111212133144567815161S GNDV CC A 11D 31D 22D 02D 12D 22D 32Q1Q1D 02S A 01D 1A 1A 01G 03MUXEN 0231Q01231S 1D 01D 11D 21D 32S 2D 02D 12D 22D 32QEN 1图2.4.1 门电路实现的四选一数据选择器 图2.4.2 74LS153管脚图 图2.4.3 74LS153逻辑符号当变量数大于地址端的数目时,可采用降维或者集成芯片扩展的方式。

例如用一块74LS153实现一位全加器,一位全加器的逻辑函数表达式为:S (A ,B ,CI )=∑m (1,2,4,7) CO (A ,B ,CI )=∑m (3,5,6,7)以CI 为图记变量,降维后A 、B 作为数据选择器的地址端A 1、A 0,输出1Q=S ,2Q=CO ,卡诺图如图2.4.4和图2.4.5所示,得到数据输入:1D 0=CI ,1D 1=CI ,1D 2=CI ,1D 3=CI ,2D 0=0,2D 1=CI ,2D 2=CI ,2D 3=1,构成的逻辑电路如图2.4.6所示。

AB CIS000111100110011001降维ABS00011110CICICICIABCI 000111100101000111降维AB00011110CI1CICO COS图2.4.4 S 的卡诺图 图2.4.5 CO 的卡诺图 图2.4.6 一位全加器的电路图(三)八选一数据选择器74LS151的应用74LS151外形为双列直插,引脚排列如图2.4.7所示,逻辑符号如图2.4.8所示。

其中D 0、D 1、D 2、D 3、D 4、D 5、D 6、D 7为数据输入端,Q 为输出端,A 0、A 1、A 2为数据选择器的控制端(地址码),控制数据选择器的数据输出,EN 为工作状态控制端(使能端),74LS151的功能表见表2.4.2。

八选一数据选择器的表达式为:70126012501240123012201210120012012D A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A )A ,A ,Q(A +++++++=输入 1 — — 0 0 0 0 0 1 0 1 0 输出01D 01Q 2Q 00 1 1SA 1A 01D 11D 21D 32D 02D 12D 22D 3表2.4.1 74LS153功能表91011121213314456781516D 3OOA 1GNDV CCEN QQ A 0D 7D 6D 3D 2D 1D 0A 2ENFD 4D 5F D2D 1D 0D 4D 5D 6D 7A 0A 1A 2图2.4.7 74LS151的管脚图 图2.4.8 74LS151逻辑符号用数据选择器74LS151实现组合逻辑函数举例: 表2.4.2 74LS151功能真值表当变量数与地址码的数量一致,不需要降维或者扩展。

例如逻辑函数F (X ,Y ,Z )=∑(1,2,4,7),令A 2=X ,A 1=Y ,A 0=Z ,EN=0(使能端,低电平有效),D 1=D 2=D 4=D 7=1,D 0=D 3=D 5=D 6=0,那么输出Q=F 。

当逻辑函数的输入变量数超过了数据选择器的地址控制端位数时,则必须进行逻辑函数降维或者集成芯片扩展。

例如用一块74LS151实现四位奇偶校验码,当输入变量中有偶数个1时,输出为1,否则输出为0。

根据题意,列出真值表,真值表和卡诺图如表2.4.3和图2.4.9所示,降维后即可得到电路如图2.4.10所示。

表2.4.3 奇偶校验码真值表CDB0001111001A A0AA AA AF 降维CD00011110000101000110F 111001100110AB图2.4.9 卡诺图和降维卡诺图 图2.4.10 电路图(四)数据选择器的扩展有些MUX 采用3S (即三态)输出结构,这样就为扩展提供了方便。

例如用两片74LS151扩展成十六选一的数据选择器,如图2.4.11所示。

输 入A B C D 0 0 0 00 0 0 1 0 0 1 0 0 0 1 1 输出0001F 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1011001101001输入输出EN A 2A 1A 0Q X X X 1000000000000010100111001011101110D 0D 1D 2D 3D 4D 5D 6D 710MHz图2.4.11 数据选择器的扩展图2.4.12 数据选择器的典型应用(五)数据选择器的综合应用数据选择器与分频器结合产生一组不同频率的选择器。

如图2.4.12所示,有一振荡频率为10MH Z具有较高频率稳定度的晶体振荡器,晶振输出的方波再经8级十分频器,就能同时获得频率从1MH Z到0.1H Z的8种方波信号,供实验电路选择。

这种选择完全由数据选择器的地址码A2 A1 A0来决定。

4 实验内容(一)基础实验部分1.验证74LS151的逻辑功能按表所列测试,特别注意所测芯片A2、A1、A0哪一个是高位,EN端是否低电平有效,当芯片封锁时,输出是什么电平。

将实验结果记录在表2.4.4中。

2.用74LS153实现一位全加器用一块74LS153及门电路实现一位全加器,输入用3个开关分别代表A、B、CI,输出用2个指示灯分别代表CO、S1。

要求写出设计过程,画出逻辑图,并按表2.4.5要求改变开关状态,观察2个指示灯的变化,记录结果。

表2.4.4 验证74LS151的逻辑功能表2.4.5 一位全加器实验结果3.用数据选择器实现组合逻辑函数用八选一数据选择器或者四选一数据选择器设计一个电路,该电路有3个输入逻辑变量输入输出EN A2A1A0Q QX X X1000001010011100101110111A、B、C和1个工作状态控制变量M,当M=0时电路实现“意见一致”功能(A、B、C 状态一致输出为1,否则输出为0),而M=1时电路实现“多数表决”功能,即输出与A、B、C中多数的状态一致。

4.用74LS153扩展成一个八选一的数据选择器,再实现实验3,要求写出设计过程,画出电路图。

(二)提高部分5.利用八选一数据选择器或四选一数据选择器实现一个输血者血型和受血者血型符合输血规则的电路,输血规则如图2.4.13所示。

输血者血型编码A00 B01 AB10 O11受血者血型编码A00 B01 AB10 O11图2.4.13 输血规则表从规则可知,A型血能输给A、AB型,B型血能输给B、AB型,AB型血只能输给AB型,O型血能输给所有四种血型。

设输血者血型编码是X1X2,受血者血型编码是X3X4,符合输血血型规则时,电路输出F为1,否则为0。

6.试用八选一数据选择器74LS151或者四选一数据选择器74LS153和适当的门电路设计一个路灯控制电路。

要求在四个不同的地点都能独立地开灯和关灯。

写出设计过程,并且验证设计结果是否正确。

(提示:可以把四个地点的开关当作四个变量,当变量为奇数个1时,路灯亮,偶数个时灭。

)7.利用74LS151数据选择器实现判断电路表2.4.6 课程学分表学生选修课程及学分如表2.4.6所示,每个学生至少必须选满6个学分,但是A,B课程因时间冲突,不能同时选上。

利用数据选择器实现判断电路,满足要求时输出Y为1,否则为0。

写出设计过程,并且验证设计结果是否正确。

8.用两块74LS153和一个七段数码管(实验箱上提供,已有译码器)构成数据显示器,实验要求电路在任意时刻能显示1(0001)、6(0110)、9(1001)、8(1000)四个数据之一,由地址码控制串行显示。

9.用74LS153来实现第7题。

10.用Multsim软件来设计和仿真实验7、9题。

5 思考题1.说明数据选择器的地址输入端和选通端各有什么作用?2.如何用74LS151设计4位奇偶校验电路?3.如何用74LS151实现10110111序列信号?4.数据选择器地址端的权重高低与被选函数输入数据有什么联系?实验2组合逻辑电路的设计1 实验目的1.掌握用基本门电路进行组合电路设计的方法。