CMOS二输入与非门设计

- 格式:docx

- 大小:411.43 KB

- 文档页数:15

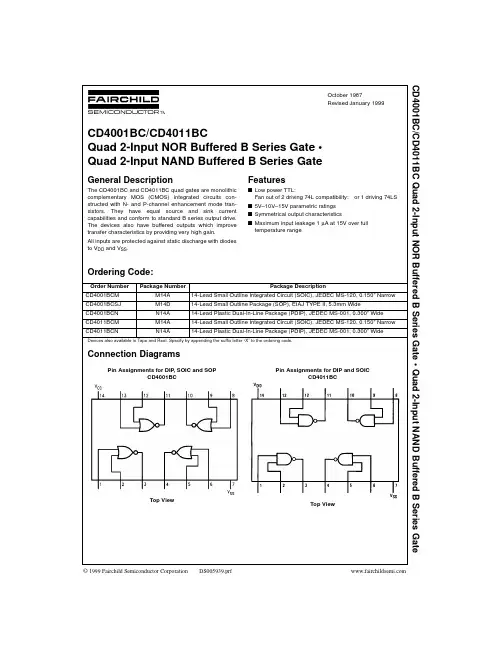

October 1987Revised January 1999CD4001BC/CD4011BC Quad 2-Input NOR Buffered B Series Gate• Quad 2-Input NAND Buffered B Series Gate © 1999 Fairchild Semiconductor Corporation DS005939.prf CD4001BC/CD4011BCQuad 2-Input NOR Buffered B Series Gate •Quad 2-Input NAND Buffered B Series GateGeneral DescriptionThe CD4001BC and CD4011BC quad gates are monolithiccomplementary MOS (CMOS) integrated circuits con-structed with N- and P-channel enhancement mode tran-sistors. They have equal source and sink currentcapabilities and conform to standard B series output drive.The devices also have buffered outputs which improvetransfer characteristics by providing very high gain.All inputs are protected against static discharge with diodesto V DD and V SS.Featuress Low power TTL:Fan out of 2 driving 74L compatibility:or 1 driving 74LSs5V–10V–15V parametric ratingss Symmetrical output characteristicss Maximum input leakage 1 µA at 15V over fulltemperature rangeOrdering Code:Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramsPin Assignments for DIP, SOIC and SOPCD4001BCTop ViewPin Assignments for DIP and SOICCD4011BCTop ViewOrder Number Package Number Package DescriptionCD4001BCM M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” NarrowCD4001BCSJ M14D14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideCD4001BCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WideCD4011BCM M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” NarrowCD4011BCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide。

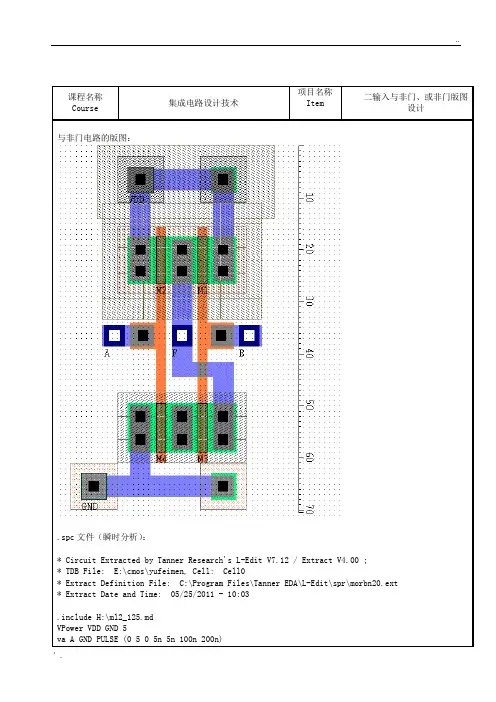

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

集成电路设计方向综合课程设计课设题目:加法器电路设计课设仪器:PC机、linux环境、Candence软件学院:专业:班级/学号:姓名:指导老师:目录一:课设内容 (3)二:课设目的 (3)三:加法器背景介绍 (3)四:半加器介绍 (4)1:半加器概念 (4)2:半加器真值表逻辑表达式 (4)五:半加器设计 (5)六:设计内容 (6)1:与非门结构 (6)2:与非门分析 (8)3:半加器电路图的绘制 (11)4:半加器版图的设计 (17)5:版图设计规则 (19)4:课设中出现的问题及分析 (22)七:课设心得 (22)一:课设内容1、查找文献,涉及一个加法器电路;2、基于Cadence的Virtuso平台画出电路图;3、采用Spectre对加法器进行仿真,主要仿真内容:加法器功能、负载电容、功耗;4、基于Virtuso平台画出加法器电路的版图,包括MOS晶体管的版图;5、提交课设报告;6完成答辩。

二:课设目的1:掌握集成电路设计技术和手段2:巩固数字集成电路所学知识3:提高搜集和综合信息能力,并能利用这些信息来实现自己所要实现的功能4:加深对Cadence软件使用的认识,并利用Cadence的Virtuso平台画出电路图5:掌握初步绘制版图的能力,并熟悉版图的设计规则三:加法器背景介绍人类社会的发展已经进入了信息时代,各种信息技术构成了信息时代的基础。

目前,与信息相关的计算机、微电子及通讯技术己经成为推动社会进步和国家发展的关键技术,而微电子技术又是信息技术的基础,因此集成电路产业己经成为整个电子信息产业的命脉。

而集成电路作为现代信息产业和信息社会的基础,是改造和提升传统产业的核心技术。

随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。

加法器作为各类集成电路模块的核心部件,其重要性不可忽略。

加法运算是最重要最基本的运算,所有的其他基本算术运算,如减法、乘法、除法运算等最终都能归结为加法运算[1]。

ttl、cmos集成与非门电路的主要参数和意义文章标题:深度解读ttl、cmos集成与非门电路的主要参数和意义一、引言TTL和CMOS集成与非门电路是数字电路中常见的两种逻辑门电路,它们在数字系统设计中扮演着重要的角色。

本文将深入探讨这两种电路的主要参数和意义,帮助读者更好地理解数字电路设计的基础知识。

二、TTL集成与非门电路的主要参数和意义1. 逻辑电平TTL集成与非门电路的逻辑电平指的是输入电压和输出电压的标准数值范围,其中高电平通常定义为2.4V至5V,低电平定义为0V至0.8V。

这个参数的意义在于确保在不同的电路之间可以进行可靠的信号传输和逻辑运算。

2. 传输延迟TTL集成与非门电路的传输延迟指的是从输入信号变化到输出信号变化所经过的时间。

传输延迟的主要影响因素包括晶体管的开关速度和电路中的负载电容等。

理解传输延迟对于设计高速数字系统至关重要,可以帮助设计师合理安排信号的传输路径和减小信号的时延。

3. 功耗TTL集成与非门电路的功耗是指在逻辑运算和信号放大过程中消耗的电能。

功耗的高低直接影响到电路的发热和稳定性。

合理控制功耗可以延长电路的寿命并减少系统的散热设计成本。

4. 抗干扰能力TTL集成与非门电路的抗干扰能力指的是在外部噪声和干扰的情况下,电路能够正确地进行逻辑运算和输出稳定的信号。

提高电路的抗干扰能力对于在工业环境中稳定运行至关重要。

5. 个人观点我认为TTL集成与非门电路在数字系统设计中具有重要的地位,其稳定性和可靠性经过了长期的验证,是非常成熟和可靠的数字逻辑电路。

三、CMOS集成与非门电路的主要参数和意义1. 静态功耗CMOS集成与非门电路的静态功耗指的是在无输入信号的情况下,由于晶体管的导通而导致的功耗。

静态功耗是CMOS电路一个重要的参数,尤其在移动设备和电池供电的场景下,合理控制静态功耗对于延长电池寿命至关重要。

2. 输入电阻CMOS集成与非门电路的输入电阻是指输入端对于外部信号的阻抗大小,它决定了电路的输入信号的驱动能力和对外部环境的适应能力。

或门电路目前实际应用的门电路都是集成电路。

在集成电路设计过程中,将复杂的逻辑函数转换为具体的数字电路时,不管是手工设计还是EDA工具自动设计,通常要用到七种基本逻辑(与、或、非、与非、或非、同或、异或)的图形表示,在电路术语中这些逻辑操作符号被称作门,对应的具体电路就叫做门电路,包括某个基本逻辑或者多个基本逻辑组合的复杂逻辑。

比如实现取反功能的反相器,就叫做非门;实现“先与后反”功能的就是与非门,如下图所示。

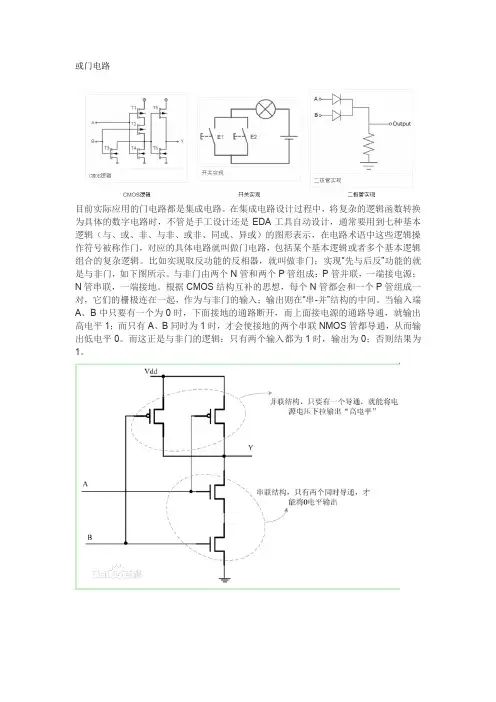

与非门由两个N管和两个P管组成:P管并联,一端接电源;N管串联,一端接地。

根据CMOS结构互补的思想,每个N管都会和一个P管组成一对,它们的栅极连在一起,作为与非门的输入;输出则在“串-并”结构的中间。

当输入端A、B中只要有一个为0时,下面接地的通路断开,而上面接电源的通路导通,就输出高电平1;而只有A、B同时为1时,才会使接地的两个串联NMOS管都导通,从而输出低电平0。

而这正是与非门的逻辑:只有两个输入都为1时,输出为0;否则结果为1。

CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO 器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO 逻辑门电路。

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

典型的CMOS与非门电路使用的电路CMOS与非门电路的概述CMOS(亦称为互补金属氧化物半导体)与非门电路是数字逻辑电路中常见的两种基本门电路。

CMOS与非门电路由CMOS技术实现,利用p型和n型金属氧化物半导体场效应晶体管(PMOS和NMOS)的组合来实现逻辑运算,并达到低功耗、高速度和抗干扰的效果。

本文将着重介绍典型的CMOS与非门电路的不同用途及其工作原理。

二级标题1:CMOS与非门电路的基本结构CMOS与非门电路是由一组PMOS和一组NMOS晶体管组成的。

PMOS晶体管是由p型半导体材料制成的,带有P型掺杂区域,而NMOS晶体管则是由n型半导体材料制成的,带有N型掺杂区域。

两组晶体管之间的交叉连接称为CMOS与非门电路。

二级标题2:CMOS与非门电路的用途CMOS与非门电路广泛应用于数字逻辑电路以及集成电路中,其用途丰富多样。

三级标题1:逻辑门电路CMOS与非门电路可以实现各种逻辑门电路,如与门、或门、非门、与非门、或非门。

通过合理的组合和连接,可以实现更复杂的逻辑功能,例如多位加法器和计数器等。

三级标题2:存储器 CMOS与非门电路还可以构建存储器单元,例如静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)。

这些存储器单元可以用于存储和获取数据,并在计算机系统中起到关键作用。

三级标题3:时钟和振荡器电路CMOS与非门电路还可以被用来构建时钟和振荡器电路。

时钟电路用于同步数字系统中各个部件的操作,而振荡器电路则用于产生特定频率的信号,例如计时器和脉冲发生器。

三级标题4:数据选择和复用CMOS与非门电路还可以实现数据选择和复用功能。

通过控制CMOS与非门电路的输入和输出,可以选择不同的数据源以及将多个输入信号复用到一个输出端口。

二级标题3:CMOS与非门电路的工作原理CMOS与非门电路的工作原理基于PMOS和NMOS晶体管的导通和截止。

当输入信号施加于CMOS与非门电路的端口时,其中的晶体管会根据输入信号的电平进行导通或截止。

《MOS管集成电路设计》期中论文CMOS二输入与非门设计日期:2015年5月21日一电路设计1.1 与非门基础 (3)1.2 CMOS二输入与非门 (4)二版图设计2.1 LASI7软件介绍 (5)2.2 版图设计过程 (5)三规则检查 (8)四 LTspice仿真 (10)4.1电路仿真分析软件简介 (10)4.2 LTspice仿真过程 (11)五总结 (15)六参考文献 (15)MOS(Metal-Oxide-Semiconductor)晶体管是一种金属-氧化物半导体硅场效应管,分为PMOS管和NMOS管两种,由NMOS和PMOS共同构成的电路即为CMOS电路。

和传统的TTL电路相比,MOS集成电路具有功耗较低,速度较快,输入阻抗高,热稳定性好等优点,因而在目前有着广泛的应有,可以预见的是,MOS集成电路代替TTL电路已是大势所趋。

与非门是一种数字电路的基本逻辑电路,可以看做是与门与非门的结合,若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1),在数字电路中有着非常重要的作用。

本设计旨在采用CMOS设计一个二输入的与非门,根据需要,它由两个PMOS(M3和M4)和两个NMOS(M1和M2)构成。

其中,两个PMOS作为上拉管,两个NMOS作为下拉管,两个输入信号A和B分别加在两对互补的NMOS管和PMOS管的栅极上,输出从他们的漏极引出。

设计完之后,用LASI7软件画出版图并进行规则检查。

关键词:CMOS、与非门、逻辑电路、LASI7一电路设计1.1 与非门基础与非门是数字电路中一种重要的逻辑电路,本设计设计的是二输入与非门,它有两个输入端和一个输出端,当输入均为高电平,输出为低电平;若输入中至少有一个为低电平,则输出为高电平,其逻辑符号如图1所示图1 二输入与非门逻辑符号由于有两个输入,所以真值表中它的组合共有4种形式,如表1所示1.2 CMOS二输入与非门二输入与非门的下拉管由串联的NMOS管M1和M2组成,上拉管则由并联的PMOS管的M3和M4构成。

数字集成电路设计

实验报告

院系名称

专业班级

学号

学生姓名

指导老师

时间

一、实验目的

通过实验了解CMOS反相器的工作原理,能自己用CMOS和PMOS 连接电路组合成2输入与非门。

实验求得直流特性曲线分析和瞬态分析。

二、实验内容

1、用软件求出输入输出电压曲线

2、通过设置不同的参数求得瞬态分析。

三、实验原理

四、实验步骤

.include "D:\Tanner\tanner\TSpice70\models\ml2_125.md" .dc lin source v5 0 5 0.1

.dc lin source v6 0 5 0.1

.print dc v(OUT)

VTC曲线

瞬态分析

五、实验心得

本次实验虽与上次实验相似,只是所求不一样。

能自己用CMOS 和PMOS连接电路组合成两输入与非门。

通过改变参数实验求得直流特性曲线分析和瞬态分析。

使我进一步了解mos管。

CMOS二输入与非门的设计CMOS(Complementary Metal-Oxide-Semiconductor)是一种常用的集成电路技术,它由N型和P型MOS(Metal-Oxide-Semiconductor)晶体管的互补结合构成。

CMOS技术具有功耗低、抗噪声能力强、集成度高等优点,广泛应用于数字逻辑电路设计中。

二输入与非门是最基本的逻辑门之一,它的输出与输入相反。

在CMOS技术中,二输入与非门的设计主要涉及到MOS晶体管的连接方式和输入信号的处理。

首先,我们需要了解CMOS技术中的N型和P型MOS晶体管的特性。

N型MOS 晶体管具有三个端口:栅(G),漏极(D)和源极(S)。

当栅极电压高于阈值电压时,N型MOS晶体管导通;当栅极电压低于阈值电压时,N型MOS晶体管截止。

P 型MOS晶体管也具有类似的特性,但是当栅极电压低于阈值电压时导通。

这种互补关系使得CMOS技术能够实现低功耗和高抗噪声能力。

在二输入与非门的设计中,我们可以使用两个N型MOS晶体管和两个P型MOS 晶体管来实现。

以下是一种常见的二输入与非门的CMOS电路设计:1. 首先,将两个N型MOS晶体管的漏极连接在一起,并与二输入与非门的输出端相连。

这个连接点称为输出节点。

2. 将两个P型MOS晶体管的漏极连接在一起,并与输出节点相连。

3. 一个N型MOS晶体管的栅极连接到输入信号A,另一个N型MOS晶体管的栅极连接到输入信号B。

4. 一个P型MOS晶体管的栅极连接到输入信号A,另一个P型MOS晶体管的栅极连接到输入信号B。

5. 将两个N型MOS晶体管的源极连接到地,将两个P型MOS晶体管的源极连接到电源Vdd。

通过这样的设计,当输入信号A和B都为高电平时,N型MOS晶体管导通,使得输出节点接地,输出低电平。

当输入信号A和B中至少一个为低电平时,N型MOS晶体管截止,P型MOS晶体管导通,使得输出节点连接到电源Vdd,输出高电平。

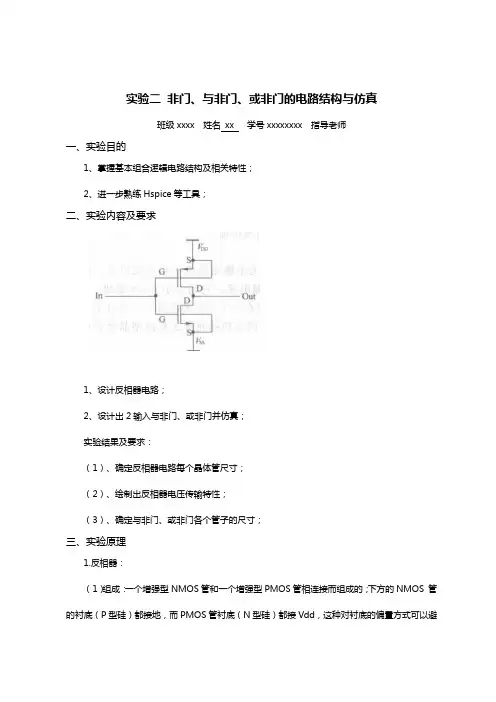

实验二非门、与非门、或非门的电路结构与仿真班级xxxx 姓名xx 学号xxxxxxxx 指导老师一、实验目的1、掌握基本组合逻辑电路结构及相关特性;2、进一步熟练Hspice等工具;二、实验内容及要求1、设计反相器电路;2、设计出2输入与非门、或非门并仿真;实验结果及要求:(1)、确定反相器电路每个晶体管尺寸;(2)、绘制出反相器电压传输特性;(3)、确定与非门、或非门各个管子的尺寸;三、实验原理1.反相器:(1)组成:一个增强型NMOS管和一个增强型PMOS管相连接而组成的;下方的NMOS 管的衬底(P型硅)都接地,而PMOS管衬底(N型硅)都接Vdd,这种对衬底的偏置方式可以避免源,漏区和衬底形成的PN结正偏,防止寄生效应。

(2)结构:CMOS反相器中输入端直接连接在NMOS管和PMOS管的栅极上,输入端引入的输入电平会直接影响NMOS管和PMOS管的工作状态。

而NMOS管和PMOS管的漏极则相互连接起来,构成了输出端,对外提供输出电平(Vout).注意:反相器的输出端并不是孤立的节点,而是连接有负载电容。

( 3 )在CMOS反相器中,NMOS管和PMOS管的栅源电压和漏源电压与输入,输出电平的关系为:V(GSN)= V(in);V(DSN)=V(out)V(GSP)=V(in)-V(DD);V(DSP)=V(out)-V(DD);备注:G为栅极,S为源极,D为漏极。

(5)反相器的工作原理:静态工作的CMOS反相器,当输入为逻辑值“0”时(V(in)= 0V),NMOS管的接地端为源极,NMOS管上的栅源电压为0V,而PMOS管接V(DD)的是源极,PMOS管的栅源电压为-V(DD).这就使得NMOS管处于截止状态而PMOS管处于导通状态;通过导通的PMOS管,在电源电压V(DD)与输出端连接的负载电容之间建立起了导电通路。

可以将负载电容充电到V(DD),使得输出的逻辑值变为“1”;当输入为逻辑值“1”时(此时的输入电平为V(DD),即V(in)=V(DD)),由于PMOS管的栅源电压为0V,而NMOS管的栅源电压为V(DD),使得PMOS管处于截止状态而NMOS管处于导通状态,这样就在负载电容与地电极之间通过NMOS管建立起了导电通路,使得负载电容被放电到0V,这就使输出逻辑值变为“0”。

CMOS二输入与非门的设计二输入与非门是一种逻辑门电路,它的输出与输入恰好相反。

当其中任意一个输入为高电平时(1),输出为低电平(0)。

只有当两个输入都是低电平(0)时,输出才为高电平(1)。

下面介绍一种基于CMOS技术的二输入与非门的设计方法。

CMOS二输入与非门的设计基于MOS管的工作原理。

CMOS电路中有两种MOS管,分别称为pMOS和nMOS。

pMOS管是由P型衬底和N型沟道构成,而nMOS管是由N型衬底和P型沟道构成。

两种MOS管的沟道可以通过引入电荷来控制电流。

1.首先构建一个与非门,包括两个输入端A和B和一个输出端Y。

这个与非门可以使用nMOS管和pMOS管来实现。

具体来说,nMOS管的源极连接到地,漏极连接到输出端Y,门极连接到输入端A。

pMOS管的源极连接到电源电压,漏极连接到输出端Y,门极连接到输入端B。

2.当输入A为低电平(0)时,nMOS管导通,pMOS管截止。

此时输出Y为高电平(1)。

3.当输入A为高电平(1)时,nMOS管截止,pMOS管导通。

此时输出Y为低电平(0)。

4.同样地,根据输入B的高低电平情况,可以推导出输出Y的高低电平情况。

1.功耗低:由于CMOS的特性,只有在输入变化时才会导通电流,因此功耗较低。

2.高噪声抗干扰特性:由于CMOS门电路的结构特点,能有效抑制噪声和干扰。

3.速度快:由于CMOS电路的响应时间很短,可以实现高速逻辑运算。

4.稳定性好:CMOS电路中的两种MOS管结构互补,可以避免静态功耗(电流流失)。

当然,CMOS二输入与非门还有一些缺点,例如:1.延迟较大:由于需要经过两个MOS管的开关过程,因此比较延迟。

2.静态功耗:尽管CMOS电路的静态功耗较低,但仍然会存在一些功耗。

综上所述,CMOS二输入与非门是一种基于CMOS技术的逻辑门电路。

通过合适的MOS管连接方式,可以实现输入与输出的恰好相反,从而满足与非门的功能要求。

CMOS技术的优点使得该设计具有低功耗、高噪声抗干扰特性、快速响应和稳定性好等特点,但也存在一些缺点,如延迟较大和静态功耗。

实验二非门、与非门、或非门的电路构造与仿真班级xxxx xx 学号xxxxxxxx 指导教师一、实验目的1、掌握根本组合逻辑电路构造及相关特性;2、进一步熟练Hspice等工具;二、实验容及要求1、设计反相器电路;2、设计出2输入与非门、或非门并仿真;实验结果及要求:〔1〕、确定反相器电路每个晶体管尺寸;〔2〕、绘制出反相器电压传输特性;〔3〕、确定与非门、或非门各个管子的尺寸;三、实验原理1.反相器:〔1〕组成:一个增强型NMOS管和一个增强型PMOS管相连接而组成的;下方的NMOS 管的衬底〔P型硅〕都接地,而PMOS管衬底〔N型硅〕都接Vdd,这种对衬底的偏置方式可以防止源,漏区和衬底形成的PN结正偏,防止寄生效应。

〔2〕构造:CMOS反相器中输入端直接连接在NMOS管和PMOS管的栅极上,输入端引入的输入电平会直接影响NMOS管和PMOS管的工作状态。

而NMOS管和PMOS管的漏极那么相互连接起来,构成了输出端,对外提供输出电平〔Vout〕.注意:反相器的输出端并不是孤立的节点,而是连接有负载电容。

( 3 )在CMOS反相器中,NMOS管和PMOS管的栅源电压和漏源电压与输入,输出电平的关系为:V(GSN)= V(in);V(DSN)=V(out)V(GSP)=V(in)-V(DD);V(DSP)=V(out)-V(DD);备注:G为栅极,S为源极,D为漏极。

(5)反相器的工作原理:静态工作的CMOS反相器,当输入为逻辑值“0〞时〔V〔in〕= 0V〕,NMOS管的接地端为源极,NMOS 管上的栅源电压为0V,而PMOS管接V〔DD〕的是源极,PMOS管的栅源电压为-V(DD).这就使得NMOS 管处于截止状态而PMOS管处于导通状态;通过导通的PMOS管,在电源电压V(DD)与输出端连接的负载电容之间建立起了导电通路。

可以将负载电容充电到V〔DD〕,使得输出的逻辑值变为“1〞;当输入为逻辑值“1〞时〔此时的输入电平为V〔DD〕,即V(in)=V(DD)〕,由于PMOS管的栅源电压为0V,而NMOS管的栅源电压为V(DD),使得PMOS管处于截止状态而NMOS管处于导通状态,这样就在负载电容与地电极之间通过NMOS管建立起了导电通路,使得负载电容被放电到0V,这就使输出逻辑值变为“0〞。

学号姓名

实验七1.反相器

反相器EECMOS的schematic图如下所示

其中PMOS管L=180nm W=720nm NMOS管L=180nm W=240nm

根据schematic画出的layout图如下所示

其中该版图长:2.16um 宽:4.87um

则版图面积为S=L*W=2.16*4.87=10.5192(um^2)

经过多此修改后,DRC验证如下

LVS验证如下

2.二输入与非门

二输入与非门nand2的schematic图如下所示

其中两个PMOS管的L=180nm W=720nm 两个NMOS管的L=180nm W=720nm

根据schematic图画出的layout版图如下所示

其中nand2版图的长:2.76um 宽:5.14um

则版图的面积S=L*W=2.76*5.14=14.1864(um^2)

通过改错后,DRC验证结果如下

LVS验证结果如下

3.二输入或非门

二输入或非门nor的schematic图如下所示

其中两个PMOS管的L=180nm W=2.51um 两个NMOS管的L=180nm W=500nm

由schematic图画出的layout版图如下所示

由于PMOS管的宽度较大,为了提高能通过的峰值电流,不浪费diff的面积,最大限度打满了源漏孔

其中该版图的长:2.91um 宽6.65um

则版图面积S=L*W=2.91*6.65=19.3531(um^2)

通过改错,DRC验证结果如下

LVS验证结果如下。

MOS 管集成电路设计》期中论文CMOS 二输入与非门设计日期:2015 年 5 月21 日目录一电路设计1.1与非门基础 (3)1.2 CMOS二输入与非门 (4)二版图设计2.1 LASI7软件介绍 (5)2.2版图设计过程 (5)三规则检查 (8)四LTspice 仿真 (10)4.1电路仿真分析软件简介 (10)4.2 LTspice仿真过程 (11)五总结 (15)六参考文献 (15)摘要MOS(Metal-Oxide-Semiconductor )晶体管是一种金属- 氧化物半导体硅场效应管,分为PMO管和NMO管两种,由NMO和PMOS共同构成的电路即为CMO电路。

和传统的TTL电路相比,MOS H成电路具有功耗较低,速度较快,输入阻抗高,热稳定性好等优点,因而在目前有着广泛的应有,可以预见的是,MOS集成电路代替TTL电路已是大势所趋。

与非门是一种数字电路的基本逻辑电路,可以看做是与门与非门的结合,若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1),在数字电路中有着非常重要的作用。

本设计旨在采用CMO设计一个二输入的与非门,根据需要,它由两个PMO(M3和M4和两个NMO(M1和M2构成。

其中,两个PMO作为上拉管,两个NMO作为下拉管,两个输入信号A和B分别加在两对互补的NMO管和PMO管的栅极上,输出从他们的漏极引出。

设计完之后,用LASI7 软件画出版图并进行规则检查。

关键词:CMO、S 与非门、逻辑电路、LASI7一电路设计1.1与非门基础与非门是数字电路中一种重要的逻辑电路,本设计设计的是二输入与非门,它有两个输入端和一个输出端,当输入均为高电平,输出为低电平;若输入中至少有一个为低电平,贝揃出为高电平,其逻辑符号如图1所示图1二输入与非门逻辑符号由于有两个输入,所以真值表中它的组合共有4种形式,如表1所示表1二输入与非门真值表1.2 CMOS二输入与非门二输入与非门的下拉管由串联的NMOST M1和M2组成,上拉管则由并联的PMO管的M3和M4构成。

两个输入信号A和B分别加在两对互补的NMO管和PMOST的栅极上,输出从他们的漏极引出。

当两个输入端A和B窦唯高电平时,两只NMO下拉管M1和M2 都导通,而两只PMOSb拉管M3和M4都截止,电源V DD和地之间没有电流通路形成,输出被导通的NMO下拉管拉倒低电平0,则输出为低电平;只要两个输入端有低电平输入,其对应的PMOSt拉管导通,但NMO下拉管截止,电源V DD到地之间没有电流通路形成,输出被导通的上拉管拉到V^D即输出高电平。

与真值表相对照,发现该电路实现了二输入与非门的功能。

用Multisim画出电路设计如图2所示图2 CMOSX输入与非门二版图设计2.1 LASI7 软件介绍LASIS是一个通用的IC布线和设计系统。

LASI可以用于各种电路的设计和布线,LASI 的图形功能很强,能够输入原理图并对其进行分析。

LASI 由一个主要的画图主程序和几个工具程序组成。

包括GDS CIF、DXF格式转换工具、位图格式的设计规则检查工具和一个能从原理图提取SPICE文件的图形化的SHPICE编译器。

LASI在80 年代中被作者用来在MS-DO下作为自己设计IC的软件,后来作者开发了WINDOWS的LASI。

LASI本身不支持SPICE仿真,但是LASI能够与现有很好的SPICE仿真工具集成。

另外,LASI作为一个开放式的项目,相关的电路资源十分丰富。

2.2 版图设计过程完成了电路原理图设计之后,需要用LASI7 进行版图的设计。

打开LASI7 之后,首先要对各层属性进行设计,点击Attr 按钮,在弹出的对话框中即可进行相关层属性的设置。

如图 3 所示Layer AttributesAttribute! Tabte 15or[~F][y][v )m[~^~]T~]mrT~)[ncv]iv )rv"]r^~]□ □□目回罔園頤叼■« BcocnciJcmDciJczicn 垄画畐區nDash _QJ -------------------------------------------B ----------------------CS ------------------- CZ) -------------------图3 Attr 界面本设计对板层属性的设置如表 2所示 Layer Color Fill Dash CONT A 13 0 NWEL W 0 3 NSEL G 0 0 PSEL Y 0 0 POLI R 7 0 MET1 B 9 0 ACTVG3表2板层属性设置接下来设置栅格属性,打开 Cnfg 对话框进行设置,如图4所示■ E PADS 囲 ■PWEL 41 ■NWEL 4?■ 匚 AC7V 43■ □ PSEL 44 ■ □ NSEL 45 ■ 0POL1 46 ■E MET1 490K页 -------------------|y|ARRW □ OTLN 5CHW NTXT _ CTXT Dixr _|PTXT J CONT1」V1A1□ MFR □ OVGL卩0L2PEAS CWEL二 V1A2_MET3生 32 33 開 37 35 罰Cn'g (Dra ™ n g Corf gLraTjorQ^|图5 NMOS 版图图 6 PMOS 版图Draw Resabiion 1 WOConwnor FLC FelderCell ResaLTioi 敏 Shial Cell Outkre 5dld 呼 Drts 、Hde图4 Cnfg 设置在设置完成之后,先新建一个cell ,命名为NMO ,采用N 掺杂, 在该cell 中画出NMO ,如图5所示。

在新建cell ,命名为PMOS 采用P 掺杂,N 阱工艺画出PMOS 如图6所示Opticme |~| Ude lODtiaE ^I'.fee- Te^iToobar | De niter ~op Todber □ Lkt d Cgfriinanc Mwu ~~| Lock Wxtow Fra™ |TjndfSihell Adi 禅 Madk |J| SnownMl [rrpert Oriy Nw Layier N LFI I MIS I Lnyc^ Descrndng L^| ■Jhdup Sef* Savrig Cdl |严屯k InCXIl~~l 03 低 Vflieri Ckvslro □ Wrttt OdTLCFomatI I Tjm> cn W HS Mooetoc L TILA |T 」rnonrRdU i Cikz? Sd /ai | T 」m eff Tcgge Redr™Working 订片◎容0.5Da SideEdkre在画好了NMO$口PMO之后,再新建一个cell,调出NMO和PMOS 画出最终需要的CMO二输入与非门。

其中,电源部分采用N阱工艺, 同时加入N掺杂,GN[部分采用P掺杂。

如图7所示图7 CMOSX输入与非门三规则检查在设计好了版图之后,需要对相关的规则的进行检查。

点击System-LasiDrc-Setup-Browse,将规则导入,如图8所示,点击“0K。

图8规则导入导入完成后点击Go即开始检查,结果如图9和图10所示Sc alih rilg Ar rm图9规则检查过程La s i DruDRC Completed ... 0 Total MapsTotal Run Time: OhrQrin-feec图10规则检查结果从检查结果可以看出,本设计没有错误四LTspice 仿真4.1电路仿真分析软件简介电路仿真(simulation )分析软件很多,有用于模拟电路的、有用于数字电路的、有既可以用于数字电路也可以用于模拟电路的,而且在这些软件中,有的功能非常强大,用户使用起来很方便、并且容易入手,而有些就要逊色多了,用户可以根据实际情况选择适合的。

LTspice是集成电路仿真分析软件其中之一,它是一个可视化的图形输入电路仿真软件,在win dows操作系统下运行。

Linear Tech no logy 公司是一家大型的美国电子元器件制造商,它生产各种各样电子元器件,有模拟电路元器件、有数字电路元器件等等。

Lin ear Tech no logy Corporati on 的LTspice/SwitcherCAD 是一款免费易用强大无限制的电路图编辑和仿真工具。

有spice netlist导出功能(也可以导出标准spice之外的其他软件的网表格式),方便配合其它仿真工具。

4.2 LTspice 仿真过程首先打开LTspice ,新建一个原理图界面,找到相关的元器件画出二输入与非门的原理图,如图 11所示。

同时,需要设计 PMO 番口 NMO 的相关参数,这里讲 PMOS 口 NMOS 勺长宽都设为0.18卩,如图12、13所示 NMOS 1M2 _,~IM3■ PMOS PMOS图11二输入与非门电路原理图图12 PMOS 参数设定图13 NMOS参数设定接下来新建一个符号界面,对电路原理图进行封装,如图14所示。

这里需要注意符号文件保存的名称要和原理图一致,否则仿真时软件将因为找不到底层文件而不能运行。

图14符号界面封装图最后要给封装好的模块添加信号源。

新建一个原理图,找到封装模型,加入信号源。

设置相关的输入信号,仿真类型为仿真做准备。

如图15所示V2 )PULSEfO 5 0 0 0 1m 4m 3) A VDD F BVS )PULSE(D 5 0 0 0 3m 4m 3)图15仿真原理图完成了以上内容之后就可以进行仿真验证了。

在这里,输入信号A 是一个幅值为5V,周期为4ms,脉冲宽度为1ms 上升时间和下降 时间都为0的方波,如图16所示;输入信号E 是一个幅值为5V, 周期为4 ms 脉冲宽度为3 ms 上升周期和下降周期都为0的方波, 如图17所示。

并对它们选用3个周期进行仿真验证。

b.OV45¥彳43- 3.SV-3.0V-*・胡™.5v -^l.OV0.5V-I°3 i r r~"—T r —""™™r r r n rV1'Fy 5vR se*r™1 .(ran 0 12m 0 OJm图17信号A 波形图图18信号B波形图从中可以看出,虽然上升时间和下降时间以及延时时间都设为了0,但波形还是出现了明显地瑕疵。

点击F之后观察输出信号如图19所示。

图19输出波形图从表1可以知道,与非门只有当输入信号都为1时输出才为0, 其它组合下输出都为0,对比图17,18,19可以发现,仿真得到的结果与理论分析是吻合的。