康华光电子技术基础—数字部分(第五版)课件

- 格式:ppt

- 大小:3.06 MB

- 文档页数:16

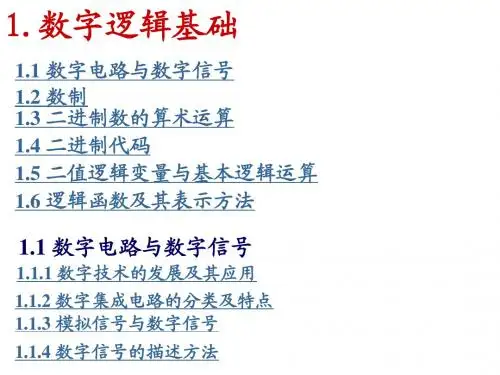

第1章 数字逻辑概论1.1 复习笔记一、模拟信号与数字信号 1.模拟信号和数字信号 (1)模拟信号在时间上连续变化,幅值上也连续取值的物理量称为模拟量,表示模拟量的信号称为模拟信号,处理模拟信号的电子电路称为模拟电路。

(2)数字信号 与模拟量相对应,在一系列离散的时刻取值,取值的大小和每次的增减都是量化单位的整数倍,即时间离散、数值也离散的信号。

表示数字量的信号称为数字信号,工作于数字信号下的电子电路称为数字电路。

(3)模拟量的数字表示①对模拟信号取样,通过取样电路后变成时间离散、幅值连续的取样信号; ②对取样信号进行量化即数字化;③对得到的数字量进行编码,生成用0和1表示的数字信号。

2.数字信号的描述方法(1)二值数字逻辑和逻辑电平在数字电路中,可以用0和1组成的二进制数表示数量的大小,也可以用0和1表示两种不同的逻辑状态。

在电路中,当信号电压在3.5~5 V 范围内表示高电平;在0~1.5 V 范围内表示低电平。

以高、低电平分别表示逻辑1和0两种状态。

(2)数字波形①数字波形的两种类型非归零码:在一个时间拍内用高电平代表1,低电平代表0。

归零码:在一个时间拍内有脉冲代表1,无脉冲代表0。

②周期性和非周期性周期性数字波形常用周期T 和频率f 来描述。

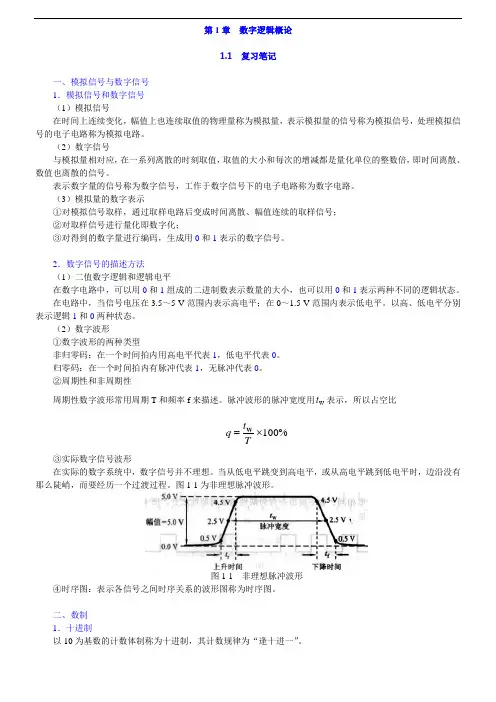

脉冲波形的脉冲宽度用W t 表示,所以占空比100%t q T=⨯W③实际数字信号波形在实际的数字系统中,数字信号并不理想。

当从低电平跳变到高电平,或从高电平跳到低电平时,边沿没有那么陡峭,而要经历一个过渡过程。

图1-1为非理想脉冲波形。

图1-1 非理想脉冲波形④时序图:表示各信号之间时序关系的波形图称为时序图。

二、数制 1.十进制以10为基数的计数体制称为十进制,其计数规律为“逢十进一”。

任意十进制可表示为:()10iDii N K ∞=-∞=⨯∑式中,i K 可以是0~9中任何一个数字。

如果将上式中的10用字母R 代替,则可以得到任意进制数的表达式:()iR ii N K R ∞=-∞=⨯∑2.二进制(1)二进制的表示方法以2为基数的计数体制称为二进制,其只有0和1两个数码,计数规律为“逢二进一”。

第3章逻辑门电路3.1复习笔记一、MOS逻辑门电路1.逻辑电路的一般特性(1)输入和输出的高、低电平数字电路中的高、低电压常用高、低电平来描述,并规定在正逻辑体制中,用逻辑1和0分别表示高、低电平。

当逻辑电路的输入信号在一定范围内变化时,输出电压并不会改变,因此逻辑1和0对应一定的电压范围。

(2)噪声容限噪声容限表示门电路的抗干扰能力。

在数字系统中,各逻辑电路之间的连线可能会受到各种噪声的干扰,这些噪声会叠加在工作信号上,只要其幅度不超过逻辑电平允许的最小值或最大值,则输出逻辑状态不会受影响。

通常将这个最大噪声幅度称为噪声容限。

(3)传输延迟时间传输延迟时间是表征门电路开关速度的参数,它说明门电路在输入脉冲波形的作用下,其输出波形相对于输入波形延迟了多长时间。

(4)功耗①静态功耗当电路的输出没有状态转换时的功耗。

静态时,CMOS电路的电流非常小,使得静态功耗非常低。

②动态功耗CMOS电路在输出发生状态转换时的功耗,它主要由两部分组成:a .由于电路输出状态转换的瞬间,其等效电阻比较小,从而导致有较大的电流从电源VDD 经CMOS 电路流入地;b .由于CMOS 管的负载通常是电容性的,因此当输出由高电平到低电平,或者由低电平到高电平转换时,会对电容进行充、放电,这个过程将增加电路的损耗。

(5)延时-功耗积理想的数字电路或系统,要求它既速度高,同时功耗低。

用符号DP 表示延时-功耗积:pd DDP t P 式中,pd t 为传输延迟时间,D P 为门电路功耗。

DP 值越小,特性越理想。

(6)扇入数和扇出数门电路的扇入数取决于它的输入端的个数。

门电路的扇出数指其在正常工作情况下,所能带同类门电路的最大数目。

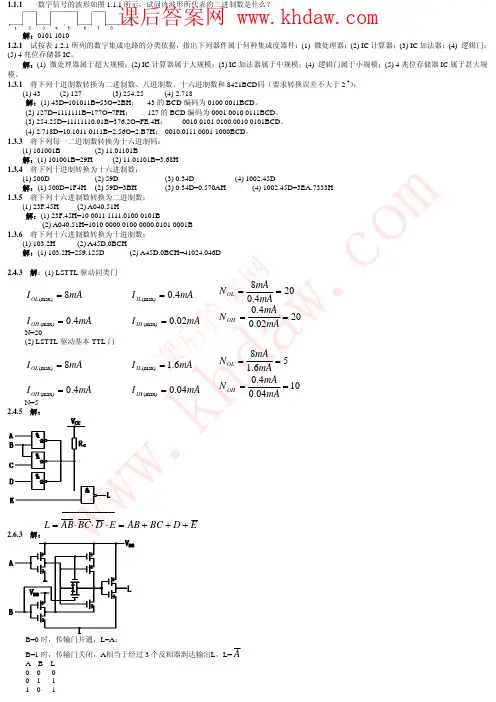

考虑如下两种情况:①拉电流工作情况负载电流从驱动门流向外电路,输出为高电平的扇出数表示:②灌电流工作情况负载电流从外电路流入驱动门,驱动门所能驱动同类门的个数:2.MOS 开关及等效电路(1)MOS 管开关特性图3-1(a )为N 沟道增强型MOS 管构成的开关电路。