L-Edit简明教程

- 格式:ppt

- 大小:4.85 MB

- 文档页数:194

4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR 等网表文件输出,提供模拟或自动布图布线。

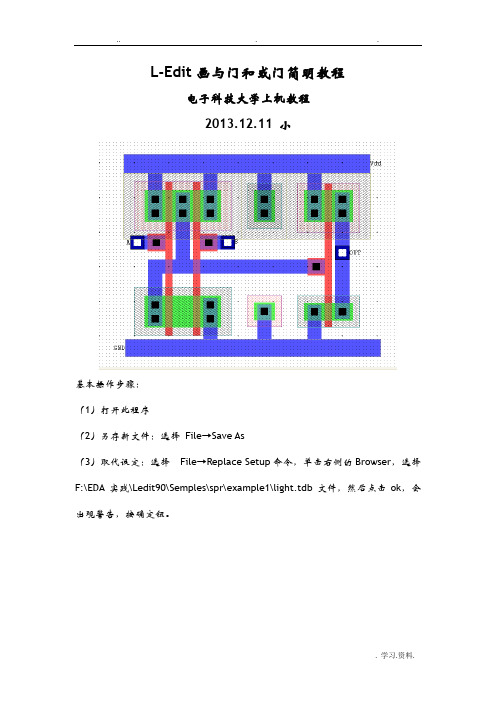

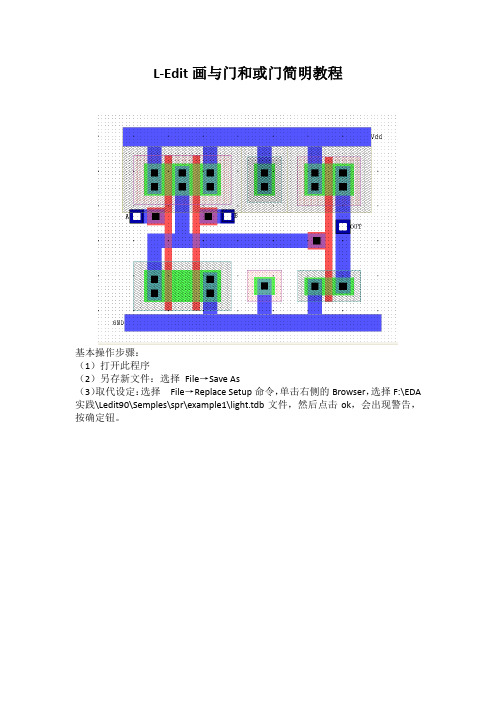

L-Edit画与门和或门简明教程电子科技大学上机教程2013.12.11 小基本操作步骤:(1)打开此程序(2)另存新文件:选择File→Save As(3)取代设定:选择File→Replace Setup命令,单击右侧的Browser,选择F:\EDA实践\Ledit90\Semples\spr\example1\light.tdb文件,然后点击ok,会出现警告,按确定钮。

(4)绘制N Well图层:横向34格,纵向19格绘制图层信息在窗口左下角显示(有图层类型,宽度,长度,坐标等)绘图完成后,通过alt+鼠标左键或者直接用鼠标滚轮来调整图层大小和位置。

Ctrl+鼠标滚轮来调整窗口大小。

home键将图层放置到整个绘图窗口中心位置。

(5)绘制Active图层:横向22格,纵向9格(6)绘制P Select图层:横向28格,纵向14格(7)绘制Poly 图层:据横向2 格,纵向14格完成后进行DRC检查,单击工具栏按钮,或者T ools→DRC,在检查完毕后会出现DRC检查结果,No DRC errors found 说明没有设计规则错误如果有错误,选中Display DRC Error Navigator 复选框,点击OK,会出现错误提示窗口,展开错误标记。

双击Error3,在版图中出现错误提示,这时可以通过alt+鼠标左键来调整图形大小位置来消除DRC错误,最后点击DRC图标,反复修改,直到错误消除,这时绘图窗口将会恢复之前的状态。

(8)绘制Active Contact 图层:横纵2格,然后DRC检查(9)绘制Metal1 图层:纵横4格,DRC检查(最好每步完成后都马上进行DRC 检查,注意,在此之后将不再提示DRC检查,但每步之后最好检查)其中重复的一些操作可以通过复制来完成,该操作通过Ground 来完成。

鼠标拖动选中要复制图形,选择Draw→Ground(或直接Ctrl+G),完成后所选中区域将会变成一个整体,可以对组件进项复制、移动操作。

L-Edit画与门和或门简明教程基本操作步骤:(1)打开此程序(2)另存新文件:选择File→Save As(3)取代设定:选择File→Replace Setup命令,单击右侧的Browser,选择F:\EDA 实践\Ledit90\Semples\spr\example1\light.tdb文件,然后点击ok,会出现警告,按确定钮。

(4)绘制N Well图层:横向34格,纵向19格绘制图层信息在窗口左下角显示(有图层类型,宽度,长度,坐标等)绘图完成后,通过alt+鼠标左键或者直接用鼠标滚轮来调整图层大小和位置。

Ctrl+鼠标滚轮来调整窗口大小。

home键将图层放置到整个绘图窗口中心位置。

(5)绘制Active图层:横向22格,纵向9格(6)绘制P Select图层:横向28格,纵向14格(7)绘制Poly 图层:据横向2 格,纵向14格完成后进行DRC检查,单击工具栏按钮,或者Tools→DRC,在检查完毕后会出现DRC检查结果,No DRC errors found 说明没有设计规则错误如果有错误,选中Display DRC Error Navigator 复选框,点击OK,会出现错误提示窗口,展开错误标记。

双击Error3,在版图中出现错误提示,这时可以通过alt+鼠标左键来调整图形大小位置来消除DRC错误,最后点击DRC图标,反复修改,直到错误消除,这时绘图窗口将会恢复之前的状态。

(8)绘制Active Contact 图层:横纵2格,然后DRC检查(9)绘制Metal1 图层:纵横4格,DRC检查(最好每步完成后都马上进行DRC 检查,注意,在此之后将不再提示DRC检查,但每步之后最好检查)其中重复的一些操作可以通过复制来完成,该操作通过Ground 来完成。

鼠标拖动选中要复制图形,选择Draw→Ground(或直接Ctrl+G),完成后所选中区域将会变成一个整体,可以对组件进项复制、移动操作。

4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件 L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR 等网表文件输出,提供模拟或自动布图布线。