简易信号发生器的设计实现

- 格式:docx

- 大小:957.65 KB

- 文档页数:24

简易函数信号发生器设计报告一、引言信号发生器作为一种测试设备,在工程领域具有重要的应用价值。

它可以产生不同的信号波形,用于测试和调试电子设备。

本设计报告将介绍一个简易的函数信号发生器的设计方案。

二、设计目标本次设计的目标是:设计一个能够产生正弦波、方波和三角波的函数信号发生器,且具有可调节频率和幅度的功能。

同时,为了简化设计和降低成本,我们选择使用数字模拟转换(DAC)芯片来实现信号的输出。

三、设计原理1.信号产生原理正弦波、方波和三角波是常见的函数波形,它们可以通过一系列周期性的振荡信号来产生。

在本设计中,我们选择使用集成电路芯片NE555来产生可调节的方波和三角波,并通过滤波电路将其转换为正弦波。

2.幅度调节原理为了实现信号的幅度调节功能,我们需要使用一个可变电阻,将其与输出信号的放大电路相连。

通过调节可变电阻的阻值,可以改变放大电路的放大倍数,从而改变信号的幅度。

3.频率调节原理为了实现信号的频率调节功能,我们选择使用一个可变电容和一个可变电阻,将其与NE555芯片的外部电路相连。

通过调节可变电容和可变电阻的阻值,可以改变NE555芯片的工作频率,从而改变信号的频率。

四、设计方案1.正弦波产生方案通过NE555芯片产生可调节的方波信号,并通过一个电容和一个电阻的RC滤波电路,将方波转换为正弦波信号。

2.方波产生方案直接使用NE555芯片产生可调节的方波信号即可。

3.三角波产生方案通过两个NE555芯片,一个产生可调节的方波信号,另一个使用一个电容和一个电阻的RC滤波电路,将方波转换为三角波信号。

五、电路图设计设计的电路图如下所示:[在此插入电路图]六、实现效果与测试通过实际搭建电路,并连接相应的调节电位器,我们成功地实现了信号的幅度和频率调节功能。

在不同的调节范围内,我们可以得到稳定、满足要求的正弦波、方波和三角波信号。

七、总结通过本次设计,我们成功地实现了一个简易的函数信号发生器,具有可调节频率和幅度的功能。

《模拟电子技术》简易函数信号发生器的设计与制作1 整机设计1.1 设计任务及要求结合所学的模拟电子技在此处键入公式。

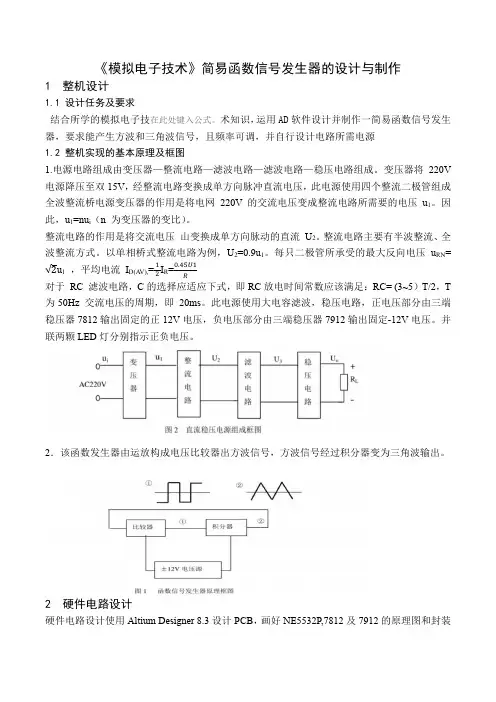

术知识,运用AD软件设计并制作一简易函数信号发生器,要求能产生方波和三角波信号,且频率可调,并自行设计电路所需电源1.2 整机实现的基本原理及框图1.电源电路组成由变压器—整流电路—滤波电路—滤波电路—稳压电路组成。

变压器将220V 电源降压至双15V,经整流电路变换成单方向脉冲直流电压,此电源使用四个整流二极管组成全波整流桥电源变压器的作用是将电网220V 的交流电压变成整流电路所需要的电压u1。

因此,u1=nu i(n 为变压器的变比)。

整流电路的作用是将交流电压山变换成单方向脉动的直流U2。

整流电路主要有半波整流、全波整流方式。

以单相桥式整流电路为例,U2=0.9u1。

每只二极管所承受的最大反向电压u RN= √2u1,平均电流I D(A V),=12I R=0.45U1R对于RC 滤波电路,C的选择应适应下式,即RC放电时间常数应该满足:RC= (3~5)T/2,T 为50Hz 交流电压的周期,即20ms。

此电源使用大电容滤波,稳压电路,正电压部分由三端稳压器7812输出固定的正12V电压,负电压部分由三端稳压器7912输出固定-12V电压。

并联两颗LED灯分别指示正负电压。

2.该函数发生器由运放构成电压比较器出方波信号,方波信号经过积分器变为三角波输出。

2 硬件电路设计硬件电路设计使用Altium Designer 8.3设计PCB,画好NE5532P,7812及7912的原理图和封装后,按照电路图画好原理图后生成PCB图。

合理摆放好各器件后设置规则:各焊盘大小按实际情况设置为了更容易的进行打孔操作,设置偏大一些,正负12V电源线路宽度首选尺寸1.2mm,最小宽度1mm,最大宽度1.2mm,GND线路宽度首选尺寸1mm,最小宽度1mm,最大宽度1.5mm,其他线路首选尺寸0.6mm,最小宽度1mm,最大宽度1.2mm。

基于Multisim的简易信号发生器的设计

随着计算机技术的发展,基于计算机教学的现代教育技术正发挥着越来越重要的作用。

虚拟电路仿真软件Multisim如同一个虚拟的电子实验室,能够方便快捷的进行各种功能电路的分析、设计、改进等。

本文将介绍利用Multisim提供的仿真试验平台进行简易信号发生器的设计过程。

1 简易信号发生器的原理分析

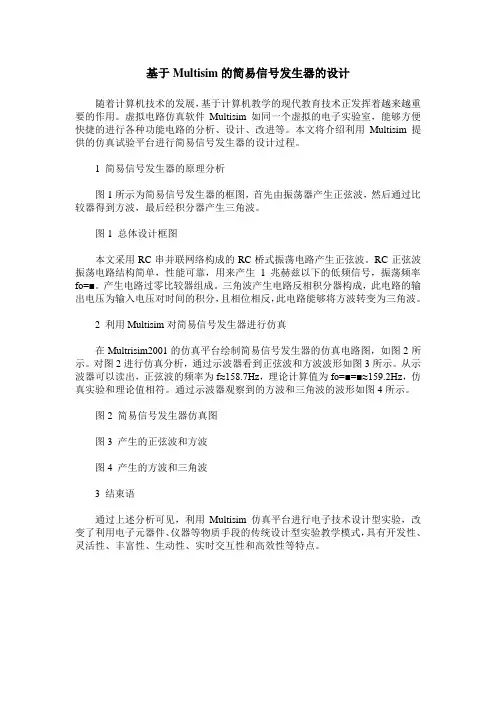

图1所示为简易信号发生器的框图,首先由振荡器产生正弦波,然后通过比较器得到方波,最后经积分器产生三角波。

图1 总体设计框图

本文采用RC串并联网络构成的RC桥式振荡电路产生正弦波。

RC正弦波振荡电路结构简单,性能可靠,用来产生1兆赫兹以下的低频信号,振荡频率fo=■。

产生电路过零比较器组成。

三角波产生电路反相积分器构成,此电路的输出电压为输入电压对时间的积分,且相位相反,此电路能够将方波转变为三角波。

2 利用Multisim对简易信号发生器进行仿真

在Multrisim2001的仿真平台绘制简易信号发生器的仿真电路图,如图2所示。

对图2进行仿真分析,通过示波器看到正弦波和方波波形如图3所示。

从示波器可以读出,正弦波的频率为f≈158.7Hz,理论计算值为fo=■=■≈159.2Hz,仿真实验和理论值相符。

通过示波器观察到的方波和三角波的波形如图4所示。

图2 简易信号发生器仿真图

图3 产生的正弦波和方波

图4 产生的方波和三角波

3 结束语

通过上述分析可见,利用Multisim仿真平台进行电子技术设计型实验,改变了利用电子元器件、仪器等物质手段的传统设计型实验教学模式,具有开发性、灵活性、丰富性、生动性、实时交互性和高效性等特点。

EDA课程设计简易信号发生器的设计实现小组成员:XXXXXXXXXXX专业:XXXXX学院:机电与信息工程学院指导老师:XXXXXX完成日期:XX年XX月XX日目录引言 (3)一、课程设计内容及要求 (3)1、设计内容 (3)2、设计要求 (3)二、设计方案及原理 (3)1、设计原理 (3)2、设计方案 (4)(1)设计思想 (4)(2)设计方案 (4)3、系统设计 (5)(1)正弦波产生模块 (5)(2)三角波产生模块 (6)(3)锯齿波产生模块 (6)(4)方波产生模块 (6)(5)波形选择模块 (6)(6)频率控制模块 (6)(7)幅度控制模块 (6)(8)顶层设计模块 (7)三、仿真结果分析 (7)波形仿真结果 (7)1、正弦波仿真结果 (7)2、三角波仿真结果 (8)3、锯齿波仿真结果 (8)4、方波仿真结果 (8)5、波形选择仿真结果 (9)6、频率控制仿真结果 (9)四、总结与体会 (10)五、参考文献 (10)六、附录 (11)简易信号发生器引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广范的应用。

它能够产生多种波形,如正弦波、三角波、方波、锯齿波等,在电路实验和设备检验中有着十分广范的应用。

本次课程设计采用FPGA来设计多功能信号发生器。

一、课程设计内容及要求1、设计内容设计一个多功能简易信号发生器2、设计要求(1)完成电路板上DAC的匹配电阻选择、焊接与调试,确保其能够正常工作。

(2)根据直接数字频率合成(DDFS)原理设计正弦信号发生器,频率步进1Hz,最高输出频率不限,在波形不产生失真(从输出1KHz正弦转换为输出最高频率正弦时,幅度衰减不得大于10%)的情况下越高越好。

频率字可以由串口设定,也可以由按键控制,数码管上显示频率傎。

(3)可以控制改变输出波形类型,在正弦波、三角波、锯齿波、方波之间切换。

(4)输出波形幅度可调,最小幅度步进为100mV。

二、设计方案及原理1、设计原理(1)简易信号发生器原理图如下2、设计方案(1)设计思想本设计基于VHDL编程,采用模块化电路进行整合。

简易正弦信号发生器设计

一、实验目的

1.进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII和EDA/SOPC试验箱

三、试验内容

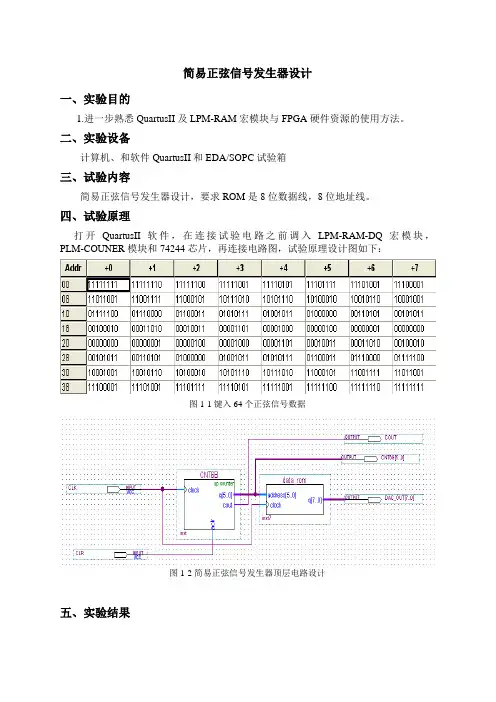

简易正弦信号发生器设计,要求ROM是8位数据线,8位地址线。

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1键入64个正弦信号数据

图1-2简易正弦信号发生器顶层电路设计

五、实验结果

试验结果如下图:

图1-3综合后的RLT图

图1-4仿真波形图3.引脚锁定方案图

图1-5引脚锁定方案图

图1-6编程下载模式图

六、试验小节

一学期匆匆而过,通过大半学期的学习,我们学到了很多处理问题的技巧。

不过我们还要熟记很多单词,大多数的单词我们还不认识,相信通过进一步的学习,我们一定能学好这个软件。

我们也将以浓厚的兴趣和积极的态度去学习。

相信我们一定会有更加长足的进步。

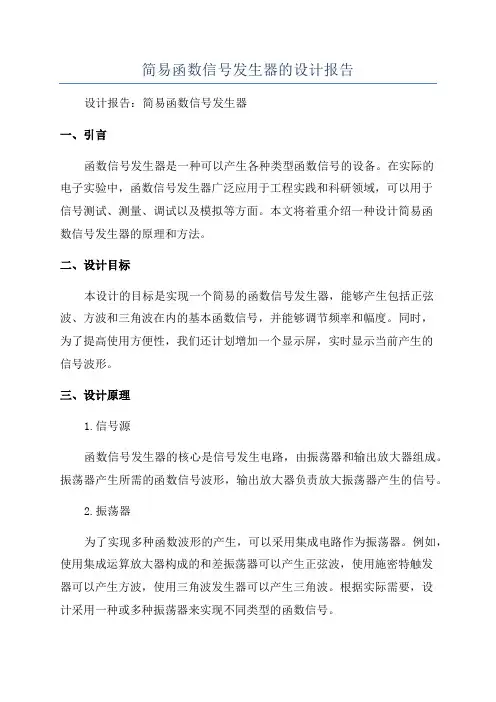

简易函数信号发生器的设计报告设计报告:简易函数信号发生器一、引言函数信号发生器是一种可以产生各种类型函数信号的设备。

在实际的电子实验中,函数信号发生器广泛应用于工程实践和科研领域,可以用于信号测试、测量、调试以及模拟等方面。

本文将着重介绍一种设计简易函数信号发生器的原理和方法。

二、设计目标本设计的目标是实现一个简易的函数信号发生器,能够产生包括正弦波、方波和三角波在内的基本函数信号,并能够调节频率和幅度。

同时,为了提高使用方便性,我们还计划增加一个显示屏,实时显示当前产生的信号波形。

三、设计原理1.信号源函数信号发生器的核心是信号发生电路,由振荡器和输出放大器组成。

振荡器产生所需的函数信号波形,输出放大器负责放大振荡器产生的信号。

2.振荡器为了实现多种函数波形的产生,可以采用集成电路作为振荡器。

例如,使用集成运算放大器构成的和差振荡器可以产生正弦波,使用施密特触发器可以产生方波,使用三角波发生器可以产生三角波。

根据实际需要,设计采用一种或多种振荡器来实现不同类型的函数信号。

3.输出放大器输出放大器负责将振荡器产生的信号放大到适当的电平以输出。

放大器的设计需要考虑到信号的频率范围和幅度调节的灵活性。

4.频率控制为了能够调节信号的频率,可以采用可变电容二极管或可变电阻等元件来实现。

通过调节这些元件的参数,可以改变振荡器中的RC时间常数或LC谐振电路的频率,从而实现频率的调节。

5.幅度控制为了能够调节信号的幅度,可以采用可变电阻作为放大电路的输入阻抗,通过调节电阻阻值来改变信号的幅度。

同时,也可以通过增加放大倍数或使用可变增益放大器来实现幅度的控制。

四、设计步骤1.确定电路结构和信号发生器的类型。

根据功能和性能需求,选择合适的振荡器和放大器电路,并将其组合在一起。

2.根据所选振荡器电路进行参数计算和元件的选择。

例如,根据需要的频率范围选择适合的振荡器电路和元件,并计算所需元件的数值。

3.设计输出放大器电路。

![毕业设计(论文)-简易信号发生器的设计[管理资料]](https://uimg.taocdn.com/b8c654297f1922791788e8cb.webp)

简易信号发生器的设计目录摘要Abstract第1章前言 (3)第2章信号发生器的发展现状 (4) (4) (4)第3章方案的设计 (5)方案的选择 (5) (5)第4章单元电路设计 (6) (6) (6)正弦波振荡电路 (7)电路工作原理 (7) (9)电压比较器 (10) (10) (11)积分电路 (12) (12) (12)第5章整体电路仿真 (14) (14) (15)第6章结束语 (17)参考文献答谢词附录摘要信号发生器是一种能够产生多种波形,如三角波、方波、正弦波的电路。

信号发生器在电路实验和设备检测中具有十分广泛的用途。

本设计通过对信号发生器的原理以及构成进行分析,设计了正弦波—方波—三角波简易信号发生器。

设计中首先确定了电路方案:由直流稳压电源电路、文氏振荡器、迟滞比较器、积分器组成;接着对各单元电路的的工作原理进行了分析,由直流稳压电源电路提供所需电压,文氏振荡器产生正弦波,迟滞比较器产生方波,积分器产生三角波,同时对电路中各元器件的参数进行了计算。

最后利用相关仪器进行测试,测试达到了设计要求。

关键词:直流稳压电源电路;文氏振荡器;迟滞比较器;积分器AbstractSignal generator is a kind of can produce much waveform, such as triangle wave, square wave, sine wave circuit. Signal generator in the circuit experiment and test equipment in a very wide range of purposes. The design of the principle of the signal generator and structure analysis, design of sine wave-square wave-triangle wave simple signal generator. Design of the first set by a dc voltage circuit scheme: power supply circuit, venturi oscillator,hysteresit comparator, integrator composed; Then each unit circuit of the principle is analyzed by dc stabilized voltage power supply circuit, provide the voltage required, venturi oscillator produce sine wave, hysteresit comparator produce square wave, integrators produce triangle, and at the same time in the circuit to wave the parameters of each component was calculated. Finally, using the related instrument testing, testing meet the design requirements.Keywords: dc stabilized voltage power supply circuit; Venturi oscillator; Hysteresit comparator; integrator第1章前言能产生多种波形,如三角波、方波、正弦波的电路被称为信号发生器,又称信号源或振荡器,在生产实践和科技领域中有广泛的应用。

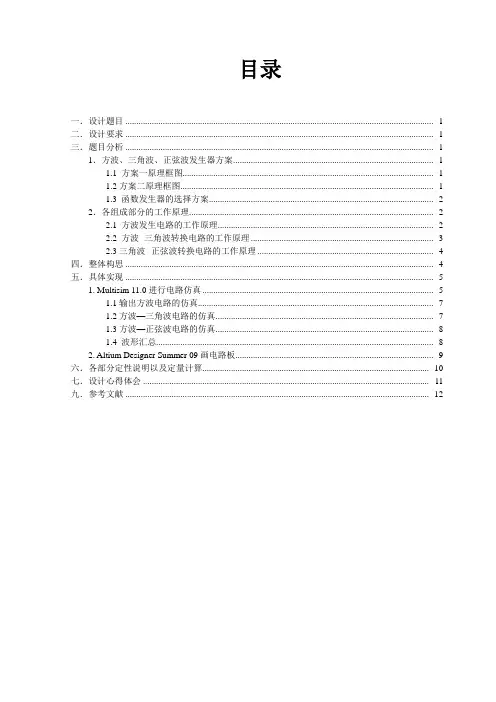

目录一.设计题目 ............................................................................................................................................ - 1 -二.设计要求 ............................................................................................................................................ - 1 -三.题目分析 ............................................................................................................................................ - 1 -1.方波、三角波、正弦波发生器方案........................................................................................... - 1 -1.1 方案一原理框图.................................................................................................................. - 1 -1.2方案二原理框图................................................................................................................... - 1 -1.3 函数发生器的选择方案...................................................................................................... - 2 -2.各组成部分的工作原理............................................................................................................... - 2 -2.1 方波发生电路的工作原理.................................................................................................. - 2 -2.2 方波--三角波转换电路的工作原理 ................................................................................... - 3 -2.3三角波--正弦波转换电路的工作原理 ................................................................................ - 4 -四.整体构思 ............................................................................................................................................ - 4 -五.具体实现 ............................................................................................................................................ - 5 -1. Multisim 11.0进行电路仿真 ......................................................................................................... - 5 -1.1输出方波电路的仿真........................................................................................................... - 7 -1.2方波—三角波电路的仿真................................................................................................... - 7 -1.3方波—正弦波电路的仿真................................................................................................... - 8 -1.4 波形汇总.............................................................................................................................. - 8 -2. Altium Designer Summer 09画电路板.......................................................................................... - 9 -六.各部分定性说明以及定量计算....................................................................................................... - 10 -七.设计心得体会 .................................................................................................................................. - 11 -九.参考文献 .......................................................................................................................................... - 12 -一.设计题目:信号发生器二.设计要求:可以产生正弦波、三角波和方波;输出频率和幅度可以在一定范围内连续可调;频率稳定度较高。

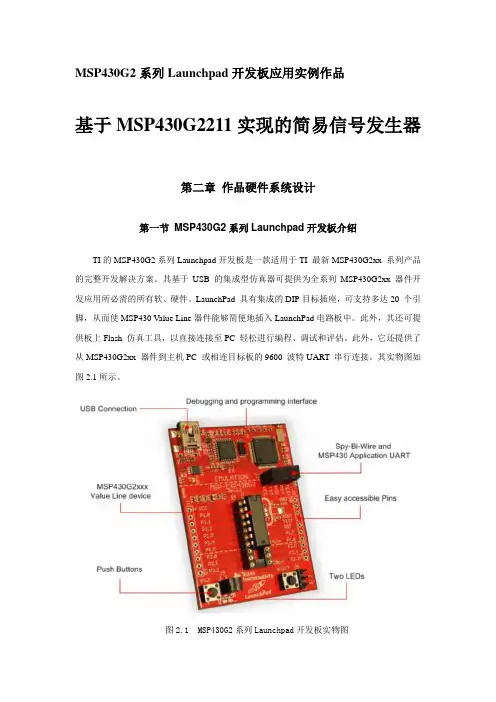

MSP430G2系列Launchpad开发板应用实例作品基于MSP430G2211实现的简易信号发生器第二章作品硬件系统设计第一节MSP430G2系列Launchpad开发板介绍TI的MSP430G2系列Launchpad开发板是一款适用于TI 最新MSP430G2xx 系列产品的完整开发解决方案。

其基于USB 的集成型仿真器可提供为全系列MSP430G2xx 器件开发应用所必需的所有软、硬件。

LaunchPad 具有集成的DIP目标插座,可支持多达20 个引脚,从而使MSP430 Value Line器件能够简便地插入LaunchPad电路板中。

此外,其还可提供板上Flash 仿真工具,以直接连接至PC 轻松进行编程、调试和评估。

此外,它还提供了从MSP430G2xx 器件到主机PC 或相连目标板的9600 波特UART 串行连接。

其实物图如图2.1所示。

图2.1 MSP430G2系列Launchpad开发板实物图MSP430G2系列Launchpad开发板的特性:●USB 调试与编程接口无需驱动即可安装使用,且具备高达9600 波特的UART 串行通信速度●支持所有采用PDIP14 或PDIP20 封装的MSP430G2xx 和MSP430F20xx 器件●分别连接至绿光和红光LED 的两个通用数字I/O 引脚可提供视觉反馈●两个按钮可实现用户反馈和芯片复位●器件引脚可通过插座引出,既可以方便的用于调试,也可用来添加定制的扩展板●高质量的20引脚DIP插座,可轻松简便地插入目标器件或将其移除本作品中所使用的MSP430G2211单片机的资源和功能:◆16位RISC指令集处理器◆128字节RAM(数据)+2K字节Flash存储器(代码)◆一个16位TA定时器◆内置数控振荡器(DCO),最高频率可达21MHz◆9个双向I/O口,每个I/O口都可以作为中断源◆自带BOR检测电路,能自动避开上电瞬间的毛刺并产生可靠的复位信号◆内置低功耗低频振荡器(VLO)◆可通过软件配置的8通道比较器第二节方案论证、比较与选择方案一:控制部分由MSP430G2211实现,波形产生采用低温漂、低失真、高线性单片压控函数发生器(如ICL8038、MAX038等)。

什么是信号发生器如何设计一个简单的信号发生器电路什么是信号发生器如何设计一个简单的信号发生器电路信号发生器是一种电子测试仪器,用于产生不同频率、不同波形的信号。

它被广泛应用于各种电子设备的测试、调试以及科学研究中。

本文将介绍信号发生器的基本原理以及如何设计一个简单的信号发生器电路。

一、信号发生器的基本原理信号发生器的基本原理是通过电路产生稳定的、可调节的频率和振幅的信号。

主要包括以下几个方面:1. 振荡器:信号发生器的核心部件是振荡器。

振荡器通过负反馈回路将部分输出信号重新输入到输入端,以维持振荡的稳定性。

2. 频率控制电路:用于调节信号的频率大小。

通常采用可变电容或可变电感等元件来实现频率的调节。

3. 幅度控制电路:用于调节信号的振幅大小。

通常采用可变电阻或放大器等元件来实现幅度的调节。

4. 输出电路:用于将振荡器产生的信号输出到外部设备,如示波器、信号分析仪等。

二、设计一个简单的信号发生器电路设计一个简单的信号发生器电路需要考虑以下几个基本要素:1. 振荡器电路:选择适合的振荡器电路,如RC振荡器、LC振荡器等。

以RC振荡器为例,可选用一个电容和一个电阻来构成振荡器电路。

2. 频率控制电路:采用可变电容电路来实现对频率的调节。

可选用一个可变电容与振荡器电路相结合,通过调节电容值,达到对频率的调节。

3. 幅度控制电路:采用可变电阻电路来实现对振幅的调节。

可选用一个可变电阻与振荡器电路相连,通过调节电阻值,达到对振幅的调节。

4. 输出电路:将振荡器产生的信号经过放大器放大后输出。

该放大器可以选择运算放大器、晶体管放大器等。

设计步骤:1. 确定电路的工作电压和功率需求,并选择适合的供电电源。

2. 根据振荡器的选择,选取合适的电容和电阻,并连接成振荡器电路。

3. 在振荡器电路中加入可变电容电路,用于频率的调节。

4. 将振荡器电路与可变电容电路连接到幅度控制电路中的可变电阻上,用于振幅的调节。

5. 添加输出电路,将振荡器产生的信号经过放大器放大后输出到外部设备。

如何设计简单的信号发生器电路设计简单的信号发生器电路是电子爱好者入门必备的技能之一。

信号发生器电路可以产生各种波形信号,用于测试电路的响应、频率特性和波形形状,是电子电路设计、修理和教学的基础设备。

本文将介绍如何设计一个简单的信号发生器电路,帮助读者快速入门。

1. 选取信号发生器电路的基本类型信号发生器电路的基本类型有多种,包括函数发生器、脉冲发生器、正弦波发生器等。

根据需求选取合适的基本类型是设计信号发生器电路的第一步。

2. 准备所需元件和工具设计信号发生器电路需要准备一些基本的元件和工具,包括集成电路、电容、电阻、电感、开关等。

此外,还需要一个电路板、焊接设备、测试仪器等。

3. 绘制电路原理图在设计信号发生器电路之前,先用电路设计软件或者手绘图纸绘制电路原理图。

原理图是电路设计的蓝图,能直观地展示电路的连接关系和元件的型号和参数。

4. 确定电路工作电压和频率范围根据设计需求,确定信号发生器电路的工作电压和频率范围。

不同类型的信号发生器电路有不同的工作电压和频率范围要求,需要注意选取合适的元件来满足要求。

5. 进行电路布局设计根据电路原理图,进行电路布局设计。

合理的电路布局能够降低电路噪音、干扰和交叉干扰,提高电路性能和稳定性。

将元件按照一定的规律排列,避免元件之间产生干扰。

6. 进行电路连接和焊接根据电路布局,进行电路连接和焊接。

在焊接过程中,需要注意焊接时间和温度,避免对元件造成损害。

焊接完成后,使用万用表测试电路的连接是否正确。

7. 进行电路调试和测试将电路连接到电源,进行电路调试和测试。

检查电路的工作状态和波形输出是否符合设计要求。

如有问题,及时调整元件参数或者电路连接,直到信号发生器电路工作正常。

8. 对信号发生器电路进行保护和优化为了保护信号发生器电路的稳定性和寿命,可以增加保护电路和滤波电路。

保护电路可以避免电源反接、过流和过压等情况对电路造成损害。

滤波电路可以降低电路的噪音和杂散频率,提高输出信号的纯净性。

1 绪论简易多功能信号发生器是信号发生器的一种,在生产实践和科研领域中有着广泛的应使用。

在研制、生产、测试和维修各种电子元件、部件以及整机设备时,都需要有信号源,由它产生不同频率不同波形的电压、电流信号并加到被测器件或设备上,使用其他仪器观察、测量被测仪器的输出响应,以分析确定它们的性能参数。

信号发生器是电子测量领域中最基本、应使用最广泛的一类电子仪器。

它可以产生多种波形信号,如正弦波,三角波,方波和锯齿波等,因而广泛使用于通信、雷达、导航、宇航等领域。

在本设计中它能够产生多种波形,如正弦波,三角波,方波和锯齿波等,并能实现对各种波频率和幅度的改变。

正因为其在生活中应使用的重要性,人们它做了大量的研究,总结出了许多实现方式。

可以基于FPGA 、VHDL、单片机、DOS 技能、数字电路等多种方法实现。

本设计是采使用VHDL来实现的简易多功能信号发生器。

它能产生正弦波,三角波,方波和锯齿波。

且对各种波形的要求如下:(1)根据按键选择不同的波形(实现正弦波,三角波,方波和锯齿波);(2)各波形的频率范围为100Hz-20KHz;(3)各波形频率可调(通过按键控制频率的变化,步进值为500Hz);(4)使使用LED数码管实时显示输出信号波形的频率值;(5)使用按键控制实现输出信号的幅度调节(幅度调节为2.5V和5V)。

2 EDA技术介绍2.1EDA介绍EDA是电子设计自动化(Electronic Design AutoMation)缩写。

EDA技术是以计算机为工具,根据硬件描述语言HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简、分割、综合及优化、布局布线、仿真以及对于特定目标芯片的适配编译和编程下载等工作。

硬件描述语言HDL 是相对于一般的计算机软件语言,如:C、PASCAL而言的。

HDL语言使使用与设计硬件电子系统的计算机语言,它能描述电子系统的逻辑功能、电路结构和连接方式。

应用设计:嵌入式系统 Applications简易信号发生器设计及 PLC 实现哈尔滨理工大学 王华林 王鹏 于舒春电子科技大学中山学院 于效宇 刘艳信号发生器又称为信号源或振荡器,在航空航天、电子、通信等诸多领域有着广泛应用。

信号发生器主要给被测电路提供所需要的已知信号(各种波形),然后用其他仪表测量感兴趣的参数。

常见的信号发生器可以产生方波、锯齿波、三角波、正余弦波等标准波形。

从设计角度出发,信号发生器分为模拟式和数字合成式两种。

数字合成式信号发生器无论频率、幅度乃至信号的信噪比均优于模拟式,不仅频率精准,而且相位抖动及频率漂移均能达到相当稳定的状态。

设计信号发生器通常采用分立元件或单片集成芯片,其稳定性和灵活性较差且不易调试。

P L C(P r o g r a m m a b l e L o g i c C o n t r o l l e r,可编程逻辑控制器)是一种在众多领域广泛应用的数字控制器,具有可靠性高、功能强大、使用灵活等诸多优点。

采用P L C设计信号发生器可以免去复杂电子线路的设计,通过编程来产生数字信号,再配以专用的模拟量转换模块即可输出需要的模拟信号。

在不改变硬件的前提下,可通过编程灵活设定产生信号的幅值和频率。

本文设计开发了由P L C实现的简易信号发生器,实验证明可提供稳定可靠的输出波形,且可方便地更新配置,操作灵活。

系统组成本文以西门子公司的S7-200系列P L C中的C P U 222模块为核心,配合E M232模拟量扩展模块,实现了一简易信号发生器。

系统框图如图1所示。

E M232配有4路模拟量输出,提供D/A转换通道。

其输出有电压和电流两种模式,电压信号输出量程为±10V,电流信号输出量程为0~20m A。

本文采用电压输出方式,其对应的数字范围为:-32000~+32000。

分辨率为12位(其中1位符号位),精度为满量程的±0.5%。

模拟量输出的电压建立时间为100μs。

模拟电子技术研究性学习论文基于LM324的简易函数发生器的设计学院:电子信息工程学院专业:通信工程学生姓名:学号:指导教师:白双2014 年06 月03 日中文摘要信号发生器广泛应用于电子工程、通信工程、自动控制、遥测控制、测量仪器、仪表和计算机等技术领域。

本文设计了以运算放大器LM324为核心器件的一个能产生正弦波、矩形波、三角波的简易低频信号发生器。

通过对电路分析,确定了元器件的参数,并利用Multisim软件仿真电路的理想输出结果。

关键词:信号发生器、RC桥式振荡电路、运算放大器AbstractSignal generator is widely used in measurement, communication, auto-control and other electric fields. This paper using operational amplifier LM324 as core device to design a simple low-frequency signal generator, which can generate sine, square, triangular. The parameters of the circuit are tested and recognized. Multisim software simulates the output of the three waves.Keywords:signal generator, RC bridge oscillator circuit, operational amplifier目录第一章引言 (3)第二章原理分析 (3)2.1RC振荡电路 (3)2.2过零比较器 (4)2.3积分运算电路 (5)2.4LM324运算放大器 (5)第三章电路设计 (7)3.1正弦波发生模块 (7)3.2矩形波发生模块 (7)3.3三角波发生模块 (8)第四章电路的仿真与调试 (8)第五章总结 (10)参考文献 (11)第一章引言信号发生器是指产生所需参数的电测试信号的仪器。

《模拟电子技术》简易函数信号发生器的设计与制作1、整机设计1.1 设计任务及要求结合所学的模拟电子技术知识,需要设计一个简易的函数信号发生器,要求能产生方波和三角波信号,并且其频率可以调节,并自行设计电路所需电源电路。

1.2 整机实现的基本原理及框图1.函数信号发生器能自动产生正弦波、三角波、方波及锯齿波、阶梯波等电压波形。

其电路中使用的器件可以是分立器件,也可以是集成电路。

本课题需要完成一个能产生方波、三角波的简易函数信号发生器。

产生方波、三角波的方案有很多种,本课题采用运放构成电压比较器出方波信号,采用积分器将方波变为三角波输出,其原理框图如图1所示。

2、直流电源电路一般由“降压——整流——滤波——稳压”这四个环节构成。

基本组成框图如图2所示。

2、硬件电路设计在硬件电路的设计过程中,需要首先知道简易信号发生器的原理,在其基本原理与结构框图中,知道需要比较器与积分器的电路,所以在设计过程中需要实现用积分器将方波变为三角波。

根据在课堂所学的积分器放大电路设计出所需的积分器电路与比较器电路。

根据设计的电路图在洞洞板上进行布局,最后根据各个元器件之间的联系进行焊接。

器件选择(1)变压器将220V交流电压变成整流电路所需要的电压u1。

本次我们选用了双15V变压器(2)整流电路将交流电压u1转换成单方向脉动的直流u2,有半波整流、全波整流,可以利用整流二极管构成整流桥堆来实现。

建议用二极管搭建全波整流电路实现。

本次使用了IN5399二极管(4个)。

(3)滤波电路将脉动直流电压u2滤除纹波,变成纹波较小的u3,有RC滤波电路、LC滤波电路等。

建议采用大电容滤波。

本次使用了2200uF/25V电容(2个)。

(4)稳压器常用集成稳压器有固定式三端稳压器和可调式三端稳压器。

下面是其中一些典型应用及选择原则。

固定式三端稳压器的常见产品有:78XX 系列稳压器输出固定的正电压,如7805输出为+5V;79XX系列稳压器输出固定的负电压,如7905输出为-5V。

EDA课程设计简易信号发生器的设计实现小组成员:XXXXXXXXXXX专业:XXXXX学院:机电与信息工程学院指导老师:XXXXXX完成日期:XX年XX月XX日目录引言 (3)一、课程设计内容及要求 (3)1、设计内容 (3)2、设计要求 (3)二、设计方案及原理 (3)1、设计原理 (3)2、设计方案 (4)(1)设计思想 (4)(2)设计方案 (4)3、系统设计 (5)(1)正弦波产生模块 (5)(2)三角波产生模块 (6)(3)锯齿波产生模块 (6)(4)方波产生模块 (6)(5)波形选择模块 (6)(6)频率控制模块 (6)(7)幅度控制模块 (6)(8)顶层设计模块 (7)三、仿真结果分析 (7)波形仿真结果 (7)1、正弦波仿真结果 (7)2、三角波仿真结果 (8)3、锯齿波仿真结果 (8)4、方波仿真结果 (8)5、波形选择仿真结果 (9)6、频率控制仿真结果 (9)四、总结与体会 (10)五、参考文献 (10)六、附录 (11)简易信号发生器引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广范的应用。

它能够产生多种波形,如正弦波、三角波、方波、锯齿波等,在电路实验和设备检验中有着十分广范的应用。

本次课程设计采用FPGA来设计多功能信号发生器。

一、课程设计内容及要求1、设计内容设计一个多功能简易信号发生器2、设计要求(1)完成电路板上DAC的匹配电阻选择、焊接与调试,确保其能够正常工作。

(2)根据直接数字频率合成(DDFS)原理设计正弦信号发生器,频率步进1Hz,最高输出频率不限,在波形不产生失真(从输出1KHz正弦转换为输出最高频率正弦时,幅度衰减不得大于10%)的情况下越高越好。

频率字可以由串口设定,也可以由按键控制,数码管上显示频率傎。

(3)可以控制改变输出波形类型,在正弦波、三角波、锯齿波、方波之间切换。

(4)输出波形幅度可调,最小幅度步进为100mV。

二、设计方案及原理1、设计原理(1)简易信号发生器原理图如下2、设计方案(1)设计思想本设计基于VHDL编程,采用模块化电路进行整合。

系统各模块所需工作时钟信号由输入系统时钟信号经分频后得到,系统时钟输入端应满足输入脉冲信号的要求。

组合波形信号经显示模块输出。

具备幅度和频率可调功能,幅度可通过电位器调整,频率控制模块则是一个简易的计数器,控制步径为100HZ的可调频率,最终送至脉冲发生模块输出脉冲信号,达到设计课题所要求的输出波形频率可调及幅度可调功能。

幅度可调功能由于比较简单,可以在FPGA外部利用硬件电路实现。

(2)设计方案采用DDS(直接数字频率合成器)来设计,设计总体框图如图2所示。

DDS器件采用高速数字电路和高速D/A 转换技术,具有频率转换时间短、频率分辨率高、频率稳定度高、输出信号频率和相位可快速程控切换等优点,所以,我们可以利用DDS具有很好的相位控制和幅度控制功能,另外其数据采样功能也是极具精确和完善的,它可以产生较为精确的任何有规则波形信号,可以实现对信号进行全数字式调制。

用FPGA和DDS实现信号调制,既克服了传统的方法实现带来的缺点,若采用它来编程设计,必定会事半功倍,且使设计趋于理想状态。

DDS的主要参数间的关系如下:频率分辨率=系统时钟频率/2^12;频率控制字(FTW)=f*2^12/T;图2 DDS系统结构框图3、系统设计(1)正弦波产生模块正弦波产生模块由相位累加器和查找表组成,相位累加器用于实现相位的累加并存储其累加结果;查找表由ROM生成,其存储的数据是每一个相位所对应的二进制数字正弦幅傎,在每一个时钟周期内,相位累加器输出序列的高n位对其进行寻址,最后输出为该相位对应的二进制正弦幅傎序列。

ROM及查找表为如下ROM为:查找表为:(2)三角波产生模块(3)锯齿波产生模块(4)方波产生模块以上几个波形的产生也是基于ROM查找表,ROM的六位地址为输入端,输出端是八位,到时钟脉冲的上升沿到来时依次从地址中读出数据,得到相应的波形。

(5)波形选择模块这一模块主要原理是根据一个四选一多路选择器来选择输出四种不同的波形,然后通过一个按键对波形进行循环选择,按下确认按钮后进行波形的调用。

(6)频率控制模块本模块要求频率步进1Hz,最高输出频率不限,在本设计中由20MHz的信号源经分频后得到,根据用户需要的频率,通过编程把频率控制数值传送给各个模块,从而实现频率的控制。

(7)幅度控制模块本模块要求输出波形幅度可调,在0-3.3V之间变动,最小幅度步进100mV。

通过一个乘法电路和一个除法电路实现。

(8)顶层设计模块三、仿真结果及分析1、正弦波仿真波形分析:clk :输入的时钟信号;dout :上升沿到来时,输出正弦波取样点的数值;示波器显示为2、三角波仿真波形分析:Clk :输入的时钟信号;Dout:上升沿到来时,输出三角波的取样值;示波器显示为3、锯齿波仿真波形分析:clk: 输入的时钟信号;dout: 上升沿到来时,输出锯齿波的取样值;示波器显示为4、方波仿真波形分析:clk:输入的时钟信号;dout: 上升沿到来时,输出方波的取样值;示波器显示为5、波形选择仿真波形分析:reset:复位键,可使系统恢复初始状态;a:按键的次数,累加循环;d1:输入对应的是正弦波,可连接到正弦波输出端;d2:输入对应的是方波,可连接到方波输出端;d3:输入对应的是锯齿波,可连接到锯齿波输出端;d4:输入对应的是三角波,可连接到三角波输出端;q:输出选择后的波形;6、频率控制(分频)仿真波形分析:ffclk:晶振的频率;cp:分频后的频率;四、总结及体会通过此次课程设计,让我们深切的体会到自己所学知识的浅薄。

众所周知,EDA技术正在成为现代电子设计技术的核心,利用EDA技术进行电路设计已经成为不可阻挡的趋势。

本设计使用了基于Alter 公司的FPGA系列,采用由Alter公司提供的系统开发工具QuartusⅡ软件进行系统的设计和仿真。

数字信号发生器在实验及工业场所都有着重要的应用,本次实验设计的能够输出四种波形的简易多功能信号发生器,其仿真结果表明本次设计是正确有效的,但由于设计者能力有限,本次设计仍有许多值得改进的地方。

在设计过程当中,遇到了软件操作不熟练,程序编写不规范等诸多问题,通过对问题的总结分析得出,应用软件的主要功能必须熟练操作,才能提高工作效率,需要规范操作的地方必须严格按照使用说明操作,避免由于软件使用不当造成的错误产生。

程序的编写格式必须规范,模块、端口以及信号变量的命名应当反映实际意义,缩进格式工整明了,方便阅读理解,这样有利于程序的编写,有利于分析调试,也有利于程序的重复使用。

总的来说,在这次课程设计过程中我们学到了很多,既复习了以前学过的QuartusⅡ软件,算是对以前学过知识的查缺补漏,又锻炼了我们遇到问题、分析并解决问题的能力,能够有针对性地查找资料,然后加以吸收利用,以提高自己的应用能力,而且还能增长自己见识,补充最新的专业知识。

相信通过此次设计的锻炼,我们对专业知识和技能的掌握将更加牢靠,在今后的工作和学习中,必将使我们受益匪浅,取得应有的优势。

五、参考文献[1]潘松、黄继业,EDA技术实用教程[M],北京:科学出版社,2010.05,338-344.[2]黄仁欣,EDA技术实用教程[M],北京:清华大学出版社,2006.09,199-200.[3]蒋小燕、俞伟钧,EDA技术及VHDL[M],南京:东南大学出版社,2008.12,230-236.六、附录1、正弦波程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned;entity singt isport(clk:in std_logic;dout:out integer range 255 downto 0);end;architecture dacc of singt issignal q :integer range 63 downto 0;signal d :integer range 255 downto 0;signal d1:integer range 255 downto 0;beginprocess(clk)beginif clk'event and clk='1' thenif q<63 then q<=q+1;else q<=0;end if; end if;end process;process(q)begincase q iswhen 00=> d<=255;when 01=> d<=254;when 02=> d<=252;when 03=> d<=249;when 04=> d<=245;when 05=> d<=239;when 06=> d<=233;when 07=> d<=225;when 08=> d<=217;when 09=> d<=207;when 10=> d<=197;when 11=> d<=186;when 12=> d<=174;when 13=> d<=162;when 14=> d<=150;when 15=> d<=137;when 16=> d<=124;when 17=> d<=112;when 18=> d<=99;when 19=> d<=87;when 20=> d<=75;when 21=> d<=64;when 22=> d<=53;when 23=> d<=43;when 24=> d<=34;when 25=> d<=26;when 26=> d<=19;when 27=> d<=3;when 28=> d<=8;when 29=> d<=4;when 30=> d<=1;when 31=> d<=0;when 32=> d<=0;when 33=> d<=1;when 34=> d<=4;when 35=> d<=8;when 36=> d<=03;when 37=> d<=19;when 38=> d<=26;when 39=> d<=34;when 40=> d<=43;when 41=> d<=53;when 42=> d<=64;when 43=> d<=75;when 44=> d<=87;when 45=> d<=99;when 46=> d<=112;when 47=> d<=124;when 48=> d<=137;when 49=> d<=150;when 50=> d<=162;when 51=> d<=174;when 52=> d<=186;when 53=> d<=197;when 54=> d<=207;when 55=>when 56=> d<=225;when 57=> d<=233;when 58=> d<=239;when 59=> d<=245;when 60=> d<=249;when 61=> d<=252;when 62=> d<=254;when 63=> d<=255;when others=>null;end case;if clk'event and clk='1' then d1<=d; end if;end process;dout<=d1;end;2、三角波程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned;entity sanjiaogt isport(clk:in std_logic;dout:out integer range 255 downto 0);end;architecture dacc of sanjiaogt issignal q :integer range 63 downto 0;signal d :integer range 255 downto 0;signal d1:integer range 255 downto 0;beginprocess(clk)beginif clk'event and clk='1' thenif q<63 then q<=q+1;else q<=0;end if; end if;end process;process(q)begincase q iswhen 00=> d<=0;when 01=> d<=4;when 02=> d<=8;when 03=> d<=12;when 04=> d<=16;when 05=> d<=20;when 06=> d<=24;when 07=> d<=28;when 08=> d<=32;when 09=> d<=36;when 10=> d<=40;when 11=> d<=44;when 12=> d<=48;when 13=> d<=52;when 14=> d<=56;when 15=> d<=60;when 16=> d<=64;when 17=> d<=68;when 18=> d<=72;when 19=> d<=76;when 20=> d<=80;when 21=> d<=84;when 22=> d<=88;when 23=> d<=92;when 24=> d<=96;when 25=> d<=100;when 26=> d<=104;when 27=> d<=108;when 28=> d<=112;when 29=> d<=116;when 30=> d<=120;when 31=> d<=124;when 32=> d<=124;when 33=> d<=120;when 34=> d<=116;when 35=>when 36=> d<=108;when 37=> d<=104;when 38=> d<=100;when 39=> d<=96;when 40=> d<=92;when 41=> d<=88;when 42=> d<=84;when 43=> d<=80;when 44=> d<=76;when 45=> d<=72;when 46=> d<=68;when 47=> d<=64;when 48=> d<=60;when 49=> d<=56;when 50=> d<=52;when 51=> d<=48;when 52=> d<=44;when 53=> d<=40;when 54=> d<=36;when 55=> d<=32;when 56=> d<=28;when 57=> d<=24;when 58=> d<=20;when 59=> d<=16;when 60=> d<=12;when 61=> d<=8;when 62=> d<=4;when 63=> d<=0;when others=>null;end case;if clk'event and clk='1' then d1<=d; end if;end process;dout<=d1;end;3、锯齿波程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned;entity juchigt isport(clk:in std_logic;dout:out integer range 255 downto 0);end;architecture dacc of juchigt issignal q :integer range 63 downto 0;signal d :integer range 255 downto 0;signal d1:integer range 255 downto 0;beginprocess(clk)beginif clk'event and clk='1' thenif q<63 then q<=q+1;else q<=0;end if; end if;end process;process(q)begincase q iswhen 00=> d<=0;when 01=> d<=4;when 02=> d<=8;when 03=> d<=12;when 04=> d<=16;when 05=> d<=20;when 06=> d<=24;when 07=> d<=28;when 08=> d<=32;when 09=> d<=36;when 10=> d<=40;when 11=> d<=44;when 12=> d<=48;when 13=> d<=52;when 14=> d<=56;when 15=> d<=60;when 16=> d<=64;when 17=> d<=68;when 18=> d<=72;when 19=> d<=76;when 20=> d<=80;when 21=> d<=84;when 22=> d<=88;when 23=> d<=92;when 24=> d<=96;when 25=> d<=100;when 26=> d<=104;when 27=>when 28=> d<=112;when 29=> d<=116;when 30=> d<=120;when 31=> d<=124;when 32=> d<=128;when 33=> d<=132;when 34=> d<=136;when 35=> d<=140;when 36=> d<=144;when 37=> d<=148;when 38=> d<=152;when 39=> d<=156;when 40=> d<=160;when 41=> d<=164;when 42=> d<=168;when 43=> d<=172;when 44=> d<=176;when 45=> d<=180;when 46=> d<=184;when 47=> d<=188;when 48=> d<=192;when 49=> d<=196;when 50=> d<=200;when 51=> d<=204;when 52=> d<=208;when 53=> d<=212;when 54=> d<=216;when 55=> d<=220;when 56=> d<=224;when 57=> d<=228;when 58=> d<=232;when 59=> d<=236;when 60=> d<=240;when 61=> d<=244;when 62=> d<=248;when 63=> d<=252;when others=>null;end case;if clk'event and clk='1' then d1<=d; end if;end process;dout<=d1;end;4、方波程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned;entity fanggt isport(clk:in std_logic;dout:out integer range 255 downto 0);end;architecture dacc of fanggt issignal q :integer range 63 downto 0;signal d :integer range 255 downto 0;signal d1:integer range 255 downto 0;beginprocess(clk)beginif clk'event and clk='1' thenif q<63 then q<=q+1;else q<=0;end if; end if;end process;begincase q iswhen 00=> d<=255;when 01=> d<=255;when 02=> d<=255;when 03=> d<=255;when 04=> d<=255;when 05=> d<=255;when 06=> d<=255;when 07=> d<=255;when 08=> d<=255;when 09=> d<=255;when 10=> d<=255;when 11=> d<=255;when 12=> d<=255;when 13=> d<=255;when 14=> d<=255;when 15=> d<=255;when 16=> d<=255;when 17=> d<=255;when 18=> d<=255;when 19=> d<=255;when 20=> d<=255;when 21=> d<=255;when 22=> d<=255;when 23=> d<=255;when 24=> d<=255;when 25=> d<=255;when 26=> d<=255;when 27=> d<=255;when 28=> d<=255;when 29=> d<=255;when 30=> d<=255;when 31=> d<=255;when 32=> d<=0;when 33=> d<=0;when 34=> d<=0;when 35=> d<=0;when 36=> d<=0;when 37=> d<=0;when 38=> d<=0;when 39=> d<=0;when 40=> d<=0;when 41=> d<=0;when 42=> d<=0;when 43=> d<=0;when 44=> d<=0;when 45=> d<=0;when 46=> d<=0;when 47=> d<=0;when 48=> d<=0;when 49=> d<=0;when 50=> d<=0;when 51=> d<=0;when 52=> d<=0;when 53=> d<=0;when 54=> d<=0;when 55=> d<=0;when 56=> d<=0;when 57=> d<=0;when 58=> d<=0;when 59=> d<=0;when 60=> d<=0;when 61=> d<=0;when 62=> d<=0;when 63=> d<=0;when others=>null;end case;if clk'event and clk='1' then d1<=d; end if;end process;dout<=d1;end;5、波形选择程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity wav_sel isport( a:in std_logic;reset:in std_logic;d1,d2,d3,d4:in integer range 255 downto 0;q:out integer range 255 downto 0);architecture behav of wav_sel issignal k:integer range 3 downto 0:=0;beginprocess(a,reset)beginif reset='0' then q<=d1;else if a'event and a='1' thenif k<3 then k<=k+1;else k<=0 ;end if;end if;end if;case k iswhen 0=> q<=d1;when 1=> q<=d2;when 2=> q<=d3;when 3=> q<=d4;end case;end process;end behav;6、频率控制程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isport(ffclk:in std_logic;cp:out std_logic);end;architecture str of fenpin issignal count:integer range 0 to 500;signal clk_data:std_logic;beginprocess(ffclk,count)beginif ffclk'event and ffclk='1' thenif count=50 thencount<=0;clk_data<=not clk_data;else count<=count+1;end if;end if;end process;end str;7、幅度控制程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity fudugt isport (d:in integer range 255 downto 0;temp,reset:in std_logic;fout:out integer range 65535 downto 0);end;architecture behav of fudugt issignal d1:integer range 65535 downto 0;signal k:integer range 255 downto 0:=1;beginprocess(temp)beginif reset='0' then d1<=0;elseif temp'event and temp='1' then k<=k+1; end if;end if;d1<=d*k;end process;fout<=d1;end;8、数码管显示程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity display isport(cp1:in std_logic;k:in std_logic_vector(5 downto 0);m:in std_logic_vector(4 downto 0);show:out std_logic_vector(7 downto 0);sel:out std_logic_vector(3 downto 0));end display;architecture behavior of display issignal count:integer range 0 to 3;signal sel_1:std_logic_vector(3 downto 0);signal p0,p1,p2,p3:integer range 0 to 9;signal show1:std_logic_vector(7 downto 0);beginprocess(cp1)beginif(cp1'event and cp1='1')thenif count=3 then count<=0;elsecount<=count+1;end if;end if;end process;process(k,m)begincase k iswhen "000000"=>p0<=0;p1<=0;when "000001"=>p0<=1;p1<=0;when "000010"=>p0<=2;p1<=0;when "000011"=>p0<=3;p1<=0;when "000100"=>p0<=4;p1<=0;when "000101"=>p0<=5;p1<=0;when "000110"=>p0<=6;p1<=0;when "000111"=>p0<=7;p1<=0;when "001000"=>p0<=8;p1<=0;when "001001"=>p0<=9;p1<=0;when "001010"=>p0<=0;p1<=1;when "001011"=>p0<=1;p1<=1;when "001100"=>p0<=2;p1<=1;when "001101"=>p0<=3;p1<=1;when "001110"=>p0<=4;p1<=1;when "001111"=>p0<=5;p1<=1;when "010000"=>p0<=6;p1<=1;when "010001"=>p0<=7;p1<=1;when "010010"=>p0<=8;p1<=1;when "010011"=>p0<=9;p1<=1;when "010100"=>p0<=0;p1<=2;when "010101"=>p0<=1;p1<=2;when "010110"=>p0<=2;p1<=2;when "010111"=>p0<=3;p1<=2;when "011000"=>p0<=4;p1<=2;when "011001"=>p0<=5;p1<=2;when "011010"=>p0<=6;p1<=2;when "011011"=>p0<=7;p1<=2;when "011100"=>p0<=8;p1<=2;when "011110"=>p0<=0;p1<=3;when "011111"=>p0<=1;p1<=3;when "100000"=>p0<=2;p1<=3;when "100001"=>p0<=3;p1<=3;when "100010"=>p0<=4;p1<=3;when "100011"=>p0<=5;p1<=3;when "100100"=>p0<=6;p1<=3;when "100101"=>p0<=7;p1<=3;when "100110"=>p0<=8;p1<=3;when "100111"=>p0<=9;p1<=3;when "101000"=>p0<=0;p1<=4;when "101001"=>p0<=1;p1<=4;when "101010"=>p0<=2;p1<=4;when "101011"=>p0<=3;p1<=4;when "101100"=>p0<=4;p1<=4;when "101101"=>p0<=5;p1<=4;when "101110"=>p0<=6;p1<=4;when "101111"=>p0<=7;p1<=4;when "110000"=>p0<=8;p1<=4;when "110001"=>p0<=9;p1<=4;when "110010"=>p0<=0;p1<=5;when "110011"=>p0<=1;p1<=5;when "110100"=>p0<=2;p1<=5;when "110101"=>p0<=3;p1<=5;when "110110"=>p0<=4;p1<=5;when "110111"=>p0<=5;p1<=5;when "111000"=>p0<=6;p1<=5;when "111001"=>p0<=7;p1<=5;when "111010"=>p0<=8;p1<=5;when "111011"=>p0<=9;p1<=5;when "111100"=>p0<=0;p1<=6;when "111101"=>p0<=1;p1<=6;when "111110"=>p0<=2;p1<=6;when "111111"=>p0<=3;p1<=6;when others=>p0<=0;p1<=0; end case;case m iswhen "00000"=>p2<=0;p3<=0;when "00001"=>p2<=1;p3<=0;when "00010"=>p2<=2;p3<=0;when "00011"=>p2<=3;p3<=0;when "00101"=>p2<=5;p3<=0;when "00110"=>p2<=6;p3<=0;when "00111"=>p2<=7;p3<=0;when "01000"=>p2<=8;p3<=0;when "01001"=>p2<=9;p3<=0;when "01010"=>p2<=0;p3<=1;when "01011"=>p2<=1;p3<=1;when "01100"=>p2<=2;p3<=1;when "01101"=>p2<=3;p3<=1;when "01110"=>p2<=4;p3<=1;when "01111"=>p2<=5;p3<=1;when "10000"=>p2<=6;p3<=1;when "10001"=>p2<=7;p3<=1;when "10010"=>p2<=8;p3<=1;when "10011"=>p2<=9;p3<=1;when "10100"=>p2<=0;p3<=2;when "10101"=>p2<=1;p3<=2;when "10110"=>p2<=2;p3<=2;when "10111"=>p2<=3;p3<=2;when "11000"=>p2<=4;p3<=2;when "11001"=>p2<=5;p3<=2;when "11010"=>p2<=6;p3<=2;when "11011"=>p2<=7;p3<=2;when "11100"=>p2<=8;p3<=2;when "11101"=>p2<=9;p3<=2;when "11110"=>p2<=0;p3<=3;when "11111"=>p2<=1;p3<=3;when others=>p2<=0;p3<=0;end case;end process;process(count)begincase count iswhen 0=>sel_1<="1110";when 1=>sel_1<="1101";when 2=>sel_1<="1011";when 3=>sel_1<="0111";end case;end process;process(sel_1)beginif(sel_1(0)='0')thencase p0 iswhen 0=>show1<="11000000";when 1=>show1<="11111001";when 2=>show1<="10100100";when 3=>show1<="10110000";when 4=>show1<="10011001";when 5=>show1<="10010010";when 6=>show1<="10000010";when 7=>show1<="11111000";when 8=>show1<="10000000";when 9=>show1<="10010000";when others=>show1<=null; end case;elsif(sel_1(1)='0')thencase p1 iswhen 0=>show1<="11000000";when 1=>show1<="11111001";when 2=>show1<="10100100";when 3=>show1<="10110000";when 4=>show1<="10011001";when 5=>show1<="10010010";when 6=>show1<="10000010";when 7=>show1<="11111000";when 8=>show1<="10000000";when 9=>show1<="10010000";when others=>show1<=null; end case;elsif(sel_1(2)='0')thencase p2 iswhen 0=>show1<="11000000";when 1=>show1<="11111001";when 2=>show1<="10100100";when 3=>show1<="10110000";when 4=>show1<="10011001";when 5=>show1<="10010010";when 6=>show1<="10000010";when 7=>show1<="11111000";when 8=>show1<="10000000";when 9=>show1<="10010000";when others=>show1<=null; end case;elsif(sel_1(3)='0')thencase p3 iswhen 0=>show1<="11000000";when 1=>show1<="11111001";when 2=>show1<="10100100";when 3=>show1<="10110000";when 4=>show1<="10011001";when 5=>show1<="10010010";when 6=>show1<="10000010";when 7=>show1<="11111000";when 8=>show1<="10000000";when 9=>show1<="10010000";when others=>show1<=null;end case;end if;end process;process(cp1)beginif cp1'event and cp1='1' thensel<=sel_1;show<=show1;end if;end process;end behavior;9、按键程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity kchoose isport(key2,clk:in std_logic;k:out std_logic_vector(5 downto 0));end;architecture str of kchoose issignal q1,q2,cp: std_logic;signal count: integer range 0 to 2048;signal clk_data: std_logic;signal imp: std_logic;signal cc: std_logic_vector(5 downto 0);beginprocess(clk,count)beginif clk'event and clk='1' thenif count=2048 thencount<=0;clk_data<=not clk_data;else count<=count+1;end if;end if;cp<=clk_data;end process;process(cp)beginif cp'event and cp='1' thenq2<=q1;q1<=key2;end if;end process;imp<=q1 and not q2;process(imp)beginif imp'event and imp='1' thenif cc="111111" thencc<="000000";else cc<=cc+1;end if;end if;end process;k<=cc;end str;10、顶层模块程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned;entity xuanzegt isport(fclk,p1,p2,reset1:in std_logic;dout:out integer range 65535 downto 0);end;architecture beh of xuanzegt iscomponent fenpinport(ffclk:in std_logic;cp:out std_logic);end component;component fudugtport (d:in integer range 255 downto 0;temp,reset:in std_logic;fout:out integer range 65535 downto 0);end component;component wav_selport( a,reset:in std_logic;d1,d2,d3,d4:in integer range 255 downto 0;q:out integer range 255 downto 0);end component;component singtport(clk:in std_logic;dout:out integer range 255 downto 0);end component;component fanggtport(clk:in std_logic;dout:out integer range 255 downto 0);end component;component juchigtport(clk:in std_logic;dout:out integer range 255 downto 0);end component;component sanjiaogtport(clk:in std_logic;dout:out integer range 255 downto 0);end component;signal w,x,y,z,v:integer range 255 downto 0;signal f:std_logic;beginu1:singt port map (dout=>w,clk=>f);u2:fanggt port map (dout=>x,clk=>f);u3:juchigt port map (dout=>y,clk=>f);u4:sanjiaogt port map (dout=>z,clk=>f);u5:wav_sel port map (d1=>w,d2=>x,d3=>y,d4=>z,q=>v,a=>p1,reset=>reset1);u6:fudugt port map (temp=>p2,d=>v,fout=>dout,reset=>reset1);u7:fenpin port map (ffclk=>fclk,cp=>f);end;。