第10章AT89C51与输入外设和输出外设的接口设计

- 格式:ppt

- 大小:1.62 MB

- 文档页数:47

AT89C51单片机的基本结构和工作原理AT89C51是一种低功耗、高性能的8位单片机,由美国公司Intel (现已被英特尔收购)开发。

它采用CMOS技术制造,在各种工业、汽车和家用电器等领域广泛应用。

AT89C51的基本结构和工作原理如下:一、基本结构:1.中央处理单元(CPU):中央处理单元是AT89C51单片机的控制中心,负责执行程序指令、算术运算和逻辑操作等。

它包括一个8位的累加寄存器ACC、一个8位的指令寄存器IR和一个8位的程序计数器PC。

2.存储器:AT89C51单片机包括4KB的内部闪存ROM用于存储程序代码,并具有可擦写和可编程的特性。

此外,还有128字节的RAM用于存储各种变量和中间结果。

3.输入输出端口(IO):AT89C51单片机有四个8位的IO口(P0、P1、P2和P3),可分别用作输入和输出。

每个IO口都可以设置为输入或输出模式,并且可以具有内部上拉电阻。

4. 定时器/计数器:AT89C51单片机包含两个定时器/计数器(Timer 0和Timer 1),用于产生定时和延时功能。

这两个定时器/计数器都可以工作在8位或16位模式下,并可以设置为定时、计数和波形发生器等不同功能。

5.串行数据通信接口(控制模式):AT89C51单片机具有一个可编程的串行数据通信接口,支持全双工和半双工模式。

它可以与其他外部设备如传感器、LCD显示器和电脑等进行通信。

二、工作原理:1.程序执行过程:首先,AT89C51单片机将程序代码从ROM存储器中读取到指令寄存器IR中。

然后,指令寄存器将指令传输给中央处理单元CPU。

CPU根据指令类型执行不同的操作,如算术运算、逻辑判断、数据读写等。

执行完一条指令后,程序计数器PC将自动递增,指向下一条指令的地址,继续执行。

2.IO交互:AT89C51单片机的IO口可以用作输入和输出。

在输入模式下,IO口可以接收来自外部设备的信号,并传输给中央处理单元CPU。

AT89C51单片机简介2.管脚说明VCC 供电电压。

GND 接地。

P0口 P0口为一个8 漏级开路 向I/O口, 脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据 储器,它可 被定义为数据/地址的第八 。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码, 时P0外部必须被拉高。

P1口 P1口是一个内部提供 拉电阻的8 向I/O口,P1口缓冲器能接收输出4TTL 门电流。

P1口管脚写入1后,被内部 拉为高,可用作输入,P1口被外部 拉为 电平时,将输出电流,这是由于内部 拉的缘故。

在FLASH编程和校验时,P1口作为第八 地址接收。

P2口 P2口为一个内部 拉电阻的8 向I/O口,P2口缓冲器可接收,输出4个TTL 门电流,当P2口被写“1”时,其管脚被内部 拉电阻拉高,且作为输入。

并因 作为输入时,P2口的管脚被外部拉 ,将输出电流。

这是由于内部 拉的缘故。

P2口当用于外部程序 储器或16 地址外部数据 储器进行 取时,P2口输出地址的高八 。

在给出地址“1”时,它利用内部 拉优势,当对外部八 地址数据 储器进行读写时,P2口输出其特殊 能寄 器的内容。

P2口在FLASH编程和校验时接收高八 地址信号和控制信号。

P3口 P3口管脚是8个带内部 拉电阻的 向I/O口,可接收输出4个TTL门电流。

当P3口写入“1”后,它们被内部 拉为高电平,并用作输入。

作为输入,由于外部 拉为 电平,P3口将输出电流 ILL 这是由于 拉的缘故。

P3口也可作为AT89C51的一些特殊 能口,如 表所示口管脚备选 能P3.0 RXD 串行输入口P3.1 TXD 串行输出口P3.2 /INT0 外部中断0P3.3 /INT1 外部中断1P3.4 T0 记时器0外部输入P3.5 T1 记时器1外部输入P3.6 /WR 外部数据 储器写选通P3.7 /RD 外部数据 储器读选通P3口同时为闪烁编程和编程校验接收一些控制信号。

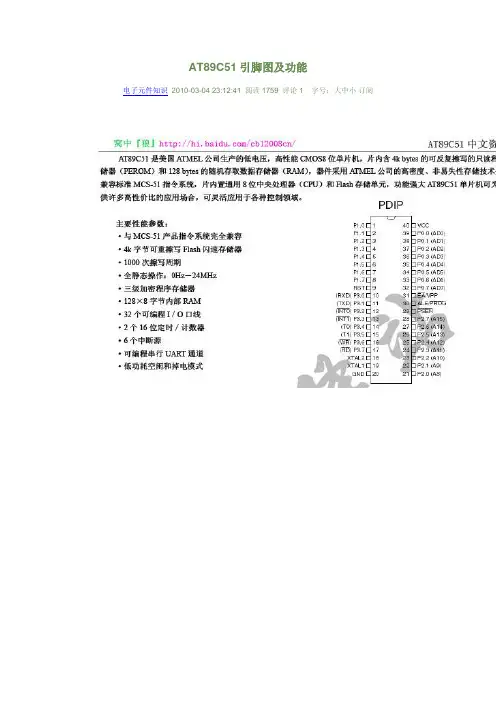

AT89C51引脚图及功能电子元件知识2010-03-04 23:12:41 阅读1759 评论1 字号:大中小订阅89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便); ┏━┓┏━┓; P1.0 ┫1 ┗┛40┣Vcc; P1.1 ┫2 39┣P0.0; P1.2 ┫3 38┣P0.1; P1.3 ┫4 37┣P0.2; P1.4 ┫5 36┣P0.3; P1.5 ┫6 35┣P0.4; P1.6 ┫7 34┣P0.5; P1.7 ┫8 33┣P0.6; RST/Vpd ┫9 32┣P0.7; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择); TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出); -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出); -INT1 P3.3 ┫13 28┣P2.7; T0 P3.4 ┫14 27┣P2.6; T1 P3.5 ┫15 26┣P2.5; -WR P3.6 ┫16 25┣P2.4; -RD P3.7 ┫17 24┣P2.3; X2 ┫18 23┣P2.2; X1 ┫19 22┣P2.1; GND ┫20 21┣P2.0; ┗━━━━┛引脚说明:①电源引脚Vcc(40脚):典型值+5V。

Vss(20脚):接低电平。

②外部晶振X1、X2分别与晶体两端相连接。

当采用外部时钟信号时,X2接振荡信号,X1接地。

③输入输出口引脚:P0口:I/O双向口。

作输入口时,应先软件置“ 1”。

P1口:I/O双向口。

作输入口时,应先软件置“ 1”。

P2口:I/O双向口。

作输入口时,应先软件置“ 1”。

P3口:I/O双向口。

作输入口时,应先软件置“ 1”。

④控制引脚:RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。

RST/Vpd(9脚):复位信号输入端(高电平有效)。

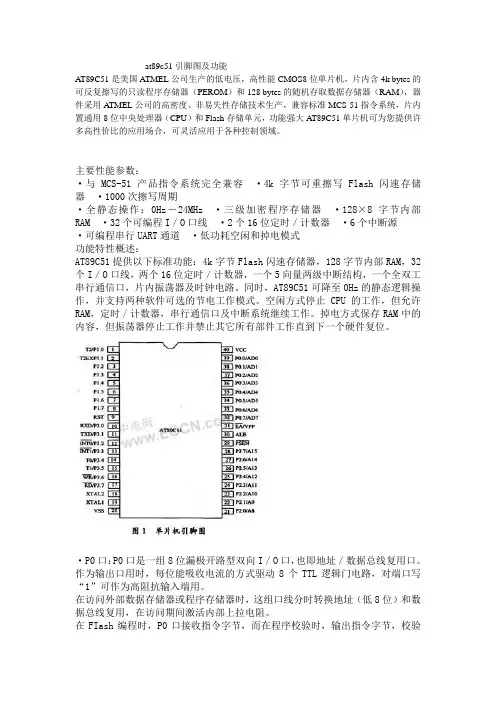

at89c51引脚图及功能AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

主要性能参数:·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

at89c51单片机与dac实验原理实验目的:通过将AT89C51单片机与DAC(数模转换器)连接,实现数字信号到模拟信号的转换,并通过外部模拟电路将转换后的信号输出到外部设备,进而实现对外部设备的控制或反馈。

实验原理:AT89C51单片机是一种常用的8位单片机,具有强大的数据处理能力和丰富的外设资源。

而DAC则是一种能够将数字信号转换为模拟信号的电子组件。

将AT89C51与DAC连接,可以实现通过单片机控制DAC输出模拟信号的功能。

DAC的工作原理是通过将一个数字信号转换为与之等效的模拟信号。

一般情况下,DAC的输入端接收到的是一个n位的数字信号。

而DAC的输出端则是一个与输入数字信号等效的模拟电压或电流信号。

通过改变输入端的数字信号,可以控制输出信号的幅度,实现对模拟信号的控制。

AT89C51单片机与DAC连接时,其输入端通过端口连接到单片机的IO 口,而DAC的输出端则通过外部模拟电路连接到外部设备。

在这个过程中,单片机通过编写程序控制IO口的输出信号,将对应的数字信号输入到DAC的输入端。

DAC将输入的数字信号转换为模拟信号,并通过外部电路将模拟信号输出到外部设备。

通过改变单片机输出信号的方式、频率和幅度,可以实现对外部设备进行控制或反馈。

实验步骤:1.连接AT89C51单片机与DAC。

根据DAC的引脚定义,将单片机的IO 口与DAC的输入端连接,同时将DAC的输出端与外部设备连接。

2.编写单片机程序。

根据实验需求,编写单片机程序,控制IO口的输出信号。

通过改变IO口输出信号的方式、频率和幅度,实现对DAC的输入信号的控制。

4.进行实验观察。

观察外部设备是否输出相应的结果,检测转换过程是否正常。

实验所需材料:-AT89C51单片机-DAC数模转换器-外部模拟电路-外部设备(如电机、灯光等)实验心得:通过将AT89C51单片机与DAC连接,可以实现数字信号到模拟信号的转换。

该实验具有一定的重要性,因为它可以通过单片机实现对外部设备的精确控制。

AT89C51设计1. 简介AT89C51是一种经典的8位单片机,由凯瑞电子(Keil)公司生产。

它是Intel 8051指令集架构的一部分,具有强大的功能和广泛的应用。

AT89C51具有51个I/O引脚,4KB flash存储器,128字节的RAM,以及4个8位定时器/计数器。

它适用于各种嵌入式系统,如家电控制,电子设备,工业自动化,安全系统等。

本文将分享AT89C51的设计相关知识,包括硬件配置、编程语言和开发工具等内容。

2. 硬件配置AT89C51的硬件配置包括以下几个方面:2.1. 晶体振荡器AT89C51支持外部晶体振荡器,用于提供时钟信号。

一般情况下,使用11.0592MHz的晶体振荡器可以满足大多数应用需求。

2.2. 电源AT89C51工作电压为4.5V至5.5V,可以通过外部电源供电。

在设计中,需要提供稳定的电源电压,并通过适当的电源滤波电路降低电源噪音。

2.3. 外部存储器AT89C51内置4KB的闪存和128字节的RAM。

如果需要更大的存储空间,可以通过外部存储器扩展。

此外,还可以通过外部EEPROM实现数据的长期存储。

2.4. 输入/输出设备AT89C51具有51个I/O引脚,可用于连接各种输入/输出设备,如LED,键盘,LCD显示器等。

在设计中,需要根据具体需求配置合适的输入/输出设备。

3. 编程语言AT89C51支持多种编程语言,如汇编语言和C语言。

以下将介绍两种常见的编程语言。

3.1. 汇编语言汇编语言是一种符号化的低级语言,直接操作计算机硬件。

AT89C51使用的汇编语言是51系列的汇编语言,具有良好的指令集和寻址模式。

以下是一个简单的AT89C51汇编代码示例:ORG 0HMOV A, #20HMOV P1, AEND3.2. C语言C语言是一种高级编程语言,具有结构化的特点,能够更方便地编写和维护代码。

AT89C51的C语言编程通常使用凯瑞电子(Keil)公司的Keil C编译器。

北方民族大学学士学位论文论文题目:AT89C51单片机USB接口驱动和应用程序的开发院(部)名称:电信学院学生姓名:杨闯指导教师姓名:周春艳论文提交时间: 2010年5月24日论文答辩时间:2010年5月29日学位授予时间:北方民族大学教务摘要通用串行总线USB是一种新兴的并逐渐取代其他接口标准的数据通信标准。

USB,由于速度快,使用方便灵活,易于扩展,支持即插即用,成本低廉等一系列优点,得到了广泛的应用。

本论文以基于USB总线的数据采集系统的研制过程为主要内容,阐述了利用CH372与ATMEL的AT89C51等组成的一套数据采集系统的设计方案、开发方法和开发过程,并给出了具体实现方案。

论文首先简要介绍了USB总线的相关内容,然后介绍了数据采集系统的设计。

数据采集系统的设计包括硬件设计、固件程序开发、驱动程序开发和应用程序开发四部分。

在硬件设计部分,首先介绍了设计中所用的CH372的性能和特点,然后给出了具体硬件设计方案,并对设计中应该注意的问题进行了说明。

驱动和应用程序主要完成USB设备的读写和即插即用功能,并提供一个友好的人机界面,对数据采集系统进行控制并显示采集后的数据。

本论文已完成了基于USB总线的数据采集系统的设计,用其实现了基本的数据采集功能。

使用USB总线传输数据,为数据采集系统与计算机之间的通讯开辟了新的道路。

关键词:USB、驱动程序、应用程序、AT89C51、CH372AbstractUniversal serial bus USB is one kind of emerging and replace other interface standards of data communication standards. USB, due to fast, convenient and flexible easy to expand, to support plug and play, low cost advantages, such as widely application.The paper is mainly concerned with design process of data acquisition system that is based on USB bus. The design scheme, developing method and developing process of a suit of data acquisition system used with CH372 and ATMEL’s AT89C51 are expatiate. In addition, the paper also gives the material realization scheme.At fist, the paper introduces the protocol of USB bus in brief, and then discusses the design of data acquisition system, which includes four parts, , firmware design, device driver and application program. In the in detail; the questions which should be paid attention to in design is explained. Drivers and applications of the main equipment and USB plug and play function, and provide a friendly -machine interface, control ofdata acquisition system and display the data collection.The paper of data acquisition system based on USB bus and realizedthe basal data acquisition foundation. Using USB bus to transfer data blazed a way in communication between data acquisition system and computer.Keywords: USB、Drive、Applications、AT89C51、CH372目录第1章绪论 (1)1.1 引言 (5)1.2 USB的特点 (5)1.3 USB实时数据采集系统的实现方案 (7)第2章 USB体系简介 (8)2.1 体系概述 (8)2.2 USB的传输类型 (10)2.3 USB的设备状态 (13)第3章 USB数据采集系统的硬件设计 (16)3.1 USB 接口方案 (16)3.2 USB接口的硬件设计 (17)3.2.1 CH372简介 (17)3.2.2 USB接口的硬件电路设计 (23)3.3 USB接口硬件的实现 (25)3.3.1时钟电路 (25)3.3.2 复位电路 (25)3.3.3 AD转换电路 (26)3.3.4 CH372接口电路 (27)3.3.5 单片机扩展RAM接口电路 (28)第4章 USB数据采集系统设备固件编写 (28)4.1 固件设计方案及工作流程 (29)4.1.1固件的设计思想 (29)4.1.2固件的工作流程 (29)4.2固件开发 (30)4.2.1主循环模块(MAINLOOP.C) (30)4.2.2外接口模块 (31)4.2.3 CH375_INIT初始化模块 (31)4.2.4上传数据块模块 (31)4.2.5上传中断数据模块 (31)第5章 USB设备驱动程序及应用程序 (32)5.1驱动开发工具的选择 (32)5.2 WDM概述 (32)5.3 主要模块设计 (33)5.3.1 初始化模块 (34)5.3.2即插即用管理模块 (34)5.3.3 I\O控制模块 (37)5.4 应用程序设计与实现 (37)5.4.1 操作例程及初始化 (38)5.4.2 设备读写接口程序的实现 (39)5.4.3 数据传输程序的设计和实现 (40)5.5 用户应用程序的具体实现 (45)结束语 (46)致谢 (47)参考文献 (47)附录一 (48)附录二 (48)第1章绪论1.1 引言现代工业生产和科学研究对数据采集系统的要求日益提高,目前比较通用的方法已逐渐不能适应其要求。

第8章AT89C51系统接口技术难点•8255的控制字•8255的工作方式1和工作方式2•DAC0832工作方式•ADC0809工作方式要求掌握:•8255接口芯片•MCS-51单片机与D/A转换器的接口连接•MCS-51单片机与A/D转换器的接口连接•初始化编程及应用了解:•I/O口扩展的原因•简单I/O口的扩展•单片机的键盘技术8.1 I/O口扩展概述8.2 简单I/O口扩展8.3 8255可编程通用并行接口芯片8.4 8155可编程通用并行接口芯片8.1 I/O口扩展概述8.1.1 I/O口扩展的原因MCS-51系列单片机共有四个并行I/O口,分别是P0、P1、P2和P3。

其中P0口一般作地址线的低八位和数据线使用;P2口作地址线的高八位使用;P3是一个双功能口,其第二功能是一些很重要的控制信号,所以P3一般使用其第二功能。

这样供用户使用的I/O口就只剩下P1口了。

另外,这些I/O口没有状态寄存和命令寄存的功能,因此难以满足复杂的I/O操作要求。

由于MCS-51系列单片机I/O口数量和功能有限,所以在实际应用中不得不使用扩展的方法,来增加I/O口的数量,增强I/O口的功能。

8.1.2 I/O口的编址技术用户可以通过对I/O口进行读和写操作来完成数据的输入和输出。

例如:P0口的地址为80H。

用户可以使用MOV指令对P0口进行写操作。

MOV P0, A8.1.3 单片机I/O传送的方式单片机为了实现数据的输入/输出传送,通常使用3种控制方式。

1. 无条件传送方式当外设和单片机能够同步工作时,可以采用无条件方式进行传送,即数据可以随时进行传送。

2. 查询方式查询方式又称为有条件传送方式,即数据的传送是有条件的。

在进行I/O操作之前,用户要通过软件查询外设是否为数据传送做好准备,只有确认外设为数据传送做好准备。

单片机才能执行数据的输入/输出(I/O)操作。

3. 中断方式当外设和计算机进行数据交换时,外设向单片机发出中断请求(即通知单片机)。

单片机原理与应用设计第一章单片机概述在一块半导体硅片上集成了中央处理单元(CPU)、存储器(RAM/ROM)、和各种I/O接口的集成电路芯片由于其具有一台微型计算机的属性,因而被称为单片微型计算机,简称单片机。

单片机主要应用于测试和控制领域。

单片机的发展历史分为四个阶段。

1974—1976年是单片机初级阶段,1976—1978年是低性能单片机阶段,1978—1983年是高性能单片机阶段,期间各公司的8位单片机迅速发展。

1983至现在是8位单片机巩固发展及16位、32位单片机推出阶段。

单片机的发展趋势将向大容量、高性能、外围电路内装化等方面发展。

单片机的发展非常迅速,其中MCS-51系列单片机应用非常广泛,而在众多的MCS-51单片机及其各种增强型、扩展型的兼容机中,AT89C5x系列,尤其是AT89C51单片机成为8位单片机的主流芯片之一。

第二章89C51单片机的硬件结构89C51单片机的功能部件组成如下:8位微处理器,128B数据存储器片外最多可外扩64KB,4KB程序存储器,中断系统包括5个中断源,片内2个16位定时器计数器且具有4种工作方式。

1个全双工串行口,具有四种工作方式。

4个8位并行I/O口及特殊功能寄存器。

89C51单片机的引脚分为电源及时钟引脚、控制引脚及I/O口。

电源为5V 供电,P0口为8位漏极开路双向I/O口,字节地址80H,位地址80H—87H。

可作为地址/数据复用口,用作与外部存储器的连接,输出低8位地址和输出/输入8位数据,也可作为通用I/O口,需外接上拉电阻。

P1、P2、P3为8位准双向I/O 口,具有内部上拉,字节地址分别为90H,A0H,B0H。

其中P0、P2口可作为系统的地址总线和数据总线口,P2口作为地址输出线使用时可输出外部存储器的的高8位地址,与P0口输出的低8位地址一起构成16位地址线。

P1是供用户使用的普通I/O口,P3口是双向功能端口,第二功能很重要。

第9章AT89C51扩展IO接口的设计第9章 AT89C51扩展IO接口的设计为了满足AT89C51单片机扩展更多IO接口的需求,本章将介绍一种设计方案,旨在增加AT89C51单片机的可扩展性和灵活性。

设计目标:1. 增加AT89C51单片机的IO接口数量,使其能够连接更多的外设设备;2. 提高IO接口的可靠性和稳定性,以确保数据传输的准确性;3. 简化硬件设计,减少电路的复杂度;4. 方便用户使用和维护。

设计思路:本方案采用串行并行转换器(Serial-to-Parallel Converter)来扩展AT89C51单片机的IO接口。

通过串行并行转换器,可以将AT89C51单片机的串行数据信号转换成并行数据信号,从而实现与更多外设设备的连接。

硬件设计:1. 连接AT89C51单片机的TXD引脚和串行并行转换器的串行数据输入端;2. 连接串行并行转换器的并行数据输出端和外设设备的输入端;3. 连接AT89C51单片机的相应引脚和外设设备的控制引脚,用于控制数据的发送和接收。

软件设计:1. 初始化AT89C51单片机的串行通信模块,设置波特率和其他串口参数;2. 编写程序代码,实现与外设设备的数据交互。

例如,发送数据到外设设备或接收来自外设设备的数据;3. 根据具体需求,编写相应的中断服务程序,以处理外设设备的数据请求或其他事件。

实施与测试:1. 绘制电路板原理图,并按照设计要求进行布线;2. 制作电路板,焊接元件;3. 完成电路板的调试,检查连接是否正确,电路是否正常工作;4. 编写测试程序,通过串行通信模块发送和接收数据,验证扩展IO 接口的功能;5. 进行充分测试,确保扩展IO接口的稳定性和可靠性。

总结:通过本章所介绍的AT89C51扩展IO接口的设计方案,可以有效地扩展AT89C51单片机的IO接口,并且提高其可靠性和稳定性。

该设计方案简化了硬件电路的复杂度,方便用户使用和维护。

在实施与测试过程中,需要严格按照设计要求进行,以确保扩展IO接口的正常工作。

AT89C51单片机高速串行输出口设计AT89C51(与MCS-51 兼容)单片机的串行口在方式0 工作状态下,使用移位寄存器芯片可以扩展多个8 位并行I/O 口。

在LED 点阵显示屏应用系统中,一般都采用数据同步移位输出方式,并使用移位寄存器芯片(如74LS595)扩展并行I/O 口驱动LED 点阵显示。

LED 点阵显示采用扫描方式,为不产生闪烁感,每秒需要传送50 屏点阵显示数据,因此有大量的数据要通过同步移位的方式送到显示驱动电路部分,这就要求单片机能够快速地输出数据。

AT89C51 单片机的串行口在方式0 工作状态下,数据以fosc/12 的波特率输出,1 个字节数据写入SBUF 后,需检查中断标志位TI 是否为1 并清0TI 或延时几个机器周期后才能继续写入了一个数据,输出速度慢。

在LED 点阵显示屏应用系统中,系统与PC 机之间的通讯需要使用单片机的串行口,显示数据的同步移位输出口只有另外扩展。

本文介绍的高速串行同步移位输出口(以下简称扩展串行口)电路,采用模块化设计,给出基于TTL 和PLD 两种电路的实现方案,波特率提高到fosc,数据输出不需要等待或延时。

一、扩展串行口与单片机的连接扩展串行口电路框图如图1 所示。

与并行存储器芯片类似,扩展串行口被视为一个外部RAM 地址单元,直接挂接在AT89C51 的外部数据总线上,D0~D7 为数据线,CE 为片选信号,WE 为写脉冲信号,也是扩展串行口的输出控制信号。

AT89C51 外接晶体振荡器的振荡信号经二个与非门整形后为扩展串行口提供时钟脉冲XTAL2。

DAT 和CLK 分别是扩展串行口的数据输出端和同步移位脉冲输出端。

二、操作指令假设AT89C51 分配给扩展串行口的地址是0000H,使用MOVX@DPTR,A。

班级电科081 班姓名龚浪学号080712110073 实验名称键盘接口实验指导教师马光喜理学院时间:2011年月日实验九键盘接口实验(设计性实验)一、实验目的:⑴熟悉单片机通过行列键盘的接口方法⑵掌握键盘扫描及处理程序的编程方法和调试方法二、实验内容:程序运行后,根据按下的数字键,数码管上应能显示相应数字。

三、实验硬件电路四、实验步骤:1、进入Keil C51组合软件的操作环境2、在Keil C51组合软件环境中, 根据实验硬件电路编辑源程序并对源文件进行编译,生成目标代码;源程序如下:;EXP9ORG 0000HLJMP MAINORG 8000H;*******检查是否有键按下******************** MAIN: MOV P0,#00MOV A,P2ANL A,#0FHSUBB A,#0FHJNC MAINACALL DELAY ;延时去抖动;****寄存器赋初值****************MOV R2,#4 ;R2记录行数MOV R3,#4 ;R3记录列数MOV A,#0FEH ;行扫描初始值MOV R4,#0FFH ;R4记录键号初值;*******按键扫描***************************** NEXT1: MOV P0,ARLC AMOV R0,A ;修改扫描码并送R0保存MOV A,P2 ;读入列值ANL A,#0FH ;清除高4位CJNE A,#0FH,NEXT2 ;有列值为0,转NEXT2MOV A,R4ADD A,R3 ;否则指向该行最后一列MOV R4,AMOV A,R0DJNZ R2,NEXT1 ;扫描下一行LJMP MAINNEXT2: INC R4 ;键号加1RRC AJC NEXT2 ;不是按键所在列,转NEXT2使键号加1MOV A,R4MOV P3,A ;键号送P3口显示LJMP MAIN ;转MAIN进行下一次等待扫描;*********延时函数***************************** DELAY: MOV R7,#2DELAY1: MOV R6,#100DELAY2: MOV R5,#200DELAY3: DJNZ R5,DELAY3DJNZ R6,DELAY2DJNZ R7,DELAY1RETEND3、运行、调试程序和结果检查⑴采用单步,设置断点等方法,观察程序走向是否正确;⑵连续运行程序,依次按动数字键观察LED的显示是否相符。

at89c51的工作原理AT89C51是一款基于8位单片机的芯片,它采用CMOS技术,具有51系列特有的功能和特点。

它由中央处理器单元(CPU)、存储器、计时器/计数器、输入/输出(I/O)端口等组成。

AT89C51的工作原理如下:1. 程序存储器(FLASH):AT89C51具有4KB的程序存储器,用于存储程序指令和数据。

CPU从程序存储器中读取指令,并按照指令进行相应的操作。

2. 数据存储器(RAM):AT89C51具有128字节的数据存储器,用于存储程序运行中的数据和临时变量。

3. 输入/输出(I/O)端口:AT89C51具有4个I/O端口(P0、P1、P2、P3),可连接外部设备,如LED灯、按键、传感器等。

CPU通过I/O端口与这些外部设备进行数据的输入和输出。

4. 中央处理器单元(CPU):AT89C51的CPU包括ALU(算术逻辑单元)、寄存器、控制单元等。

ALU用于执行算术和逻辑运算,寄存器用于存储运算结果和中间数据,控制单元用于控制和协调各个部件的工作。

5. 计时器/计数器:AT89C51具有两个16位定时器/计数器(T0、T1),用于产生精确的时间延迟或进行计数。

它们可以用来测量时间、控制外设的工作等。

6. 时钟源:AT89C51需要外部提供时钟信号,以确定指令的执行速度。

它支持多种时钟源,如晶体振荡器、RC振荡器等。

在工作时,AT89C51首先从程序存储器中读取指令,然后根据指令执行相应的操作,如进行算术运算、逻辑判断、数据存储与读取等。

同时,它还可以通过I/O端口与外部设备进行数据交互,实现各种功能。

整个工作过程由时钟信号驱动,时钟信号的频率决定了指令的执行速度。