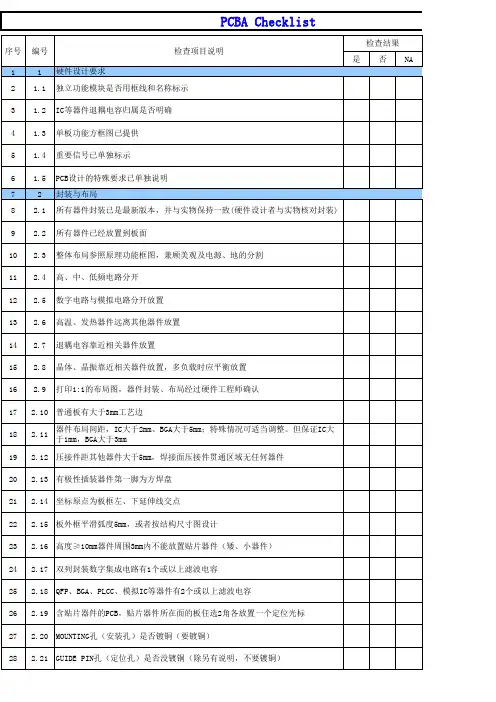

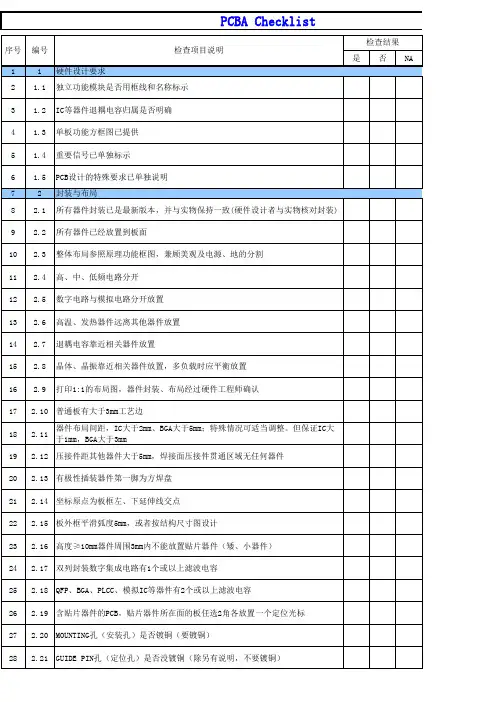

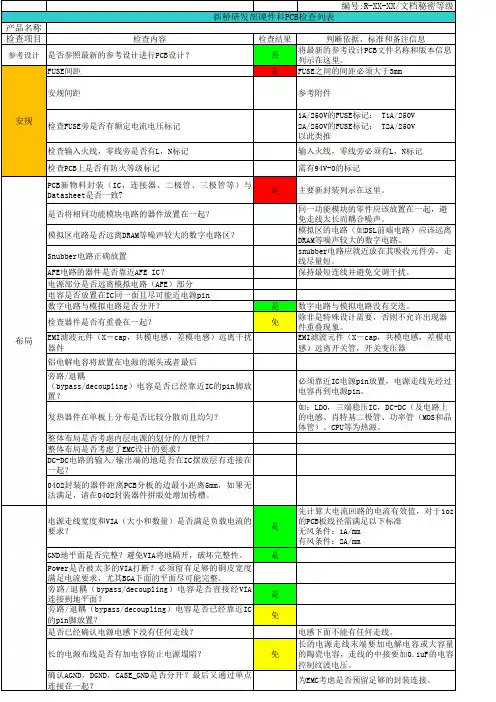

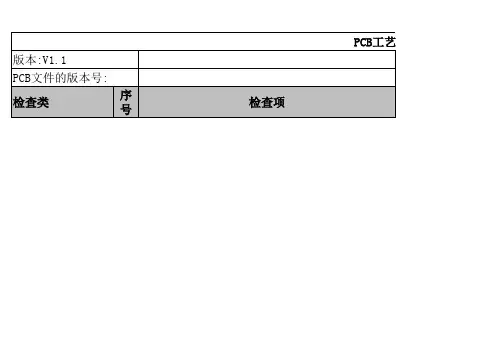

很全面的PCB_checklist_表格

- 格式:xlsx

- 大小:29.83 KB

- 文档页数:5

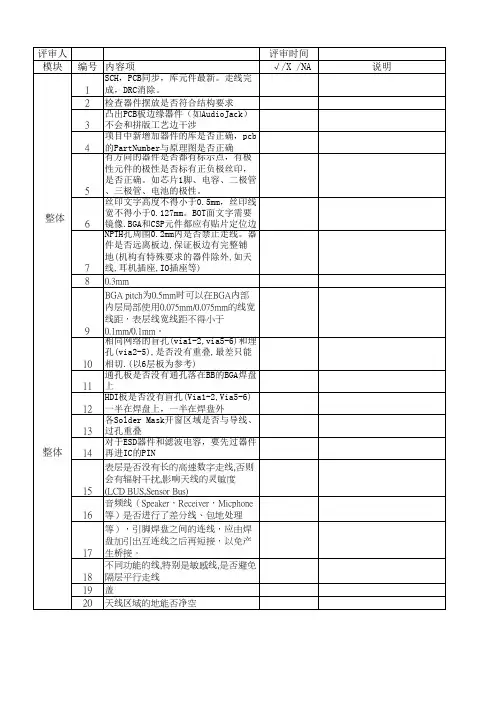

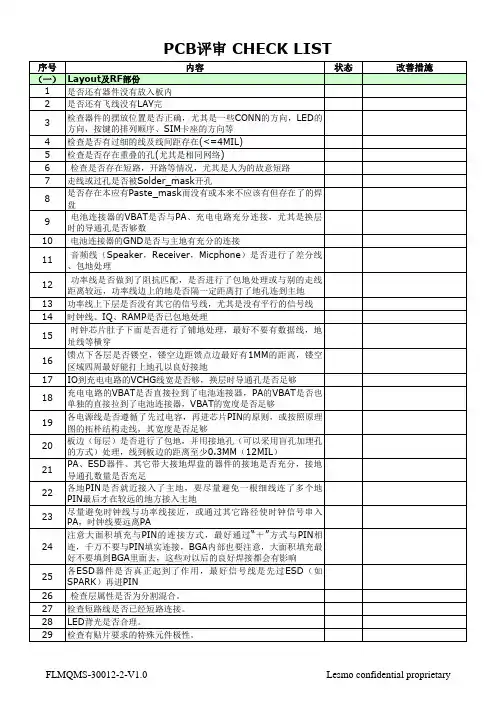

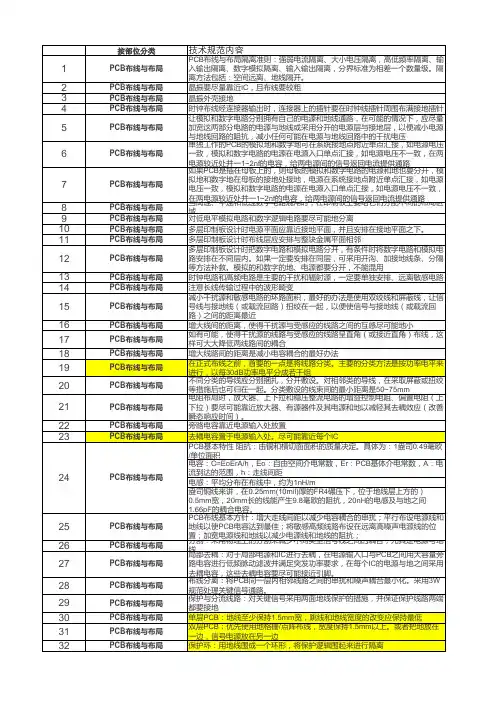

RF Switch的接地pin是否有就近打VIA到地?是PA的接地Pin是否有用铜皮实铺,并就近打VIA到地?是必须用铜皮实铺,并就近打VIA到地PA芯片的接地PAD是否有打9个或以上的VIA到地?是RF的模块是否远离SDRAM模块?是RF的TX回路元件是否远离RX回路元件?免RF的TX回路必须远离RX回路,避免干扰。

内置天线的限制区内不能有放置任何金属器件否2根内置天线的情况下天线的隔离度是否合理?是需要天线场型图仿真数据RF天线Jack的位置是否合适?是RF Cable 出线与板边垂直时,Jack 不能太靠近板边,否则RF Cable 出线容易与塑胶外壳干涉。

同时RF Cable 出线不能直对螺柱或其它高的器件,否则RF Cable 出线会和螺柱或其它高的器件干涉。

RF天线Jack周围5mm范围内是否有元器件?否 1.RF 天线Jack 需要用烙铁焊接天线,如果周围有SMD 器件,容易被烙铁碰掉,如果有DIP器件,容易档到烙铁,造成焊接困难。

内置天线射频线走线是否远离DSL RX滤波电路?免内置天线及射频线线离RX 滤波电感太近,会影响DSL性能PCB天线离晶体是否足够远?免PCB 天线离晶体太近会影响时钟信号,距离1cm以上检查是否采用了最新的PCBA结构图纸?是将最新的参考文件放在这里。

检查是否按照最新产品需求规格书设计是重点为LED顺序,接口顺序,雷击要求。

检查USB 连接器的缩进方式是否正确?是USB Device 连接器通常与后面板平齐,而USB Host连接器通常内缩到后面板内侧。

检查JTAG和串口连接器的放置是否方便测试?是重复检查特殊连接器件的1pin是否正确?放DATASHEET在这里机构上禁止放置器件的区域是否放置了器件?否禁止放置器件的区域:如螺丝孔禁布区机构上限高的区域是否放置了超高的器件?否限高区域器件要比限高至少矮2mm (必须留这个余量,器件在焊接时会浮高)。

仔细检查大器件的高度限制是否满足要求将大器件高度列示在备注栏确认一些螺丝孔的接地是否正确?如MinPCI插槽,PCMCIA插槽…是否对所有兼容模具进行3D评估是所有I/O接口器件及LED灯的位置是否正确?是特别注意:通常LAN RJ45与LAN LED 灯是平行对应关系。

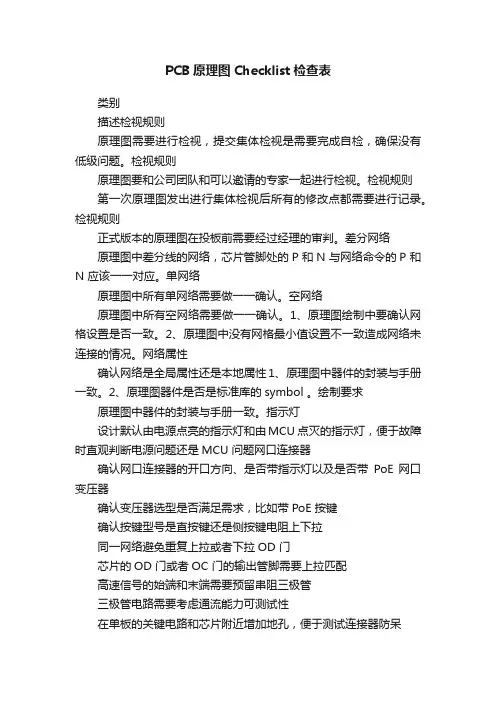

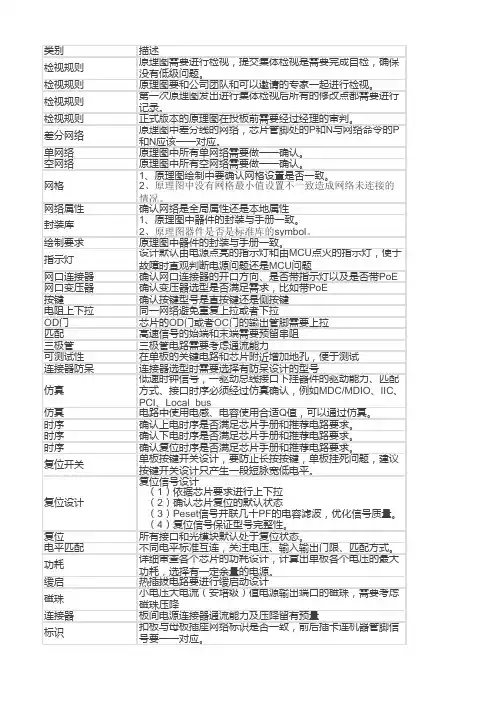

PCB原理图Checklist检查表类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

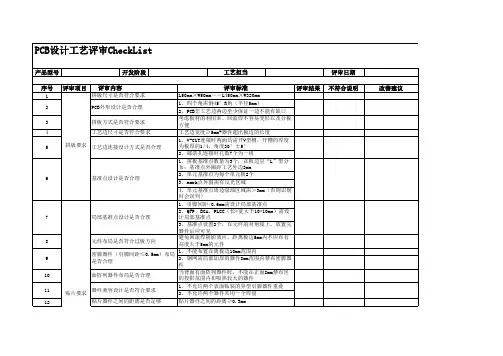

PCB CHECK LIST(讨论稿)一.布局方面:Check Approval□□ 1.产品外形尺寸,接口位置,安装孔的尺寸和位置符合要求(定位孔或非接地的安装孔需设置为非金属化孔)。

导线、功能焊盘应为圆角矩形,建议尺寸为2mm×3mm,在允许的情况下应采用双面焊盘,并用过孔(15mil)固定,且到板边的距离保持1mm以上。

□□ 2.元器件的摆放不重叠。

□□ 3.元器件的摆放不影响其他元器件的插拔和贴焊。

□□ 4.元器件的摆放应符合限高的要求,不会影响其他器件的贴焊和安装。

如电池盒下方,电池下方,背光板液晶下方等。

□□ 5.MARK点的位置摆放应符合要求:1、MARK点离板边及周围器件3mm 以上。

2、MARK点需放在PCB板对角位置。

3、单板上至少设置两个MARK点,若单板上无法放置MARK点,可在拼板或单板工艺边对角设置2个以上MARK点。

□□ 6.元器件离板边的距离应符合工艺要求:元器件焊盘到传送边的距离大于3mm,到非传送边的距离大于2mm。

□□ 7.体积大,间距小的元器件尽量放在元件面。

如果必须放在焊接面,其离板边的距离要大于等于7mm。

□□ 8.BGA和大于120PIN的QFP器件不能放在焊接面,BGA周围6mm以内不要有体积大插件或贴片器件,以免造成BGA返修困难□□ 9.有极性器件的摆放方向要尽可能一致。

□□ 10.相邻贴片器件的焊盘最少相距30mil。

BGA内部或背面密度大的地方可以放宽到25mil。

□□ 11.对于插拔时受力比较大的元器件,比如变压器引脚,热敏,压敏电阻的焊盘等,器件引脚直径与PCB 焊盘孔径及焊盘直径的对应□□插座)焊盘保持2mm以上,同时保持液晶(多PIN插座)引脚平行方向无器件阻挡,以利于焊接。

□□ 13.靠板边的热敏电阻或其他易倒伏器件,尽量放置于引线外围,以免造成加工不良□□ 14.与新结构配合的PCB要打印出1:1的图纸与结构比对,或者将PCB 转化为CAD支持的格式,请结构人员协助比对。

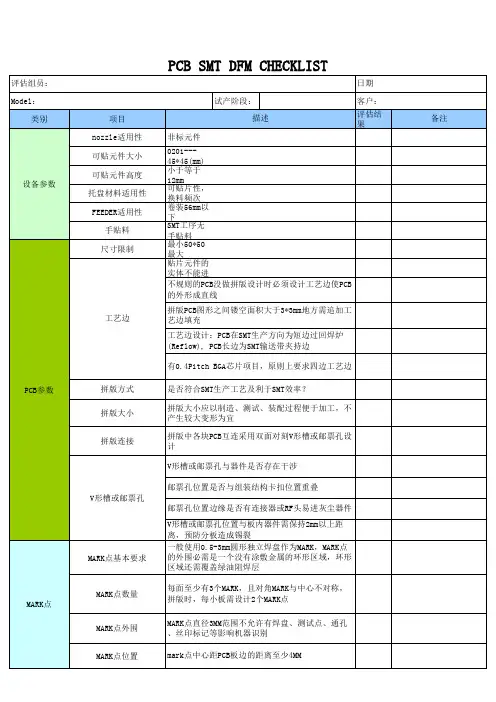

23过炉传送方向规定11234512345123457有SMD器件的PCB必须设置全局MARK点,数量要保证4个;两面有贴片器件的PCB,两面都必须设置MARK点;安装孔及定位孔设计较小的SMD元器件是否尽量放置在先进入焊料位置,利于去除波峰尽量将有极性零件按同方向排列,避免极性插反;波峰焊接设计,孔壁采用非金属化孔设计;波峰焊接的SOIC、QFP零件必须在锡流的末端设置盗锡用的工艺焊波峰焊面IMD和SMD的距离要保证如下:高度低于1.0mm的SMD元件,与器件通过孔的焊盘边沿距离保证在3.0mm或以上;高度在1.0mm至3.5mm的SMD元件,与器件通孔的焊盘边沿距离保证波峰焊接的PCB Bottom Layer是否放置QFP、PLCC、BGA和小间距S引脚数多、引脚间距小的SMD、BGA等器件(管脚中心距≤0.5 mm的BGA器件),对角上必须增加两个专用MARK点;插装元器件的管脚方向是否平行于锡流方向,利于去除波峰焊接的螺丝孔应以NPTH的方式设置,使用小通孔导通,BOTTOM面不能有大在PCB板靠近四个角部位,设计至少三个非金属化定位孔(含安装孔插件料件是否尽可能采用波峰焊焊接设计;器件布局在加工工艺上的要求MARK点设计定位孔尺寸为φ2mm以上;安装孔位号H开头(如H1,H2,…),便于写安装工艺说明;热焊接特性差的器件要明确;是否在工艺边或合适的位置标示设计时考虑的焊接传送方向(通常6器件焊接方式MARK点距离PCB边缘或工艺边至少5mm且处在对角上;完整的MARK点由标记点和空旷区域组成,空旷区域(不能有阻焊油足r=2R(R为MARK点半径),MARK点实心圆直径为1.0mm。

波峰焊面,高的器件要不影响小器件的焊接,SMD的引脚组要平行P波峰焊面,SMD元件的最大高度为3.5mm或以下,禁止出现高度3.5器件布局在加工工91011121314151612345678910111213注意事项光耦正下方不能有其它网络走线经过;走线或铜箔边是否有直角或锐角;易受干扰之线路周围是否已被信号地GND包覆;电源层、地层大面积铺铜箔是否有孤岛、通道狭窄现象;单点接地的位置和连接方式是否合理;IC下方是否已铺上地铜箔;长过孔和直径2.5过孔仅当固定部份.电气导通应当由VIA构成.走线设计检查需要接地的金属外壳器件是否正确接地;最小铜线宽度:控制板:信号线:0.2mm,電源・地线:0.2mm 电源板信号线:0.25mm,電源・地线:0.25mm 变压器、电感,光耦合器件、电源模块下面是否尽量不穿线;VIA near connector:VIA hole shall not lay right under resin adhering to PCB,VIA that is near cless) shall be coated by resist如果电源引线切换到其它层,VIA过孔需有2个或以上.主回路电解电容之下方除负端线路外,不能有其它线路经过;多层PCB板通过通孔的直径连接到内部层每一信号线TRACE之上下层切换次数是否在3次以内.铜线间最小间隔:控制板为0.2mm,电源板为0.25mm PCB板上所有线路是否与线路图完全吻合,无断线或错误情形;同一条布线宽度是否一致,无忽大忽小之情形;到IC的信号线/电源线,尽量不经过过孔直接连接到去耦/滤波电容来自VIA过孔走线应有泪滴形状.2.5mm或以上的通过孔以及长孔要附加上VIA导通孔导通孔不能放置在树脂涂覆PCB板上的正下方、FR5、聚四氟乙容heck point直径连到内部层(通常用箭头线标示);阻焊油、走线、元器件和任何标记)的半径必须满1.0mm。

自审结果审核结果结论说明新器件封装是否与实物一致是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]极性器件有方向标示是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]所有器件均有明确标识,且字体大小整齐是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]不对称元件的原理图和PCB封装是否校对,管脚顺序是否一致(如三极管)是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]PCB实际尺寸、定位器件位置等与工艺结构要素图吻合是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]各种需加的附加孔无遗漏,且设置正确是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]安装孔的大小是否满足要求是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]拨码开关、复位器件,指示灯等位置是否合适,不与拉手条或其他器件冲突,且放在元件面是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]发热元件及外壳裸露器件不能紧邻导线和热敏元件,其他器件也应适当远离是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]同类型有极性插装元器件X、Y向各自方向相同是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]高器件之间无矮小器件,且高度≥10mm器件之间5mm内不能放置贴片器件和矮、小的插装器件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]器件布局间距,表面贴装器件大于0.7mm、IC大于2mm、BGA大于5mm 是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]接插口尽量分布在PCB的四周是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]丝印是否摆放整齐,无重叠,不压焊盘,芯片焊接后不被覆盖是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]常插拔的器件3mm周围是否有表贴器件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]TVS管要在电路的最外端靠近加插件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电解电容不可触及或靠近发热元件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]布局设计3结构设计2检查项目PCB投板评审Check List V1.0PCB版本号: 所属项目:设计者: 评审人: 评审花费时间: 评审日期:注: 评审结论为“否”需在“结论说明”中注明内容实例,结论为“免”需在“结论说明”中注明理由1器件封装计线5。