Cy7c68013 的win7 驱动和SlaveFifo例程

- 格式:docx

- 大小:47.68 KB

- 文档页数:3

CY7C68013与FPGA接口的Verilog HDL实现0 引言USB(通用串行总线)是英特尔、微软、IBM、康柏等公司1994年联合制定的一种通用串行总线规范,它解决了与网络通信问题,而且端口扩展性能好、容易使用。

最新的USB2.0支持3种速率:低速1.5 Mbit/s,全速12 Mbit/s,高速480 Mbit/s。

这3种速率可以满足目前大部分外设接口的需要。

本文介绍了目前使用较多的USB2.0控制器CY7C68013芯片与FPGA(现场可编程门阵列)芯片接口的Verilog HDL(硬件描述语言)实现。

本系统可扩展,完全可用于其他高速数据采集系统中。

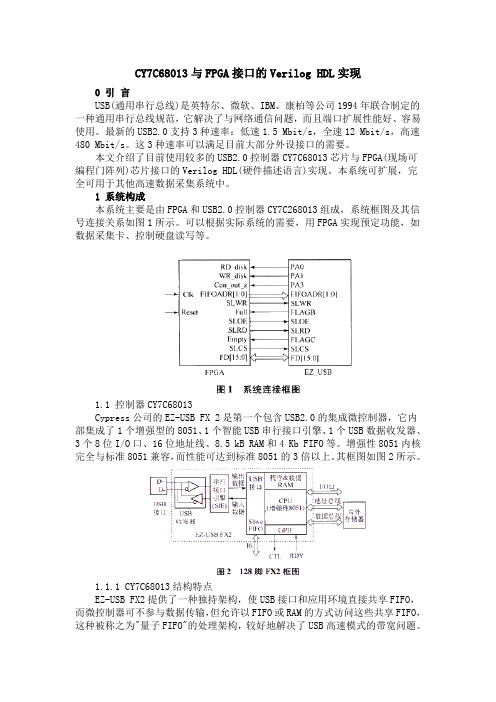

1 系统构成本系统主要是由FPGA和USB2.0控制器CY7C268013组成,系统框图及其信号连接关系如图1所示。

可以根据实际系统的需要,用FPGA实现预定功能,如数据采集卡、控制硬盘读写等。

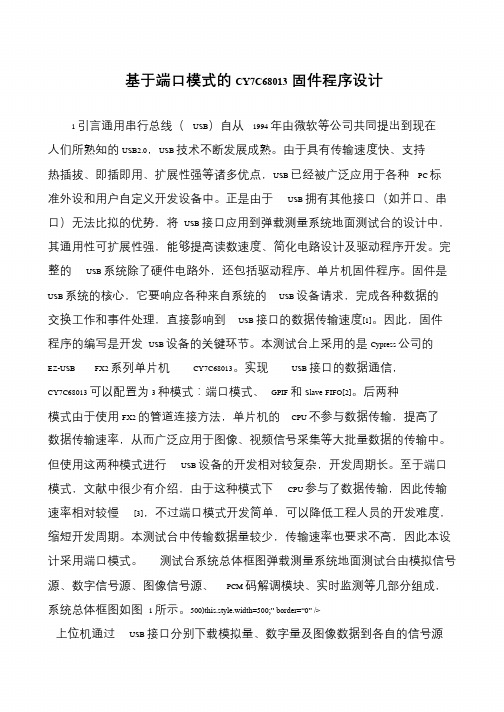

1.1 控制器CY7C68013Cypress公司的EZ-USB FX 2是第一个包含USB2.0的集成微控制器,它内部集成了1个增强型的8051、1个智能USB串行接口引擎、1个USB数据收发器、3个8位I/O口、16位地址线、8.5 kB RAM和4 Kb FIFO等。

增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3倍以上。

其框图如图2所示。

1.1.1 CY7C68013结构特点EZ-USB FX2提供了一种独持架构,使USB接口和应用环境直接共享FIFO,而微控制器可不参与数据传输,但允许以FIFO或RAM的方式访问这些共享FIFO,这种被称之为"量子FIFO"的处理架构,较好地解决了USB高速模式的带宽问题。

FX2芯片在数据传输时主要利用了4 kB的FIFO,分为7个端点:EPOIN&OUT、EP1IN、EP1OUT、EP2、EP4、EP6和EP8。

其中EPO、EPlIN和EP1OUT是3个64 B 的缓存,只能被固件访问,EP0是一个默认的数据输入输出端口缓存;EP1IN和EP1OUT是单独的64 B缓存,呵以配置这些端点为块传输、中断传输或同步传输;端点2、4、6、8是大容量高带宽的数据传输端点,可以配置为各种带宽以满足实际需要,端点2、4是输出端点,端点6、8是输入端点。

SlaveFIFO模式下CY7C68013和FPGA的数据通信马俊涛;李振宇【期刊名称】《中国传媒大学学报(自然科学版)》【年(卷),期】2009(016)002【摘要】介绍了支持USB2.0协议的接口芯片CY7C68013,利用芯片的SlaveFIFO从机模式,实现了FPGA和PC之间的数据传输并详细介绍在SlaveFIFO 模式下CY7C68013和FPGA之间数据传输的软硬件设计.%USB2.0 technology provides a flexible and highly efficient hi-directional data channel between periph-erals and the host. This paper introducers an interface chipCY7C68013 supporting USB2.0 protocol. The design realises data transmission between FPGA and PC based on SlaveFIFO mode of the chip and introduces the soft and hardware of the design.【总页数】7页(P38-44)【作者】马俊涛;李振宇【作者单位】中国传媒大学,广播电视数字化工程中心,北京,100024;中国传媒大学,广播电视数字化工程中心,北京,100024【正文语种】中文【中图分类】TN911【相关文献】1.DSP和FPGA下的数据通信方案设计 [J], 许智勇;周炜2.slaveFIFO模式下USB和FPGA的数据通信 [J], 周莹;邹连英3.Ports模式下CY7C68013和FPGA的数据通信 [J], 袁卫;赵小明;张建奇4.CY7C68013A端口模式下数据传输模块的设计 [J], 刘正发;韦飞;冷双;王永松5.EPP模式下的并口与FPGA的高速数据通信 [J], 谢庭军;刘少君;黄道平因版权原因,仅展示原文概要,查看原文内容请购买。

基于端口模式的CY7C68013固件程序设计1 引言通用串行总线(USB)自从1994 年由微软等公司共同提出到现在人们所熟知的USB2.0,USB 技术不断发展成熟。

由于具有传输速度快、支持热插拔、即插即用、扩展性强等诸多优点,USB 已经被广泛应用于各种PC 标准外设和用户自定义开发设备中。

正是由于USB 拥有其他接口(如并口、串口)无法比拟的优势,将USB 接口应用到弹载测量系统地面测试台的设计中,其通用性可扩展性强,能够提高读数速度、简化电路设计及驱动程序开发。

完整的USB 系统除了硬件电路外,还包括驱动程序、单片机固件程序。

固件是USB 系统的核心,它要响应各种来自系统的USB 设备请求,完成各种数据的交换工作和事件处理,直接影响到USB 接口的数据传输速度[1]。

因此,固件程序的编写是开发USB 设备的关键环节。

本测试台上采用的是Cypress 公司的EZ-USB FX2 系列单片机CY7C68013。

实现USB 接口的数据通信,CY7C68013 可以配置为3 种模式:端口模式、GPIF 和Slave FIFO[2]。

后两种模式由于使用FX2 的管道连接方法,单片机的CPU 不参与数据传输,提高了数据传输速率,从而广泛应用于图像、视频信号采集等大批量数据的传输中。

但使用这两种模式进行USB 设备的开发相对较复杂,开发周期长。

至于端口模式,文献中很少有介绍,由于这种模式下CPU 参与了数据传输,因此传输速率相对较慢[3],不过端口模式开发简单,可以降低工程人员的开发难度,缩短开发周期。

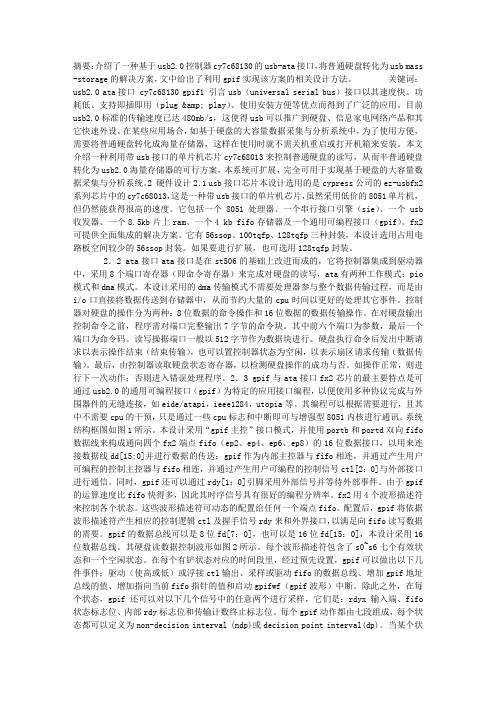

本测试台中传输数据量较少,传输速率也要求不高,因此本设计采用端口模式。

测试台系统总体框图弹载测量系统地面测试台由模拟信号源、数字信号源、图像信号源、PCM 码解调模块、实时监测等几部分组成,系统总体框图如图 1 所示。

500)this.style.width=500;”border=“0” />上位机通过USB 接口分别下载模拟量、数字量及图像数据到各自的信号源。

【博文连载】CY7C68013同步FIFO配置在VIP Mini开发板资料包08_USB_Keil_Project目录下,Bingo 提供了CY7C68013的同步FIFO配置工程,以及其他的一些功能。

软件版本为Keil UVision 4.73.00,C51V95200。

首先介绍一下68013的Slave FIFO,对于CY7C68013的通信接口而言,最主要的有GPIF 与Slave FIFO。

Slave FIFO模式是FX2最常用的模式。

芯片工作于Slave FIFO模式下,该芯片就像一个USB FIFO。

一端接USB口,另外一端就是一个简单的FIFO接口。

USB的数据直接从上位机传递到该FIFO中,用户可以直接用现成的驱动程序和固件程序进行开发,省去了很多熟悉USB协议和驱动开发的工作。

Slave FIFO通过内部的FIFO 乒乓操作,实现数据的实时传输,框图如下所示:在Slave FIFO模式,68013与处理器只需要如下一个信号的链接,通过简单的片选,写入/读取实现,别可以实现数据的双向通信。

全功能接口如下所示:USB_Camera_Demo工程如下所示,我们主要关心的为USB_Camera_Demo.c、intr.c,其他内容Bingo已经完整的整理封装好。

关于同步FIFO的配置,详见USB_Camera_Demo.c,这里给出最重要的几个寄存器的介绍,请同步参照《FX2+TechRefManual》《USB68013_slave_fifo说明文档》寄存器配置手册。

手册Page342如下图所示:其中EF为EMPTY标志,FF为FULL标志:备注:FLAGA = PF;FLAGB = FF;FLAGC = EF;FLAGD = EP2PF,默认由FIFOADDR选择。

摘要:介绍了一种基于usb2.0控制器cy7c68130的usb-ata接口,将普通硬盘转化为usb mass -storage的解决方案,文中给出了利用gpif实现该方案的相关设计方法。

关键词:usb2.0 ata接口 cy7c68130 gpif1 引言usb(universal serial bus)接口以其速度快、功耗低、支持即插即用(plug & play)、使用安装方便等优点而得到了广泛的应用。

目前usb2.0标准的传输速度已达480mb/s,这使得usb可以推广到硬盘、信息家电网络产品和其它快速外设。

在某些应用场合,如基于硬盘的大容量数据采集与分析系统中,为了使用方便,需要将普通硬盘转化成海量存储器,这样在使用时就不需关机重启或打开机箱来安装。

本文介绍一种利用带usb接口的单片机芯片cy7c68013来控制普通硬盘的读写,从而半普通硬盘转化为usb2.0海量存储器的可行方案,本系统可扩展,完全可用于实现基于硬盘的大容量数据采集与分析系统。

2 硬件设计2.1 usb接口芯片本设计选用的是cypress公司的ez-usbfx2系列芯片中的cy7c68013,这是一种带usb接口的单片机芯片,虽然采用低价的8051单片机,但仍然能获得很高的速度。

它包括一个8051处理器、一个串行接口引擎(sie)、一个usb 收发器、一个8.5kb片上ram、一个4 kb fifo存储器及一个通用可编程接口(gpif)。

fx2可提供全面集成的解决方案。

它有56ssop、100tqfp、128tqfp三种封装,本设计选用占用电路板空间较少的56ssop封装。

如果要进行扩展,也可选用128tqfp封装。

2.2 ata接口ata接口是在st506的基础上改进而成的,它将控制器集成到驱动器中,采用8个端口寄存器(即命令寄存器)来完成对硬盘的读写,ata有两种工作模式:pio 模式和dma模式。

本设计采用的dma传输模式不需要处理器参与整个数据传输过程,而是由i/o口直接将数据传送到存储器中,从而节约大量的cpu时间以更好的处理其它事件。

红色飓风II开发板USB2FPGA实验指导(ver1.0)Red Logic工作室二〇〇六年四月三日目录第一章FX2特性介绍 (3)1.1介绍 (3)1.2结构 (3)1.3特征 (4)第二章Slave FIFO传输 (5)2.1概述 (5)2.2硬件连接 (5)2.3 Slave FIFO的几种传输方式 (6)2.3.1 同步Slave FIFO写 (6)2.3.2 同步Slave FIFO读 (9)2.3.3异步Slave FIFO写 (11)2.3.4异步Slave FIFO读 (12)第三章寄存器设置 (15)3.1 IFCONFIG (15)3.2 PINFLAGSAB/CD (16)3.3 FIFORESET (17)3.4 FIFOPINPOLAR (18)3.5 EPxCFG (18)3.6 EPxFIFOCFG (19)3.7 EPxAUTOINLENH/L (20)3.8 EPxFIFOPFH/L (21)3.9 INPKTEND (22)3.10 OUTPKTEND (22)3.11 EPxFIFOIE和EPxFIFOIRQ (22)3.12PORTACFG (23)3.13 EPxFIFOBCH EPxFIFOBCL (23)3.14 EP24\68FIFOFLAG (24)3.15其它通用寄存器 (25)第四章同步slave fifo测试操作指南 (26)4.1安装软件包 (26)4.2同步写FIFO测试 (26)4.3同步读FIFO测试 (30)4.4同步读写FIFO测试 (31)第五章红色飓风II开发板USB2FPGA软件设计 (33)5.1 68013固件程序设计 (33)5.2 FPGA源代码设计 (35)第六章USB2FPGA硬件原理图 (37)第七章改板后注意的问题 (37)附录1 版本历史 (39)一.FX2特性介绍1.1介绍Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。

USB接口芯片CY7C68013自动下载固件驱动程序的配置2012-06-02 20:33:44分类:LINUXCY7C68013自动下载固件驱动程序的配置EZ Loader Custom USB Firmware Loader Driver 上面的一串英文是cypress公司的一个文档名称,是讲如何设置的,在这里保留一下,你可以google这个名称,然后找到那个文档读一下。

这里说一下CY7C68013A的C0加载方式是如何实现的。

首先我的系统是XP,系统装好了WINDDK,VC6.0.1,你要有一个CY7C68013A的开发板,2,安装CYPRESS的USB控制面板软件,它里面也包含了基本的驱动和一些固件例程。

我用的是如图所示的开发包,这是第一个版本,好像,现在还有2个新的版本。

我这里只是使用这个版本。

安装以后目录如下然后到drivers目录3,把EZLOADER文件夹,EZUSBDRV文件夹,EZUSBW2K.INF文件,这3个复制到另外的一个文件夹,我这里就直接放在C盘了。

4,从开始菜单,进入到WINDDK的编译环境,是DOS界面,启动它。

到c:\ezloaderok目录目录下文件有:5,用记事本打开Sources文件,将其中的一段修改如下,to build那个英文说得很明白了。

然后回到DOS界面6,输入build –c,如果没有错误编译成功的话,界面如下Ezloader.sys,就是下载固件程序到cy7c68013RAM的驱动文件,说白点就是,它是C0加载方式的,第一个驱动文件,功能就是将固件程序下载到RAM中。

这里差点漏了说,在这之前,我们要把固件程序也就是HEX文件转化为.c 的文件,将这个.c 文件中的那个数组,替换fireware.c 中对应的数组,如图7,成功没有那么容易,我在编译的时候出现了这样的错误,关于USHORT,类型不匹配的错误,找到相应的行,将数据变量强制类型转换,就好了。

之前用的是xp环境,用的红色飓风开发板,现在自己做的板子,改成了win7系统,可是原来的eZ-USB控制面板不能用了,搜了一下cypress的官方驱动,Cypress Suite USB 3.4.7,可以支持XP和win7系统。

连上后,按照driver文件夹下面的CyUSB.pdf文件,修改Cypress Suite USB 3.4.7\Driver\bin\wlh\x64下面的cyusb.inf文件,用记事本打开,将里面VID_XXXX&PID_XXXX改成VID_04B4&PID_8613(在设备管理器中可以查看属性,看到这两个16进制数),注意别忘了把这几行前面的注释号“;”去掉,否则认为这一行被注释了哦。

下面的文件是我的CY7C68013的inf文件。

这样系统就可以识别到USB设备了。

但是原来的例程SlaveFIFO不能用了,下载.hex文件之后,识别到SlaveFIFO设备,不能装驱动。

由于对这个USB芯片的固件不熟,研究固件编写短期内搞不定。

于是在Cypress 官方网站上找到了例程AN63787,是关于8bit模式下的slavefifo例程,但是我的FPGA配置的是16位模式,明显看到例程中少了一半字节的数据。

下面只能自己改例程了。

首先下载**版的keil uVision2,/f/12062296.html?from=like更改C:\Cypress\Cypress Suite USB 3.4.7\Firmware\Bulkloop下面的keil工程,用原来红色飓风自带的固件源代码配置进行更改,将 bulkloop.c中TD_Init函数用红色飓风如下TD_Init函数替换,void TD_Init( void ){ // Called once at startup//时钟设置//CPUCS = 0x02; //12MHZ CLKOUT ENALBE//CPUCS = 0x0a; //24MHZ CLKOUT ENALBECPUCS = 0x12; //48MHZ CLKOUT ENALBEIFCONFIG =0x43;//使用外部时钟,IFCLK输入不反向SYNCDELAY;EP2CFG=0xA0; //需要设定为四缓冲,每个缓冲区大小为512字节SYNCDELAY;EP4CFG=0x00;SYNCDELAY;EP6CFG=0xE0;SYNCDELAY;EP8CFG=0x00;SYNCDELAY;FIFORESET = 0x80; // activate NAK-ALL to avoid race conditionsSYNCDELAY; // see TRM section 15.14FIFORESET = 0x02; // reset, FIFO 2SYNCDELAY; //FIFORESET = 0x06; // reset, FIFO 6SYNCDELAY; //FIFORESET = 0x00; // deactivate NAK-ALLSYNCDELAY;PINFLAGSAB = 0xE6; // FLAGA - fixed EP6PF, FLAGB - fixed EP6FFSYNCDELAY;PINFLAGSCD = 0xf8; // FLAGC - fixed EP2EF, FLAGD - reservedSYNCDELAY;PORTACFG |= 0x00; //0x40; // SLCS, set alt. func. of PA7 pinSYNCDELAY;FIFOPINPOLAR = 0x00; // all signals active low,SYNCDELAY;OEA|=0x0F;//小于64字节有效//EP6FIFOPFH=0x00; //DEIS PKSTAT PK2 PK1 PK0 0 PFC9 PFC8//EP6FIFOPFL=0x40; //PFC7 PFC6 PFC5 PFC4 PFC3 PFC2 PFC1 PFC0// handle the case where we were already in AUTO mode...EP2FIFOCFG = 0x01; // AUTOOUT=0, WORDWIDE=1SYNCDELAY;EP2FIFOCFG = 0x11; // AUTOOUT=1, WORDWIDE=1SYNCDELAY;EP6FIFOCFG = 0x09; // AUTOIN=1, ZEROLENIN=0, WORDWIDE=1SYNCDELAY;//IO设置PORTCCFG=0x00;PORTECFG=0x00;OEC=0x00;OEE=0xff;//串口初始化// PA3=0;PA0=1;enum_high_speed=FALSE;}编译生成.hex文件,用EZ-USB控制面板下载到USB芯片中,然后提示找到设备Bulkloop Device,自动安装驱动,点击get piples,Pipe: 0 Type: BLK Endpoint: 2 OUT MaxPktSize: 0x200Pipe: 1 Type: BLK Endpoint: 4 OUT MaxPktSize: 0x200Pipe: 2 Type: BLK Endpoint: 6 IN MaxPktSize: 0x200Pipe: 3 Type: BLK Endpoint: 8 IN MaxPktSize: 0x200选择: BLK Endpoint: 6 IN ,点击传输,这是我用24bitAD芯片采集数据的结果,每采集两次,放入3个数据进FIFO,数据正确但是现在传输速度测试的VC6.0程序还不能用,估计还是因为win7的某些不兼容吧,以后再试。

CY7C68013软件硬件调试手册一平台准备1,硬件平台:购买的CY7C68013A-56PVXC最小系统板,连接AT24C128 EEPROM芯片,连接电路如下,看参考资料有说明说硬件上不同容量的EEPROM接法是不一样的,否则烧写之后也无法启动。

大容量EEPROM的A0管腿需要上拉,另外需要注意的是SCL SDA需要上拉,否则也会出现读取问题。

板子上J2是个跳线帽,实际测试的时候发现连上J2下载有问题,取下J2下载和执行程序正常。

(更改PID VID 不能找到驱动需要更换回来时插上J2复位,能找到驱动,再拔掉J2,然后下载IIC,便能再次回复上次的VID,PID了)2,软件开发工具新版fx2lp.Exe安装后在C盘生成cypress的文件夹包含cyconsole软件,驱动和源代码。

VC6.0和cyapi.h,cyapi.lib进行软件开发。

KEIL C51 V9.0以上2,编译固件用KEIL写好固件程序后在option/User/run1中添加c:\cypress\usb\bin\hex2bix -i -f 0xC2 slave.iic slave.hex并打钩-i 表示输出文件,也就是IIC文件-o 表示输入文件,也就是HEX文件-f 表示68013A发送PID/VID的方式C0,即从EEPROM上读取PID,VID不执行程序。

C2表示从EEPROM上读取PID,VID和执行程序。

PID VID在固件程序中DSCR.A51中定义好了。

-v 表示VID的BCD码-p 表示PID的BCD码下载程序:通过USB连接到计算机后,通过Cypress USB Console即可烧写。

打开EZ-USB Interface,点击Lg EEPROM,然后选择刚才生成好的IIC文件可以,下载后重新打开板子电源。

二固件编写我们的固件主要基于官方的例程AN61345,芯片工作于slave-fifo模式,(对于FPGA应该由芯片产生IFCLK,工作于同步模式,对于低速外设应该工作于异步模式(芯片自己产生IFCLK))内部构建2个bulk传输,利用端口2进行out 传输和端口6进行in传输,另外一些参数的设定使用端口0进行控制传输。

CY7C68013软件硬件调试手册一平台准备1,硬件平台:购买的CY7C68013A-56PVXC最小系统板,连接AT24C128 EEPROM芯片,连接电路如下,看参考资料有说明说硬件上不同容量的EEPROM接法是不一样的,否则烧写之后也无法启动。

大容量EEPROM的A0管腿需要上拉,另外需要注意的是SCL SDA需要上拉,否则也会出现读取问题。

板子上J2是个跳线帽,实际测试的时候发现连上J2下载有问题,取下J2下载和执行程序正常。

(更改PID VID 不能找到驱动需要更换回来时插上J2复位,能找到驱动,再拔掉J2,然后下载IIC,便能再次回复上次的VID,PID了)2,软件开发工具新版fx2lp.Exe安装后在C盘生成cypress的文件夹包含cyconsole软件,驱动和源代码。

VC6.0和cyapi.h,cyapi.lib进行软件开发。

KEIL C51 V9.0以上2,编译固件用KEIL写好固件程序后在option/User/run1中添加c:\cypress\usb\bin\hex2bix -i -f 0xC2 slave.iic slave.hex并打钩-i 表示输出文件,也就是IIC文件-o 表示输入文件,也就是HEX文件-f 表示68013A发送PID/VID的方式C0,即从EEPROM上读取PID,VID不执行程序。

C2表示从EEPROM上读取PID,VID和执行程序。

PID VID在固件程序中DSCR.A51中定义好了。

-v 表示VID的BCD码-p 表示PID的BCD码下载程序:通过USB连接到计算机后,通过Cypress USB Console即可烧写。

打开EZ-USB Interface,点击Lg EEPROM,然后选择刚才生成好的IIC文件可以,下载后重新打开板子电源。

二固件编写我们的固件主要基于官方的例程AN61345,芯片工作于slave-fifo模式,(对于FPGA应该由芯片产生IFCLK,工作于同步模式,对于低速外设应该工作于异步模式(芯片自己产生IFCLK))内部构建2个bulk传输,利用端口2进行out 传输和端口6进行in传输,另外一些参数的设定使用端口0进行控制传输。

之前用的是xp环境,用的红色飓风开发板,现在自己做的板子,改成了win7系统,可是原来的eZ-USB控制面板不能用了,搜了一下cypress的官方驱动,Cypress Suite USB 3.4.7,可以支持XP和win7系统。

连上后,按照driver文件夹下面的CyUSB.pdf文件,修改Cypress Suite USB 3.4.7\Driver\bin\wlh\x64下面的cyusb.inf文件,用记事本打开,将里面VID_XXXX&PID_XXXX改成VID_04B4&PID_8613(在设备管理器中可以查看属性,看到这两个16进制数),注意别忘了把这几行前面的注释号“;”去掉,否则认为这一行被注释了哦。

下面的文件是我的CY7C68013的inf文件。

这样系统就可以识别到USB设备了。

但是原来的例程SlaveFIFO不能用了,下载.hex文件之后,识别到SlaveFIFO设备,不能装驱动。

由于对这个USB芯片的固件不熟,研究固件编写短期内搞不定。

于是在Cypress 官方网站上找到了例程AN63787,是关于8bit模式下的slavefifo例程,但是我的FPGA配置的是16位模式,明显看到例程中少了一半字节的数据。

下面只能自己改例程了。

首先下载**版的keil uVision2,/f/12062296.html?from=like

更改C:\Cypress\Cypress Suite USB 3.4.7\Firmware\Bulkloop下面的keil工程,用原来红色飓风自带的固件源代码配置进行更改,将 bulkloop.c中TD_Init函数用红色飓风如下TD_Init函数替换,

void TD_Init( void )

{ // Called once at startup

//时钟设置

//CPUCS = 0x02; //12MHZ CLKOUT ENALBE

//CPUCS = 0x0a; //24MHZ CLKOUT ENALBE

CPUCS = 0x12; //48MHZ CLKOUT ENALBE

IFCONFIG =0x43;//使用外部时钟,IFCLK输入不反向

SYNCDELAY;

EP2CFG=0xA0; //需要设定为四缓冲,每个缓冲区大小为512字节

SYNCDELAY;

EP4CFG=0x00;

SYNCDELAY;

EP6CFG=0xE0;

SYNCDELAY;

EP8CFG=0x00;

SYNCDELAY;

FIFORESET = 0x80; // activate NAK-ALL to avoid race conditions

SYNCDELAY; // see TRM section 15.14

FIFORESET = 0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET = 0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET = 0x00; // deactivate NAK-ALL

SYNCDELAY;

PINFLAGSAB = 0xE6; // FLAGA - fixed EP6PF, FLAGB - fixed EP6FF

SYNCDELAY;

PINFLAGSCD = 0xf8; // FLAGC - fixed EP2EF, FLAGD - reserved

SYNCDELAY;

PORTACFG |= 0x00; //0x40; // SLCS, set alt. func. of PA7 pin

SYNCDELAY;

FIFOPINPOLAR = 0x00; // all signals active low,

SYNCDELAY;

OEA|=0x0F;

//小于64字节有效

//EP6FIFOPFH=0x00; //DEIS PKSTAT PK2 PK1 PK0 0 PFC9 PFC8

//EP6FIFOPFL=0x40; //PFC7 PFC6 PFC5 PFC4 PFC3 PFC2 PFC1 PFC0

// handle the case where we were already in AUTO mode...

EP2FIFOCFG = 0x01; // AUTOOUT=0, WORDWIDE=1

SYNCDELAY;

EP2FIFOCFG = 0x11; // AUTOOUT=1, WORDWIDE=1

SYNCDELAY;

EP6FIFOCFG = 0x09; // AUTOIN=1, ZEROLENIN=0, WORDWIDE=1

SYNCDELAY;

//IO设置

PORTCCFG=0x00;

PORTECFG=0x00;

OEC=0x00;

OEE=0xff;

//串口初始化

// PA3=0;

PA0=1;

enum_high_speed=FALSE;

}

编译生成.hex文件,用EZ-USB控制面板下载到USB芯片中,然后提示找到设备Bulkloop Device,自动安装驱动,点击get piples,

Pipe: 0 Type: BLK Endpoint: 2 OUT MaxPktSize: 0x200

Pipe: 1 Type: BLK Endpoint: 4 OUT MaxPktSize: 0x200

Pipe: 2 Type: BLK Endpoint: 6 IN MaxPktSize: 0x200

Pipe: 3 Type: BLK Endpoint: 8 IN MaxPktSize: 0x200

选择: BLK Endpoint: 6 IN ,点击传输,这是我用24bitAD芯片采集数据的结果,每采集两次,放入3个数据进FIFO,数据正确

但是现在传输速度测试的VC6.0程序还不能用,估计还是因为win7的某些不兼容吧,以后再试。

关于eeprom固件,我采用24LC64,A0脚拉高。

采用如下命令将.hex文件转化为.iic文件:Hex2bix -i -f 0xc2 -v 0x04B4 -p 0x8613 -o bulkloop.iic bulkloop.hex

然后在控制面板中点击Lg EEPROM,将生成的.iic文件下载进去,重新上电,USB加载成功。