西工大数字集成电路实验报告_实验2反相器(上)代码

- 格式:doc

- 大小:356.50 KB

- 文档页数:9

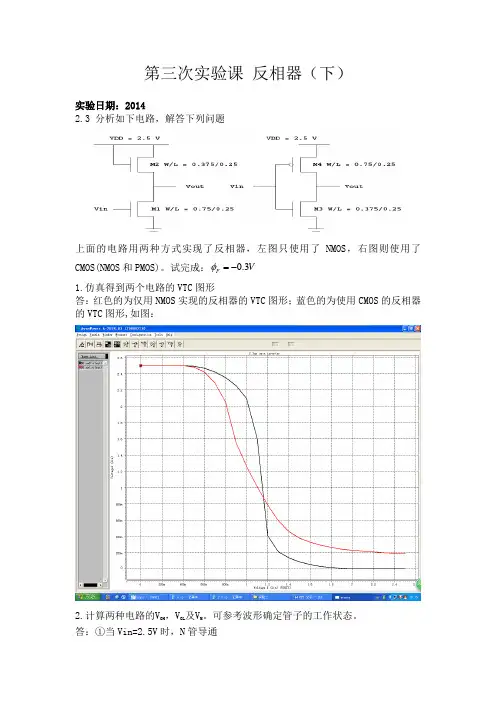

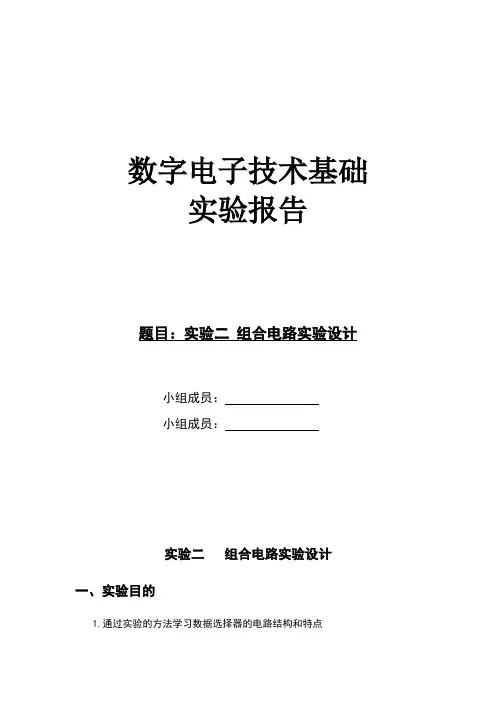

第三次实验课 反相器(下)实验日期:20142.3 分析如下电路,解答下列问题上面的电路用两种方式实现了反相器,左图只使用了NMOS ,右图则使用了CMOS(NMOS 和PMOS)。

试完成:V F 3.0-=φ1.仿真得到两个电路的VTC 图形答:红色的为仅用NMOS 实现的反相器的VTC 图形;蓝色的为使用CMOS 的反相器的VTC 图形,如图:2.计算两种电路的V OH ,V OL 及V M 。

可参考波形确定管子的工作状态。

答:①当Vin=2.5V 时,N 管导通有在体偏置条件下阀值电压公式:)22(0F SB F T T V V V φφγ-+-+=()()()⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=22220'2011'222'OL OL T in n DS DS T GS M M n d DSAT DSAT T DD M M n DSAT V V V V L W k V V V V L W k I V V V V L W k I (M2速度饱和)将下列数据代人VV V A k V V V D SAT n F T 63.0,/10115,3.0,43.026'0=⨯=-==-φ25.075.0,25.0375.01122==M M M M L W L W解得: V V OL 2875.0=当Vin=0V 时,N 管截止,Vout=OH V =2.5V求解M V :当out in V V =时,由于GS DS V V =,M1工作在饱和区此时流过M1(速度饱和)的电流为:()⎥⎥⎦⎤⎢⎢⎣⎡--=22011'1DSAT DSAT T in M M n DSAT V V V V L W k I (1) 流过M2的电流为(速度饱和)()⎥⎥⎦⎤⎢⎢⎣⎡---=2222'2DSAT DSAT T out DD M M n DSAT V V V V V L W k I (2) )22(0F SB F T T V V V φφγ-+-+=(3)M out in SB V V V V ===联立方程解得M V =1.017V②对于CMOS 器件当Vin=0时,V V V out O H 5.2==当Vin=2.5时,V V V out O L 0==求解M V :当out in V V =时,由于GS DS V V =,NMOS 与PMOS 工作在饱和区由于T M D SAT V V V -<,此时已经发生了速度饱和(参考波形)代入,联立解得:将下列数据V V V V V V V V V A k V A k L W k k L W k k V k V k r r V V V r V V V V V V V V k V V V V k DSATp DSATn Tp Tn p n pp p p nn n n DSATnn DSATpp DSAT TP DD DSAT Tn M DSATp Tp DD M DSATp p DSATn Tn M DSATn n 1,63.04.0,43.0,/1030,/101151)2/()2/(0)2/()2/(26'26'''-==-==⨯-=⨯====+++++==---+----M V =1.132315968V3.哪一种结构的反相器的功能性更好,为什么?(噪声容限,再生性,过渡区增益)答:CMOS 反相器更好。

数字电子技术基础实验报告题目:实验二组合电路实验设计小组成员:小组成员:实验二组合电路实验设计一、实验目的1.通过实验的方法学习数据选择器的电路结构和特点2.掌握数据选择器的逻辑功能及其基本应用3.通过实验的方法学习74LS138的电路结构和特点4.掌握74LS138的逻辑功能及其基本应用二、实验要求要求一:参照参考内容,调用 MAXPLUSII 库中的组合逻辑器件74153双四数据选择器和7400与非门,用原理图输入方法实现一位全加器。

(MULTISIM仿真和FPGA 实现)要求二:参照参考内容,调用 MAXPLUSII 库中的组合逻辑器件74138三线八线译码器和7420与非门,用原理图输入方法实现一位全减器。

(MULTISIM仿真和FPGA 实现)要求三:参照参考内容,调用 MAXPLUSII 库中的组合逻辑器件74138三线八线译码器和门电路,用原理图输入方法实现一个两位二进制数值比较器。

(MULTISIM 仿真和 FPGA 实现)三、实验设备(1)电脑一台;(2)数字电路实验箱;(3)数据线一根。

四、实验原理Multisim 的模拟电路编程原理Quartus II的模拟电路编译、波形仿真及目标器件写入的基本应用数字电路逻辑表达式转换的基本知识数据选择器和译码器的电路结构及其特点实验开发板的基本使用知识五、实验内容1、调用 MAXPLUSII 库中的组合逻辑器件74153双四数据选择器和7400与非门,用原理图输入方法实现一位全加器。

(MULTISIM仿真和 FPGA 实现)(1)构建真值表、卡诺图及降维卡诺图真值表:真值表:S1卡诺图:C0卡诺图:降维卡诺图:(2)逻辑表达式变换过程(3)原理图(Multisim和QuartusII中绘制的原理图):Quartus II 中原理图Multisim 中原理图(4)波形仿真:(5)记录电路输出结果2、调用 MAXPLUSII 库中的组合逻辑器件74138三线八线译码器和7420与非门,用原理图输入方法实现一位全减器。

数字集成电路实验报告西北工业大学2014年5月7日星期三实验二、反相器(上)一、分析电路,解答下面的问题。

1. 这个电路是不是反相器,为什么?该门属于有比逻辑,还是无比逻辑,为什么?答:该电路是反相器电路,因为当输入为0时,MOS 管截止,vout 连接到高电位Vdd ,当输入为Vdd 时,输出取决于MOS 管电阻与上面电阻的分压,是一个较低的电位。

该门是一个有比逻辑,因为输出与MOS 管的尺寸有关。

2. 计算出这个电路的VOH VOL 及VIH VIL 。

(计算可先排除速度饱和的可能)答:V V v V O H in 5.20=⇒=v V in 5.2=时,无法判断器件工作状态。

假设NMOS 工作在临界饱和区有:AI V R I vV V V AI V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1说明器件饱和时,同一通路上下电流大小不一致。

那么Vout 必须相应减小使同一通路的电流一致,所以器件必定进入线性区。

进一步求Vol⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L WK I in OL L D OL OL T in D 5.25.2]2)[(2` 6`10115-⨯=K 将,5.0/5.1=LW,43.0=T V 代入kohm R L 75=VVol A I 0.04638 10272.35=⨯=-(注:经过Hspice 仿真结果为0.0356V )当out in V V =时NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`可解得反相器阈值电压===out in M V V V 0.7932V此时 -9.3978V)43.0(875.25,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.6116V ||0.8776V ||g V V V V g V V V M OH MIL M M IH分析电路噪声容限。

一、实验目的1. 理解反相器的工作原理,掌握反相器的设计方法;2. 学习使用模拟电路设计软件,进行反相器电路的搭建与仿真;3. 提高动手实践能力,培养团队协作精神。

二、实验原理反相器是一种基本的逻辑门电路,其功能是将输入信号进行反转输出。

本实验采用CMOS反相器,由P型MOSFET和N型MOSFET组成。

当输入信号为高电平时,P型MOSFET导通,N型MOSFET截止,输出信号为低电平;当输入信号为低电平时,P 型MOSFET截止,N型MOSFET导通,输出信号为高电平。

三、实验仪器与材料1. 实验仪器:示波器、信号发生器、电源、面包板、导线等;2. 实验材料:CMOS集成电路芯片、电阻、电容等。

四、实验步骤1. 设计反相器电路:根据实验要求,设计一个简单的CMOS反相器电路,并绘制电路原理图。

2. 电路搭建:按照电路原理图,在面包板上搭建反相器电路,包括P型MOSFET、N型MOSFET、电阻、电容等元件。

3. 信号输入:使用信号发生器产生不同幅值的正弦波信号,作为反相器的输入信号。

4. 信号采集:使用示波器分别测量反相器的输入信号和输出信号,观察信号的变化。

5. 数据分析:分析反相器的输入输出特性,验证反相器的工作原理。

6. 仿真实验:使用模拟电路设计软件,对反相器电路进行仿真实验,观察仿真结果与实际实验结果是否一致。

五、实验结果与分析1. 实验结果通过实际搭建电路和仿真实验,观察到了以下现象:(1)当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)实际实验和仿真实验结果基本一致,说明实验设计合理,电路搭建正确。

2. 数据分析(1)输入输出特性:反相器的输入输出特性如图1所示。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)电路功耗:反相器的功耗主要来源于电阻和电容的功耗。

在本实验中,电路功耗较小,约为几毫瓦。

六、实验总结1. 通过本次实验,掌握了反相器的工作原理,学会了反相器的设计方法。

一、实验目的:

1、熟悉T-spice的使用,并且熟练掌握。

2、仿真出反相器的输出曲线,并观察它的特性。

二、实验原理:

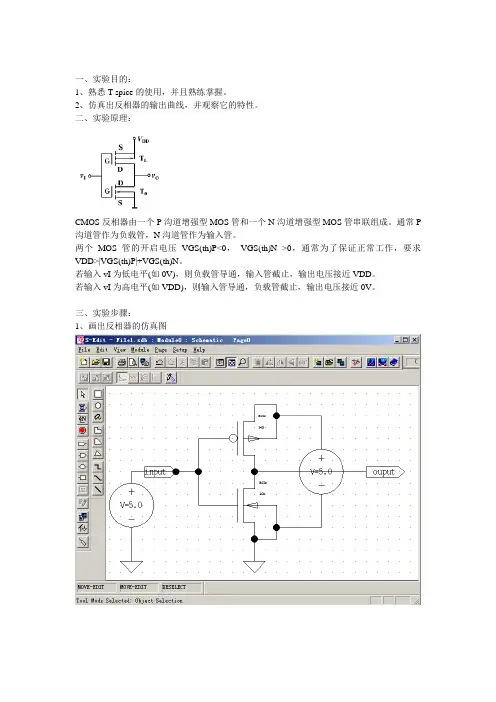

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成。

通常P 沟道管作为负载管,N沟道管作为输入管。

两个MOS管的开启电压VGS(th)P<0,VGS(th)N >0,通常为了保证正常工作,要求VDD>|VGS(th)P|+VGS(th)N。

若输入vI为低电平(如0V),则负载管导通,输入管截止,输出电压接近VDD。

若输入vI为高电平(如VDD),则输入管导通,负载管截止,输出电压接近0V。

三、实验步骤:

1、画出反相器的仿真图

实验小结:

通过这次Hspice仿真反相器的上机实验,我收获颇多。

第一、我更加熟悉了Hspice 仿真环境的使用,对T-spice更加的熟练。

这将对我以后再做其它实验奠定了良好的基础。

第二、以前只在课堂上听老师讲授那些反相器的原理和输出曲线等,但自己的意识当中对反相器的工作还是很疑惑,在做完这个仿真实验后,才恍然大悟,觉得反相器原来就是这么回事。

第三、反相器是我们学习数字集成电路的桥梁,我们后续将会用它进行许多的设计,所以这次实验的重要度是很高的。

我非常的重视这次实验。

哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号:1207010132姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层;(4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层;(7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟;4. 实验结果4.1 nmos版图4.2 pmos版图4.3反相器的版图4.4反相器的spice文件4.5反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号:1207010132姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层;(3) 绘制P Select图层;(4) 绘制Poly图层;(5) 绘制Active Contact图层;(6) 绘制Metal1图层;(7) 设计规则检查;(8) 检查错误;(9) 修改错误;(10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos 组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点;(11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice模拟;4. 实验结果4.1 nmos版图4.2 pmos版图4.3反相器的版图4.4反相器的spice文件4.5反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

数字电子技术基础第三次实验报告一、描述QuartusII软件基本使用步骤①编写Verilog代码,用文本编辑器正确编写源文件,并经modelsim仿真确认该电路设计正确。

②打开QuartusII软件,新建工程New project (注意工程名和设计文件的module名保持一致),选择和开发板一致的FPGA器件型号。

③添加文件,点击file->open,之后选择要添加的文件,并勾选Add file to currentproject.④编译,Start Compilation ,编译源文件(如有错误修改后,重新编译)。

⑤查看电路结构,使用Tool->RTL viewer工具查看电路图结构,是否和预期设计一致。

二、题目代码以及波形分析1.设计一款时钟上升沿触发的D寄存器a)编写模块源码module flipflop(D,Clock,Q);input D,Clock;output reg Q;always@(posedge Clock)Q=D;endmoduleb)测试模块`timescale 1ns/1psmodule tb_flipflop;reg Clock_test;reg D_test;wire Q_test;initialClock_test=0;always #20 Clock_test=~Clock_test;initialD_test=0;always #77 D_test=~D_test;flipflop UUT_flipflop(.Clock(Clock_test),.D(D_test),.Q(Q_test));endmodulec)仿真后的波形截图每当时钟上升沿到来时,触发器把D的信号传给Qd)综合后的RTL图形2.设计一款4bBit具有并行加载功能的移位寄存器编写模块源码a)编写模块源码module muxdff(D0,D1,Sel,Clock,Q);input D0,D1,Sel,Clock;output reg Q;wire D;assign D=Sel?D1:D0;always@(posedge Clock)Q<=D;endmodulemodule shift4(R,L,w,Clock,Q);input [3:0]R;input L,w,Clock;output wire [3:0]Q;muxdff Stage3(w,R[3],L,Clock,Q[3]);muxdff Stage2(Q[3],R[2],L,Clock,Q[2]);muxdff Stage1(Q[2],R[1],L,Clock,Q[1]);muxdff Stage0(Q[1],R[0],L,Clock,Q[0]); endmoduleb)测试模块`timescale 1ns/1psmodule tb_shift4;reg Clock_test;reg L_test;reg w_test;reg [3:0]R_test;wire [3:0]Q_test;initialClock_test=0;always #10 Clock_test=~Clock_test;initialbeginL_test=1;#14L_test=0;//always #14 L_test=~L_test;endinitialw_test=0;always #13 w_test=~w_test;initialR_test=4'b1010;shift4 UUT_shift4(.Clock(Clock_test),.L(L_test),.w(w_test),.R(R_test),.Q(Q_test));endmodulec)仿真后的波形截图L为0时并行加载,数组R为加载时的输入。

数字集成电路设计课程实验报告姓名:班级:学号:指导老师:实验时间:实验地点:实验一:设计一个反相器一、实验目的1、学习及掌握cadence 图形输入及仿真方法;2、掌握基本反相器的原理与设计方法;3、掌握反相器电压传输特性曲线VTC 的测试方法;4、分析电压传输特性曲线,确定五个关键电压OH V 、OL V 、IH V 、IL V 、TH V 。

二、实验内容本次实验主要是利用cadence 软件来设计一基本反相器(inverter),并利用仿真工具Analog Artist(Spectre)来测试反相器的电压传输特性曲线(VTC, Voltage transfer characteristic curves),并分析其五个关键电压:输出高电平OHV 、输出低电平OLV 、输入高电平IHV 、输入低电平ILV 、阈值电压THV 。

1、在cadence 环境中绘制的反相器原理图如图一所示。

值得注意的是应将NMOS 的衬底接地(GND ),而相应的应将PMOS 的衬底接电源(VDD ),这样不仅能消除体效应,而且还能够减弱闩锁效应(在NMOS 实现中并不存在)。

2、在Analog Environment 中,对反相器进行瞬态分析(tran),仿真时间设置为4ns 。

其输入输出波形如图二所示。

三、实验环境 软件:Cadence硬件:计算机四、实验结果由图可以看出:输出高电平5OH V V =、输出低电平0OL V V =、输入高电平 3.15IH V V =、输入低电平 2.24IL V V =、阈值电压 2.66TH V V =。

所以,噪声容限为:2.240 2.24L IL OL NM V V V =-=-= 53.15 1.85H OH IH NM V V V =-=-=实验二:设计一个水位控制器一、设计要求1、给出满足题目要求的电路图;2、根据设计目标,计算各MOS 管的尺寸;3、对电路进行仿真,仿真内容包括:直流输入范围、直流输出范围;4、对结果进行分析。

集成电路集中上机实验报告——反相器、与非门设计学院:专业:姓名:学号:一、实验目的(一)全面了解Schematic设计环境,并学会运用(二)掌握与非门、或非门、反相器等电路原理图输入方法(三)掌握逻辑符号创建方法二、实验原理启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口,具体介绍如下:图2.1 Schematic Editing窗口菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些菜单为快捷方式,旨在提高设计效率。

在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷方式。

Cadence系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需要自行设置,在CIW窗口中,选择Options→Bindkeys,可以对所有设置的盲键自定义。

Cadence系统支持3D鼠标,左、中、右分别定义为LMB、MMB、RMB。

LMB用于点击和选择之用,MMB用于辅助编辑,RMB与LMB配合使用,在调查元件属性,局域放大,元件旋转等方面都有应用,在具体实验过程中有详细说明。

在所有元件的添加中,必须定义元件的属性。

最后,为了后续设计中执行仿真,每个元件必须具有物理模型(Model),在lab3中将有实例说明。

三、电路原理图设计的一般流程(一)创建库与视图(二)添加元件:在Schematic Editing窗口中,选择Add→Instance。

(三)添加Pins :在左侧Tool bar图标栏中选择pin icon图标,出现Add form,在Pin names栏中输入。

(四)添加Sources和Ground:选择Add→Instance,在Library column中选择analogLib,再选择vdd并添加到schematic中。

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。

(计算可先排除速度饱和的可能)V in =0时,V OH =2.5VV in=2.5时,假设NMOS 工作在临界饱和区:AI V R I vV V V A I V V L W K I D out L D T in out D T in D61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1,器件实际工作在线性区⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W KI in OL L D OL OL T in D 5.25.2]2)[(2`6`10115-⨯=K 将, 5.0/5.1=L W,43.0=T V 代入kohm R L 75=解得:=OL V 0.04633V由图得:V OH =2.5V, V OL =0.0356V. 当out in V V =时,NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`反相器阈值电压===out in M V V V 0.7932 此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH由图得:V IH=0.881V, V IL=0.0378V.SP文件:.TITLE 1.2UM CMOS INVERTER.options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vddMn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)RL OUT VDD 75kVDD VDD 0 2.5VVIN IN 0 0.DC VIN 0 2.5V 0.1V.op.probe dc v(out).end2.3.分析电路噪声容限。

广西机电职业技术学院电气系实验报告学号20100211020实验名称画反相器上机时间实验成绩实验目的:1、熟悉使用版图设计软件Tanner L-EDIT 11.1;2、了解软件的操作流程和基本参数的设置;3、学会修改错误;4、学会看编译文件、电路图等;实验要求:1、计算机;2、Tanner L-EDIT 11.1版图开发软件;实验内容:下面是反相器符号。

1、一、电路图1、新建一个名为“f_x_q.sdb”的工程文件,Module——now新建名为“f_x_q”的电路图2、保存后复制粘贴到新的电路图里命名为“f_x_q_2”添加直流源和交流源3、保存后设置瞬时仿真最大值为1ns 仿真长度为400ns4、输出信号输入端(IN)和信号输出端(out)的瞬时波形得下图5、开始仿真6、相同方法输入信号换成直流信号,命名为“f_x_q_3”二、版图1、打开L-Edit软件新建名为F_X_Q.tdb的文件再里头新建元件有PB(basecontactn)、NB(basecontactn)、PMOS、NMOS、IN(输入端)、OUT(输出端)、PB(basecontactn)NB(basecontactn)PMOSNMOSIN(输入端)OUT(输出端)2、以上元件都要进行DRC错误检查,因为out端少了金属一层,所以提示会出错。

3、新建元件F_X_Q导入以上所有元件并画地和电源并连线,加入节点名称,如下图4、检查没有错误后创建仿真文件。

得按要求添加周期为100ns高电平保持时间为50ns高低跳变时间为5ns幅度电位为0~5v的交流源Va 总电源5v的直流源vvdd加入仿真长度和时间1ns 400ns三、进行电路图和版图的一致性对比结果:。

反相器实验报告反相器实验报告引言反相器是电子电路中常用的一种元件,它可以将输入信号的相位进行180度的翻转。

本次实验旨在通过搭建一个基本的反相器电路,验证其工作原理,并探究其在实际应用中的一些特性。

实验原理反相器是由一个晶体管和几个电阻器组成的简单电路。

晶体管作为放大元件,可以控制电流的流动,而电阻器则用来限制电流的大小。

当输入信号为高电平时,晶体管处于截止状态,输出信号为低电平;而当输入信号为低电平时,晶体管处于饱和状态,输出信号为高电平。

这样就实现了输入信号相位的反转。

实验步骤1. 准备材料和设备:晶体管、电阻器、电源、示波器等。

2. 搭建电路:按照实验原理中所述的电路图,连接晶体管、电阻器和电源。

3. 测量电流和电压:使用万用表测量电流和电压的数值,并记录下来。

4. 输入信号测试:将示波器连接到电路的输入端和输出端,观察输入信号和输出信号的波形,并记录下来。

5. 分析数据:根据测量数据和波形图,分析反相器的工作原理和特性。

实验结果与讨论通过实验,我们得到了以下数据和观察结果:1. 输入电压为高电平时,输出电压为低电平;输入电压为低电平时,输出电压为高电平。

这验证了反相器的工作原理。

2. 输入信号的频率对反相器的输出有一定的影响。

当频率较低时,输出信号的波形较为稳定;而当频率较高时,输出信号的波形可能出现失真。

3. 输入信号的幅度对反相器的输出也有影响。

当输入信号的幅度较小时,输出信号的幅度也会相应减小;而当输入信号的幅度较大时,输出信号的幅度也会增大。

4. 在实际应用中,反相器常用于信号放大、波形变换等电路中。

通过调整电阻器的阻值和电源的电压,可以实现不同的放大倍数和波形变换效果。

结论通过本次实验,我们成功搭建了一个基本的反相器电路,并验证了其工作原理。

反相器在电子电路中具有广泛的应用,可以实现信号的相位反转、波形变换等功能。

在实际应用中,我们还可以通过调整电路参数来达到不同的效果。

反相器的研究和应用对于电子技术的发展具有重要意义。

实验二:Quartus II入门班级:姓名:学号:同组人员:一、实验目的(1)掌握Quartus Ⅱ集成开发软件的原理。

(2)熟练运用Quartus Ⅱ集成开发软件实现基本逻辑电路的实现。

(3)熟悉DEO硬件开发板的连接使用。

二、实验要求要求1:根据参考内容,用原理图输入方法实现一位全加器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:参照参考内容,用74138 3-8 译码器和7400与非门,用原理图输入方法实现一位全减器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

三、实验内容(一)全加器的设计与实现a.根据逻辑真值表写出逻辑函数表达式Ai和Bi分别表示加数与被加数,Ci表示低位向本位的进位,Si表示本位和,Ci1表示本位向高位的进位。

b.根据逻辑函数表达式画出电路逻辑图c.在QuartusII上绘制全加器原理图并仿真出波形,结果如下:d.下载到DEO板子上验证,实现全加器功能。

(二)全减器的设计与实现a.根据逻辑真值表写出逻辑函数表达式An和Bn分别表示被减数和减数,Cn表示低位向本位的借位,Dn 表示本位差,Cn1表示本位向高位的借位。

逻辑真值表An Bn Cn Cn1 Dn0 0 0 0 00 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1b.根据逻辑函数表达式画出电路逻辑图c.在QuartusII上绘制全减器原理图并仿真出波形,结果如下:d.下载到DEO板子上验证,实现全减器功能。

四、实验心得通过这个实验,我对与非门的用法有了更深刻的理解,对设计电路也从之前的“纸上谈兵”变成了具体实践,设计以及实验完成之后很有成就感。

最重要的是我了解并掌握了Quartyrs的一些基本用法,相信在以后的学习中可以取得更深入的了解。

《数字集成电路》上机实验姓名:***班级:***学号:***第一次实验一、实验目的:掌握HSPICES软件的使用方法,用于分析二极管及CMOS反相器的直流特性,通过改变电源电压及MOS管的宽长比得到一组CMOS反相器的电压传输特性曲线,从而理解CMOS反相器电压传输特性曲线的影响因素和调整方法。

二、实验内容:1. 由上图所示,令(1)I S=10-14A,T=300K;(2) I S=10-16A,T=300K;(3) I S=10-14A,T=350K,利用SPICE求解V D1、V D2和I D。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\csmc06.LIB' TT.TEMP temvalueR1 1 2 2kR2 3 4 2kD1 2 3 DMODD2 4 0 DMOD.MODEL DMOD D Is=isvalue.PARAM temvalue=27 isvalue=1E-14 V1 1 0 DC 2.5.OP.ALTER.PARAM temvalue=27 isvalue=1E-16 .ALTER.PARAM temvalue=77 isvalue=1E-14 .OPIONS LIST NODE POST=2.END【结果】【分析】V D1=525.4463mv、V D2=525.4463mv和I D=362.2768uA2. (1)由下图所示,令Vin从0V变化到2.5V,步长为0.5V,利用SPICE求M1管电流变化的曲线,判断管子的工作状态;当M1的尺寸变化为W/L=4u/1u时,求I M1,并解释两条曲线存在误差的原因。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=1U W=4U.DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=0.25U W=1U .DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END【结果】【分析】在1.5V之前是工作在线性区,1.5-2V之间是可变电阻区,2V以后工作在饱和区。

数电实验2一.实验目的1.学习并掌握硬件描述语言(VHDL 或Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求1:编写一个异或门逻辑电路,编译程序如下。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:编写一个将二进制码转换成0-F 的七段码译码器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板,利用开发板上的数码管验证。

要求3:编写一个计数器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求4:编写一个能实现占空比50%的5M 和50M 分频器即两个输出,输出信号频率分别为10Hz 和1Hz。

1)下载到DE0 开发板验证。

(提示:利用DE0 板上已有的50M 晶振作为输入信号,通过开发板上两个的LED 灯观察输出信号)。

2)电路框图如下:扩展内容:利用已经实现的VHDL 模块文件,采用原理图方法,实现0-F 计数自动循环显示,频率10Hz。

(提示:如何将VHDL 模块文件在逻辑原理图中应用,参考参考内容5)四.实验原理1.实验1实现异或门逻辑电路,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXORGATE ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END EXORGATE;ARCHITECTURE fwm OF EXORGATE ISBEGINC<=A XOR B;END;2.实验2实现一个将二进制码转换成0-F的七段译码器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示0 WHEN"0001"=>dis_out<="1111001";--显示1 WHEN"0010"=>dis_out<="0100100";--显示2 WHEN"0011"=>dis_out<="0110000";--显示3 WHEN"0100"=>dis_out<="0011001";--显示4 WHEN"0101"=>dis_out<="0010010";--显示5 WHEN"0110"=>dis_out<="0000010";--显示6WHEN"0111"=>dis_out<="1111000";--显示7 WHEN"1000"=>dis_out<="0000000";--显示8 WHEN"1001"=>dis_out<="0010000";--显示9 WHEN"1010"=>dis_out<="0001000";--显示A WHEN"1011"=>dis_out<="0000011";--显示b WHEN"1100"=>dis_out<="1000110";--显示C WHEN"1101"=>dis_out<="0100001";--显示d WHEN"1110"=>dis_out<="0000110";--显示E WHEN"1111"=>dis_out<="0001110";--显示FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;3.实验3完成一个计数器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT ( clk,RST : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数COUT : OUT STD_LOGIC); --进位位END counter;ARCHITECTURE fwm OF counter ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINPROCESS(clk,RST)BEGINIF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';ELSIF clk'EVENT AND clk='1' THENQ1<=Q1+1;COUT<= '0';IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;4.实验4编写一个能实现占空比50%的5M 和50M 分频器即两个输出,输出信号频率分别为10Hz 和1Hz,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fpq ISPORT(clk:IN STD_LOGIC;clk_out,clk_out1:OUT STD_LOGIC);END fpq;ARCHITECTURE fwm OF fpq ISCONSTANT m : INTEGER:= 25000000; --50M 分频到1Hz 时=25000000。

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。

(计算可先排除速度饱和

的可能)

V in =0时,V OH =2.5V

V in=2.5时,假设NMOS 工作在临界饱和区:

A

I V R I v

V V V A I V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据 D D I I <1,器件实际工作在线性区

⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W K I in

OL L D OL OL T in D 5.25.2]2)[(2`

6`10115-⨯=K 将, 5.0/5.1=L W ,43.0=T V 代入kohm R L 75=

解得:

=OL V 0.04633V

由图得:V OH =2.5V, V OL =0.0356V.

当out in V V =时,NMOS 工作在饱和区

⎪⎩⎪⎨⎧+=-⨯=out

L D T in D V R I V V L W K I 5.2)(2/2` 反相器阈值电压===out in M V V V 0.7932

此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--==

--=in Vin

Vout in out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH

由图得:V IH=0.881V, V IL=0.0378V.

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)

RL OUT VDD 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.op

.probe dc v(out)

.end

2. 3.分析电路噪声容限。

计算NM H(高电平噪声容限)和NM L(低电平

噪声容限), 并使用HSPICE画出反相器的VTC曲线。

NM H=V OH - V IH=1.619V

NM L= V IL- V OL=0.0022V

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)

RL OUT VDD 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.op

.probe dc v(out)

.end

3. 4.使用HSPICE画出RL=35k,75K,150k三种情况下的VTC。

(从左到右依次为RL=150k,75k, 35k)

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear .options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u

RL VDD OUT 75k

VDD VDD 0 2.5V

VIN IN 0 0

.DC VIN 0 2.5V 0.1V

.probe V(out)

.probe V(in)

.alter

.TITLE Exercise 2.1 RL = 150k

RL Vdd out 150k

.alter

.TITLE Exercise 2.1 RL = 35k

RL Vdd out 35k

.end

1.5.对2的结果进行仿真验证。

(tran 仿真;输入加脉冲,上升和下

降时间都为5ns)

由图得:t PHL=; t PLH=s

SP文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)RL OUT VDD 75k

CL OUT 0 3p

VDD VDD 0 2.5V

Vin in 0 PULSE(0 2.5v 100n 5n 5n 5u 10u)

.TRAN 1n 30u

.measure tran TPHL trig v(in) val=1.25 td=1n rise=2 targ v(out)

+val=1.25 td=1n fall=2

.measure tran TPLH trig v(in) val=1.25 td=1n fall=2 targ v(out) +val=1.25 td=1n rise=2

.probe V(out)

.probe V(in)

.end。