基于FPGA的北斗卫星信号接收机设计

- 格式:pdf

- 大小:424.34 KB

- 文档页数:2

基于FPGA和DSP的卫星导航接收机测试平台卫星导航接收机是卫星导航系统的用户终端,用以给用户提供精确的经度、纬度、高度和速度等信息。

现在,卫星导航接收机已经应用于航空,交通管理,石油等各个领域,针对卫星导航接收机的研究也越发深入。

本文介绍了一种以FPGA和DSP为主处理器的卫星导航接收机硬件平台。

在该平台上不仅可以验证针对现在所有卫星导航系统(GPS,Glonass,伽利略,北斗)的基带信号处理算法和导航解算算法,同时也可以实现完整的单频、双频或者兼容接收机。

1 硬件设计1.1 硬件平台组成硬件平台结构框图如本实验室所示;该平台以两片FPGA芯片和两片DSP芯片为主处理器。

经过AD采样后的信号直接进入FPGA,此后所有对信号的处理均由软件来实现。

如此可以充分利用FPGA和DSP的重复烧写及在线调试能力,尽量减少对硬件的依赖程度,从而增加平台的灵活性。

另外,每片DSP都外接了Flash和SDRAM。

由于Flash掉电数据不会丢失,可以在Flash内保存程序及数据,功能有如PC机上的硬盘,而外接的SDRAM是DSP的扩展Ram,当DSP运行大型程序(如导航解算程序)以致DSP的内部Ram不够用时,可以将程序放到外接的SDRAM内运行。

平台上还有多个串口,可以接显控等设备。

两个Arinc-429接口可以接惯导等航空设备。

JTAG是在线调试接口。

时钟模块提供系统的工作时钟。

只要连接上针对不同卫星导航系统的射频模块和天线,该平台就可以成为一个完整的接收机。

1.2 芯片介绍FPGA采用Altera公司CycloneII系列中的EP2C70F672。

Altera公司的Cy cloneII系列FPGA是业界成本及功耗最低的FPGA之一,采用90nm工艺制造。

EP2C70F672是CycloneII系列中的最高型号,拥有7万个逻辑单元,1Mbits内部RAM,300个9×9乘法器,4个PLL环和422个I/O接口,最高数据率可以达到330Mbps。

欢迎网上投稿 《电子技术应用》2011年第37卷第7期当前,以FPGA +DSP 为硬件平台实现的软件接收机,由于参数设置灵活、可验证新的导航算法而备受重视。

伴随着新算法的日益复杂和对接收机要求的不断提高,对系统的速度提出了更高的要求[1-2]。

比较GNSS 接收机不同解决方案的处理能力与灵活性[3],将更多的任务交给FPGA 处理以减少DSP 的负担、提高系统速度。

本文采用FPGA 完成GPS 的基带处理,保留了软件接收机参数的灵活性;节省了DSP 资源,增加了定位结果的输出率;在FPGA 硬件资源允许下,通道个数可以任意扩展。

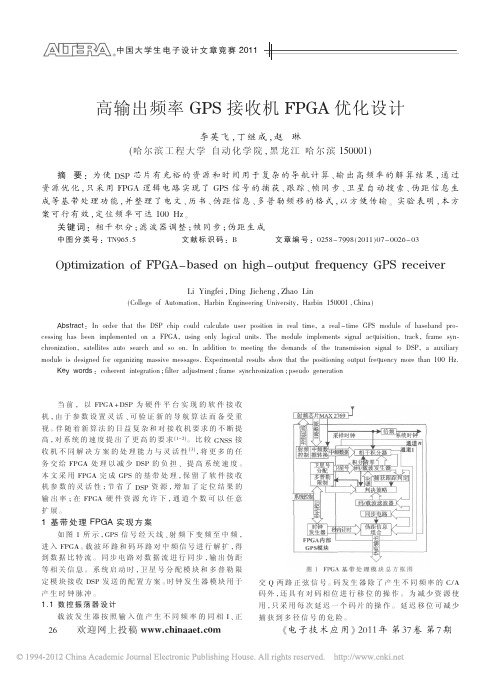

1基带处理FPGA 实现方案如图1所示,GPS 信号经天线、射频下变频至中频,进入FPGA 。

载波环路和码环路对中频信号进行解扩,得到数据比特流。

同步电路对数据流进行同步,输出伪距等相关信息。

系统启动时,卫星号分配模块和多普勒限定模块接收DSP 发送的配置方案。

时钟发生器模块用于产生时钟脉冲。

1.1数控振荡器设计载波发生器按照输入值产生不同频率的同相I 、正交Q 两路正弦信号。

码发生器除了产生不同频率的C/A 码外,还具有对码相位进行移位的操作。

为减少资源使用,只采用每次延迟一个码片的操作。

延迟移位可减少捕获到多径信号的危险。

高输出频率GPS 接收机FPGA 优化设计李英飞,丁继成,赵琳(哈尔滨工程大学自动化学院,黑龙江哈尔滨150001)摘要:为使DSP 芯片有充裕的资源和时间用于复杂的导航计算、输出高频率的解算结果,通过资源优化,只采用FPGA 逻辑电路实现了GPS 信号的捕获、跟踪、帧同步、卫星自动搜索、伪距信息生成等基带处理功能,并整理了电文、历书、伪距信息、多普勒频移的格式,以方便传输。

实验表明,本方案可行有效,定位频率可达100Hz 。

关键词:相干积分;滤波器调整;帧同步;伪距生成中图分类号:TN965.5文献标识码:B文章编号:0258-7998(2011)07-0026-03Optimization of FPGA-based on high-output frequency GPS receiverLi Yingfei ,Ding Jicheng ,Zhao Lin(College of Automation,Harbin Engineering University,Harbin 150001,China)Abstract :In order that the DSP chip could calculate user position in real time,a real -time GPS module of baseband pro -cessing has been implemented on a FPGA,using only logical units.The module implements signal acquisition,track,frame syn -chronization,satellites auto search and so on.In addition to meeting the demands of the transmission signal to DSP,a auxiliary module is designed for organizing massive messages.Experimental results show that the positioning output frequency more than 100Hz.Key words :coherent integration ;filter adjustment ;frame synchronization ;pseudo generation图1FPGA 基带处理模块总方框图26《电子技术应用》2011年第37卷第7期表1环路参数对比锁相环ω2n T sa 2ωωn ω2n T s a 2ω12锁频环延迟锁定环41/432241/411/321/2561/1024图2不同参数的环路状态(a)第一组参数正交Q 支路积分值锁相环滤波器输入/△°正交Q 支路积分值锁相环滤波器输入/△°(b)第二组参数1.2环路滤波器参数调整考虑到FPGA 除法运算的舍入误差和射频芯片带宽的影响,环路参数的调整工作按以下步骤进行。

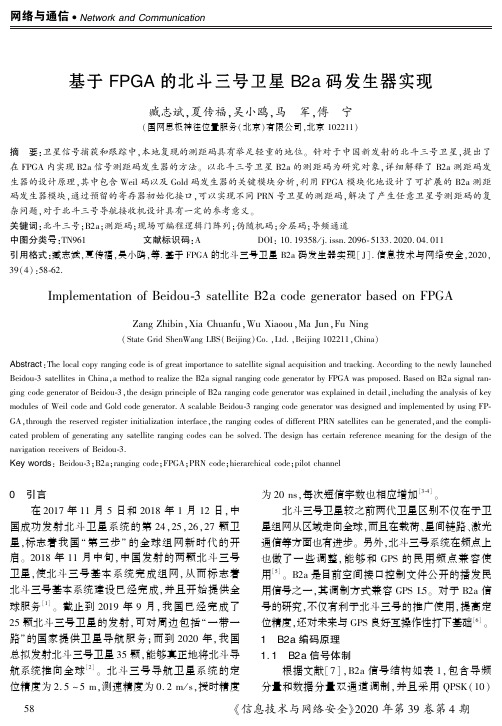

基于FPGA的北斗三号卫星B2a码发生器实现臧志斌ꎬ夏传福ꎬ吴小鸥ꎬ马㊀军ꎬ傅㊀宁(国网思极神往位置服务(北京)有限公司ꎬ北京102211)摘㊀要:卫星信号捕获和跟踪中ꎬ本地复现的测距码具有举足轻重的地位ꎮ针对于中国新发射的北斗三号卫星ꎬ提出了在FPGA内实现B2a信号测距码发生器的方法ꎮ以北斗三号卫星B2a的测距码为研究对象ꎬ详细解释了B2a测距码发生器的设计原理ꎬ其中包含Weil码以及Gold码发生器的关键模块分析ꎬ利用FPGA模块化地设计了可扩展的B2a测距码发生器模块ꎬ通过预留的寄存器初始化接口ꎬ可以实现不同PRN号卫星的测距码ꎬ解决了产生任意卫星号测距码的复杂问题ꎬ对于北斗三号导航接收机设计具有一定的参考意义ꎮ关键词:北斗三号ꎻB2aꎻ测距码ꎻ现场可编程逻辑门阵列ꎻ伪随机码ꎻ分层码ꎻ导频通道中图分类号:TN961㊀㊀㊀㊀㊀㊀文献标识码:A㊀㊀㊀㊀㊀㊀DOI:10.19358/j.issn.2096 ̄5133.2020.04.011引用格式:臧志斌ꎬ夏传福ꎬ吴小鸥ꎬ等.基于FPGA的北斗三号卫星B2a码发生器实现[J].信息技术与网络安全ꎬ2020ꎬ39(4):58 ̄62.ImplementationofBeidou ̄3satelliteB2acodegeneratorbasedonFPGAZangZhibinꎬXiaChuanfuꎬWuXiaoouꎬMaJunꎬFuNing(StateGridShenWangLBS(Beijing)Co.ꎬLtd.ꎬBeijing102211ꎬChina)Abstract:Thelocalcopyrangingcodeisofgreatimportancetosatellitesignalacquisitionandtracking.AccordingtothenewlylaunchedBeidou ̄3satellitesinChinaꎬamethodtorealizetheB2asignalrangingcodegeneratorbyFPGAwasproposed.BasedonB2asignalran ̄gingcodegeneratorofBeidou ̄3ꎬthedesignprincipleofB2arangingcodegeneratorwasexplainedindetailꎬincludingtheanalysisofkeymodulesofWeilcodeandGoldcodegenerator.AscalableBeidou ̄3rangingcodegeneratorwasdesignedandimplementedbyusingFP ̄GAꎬthroughthereservedregisterinitializationinterfaceꎬtherangingcodesofdifferentPRNsatellitescanbegeneratedꎬandthecompli ̄catedproblemofgeneratinganysatelliterangingcodescanbesolved.ThedesignhascertainreferencemeaningforthedesignofthenavigationreceiversofBeidou ̄3.Keywords:Beidou ̄3ꎻB2aꎻrangingcodeꎻFPGAꎻPRNcodeꎻhierarchicalcodeꎻpilotchannel0㊀引言在2017年11月5日和2018年1月12日ꎬ中国成功发射北斗卫星系统的第24ꎬ25ꎬ26ꎬ27颗卫星ꎬ标志着我国 第三步 的全球组网新时代的开启ꎮ2018年11月中旬ꎬ中国发射的两颗北斗三号卫星ꎬ使北斗三号基本系统完成组网ꎬ从而标志着北斗三号基本系统建设已经完成ꎬ并且开始提供全球服务[1]ꎮ截止到2019年9月ꎬ我国已经完成了25颗北斗三号卫星的发射ꎬ可对周边包括 一带一路 的国家提供卫星导航服务ꎻ而到2020年ꎬ我国总拟发射北斗三号卫星35颗ꎬ能够真正地将北斗导航系统推向全球[2]ꎮ北斗三号导航卫星系统的定位精度为2.5~5mꎬ测速精度为0.2m/sꎬ授时精度为20nsꎬ每次短信字数也相应增加[3 ̄4]ꎮ北斗三号卫星较之前两代卫星区别不仅在于卫星组网从区域走向全球ꎬ而且在载荷㊁星间链路㊁激光通信等方面也有进步ꎮ另外ꎬ北斗三号系统在频点上也做了一些调整ꎬ能够和GPS的民用频点兼容使用[5]ꎮB2a是目前空间接口控制文件公开的播发民用信号之一ꎬ其调制方式兼容GPSL5ꎮ对于B2a信号的研究ꎬ不仅有利于北斗三号的推广使用ꎬ提高定位精度ꎬ还对未来与GPS良好互操作性打下基础[6]ꎮ1㊀B2a编码原理1.1㊀B2a信号体制根据文献[7]ꎬB2a信号结构如表1ꎬ包含导频分量和数据分量双通道调制ꎬ并且采用QPSK(10)85«信息技术与网络安全»2020年第39卷第4期«信息技术与网络安全»2020年第39卷第4期调制方式调制在1176.45MHz频点上ꎮB2a信号采用主码和子码的分层码结构ꎬ由主码和子码相异或构成ꎬ子码的码元宽度和主码的周期相同ꎬ子码码元起始时刻与主码第一个码元的起始时刻严格对齐ꎬ时序对应关系如图1所示ꎮ表1㊀B2a信号结构信号信号分量载波频率/MHz调制方式符号速率/sps服务类型B2a数据分量导频分量1176.45QPSK(10)2000RNSS图1㊀主码㊁子码时序关系示意图㊀㊀B2a信号主码的码速率为10.23Mcpsꎬ码长为10230ꎬ由两个13级线性反馈移位寄存器通过移位和模二加生成的Gold码扩展得到ꎮB2a数据分量主码㊁导频分量主码的生成多项式分别如式(1)㊁(2)所示:g1(x)=1+x+x5+x11+x13g2(x)=1+x3+x5+x9+x11+x12+x13{(1)g1(x)=1+x3+x6+x7+x13g2(x)=1+x+x5+x7+x8+x12+x13{(2)对于不同卫星ꎬB2a数据分量的子码相同ꎬ采用固定的5位码序列作为子码ꎬ子码序列为00010ꎬ高位先传ꎻB2a导频分量的子码码长为100ꎬ由长度为1021的Weil码通过截断得到ꎮ1.2㊀B2a信号主码结构由于B2a数据分量和导频分量的主码发生器结构类似ꎬ因此本文主要分析B2a数据分量的主码发生器ꎬ导频分量的主码发生器可参考数据分量的主码发生器ꎮ根据式(1)可以得到B2a数据分量的主码发生器如图2所示ꎮ与原B1I㊁B2I的Gold发生器不同的是[8]ꎬB2a数据分量主码采用13级非线性移位寄存器ꎮ寄存器1的初始值与B1I㊁B2I的一样ꎬ所有卫星采用相同的初始值ꎬ但是B2a寄存器的初始值与之不同ꎬ其初始值全为1ꎻ寄存器2的初始值根据不同卫星的PRN号采用不同的数值ꎬ对应的寄存器2初始值表在接口文件中给出ꎮ1.3㊀B2a信号子码B2a数据分量的子码采用固定的5位码序列(00010)ꎬ在实现方式上可以利用在基带中捕获到的信号ꎬ设置历元时ꎬ在每逢4的整数个主码周期将主码码片取反(即与1异或)ꎬ其他主码周期输出主码码片值不变ꎮB2a导频分量的子码是采用长度为1021的Weil码通过截断得到ꎮWeil码是一种性能优良的码片ꎬ它的相关性能非常好ꎬ且具有相对灵活的可选序列长度[9]ꎮWeil码的产生是基于有限长的伪随机序列 勒让德序列ꎮ它的长度为质数ꎮ式(3)定义的是长度为N的勒让德序列ꎬ对于固定长度的Nꎬ有且仅有一个勒让德序列[10]ꎬB2a中的N代表1021ꎮL(k)=0ꎬk=01ꎬkʂ0ꎬ且存在整数xꎬ使得k=x2modN0ꎬ其他{(3)95«信息技术与网络安全»2020年第39卷第4期图2㊀B2a数据分量的主码发生器其中ꎬmod表示模除运算ꎮ因此ꎬ长度为N的Weil码序列定义如式(4)所示:W(kꎻw)=L(k) L((k+w)modN)ꎬk=0ꎬ1ꎬ2ꎬ ꎬN-1(4)其中ꎬw表示两个勒让德序列之间的相位差ꎮB2a导频分量子码的截取方式为循环截取ꎬ即截断序列如式(5)所示:c(nꎻwꎻp)=W((n+p-1)mod1021ꎻw)ꎬn=0ꎬ ꎬ99(5)其中ꎬp为截取点ꎬ表示从Weil码的第p位开始截取ꎬ取值范围为1~1021ꎬw取值为1~510ꎮ2㊀B2a码发生器的设计与实现2.1㊀B2a信号主码FPGA内有丰富的触发器资源ꎬ非常适合移位操作ꎮ根据B2a数据分量主码发生器框图ꎬ可以得出g1和g2码的实现过程ꎬ式(6)㊁式(7)分别表示的是g1㊁g2寄存器组的更新过程ꎮC1=c1ꎬ1 c1ꎬ5 c1ꎬ11 c1ꎬ13c1ꎬ1=C1c1ꎬi=c1ꎬi ̄1ꎬi=2ꎬ ꎬ13ìîíïïï(6)C2=c2ꎬ3 c2ꎬ5 c2ꎬ9 c2ꎬ11 c2ꎬ12 c2ꎬ13c2ꎬ1=C2c2ꎬi=c2ꎬi ̄1ꎬi=2ꎬ ꎬ13ìîíïïï(7)式中ꎬC1㊁C2表示寄存器1㊁寄存器2的反馈值ꎬc1ꎬi㊁c2ꎬi分别表示寄存器1㊁寄存器2第i位的内容ꎮ在主码发生的起始时刻ꎬ寄存器1和寄存器2同步复位(寄存器1的初始值为1111111111111ꎬ寄存器2的初始值通过配置得到)ꎬ而后在每一个时钟上升沿来临的时刻ꎬ第2~13位寄存器内容被前一位寄存器内容更新ꎬ第1位寄存器内容被反馈值更新ꎮ值得注意的是ꎬ寄存器1在8190码片时发生截断ꎮ图3所示是主码发生器模块的接口示意图ꎮ为了节省FPGAROM的容量ꎬ寄存器2的初始值在FPGA内留有接口ꎬ通过外部寄存器配置写入ꎻ而寄存器1初始值是固定的ꎬ可以固化于FPGA内ꎮ为了后续捕获信号时能够调整主码相位ꎬ在FPGA内预留有码相位偏移接口ꎬ以及三路码片超前码㊁即时码和滞后码ꎻ码片捕获精度为半个码片ꎬ因此主码产生时钟为20.46MHzꎮ2.2㊀B2a信号子码根据B2a子码的结构与编码原理ꎬ不同PRN号的卫星ꎬ它的截取点p和相位差w设置不同ꎬ对应的Weil码是相同的ꎮ因此导频子码的生成关键在于生成Weil码ꎮ由于Weil码生成过程包含有模除操作ꎬ勒让德序列基于同余理论构建ꎬ无法用简单的电路结构实时生成ꎮ在本文中ꎬ提出一种产生B2a导频子码的方案ꎬ先利用软件生成Weil码ꎬ定义一个长度为N的一维数组L[N]并且所有元素初始化06«信息技术与网络安全»2020年第39卷第4期图3㊀主码发生器模块接口示意图为0ꎬk从0~N-1遍历ꎬ求出t=k2mod1021ꎬ数组L在t元素处置1ꎮ接着ꎬ把生成好的Weil码存储于FPGA的ROM中ꎬ生成不同PRN卫星的导频子码时再根据子码参数(截取点和相位差)实时从ROM中读取ꎬ由于导频子码的长度是100ꎬ因此只需循环读取ROM中的100个值即可ꎮB2a导频子码的周期是100msꎬ同样地ꎬ历元设置后ꎬ当历元计数到100ms的整数倍时ꎬ开始产生导频子码ꎬ再与B2a导频主码异或ꎬ即可产生B2a导频组合码ꎬ如图4所示ꎬ在导频子码模块中预留有子码发生器使能时钟接口(sub_code_enable)ꎬ在历元满足上述条件时ꎬ可产生导频子码ꎮ图4㊀导频子码发生器模块3㊀B2a码发生器的仿真本次仿真编码工具采用的是QuartusII13.1sp1版本ꎬ芯片选取的是AlteraEP3C120F484C7ꎬ仿真软件采用的是Modelsim10.1cꎬ主码和子码的仿真参数均选取为PRN号为1号星的参数ꎮ3.1㊀主码发生器仿真图5给出了主码发生器模块的仿真波形图ꎮ其中ꎬB2a数据分量㊁导频分量的寄存器2初始值(pi ̄lot_regꎬdata_reg)均设置为1000000100101ꎬ即均设置为PRN号为1号星的主码参数ꎬ并且设置码偏移(chip_shift)为0ꎮ图5㊀主码发生器仿真波形图㊀㊀图5中ꎬdata_code_early㊁data_code_prompt㊁data_code_late分别表示数据分量主码的超前码㊁即时码以及滞后码ꎻ同样地ꎬpilot_code_early㊁pilot_code_prompt㊁pilot_code_late分别表示导频分量主码的超前码㊁即时码以及滞后码ꎮ超前码与即时码㊁即时码与滞后码仅相差半个码片的宽度ꎬ因此在此分析超前码片ꎮdump_1ms表示一主码周期的结束ꎬ当dump_1ms下降沿来临之时表示新的主码周期开始产生ꎬ从图中可看出产生的数据分量主码和导频分量主码超前码头24码片分别为(010110111111001000101110)2(或(26771056)8)㊁(010110111111010100011101)2(或(26772435)8)ꎬ与控制接口文件中B2a数据分量㊁导频分量主码具体参数表对比ꎬ仿真结果正确ꎮ3.2㊀导频子码发生器仿真图6给出的是导频子码发生器模块的仿真波形图ꎮ其中ꎬ相位差w㊁截取点p分别设置为123㊁138ꎬ即仿真PRN号为1的卫星导频分量子码ꎮ从图6可以看出ꎬ当写入截取点138时ꎬ由于在双口ROM读取时需要先打一拍之后才能出数据ꎬ因此在ROM地址值(address_a㊁address_b)有效之后的第二地址导频子码(sub_code)才有效ꎬ可以得到输出导频子码头24码片为(011010000110011000101000 )2(或(32063050 )8)ꎬ与控制接口16«信息技术与网络安全»2020年第39卷第4期图6㊀导频子码发生器模块仿真波形图文件中B2a导频分量子码具体参数表对比ꎬ仿真结果正确ꎮ4㊀结束语本文根据北斗三号卫星B2a信号测距码发生器的原理ꎬ利用Verilog语言ꎬ采用模块化设计方法ꎬ给出了基于FPGA的B2a主码(Gold码)以及导频子码(Weil码)的设计方案ꎬ并提出了基于历元计数的子码解调方案ꎮ仿真结果表明ꎬ本设计可以实现北斗三号B2a本地复制伪码的产生ꎬ并且提供了扩展性接口ꎬ为后续B2a信号捕获奠定了基础ꎬ对于北斗三号接收机研制具有重要意义ꎮ参考文献[1]科技导报编辑部.北斗三号组网卫星首发成功[J].科技导报ꎬ2017ꎬ35(22):5.[2]数字通信世界编辑部.北斗三号全球定位系统启动建设[J].数字通信世界ꎬ2017(B10):59.[3]杨元喜.北斗卫星导航系统的进展㊁贡献与挑战[J].测绘学报ꎬ2010ꎬ39(1):1 ̄6.[4]InformationOfficeoftheStateCouncil.ChinaᶄsBeiDouNavigationSatelliteSystem[J].BeijingReviewꎬ2016ꎬ59(28):8 ̄16.[5]LiuBiꎬTengYunlongꎬHuangQi.GDOPminimuminmulti ̄㊀㊀GNSSpositioning[J].AdvancesinSpaceResearchꎬ2017ꎬ7:1400 ̄1403.[6]庄新彦ꎬ郭莉莉.CompassB2a与GPSL5信号间干扰仿真分析[J].全球定位系统ꎬ2009ꎬ34(3):17 ̄20.[7]中国卫星导航系统管理办公室.北斗卫星导航系统空间信号接口控制文件公开服务信号B2a(1.0版)[S].2017.[8]王迪ꎬ郝士琦ꎬ朱斌ꎬ等. 北斗 2代B1I信号导航电文分析[J].航天电子对抗ꎬ2013ꎬ29(6):30 ̄32.[9]LuHui.NiuRuiyao.GenerationmethodofGPSL1Ccodesbasedonquadraticreciprocitylaw[J].JournalofSystemsEngineeringandElectronicsꎬ2013ꎬ24(2):189 ̄195.[10]HOFERRꎬWINTERHOFA.Onthearithmeticautocorre ̄lationoftheLegendresequence[J].AdvancesinMathe ̄maticsofCommunicationsꎬ2017ꎬ11(1):237 ̄244.(收稿日期:2020 ̄01 ̄15)作者简介:臧志斌(1974-)ꎬ男ꎬ硕士ꎬ高级工程师ꎬ主要研究方向:电力芯片研发制造㊁电力行业信息化㊁电力工程设计ꎮ夏传福(1983-)ꎬ男ꎬ博士ꎬ高级工程师ꎬ主要研究方向:地理信息研究ꎮ吴小鸥(1990-)ꎬ男ꎬ本科ꎬ工程师ꎬ主要研究方向:电力工程㊁动力电气技术ꎮ26。

基于FPGA的数字式GPS接收机载波环设计与实现张博;张斌【摘要】同步系统工作的好坏,在很大程度上决定了通信系统的质量。

GPS接收机将天线接收到的卫星信号经射频前端处理后变成了数字中频信号,接收机对GPS卫星的信号处理过程,可依次分为捕获、跟踪、位同步和帧同步4个阶段。

针对GPS信号的BPSK调制和强度微弱等特点,模拟 GPS接收机基带数字信号处理过程,首先介绍了科斯塔斯(Costas)接收机的工作原理,分析研究了基于现场可编程门阵列( field-programmable gate array , FPGA)的软件无线电载波同步技术的实现方法,并采用Costas环实现了载波同步,性能测试验证了设计的正确性和可行性。

%The quality of communication systems can be largely determined by the synchronization technology used in the systemdesign .GPS receiver transforms a satellite signal received by an antenna into a digital medium-fre-quency signal by processing at the radiation frequency front end .The processing of the receiver for the signal of GPS satellite can be divided into four steps in order:capturing, tracking, bit synchronization and frame synchronization . Aiming at such characteristics as BPSK modulation and weak strength of GPS signal , this paper simulates the process of GPS receiver for processing digital signals of baseband .First, the working principle of Costas receiver is introduced , the realization method for FPGA-based software radio carrier synchronization technology is analyzed and researched .In addition , Costas loop is used to realize carrier synchronization .The performance testing demonstrated the accuracy and feasibility of design .【期刊名称】《应用科技》【年(卷),期】2015(000)002【总页数】5页(P29-32,38)【关键词】载波同步;伪随机码;Costas环;现场可编程门阵列【作者】张博;张斌【作者单位】空军工程大学信息与导航学院,陕西西安710077;空军工程大学信息与导航学院,陕西西安710077【正文语种】中文【中图分类】P228.42接收机对GPS卫星的信号处理过程,可以依次分为捕获、跟踪、位同步和帧同步4个阶段。

本科生毕业设计基于FPGA的简单OEM板GPS接收机设计Design of Simple OEM GPS Receiver Based on FPGA学生姓名所在专业所在班级申请学位指导教师职称副指导教师职称答辩时间目录设计总说明 ......................................................................................................................... I V INTRODUCTION .. (V)1前言 (1)1.1课题发展概况 (2)1.1.1国内外现况 (2)1.1.2存在问题 (4)1.2关于本设计 (5)2设计方案论证 (6)2.1设计原理 (6)2.2候选方案 (6)2.3方案选择 (7)3FPGA控制芯片设计 (10)3.1数据采集(COM_R) (10)3.2存储器(memory) (13)3.3写地址控制(writer) (15)3.4接收数据处理(reader) (15)3.5键盘、状态控制(controller) (18)3.6显示控制(displayer) (19)3.7读写地址耦合(AND_10) (21)3.8控制系统整合 (22)3.9芯片选型 (24)4接收机电路设计 (25)4.1接收机控制按钮 (25)4.2状态指示灯 (25)4.3数码管驱动 (26)4.4供电电路 (26)4.5GPS模块接口、FPGA开发板接口 (26)5接收机电路板制作 (28)5.1绘制原理图 (28)5.2绘制PCB板图 (28)5.3输出PCB板图 (29)5.4钻孔 (30)5.5热转印 (30)5.6腐蚀 (30)5.7焊接 (31)6系统测试 (32)7总结 (35)鸣谢 (37)参考文献 (38)附录 (39)附录A (39)附录B (49)设计总说明GPS(全球定位系统)随着时代的发展,技术的进步,展现出非常广阔的应用前景,吸引了不同行业科学家的热心研究和开发。

基于GPS中频信号源的FPGA设计实现方案1.引言在GPS接收机的设计中,为了检验和完善值号处理篁法,需要在本地获得GPS数字中频信号数据。

采用真实的数据并不是最佳选择,主要是因为其中的许多信号属性无法控制,也无法摸拟不同的接收环境和干扰情况,这给算法的验证测试带来麻烦;而且存储GPS真实数据需要消耗大量的硬件资源。

解决这一问题的有效方法是设计一个能够产生GPS数字中频信号并且参数可控的仿真信号源。

通常的仿真信号源设计方式被割裂为两种一一纯硬件方式和纯软件方式。

纯硬件方式是利用硬件器件和硬件表述直接进行设计,其设计难度大、周期长,而且系统结构设计的改变会带来巨大的硬件设计工作量。

纯软件设计的仿真信号源,是利用软件语言在PC机上搭建整个系统,其产生的数据需要被缓存起来以供硬件测试。

这样做不仅浪费存储资源,而且难以满足实时性要求。

本文介绍了一种新的GPS中频信号源的例由设计方案,它是利用Xi1inXSystemGeneratorfor幽工具可以自动由系统级表述转换成FPGA硬件表述的特点,完成从软件图形化设计到FPGA硬件实现的一体化流程。

其优点在于,功能设计部分在MAT1AB/SIMU1INK下完成,信号源产生结构清晰,进行信号验证检测和参数更改;硬件实现时,通过XiIinXSystemGenerator工具,自动生成优化的硬件描述语言文件和硬件测试文件,辅以Xi1inX硬件开发平台,大大减少了直接的硬件设计工作量,缩短了从设计到实现的过程,也方便了对系统设计的修改和升级。

2.Xi1inxSystemGeneratorforDSPXi1inxSystemGenerator是Xi1inx公司开发的FPGA辅助设计工具,包括嵌入SimUIink的Xi1inX模块集合(B1ockSet)和模型到硬件的转换软件。

它可自动生成FPGA综合、仿真和实现工具所需的命令文件。

用户可以在图形化环境中完成系统模型的硬件开发。

基于FPGA的ADS—B接收机信号处理单元设计研究了基于1090ES数据链技术的广播式自动相关监视设备(ADS-B)的信号格式和解码流程;给出了FPGA信息提取的实现方案。

通过报头识别、参考功率计算、数据位转换及校验,采用Verilog编程语言完成了其各个功能模块的设计。

实验结果表明,该方案可以实现ADS-B信号信息的提取。

标签:ADS-B;FPGA;参考功率;报头识别引言广播式自动相关监视(Automatic Dependent Surveillance-Broadcast,ADS-B)是基于全球卫星导航系统(Global Navigation Satellite System,GNSS)进行定位的航空器运行监视技术,是国际民航组织(ICAO)推荐的新监视技术。

基于1090 ES的ADS-B数据链技术被ICAO和我国民航确定为应用于商业航空运输的监视技术。

它基于S模式数据链,能够提供的最大数据带宽为1M Bits/s,可提供航空器的航班号、ICAO地址码、位置、高度、速度、航向、飞行意图等相关丰富的信息。

ADS-B监视信息的更新频率是雷达的4-5倍,成本却是雷达系统的十分之一。

由于其自身的诸多优势,ADS-B越来越受到多方的关注与应用。

本文主要围绕基于1090ES数据链技术的ADS-B接收系统的信号解码开展研究。

1 消息编码简介ADS-B消息包括4个前导脉冲和112比特消息序列[1]。

前五个比特为DF 域,在1090Mhz ES中为固定值17;Bit6到Bit8在1090 ES中为CA域;Bit9到Bit32总共24 Bit位为设备唯一地址码(AA域);Bit33到Bit88总共56Bit位为报文信息(ME域);最后24Bit为校验域(PI域)。

ADS-B消息数据块格式采用脉冲位置调制(PPM)编码,如图1所示:图1 ADS-B消息传输波形ADS-B 消息包含4个识别脉冲,每个脉冲持续0.5±0.05μs。