一种使用滤波器实现射频功放输出口ESD防护的方法

- 格式:pdf

- 大小:159.84 KB

- 文档页数:3

5种ESD防护方法静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。

常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。

芯片级一般用HBM做测试,而电子产品则用IEC 6 100042的放电模型做测试。

为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 6100042 已建立起严格的瞬变冲击抑制标准;电子产品必须符合这一标准之后方能销往欧共体的各个成员国。

因此,大多数生产厂家都把 IEC 6100042看作是 ESD 测试的事实标准。

我国的国家标准(GB/T 17626.21998)等同于I EC 6 100042。

大多是实验室用的静电发生器就是按 IEC 6 100042的标准,分为接触放电和空气放电。

静电发生器的模型如图 1。

放电头按接触放电和空气放电分尖头和圆头两种。

IEC 6100042的 静电放电的波形如图2,可以看到静电放电主要电流是一个上升沿在1nS左右的一个上升沿,要消除这个上升沿要求ESD保护器件响应时间要小于这个时间。

静电放电的能量主要集中在几十MHz到500MHz,很多时候我们能从频谱上考虑,如滤波器滤除相应频带的能量来实现静电防护。

IEC 6100042规定了几个试验等级,目前手机CTA测试执行得是3级,即接触放电6KV,空气放电8KV。

很多手机厂家内部执行更高的静电防护等级。

当集成电路( IC )经受静电放电( ESD)时,放电回路的电阻通常都很小,无法限制放电电流。

例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的 IC 管脚。

瞬间大电流会严重损伤 IC ,局部发热的热量甚至会融化硅片管芯。

完整ESD及EMI保护方案对于电子产品而言,保护电路是为了防止电路中的关键敏感型器件受到过流、过压、过热等冲击的损害.保护电路的优劣对电子产品的质量和寿命至关重要.随着消费类电子产品需求的持续增长,更要求有强固的静电放电(ESD)保护,同时还要减少不必要的电磁干扰(EMI)/射频干扰(RFI)噪声。

此外,消费者希望最新款的消费电子产品可以用小尺寸设备满足越来越高的下载和带宽能力.随着设备的越来越小和融入性能的不断增加,ESD以及许多情况下的EMI/RFI抑制已无法涵盖在驱动所需接口的新一代IC当中。

另外,先进的系统级芯片(SoC)设计都是采用几何尺寸很小的工艺制造的.为了优化功能和芯片尺寸,IC设计人员一直在不断减少其设计的功能的最小尺寸。

IC尺寸的缩小导致器件更容易受到ESD电压的损害。

过去,设计人员只要选择符合IEC61000-4—2规范的一个保护产品就足够了.因此,大多数保护产品的数据表只包括符合评级要求。

由于集成电路变得越来越敏感,较新的设计都有保护元件来满足标准评级,但ESD冲击仍会形成过高的电压,有可能损坏IC。

因此,设计人员必须选择一个或几个保护产品,不仅要符合ESD脉冲要求,而且也可以将ESD冲击钳位到足够低的电压,以确保IC得到保护。

图1:美国静电放电协会(ESDA)的ESD保护要求先进技术实现强大ESD保护安森美半导体的ESD钳位性能备受业界推崇,钳位性能可从几种方法观察和量化。

使用几个标准工具即可测量独立ESD保护器件或集成器件的ESD钳位能力,包括ESD保护功能。

第一个工具是ESD IEC61000-4-2 ESD脉冲响应截图,显示的是随时间推移的钳位电压响应,可以看出ESD事件中下游器件的情形。

图2:ESD钳钳位截图除了ESD钳位屏幕截图,另一种方法是测量传输线路脉冲(TLP)来评估ESD钳位性能。

由于ESD事件是一个很短的瞬态脉冲,TLP可以测量电流与电压(I-V)数据,其中每个数据点都是从短方脉冲获得的。

ESD结构防护设计的主要目标是确保电子系统的功能可靠性,避免ESD(静电放电)对系统产生干扰或损坏。

以下是一些常见的ESD防护设计方法:

1. 隔离和接地:将ESD敏感器件隔离并接地可以有效地防止ESD 对系统的影响。

这可以通过在电路板上的敏感区域设置ESD防护器件,如TVS二极管、齐纳二极管等来实现。

2. 滤波器:在电源和信号线路上设置滤波器可以有效地减少ESD 产生的噪声干扰。

这可以通过使用LC滤波器、RC滤波器或者铁氧体磁珠等来实现。

3. 屏蔽:使用金属屏蔽材料将ESD敏感器件或电路板包裹起来,可以有效地防止ESD电磁场对系统的影响。

这可以通过在PCB上设置金属罩或者使用金属盒等方式来实现。

4. 限流:在ESD防护器件上设置限流电阻可以有效地限制ESD 电流的幅度,从而保护敏感器件或电路。

这可以通过在TVS二极管或齐纳二极管上串联限流电阻来实现。

5. 保护电路:在电路中添加保护电路可以防止ESD对电路的影响。

这可以通过在电路中添加电压钳位器件、过压保护器件等来实现。

6. 人体放电:在人体放电模型(HBM)下,通过设置放电电阻、电容等元件,可以有效地将人体静电放电引入到地线中,从而避免对系统的影响。

以上是一些常见的ESD防护设计方法,但具体的防护方案需要根据具体的系统和应用场景来确定。

5种ESD防护方法静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。

常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。

芯片级一般用HBM做测试,而电子产品则用IEC 6 100042的放电模型做测试。

为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 6100042 已建立起严格的瞬变冲击抑制标准;电子产品必须符合这一标准之后方能销往欧共体的各个成员国。

因此,大多数生产厂家都把 IEC 6100042看作是 ESD 测试的事实标准。

我国的国家标准(GB/T 17626.21998)等同于I EC 6 100042。

大多是实验室用的静电发生器就是按 IEC 6 100042的标准,分为接触放电和空气放电。

静电发生器的模型如图 1。

放电头按接触放电和空气放电分尖头和圆头两种。

IEC 6100042的 静电放电的波形如图2,可以看到静电放电主要电流是一个上升沿在1nS左右的一个上升沿,要消除这个上升沿要求ESD保护器件响应时间要小于这个时间。

静电放电的能量主要集中在几十MHz到500MHz,很多时候我们能从频谱上考虑,如滤波器滤除相应频带的能量来实现静电防护。

IEC 6100042规定了几个试验等级,目前手机CTA测试执行得是3级,即接触放电6KV,空气放电8KV。

很多手机厂家内部执行更高的静电防护等级。

当集成电路( IC )经受静电放电( ESD)时,放电回路的电阻通常都很小,无法限制放电电流。

例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的 IC 管脚。

瞬间大电流会严重损伤 IC ,局部发热的热量甚至会融化硅片管芯。

EMC知识大全传导与辐射电磁干扰(Electromagnetic Interference),简称EMI,有传导干扰和辐射干扰两种。

传导干扰主要是电子设备产生的干扰信号通过导电介质或公共电源线互相产生干扰;辐射干扰是指电子设备产生的干扰信号通过空间耦合把干扰信号传给另一个电网络或电子设备。

为了防止一些电子产品产生的电磁干扰影响或破坏其它电子设备的正常工作,各国政府或一些国际组织都相继提出或制定了一些对电子产品产生电磁干扰有关规章或标准,符合这些规章或标准的产品就可称为具有电磁兼容性EMC(Electromagnetic Compatibility)。

电磁兼容性EMC 标准不是恒定不变的,而是天天都在改变,这也是各国政府或经济组织,保护自己利益经常采取的手段。

EMC标准及测试国际标准1、国际电工委员为IEC2、国际标准华组织ISO3、电气电子工程师学会IEEE4、欧盟电信标准委员会ETSI5、国际无线电通信咨询委员CCIR6、国际通讯联盟ITU6、国际电工委员会IEC有以下分会进行EMC标准研究-CISPR:国际无线电干扰特别委员会-TC77:电气设备(包括电网)内电磁兼容技术委员会-TC65:工业过程测量和控制国际标准化组织1、FCC联邦通2、VDE德国电气工程师协会3、VCCI日本民间干扰4、BS英国标准5、ABSI美国国家标准6、GOSTR俄罗斯政府标准7、GB、GB/T中国国家标准EMI测试1、辐射骚扰电磁场(RE)2、骚扰功率(DP)3、传导骚扰(CE)4、谐波电路(Harmonic)5、电压波动及闪烁(Flicker)6、瞬态骚扰电源(TDV)EMS测试1、辐射敏感度试验(RS)2、工频次次辐射敏感度试验(PMS)3、静电放电抗扰度(ESD)4、射频场感应的传导骚扰抗扰度测试(CS)5、电压暂降,短时中断和电压变化抗扰度测试(DIP)6、浪涌(冲击)抗扰度测试(SURGE)7、电快速瞬变脉冲群抗扰度测试(EFT/B)8、电力线感应/接触(Power induction/contact)EMC测试结果的评价A级:实验中技术性能指标正常B级:试验中性能暂时降低,功能不丧失,实验后能自行恢复C级:功能允许丧失,但能自恢复,或操作者干预后能恢复R级:除保护元件外,不允许出现因设备(元件)或软件损坏数据丢失而造成不能恢复的功能丧失或性能降低。

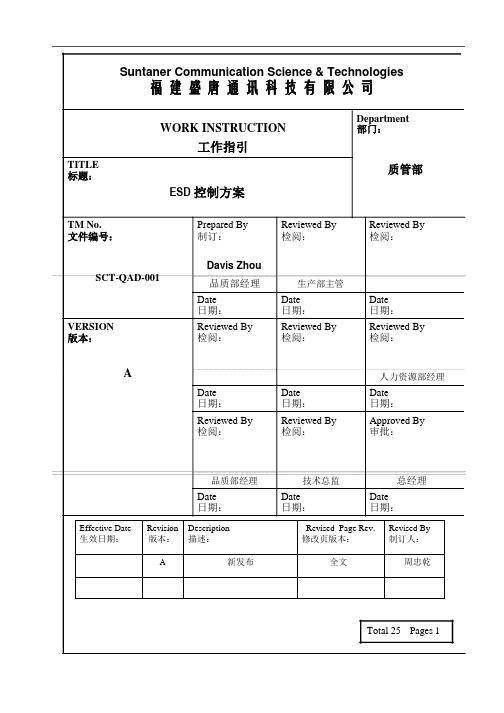

Suntaner Communication Science & Technologies 福建盛唐通讯科技有限公司WORK INSTRUCTION Department 部门:工作指引TITLE质管部标题:ESD 控制方案TM No.Prepared By Reviewed By Reviewed By 文件编号:制订:检阅:检阅:SCT-QAD-001Davis Zhou品质部经理生产部主管Date Date Date 日期:日期:日期:VERSION Reviewed By Reviewed By Reviewed By版本:检阅:检阅:检阅:A人力资源部经理Date Date Date日期:日期:日期:Reviewed By Reviewed By Approved By检阅:检阅:审批:品质部经理技术总监总经理Date Date Date日期:日期:日期:Effective Date Revision Description Revised Page Rev.Revised By 生效日期:版本:描述:修改页版本:制订人:A新发布全文周忠乾Total 25Pages 1WORK INSTRUCTION WI No.REV.工作指引工作指引编号:SCT-QAD-001版本:A Version Change HistoryRevision From To Date Revision Description Revised By Reviewed By 版本变更日期描述:修订人审核人A2006/2/18新发布周忠乾周忠乾WORK INSTRUCTION WI No.REV.工作指引工作指引编号:SCT-QAD-001版本:A1.0 目的:按 ANSI/ESD S20.20-1999 标准关于行政和技术上的要求,建立、实施和维护、改进公司防静电管理,对静电区域的产品(包括产品的各种状态)和人员、设备进行连续的防静电保护。

实用ESD防护设计方法陆健赵健徐佰新无锡华润矽科微电子有限公司论文摘要:本文就芯片设计中I/O口静电放电(Electrostatic Discharge, ESD)保护器件设计方法,在某一ESD失效模式下端口间ESD防护解决办法,及某些特殊内部结构制约整个电路ESD水平的解决办法;并介绍了一些新的射频电路ESD 保护结构,对如何提高芯片整体ESD性能作了一定的实际研究与总结, 在整体把握电路的ESD水平上给出一点启示。

1.引言静电在芯片的制造、封装、测试和使用过程中无处不在,积累的静电荷以几安培或几十安培的电流在纳秒到微秒的时间里释放,瞬间功率高达几百千瓦,放电能量可达毫焦耳,对芯片的摧毁强度极大。

所以芯片设计中静电保护模块的设计直接关系到芯片的功能稳定性,极为重要。

芯片的抗ESD能力是可靠性方面的一个非常重要的因素,电路的整体ESD能力有时往往是客户接受产品的一个非常重要的门坎,对于版图设计人员来说,如何整体把握电路ESD能力已是迫在眉睫,而非单单某些PIN的ESD能力提高。

一直以来,人们对电路的ESD保护都重点放在了I/O口处的ESD保护结构上,不遗余力的对其进行优化改进。

这种优化措施对有的电路的ESD保护有很大帮助,但是对有的电路却没什么效果。

针对这些优化ESD保护结构后仍旧没有改进的电路,我们进行了深入分析和大量讨论,发现电路的ESD特性不仅与电路中的ESD保护结构有关,还与电路内部结构有很大的关系。

ESD防护电路的安排必须全方位地考虑到ESD测试的各种组合,因为一颗IC的ESD 失效是看整颗IC所有脚中,在各种测试模式下,最低之ESD耐压值为该颗IC的ESD值。

射频电路的频率一般工作在低频段(30K~300K),中高频(3M~30M),高频(400M以上),在低频和中高频的ESD保护可以沿用一般的保护结构,但当电路工作在高频端时由于静电放电保护电路所造成的寄生效应,通常会造成射频电路的功率增益衰减,并且会增加噪声,在GHz频段的损害会更严重。

一种使用滤波器实现射频功放输出口ESD防护的方法马永华【摘要】文章分析人体模型电压波形的基波频谱范围,使用射频滤波器对人体模型电压波形的基波滤除,以实现对射频功放器件输出口的ESD防护.【期刊名称】《无线互联科技》【年(卷),期】2017(000)010【总页数】3页(P6-8)【关键词】ESD防护;射频功放;滤波器;ADS仿真【作者】马永华【作者单位】北京联合大学生物化学工程学院,北京 100023【正文语种】中文在生活中大家都有过静电放电 (Electro-Static Discharge,ESD)的体验,如冬天开门的时候,手去抓门把手的瞬间感受到刺痛,同时能看到一个小电弧的出现。

在实验室里如果工作不注意,用带有静电的手去接触设备,会导致工作设备失常。

射频功放因其工作频率高,其栅极通常都较薄,同时器件内部无法添加防静电电路,导致射频功放器件抗ESD的性能较弱。

如NXP公司出品的射频功放器件A2I20H080N,其抗HBM(人体模型)ESD的指标性能如表1所示。

国际ESD标准JESD22-A114防静电等级划分如图1所示。

从文中可以看出NXP A2i20H080N功放最大能承受的HBM的ESD电压为1 000~2 000 V,制作的射频电路如果不添加ESD防护器件或电路,NXPA2i20H080N这个器件被静电击毁的概率会很高。

在实际工作中,NXPA2i20H080N防静电等级为中等,所以防静电等级较低的抗静电性能更差。

如果在其射频频口上添加ESD防护电路或器件,可以极大提高NXP A2i20H080N等芯片的工作可靠性。

普通电路中为了提升电路的抗ESD性能,一般在器件ESD敏感管脚添加瞬态电压抑制器(Transient Voltage Suppressor,TVS)来实现电路抗ESD等级。

然而射频功放输出口不适合再添加TVS器件来提升射频功放的ESD性能。

原因如下:(1)TVS的结电容较大,将TVS器件添加在射频功放的输出口上会对射频的输出匹配造成影响,导致射频功放的输出匹配处于失配状态,从而降低了功放的输出功率;(2)TVS是非线性现器件,TVS器件添加在功放口上会造成射频信号的非线性失真,导致功放输出信号质量下降;(3)TVS等效内电阻较大,其添加在功放输出口上,因输出功率很大,TVS器件消耗很多的射频功率,导致TVS器件温度升高最终出现TVS器件烧毁。