ARM作业3

- 格式:doc

- 大小:2.97 KB

- 文档页数:3

arm嵌入式技术原理与应用答案【篇一:嵌入式系统原理与开发课后答案】章嵌入式系统概述:1、什么是嵌入式系统?是简单列举一些生活中常见的嵌入式系统的实例。

p3嵌入式系统是用于检测、控制、辅助、操作机械设备的装置。

以应用为中心,一计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗等严格要求的专用计算机系统。

3、是比较嵌入式系统与通用pc的区别。

p3(1)嵌入式系统是专用的计算机系统,而pc是通用的计算机系统。

(2)技术要求不同,通用pc追求高速、海量的数据运算;嵌入式要求对象体系的智能化控制。

(3)发展方向不同,pc追求总线速度的不断提升,存储容量不断扩大;嵌入式追求特定对象系统的智能性,嵌入式,专用性。

4、嵌入式体统有哪些部分组成?简单说明各部分的功能与作用。

p6(1)硬件层是整个核心控制模块(由嵌入式微处理器、存储系统、通信模块、人机接口、其他i/o接口以及电源组成),嵌入式系统的硬件层以嵌入式微处理器为核心,在嵌入式微处理器基础上增加电源电路、时钟电路、和存储器电路(ram和rom等),这就构成了一个嵌入式核心控制模块,操作系统和应用程序都可以固化在rom 中。

(2)中间层把系统软件与底层硬件部分隔离,使得系统的底层设备驱动程序与硬件无关。

一般包括硬件抽象层(hardware abstract layer,hal)和板级支持包(board support package,bsp)。

(3)软件层由实时操作系统(real time operating system,rtos)、文件系统、图形用户接口(graphical user interfaces,gui)、网络组件组成。

(4)功能层是面向被控对象和用户的,当需要用户操作是往往需要提供一个友好的人际界面。

5、嵌入式系统是怎么分类的?p7按照嵌入式微处理器的位数分类(4位、8位、16位、32位、64位);按照是实时性分类(硬实时系统式之系统对响应时间有严格的要求;软实时系统是对响应时间有一定要求);按照嵌入式软件结构分类(循环轮询系统、前后台系统、多任务系统);按照应用领域分类。

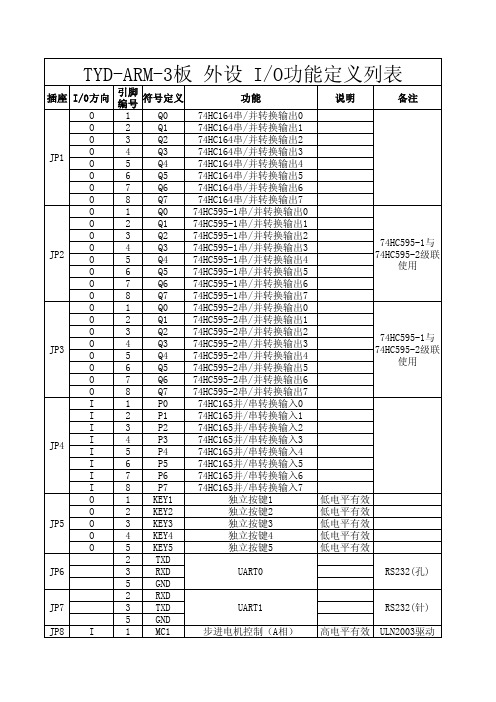

TYD-ARM-3板 外设 I/O功能定义列表插座I/0方向引脚编号符号定义功能说明备注JP1O1Q074HC164串/并转换输出0 O2Q174HC164串/并转换输出1 O3Q274HC164串/并转换输出2 O4Q374HC164串/并转换输出3 O5Q474HC164串/并转换输出4 O6Q574HC164串/并转换输出5 O7Q674HC164串/并转换输出6 O8Q774HC164串/并转换输出7 JP2O1Q074HC595-1串/并转换输出0 74HC595-1与74HC595-2级联使用O2Q174HC595-1串/并转换输出1 O3Q274HC595-1串/并转换输出2 O4Q374HC595-1串/并转换输出3 O5Q474HC595-1串/并转换输出4 O6Q574HC595-1串/并转换输出5 O7Q674HC595-1串/并转换输出6 O8Q774HC595-1串/并转换输出7 JP3O1Q074HC595-2串/并转换输出0 74HC595-1与74HC595-2级联使用O2Q174HC595-2串/并转换输出1 O3Q274HC595-2串/并转换输出2 O4Q374HC595-2串/并转换输出3 O5Q474HC595-2串/并转换输出4 O6Q574HC595-2串/并转换输出5 O7Q674HC595-2串/并转换输出6 O8Q774HC595-2串/并转换输出7 JP4I1P074HC165并/串转换输入0 I2P174HC165并/串转换输入1 I3P274HC165并/串转换输入2 I4P374HC165并/串转换输入3 I5P474HC165并/串转换输入4 I6P574HC165并/串转换输入5 I7P674HC165并/串转换输入6 I8P774HC165并/串转换输入7 JP5O1KEY1独立按键1低电平有效 O2KEY2独立按键2低电平有效 O3KEY3独立按键3低电平有效 O4KEY4独立按键4低电平有效 O5KEY5独立按键5低电平有效 JP6 2TXDUART0RS232(孔) 3RXD 5GND JP7 2RXDUART1RS232(针) 3TXD 5GND JP8I1MC1步进电机控制(A相)高电平有效ULN2003驱动JP8I2MC2步进电机控制(B相)高电平有效ULN2003驱动I3MC3步进电机控制(C相)高电平有效I4MC4步进电机控制(D相)高电平有效JP9O1Y074HC138译码输出0低电平有效 O2Y174HC138译码输出1低电平有效O3Y274HC138译码输出2低电平有效O4Y374HC138译码输出3低电平有效O5Y474HC138译码输出4低电平有效O6Y574HC138译码输出5低电平有效O7Y674HC138译码输出6低电平有效O8Y774HC138译码输出7低电平有效JP10 1OUT3步进电机C相 接步进电机 25V5V电源 3OUT1步进电机A相 4OUT4步进电机D相 5OUT2步进电机B相 JP11I1L1共阳极8*8点阵的行控1低电平有效JP11与JP22一起使用实现点阵LED动态扫描显示I2L2共阳极8*8点阵的行控2低电平有效I3L3共阳极8*8点阵的行控3低电平有效I4L4共阳极8*8点阵的行控4低电平有效I5L5共阳极8*8点阵的行控5低电平有效I6L6共阳极8*8点阵的行控6低电平有效I7L7共阳极8*8点阵的行控7低电平有效I8L8共阳极8*8点阵的行控8低电平有效JP12I1A8位共阴极数码管的段码A低电平有效JP12与JP13一起使用实现数码管动态扫描显示I2B8位共阴极数码管的段码B低电平有效I3C8位共阴极数码管的段码C低电平有效I4D8位共阴极数码管的段码D低电平有效I5E8位共阴极数码管的段码E低电平有效I6F8位共阴极数码管的段码F低电平有效I7G8位共阴极数码管的段码G低电平有效I8DP8位共阴极数码管的段码DP低电平有效JP13I1W18位共阴极数码管的位控制码1低电平有效JP12与JP13一起使用实现数码管动态扫描显示I2W28位共阴极数码管的位控制码2低电平有效I3W38位共阴极数码管的位控制码1低电平有效I4W48位共阴极数码管的位控制码3低电平有效I5W58位共阴极数码管的位控制码4低电平有效I6W68位共阴极数码管的位控制码5低电平有效I7W78位共阴极数码管的位控制码6低电平有效I8W88位共阴极数码管的位控制码7低电平有效JP14 1KL14*4矩阵键盘行线1 4*4矩阵扫描键盘带10K排电阻上拉 2KL24*4矩阵键盘行线2 3KL34*4矩阵键盘行线3 4KL44*4矩阵键盘行线4 5KS14*4矩阵键盘列线1 6KS24*4矩阵键盘列线2 7KS34*4矩阵键盘列线3 8KS44*4矩阵键盘列线4 JP15 1OPEN继电器常开触点 2COM继电器公共触点 3CLOSE继电器常闭触点 JP16 2PS2-DAT PS2标准键盘 35V 4GND 6PS2-CLK JP17O0KEY1独立按键1低电平有效低电平有效O1KEY2独立按键2低电平有效低电平有效 2RXD1UART1 3TXD1 JP18 0RXD2UART2 1TXD2 O2KEY3独立按键3低电平有效 O3KEY4独立按键4低电平有效 O4BELL蜂鸣器的控制口线 O5KEY5独立按键5低电平有效 JP19I0MC1步进电机控制(A相)高电平有效ULN2003驱动I1MC2步进电机控制(B相)高电平有效I2MC3步进电机控制(C相)高电平有效I3MC4步进电机控制(D相)高电平有效JP20O0RXD0UART0 O1TXD0 O2JDQ继电器控制线高电平有效 O3ADD074HC138译码输入0高电平有效 O4ADD174HC138译码输入0高电平有效 O5ADD274HC138译码输入0高电平有效 O6SCL I2C信号线 O7SDA I2C信号线 JP21I0ADC010位A/D转换器输入端0 模拟量测量I1ADC110位A/D转换器输入端1 I2ADC210位A/D转换器输入端2 I3ADC310位A/D转换器输入端3 I4ADC410位A/D转换器输入端4 I5ADC510位A/D转换器输入端5 I6ADC610位A/D转换器输入端6 I7ADC710位A/D转换器输入端7 JP22I1R1共阳极8*8点阵的列控1低电平有效JP11与JP22一起使用实现点阵LED动态扫描显示I2R2共阳极8*8点阵的列控2低电平有效I3R3共阳极8*8点阵的列控3低电平有效I4R4共阳极8*8点阵的列控4低电平有效I5R5共阳极8*8点阵的列控5低电平有效I6R6共阳极8*8点阵的列控6低电平有效I7R7共阳极8*8点阵的列控7低电平有效I8R8共阳极8*8点阵的列控8低电平有效JP23 15V USB 2D- JP23 3D+ USB 4GND JP24I1L18位独立发光管1低电平有效 I2L28位独立发光管2低电平有效I3L38位独立发光管3低电平有效I4L48位独立发光管4低电平有效I5L58位独立发光管5低电平有效I6L68位独立发光管6低电平有效I7L78位独立发光管7低电平有效I8L88位独立发光管8低电平有效JP25O0DB0液晶数据线输入0 O1DB1液晶数据线输入1 O2DB2液晶数据线输入2 O3DB3液晶数据线输入3 O4DB4液晶数据线输入4 O5DB5液晶数据线输入5 O6DB6液晶数据线输入6 O7DB7液晶数据线输入7 JP26O0DQ温度传感器口线 O1IRO空外接收头口线 O2SDAT74HC595数据口线 O3SCLK74HC595脉冲口线 O4LOAD74HC595时序口线 O5PL液晶恢度调节口线 O6SDI液晶口线 JP27 0/KEY ZLG7290复位口线 1 2PDAT PS2键盘数据口线 3PCLK PS2键盘脉冲口线 JP28 1GND JTAG调试器 2TCK 3TDI 4TDO 5TMS JP29 1 3.3V 3.3V 2 3.3V 3 3.3V 4 3.3V 5 GND GND 6 GND 7 GND 8 GND JP30 1 5V 5V 2 5V 3 5V 4 5V 5 GND GNDJP30 6 GND GND 7 GND 8 GND 。

北航ARM9实验报告:实验3uCOS-II实验北航 ARM9 实验报告:实验 3uCOSII 实验一、实验目的本次实验的主要目的是深入了解和掌握 uCOSII 实时操作系统在ARM9 平台上的移植和应用。

通过实际操作,熟悉 uCOSII 的任务管理、内存管理、中断处理等核心机制,提高对实时操作系统的理解和应用能力,为后续的嵌入式系统开发打下坚实的基础。

二、实验环境1、硬件环境:ARM9 开发板、PC 机。

2、软件环境:Keil MDK 集成开发环境、uCOSII 源代码。

三、实验原理uCOSII 是一个可裁剪、可剥夺型的多任务实时内核,具有执行效率高、占用空间小、实时性能优良和可扩展性强等特点。

其基本原理包括任务管理、任务调度、时间管理、内存管理和中断管理等。

任务管理:uCOSII 中的任务是一个独立的执行流,每个任务都有自己的堆栈空间和任务控制块(TCB)。

任务可以处于就绪、运行、等待、挂起等状态。

任务调度:采用基于优先级的抢占式调度算法,始终让优先级最高的就绪任务运行。

时间管理:通过系统时钟节拍来实现任务的延时和定时功能。

内存管理:提供了简单的内存分区管理和内存块管理机制。

中断管理:支持中断嵌套,在中断服务程序中可以进行任务切换。

四、实验步骤1、建立工程在 Keil MDK 中创建一个新的工程,选择对应的 ARM9 芯片型号,并配置相关的编译选项。

2、导入 uCOSII 源代码将 uCOSII 的源代码导入到工程中,并对相关的文件进行配置,如设置任务堆栈大小、系统时钟节拍频率等。

3、编写任务函数根据实验要求,编写多个任务函数,每个任务实现不同的功能。

4、创建任务在主函数中使用 uCOSII 提供的 API 函数创建任务,并设置任务的优先级。

5、启动操作系统调用 uCOSII 的启动函数,使操作系统开始运行,进行任务调度。

6、调试与测试通过单步调试、查看变量值和输出信息等方式,对系统的运行情况进行调试和测试,确保任务的执行符合预期。

ARM Cortex-M3 内核介绍内核包含四部分:1.乘法器;2.控制逻辑;3.Thumb 指令译码器;4.内部接口CM3 内部包含元素介绍:1. DAP,调试访问接口,Debug Access Port。

Cortex‐M3 的调试系统基于ARM 最新的CoreSight 架构。

不同于以往的ARM 处理器,内核本身不再含有JTAG 接口。

取而代之的,是CPU 提供称为调试访问接口(DAP)的总线接口。

通过这个总线接口,可以访问芯片的寄存器,也可以访问系统存储器,甚至是在内核运行的时候访问!对此总线接口的使用,是由一个调试端口(DP)设备完成的。

DPs 不属于CM3 内核,但它们是在芯片的内部实现的。

目前可用的DPs 包括SWJ‐DP(既支持传统的JTAG 调试,也支持新的串行线调试协议),另一个SW‐DP 则去掉了对JTAG 的支持。

另外,也可以使用ARM CoreSignt 产品家族的JTAG‐DP 模块。

这下就有 3 个DPs 可以选了,芯片制造商可以从中选择一个,以提供具体的调试接口(通常都是选SWJ‐DP)。

2. ETM 的作用就是记录处理器做的事情并送到外面的调试器。

由于微控制器带有大量的片内存储器,因此不能简单地通过观察外部管脚来确定处理器核是如何运行的。

ETM 对深嵌入处理器内核提供了实时跟踪能力。

它向一个跟踪端口输出处理器执行的信息。

软件调试器允许使用JTAG 接口对ETM 进行配置并以用户易于理解的格式显示捕获到的跟踪信息。

ETM 直接连接到ARM 内核而不是主AMBA 系统总线。

3.NVIC 是Cortex-M3 处理器中一个完整的部分,它可以进行高度配置,为处理器提供出色的中断处理能力。

在NVIC 的标准执行中,它提供了一个非屏蔽中断(NMI)和32 个通用物理中断,这些中断带有8 级的抢占优先权。

NVIC可以通过综合选择配置为1 到240 个物理中断中的任何一个,并带有多达256。

ARM3_汇编指令16位数据操作指令名字功能ADC 带进位加法(ADD with Carry)ADD 加法AND 按位与。

这里的按位与和C的”&”功能相同ASR 算术右移(Arithmetic Shift Right)BIC 按位清零(把一个数跟另一个无符号数的反码按位与)CMN 负向比较(把一个数跟另一个数据的二进制补码相比较)CMP 比较(Compare,比较两个数并且更新标志)CPY 把一个寄存器的值拷贝(COPY)到另一个寄存器中EOR 近位异或LSL 逻辑左移(Logic Shift Left)LSR 逻辑右移(Logic Shift Right)MOV 寄存器加载数据,既能用于寄存器间的传输,也能用于加载立即数MUL 乘法(Multiplication)MVN 加载一个数的NOT值(取到逻辑反的值)NEG 取二进制补码ORR 按位或ROR 循环右移SBC 带借位的减法SUB 减法(Subtraction)TST 测试(Test,执行按位与操作,并且根据结果更新Z)REV 在一个32位寄存器中反转(Reverse)字节序REVH 把一个32位寄存器分成两个(Half)16位数,在每个16位数中反转字节序REVSH 把一个32位寄存器的低16位半字进行字节反转,然后带符号扩展到32位SXTB 带符号(Signed)扩展一个字节(Byte)到32位SXTH 带符号(Signed)扩展一个半字(Half)到32位UXTB 无符号(Unsigned)扩展一个字节(Byte)到32位UXTH 无符号(Unsigned)扩展一个半字(Half)到32位16位转移指令名字功能B 无条件转移(Branch)B 有条件(Condition)转移BL 转移并连接(Link)。

用于呼叫一个子程序,返回地址被存储在LR中CBZ 比较(Compare),如果结果为零(Zero)就转移(只能跳到后面的指令)CBNZ 比较,如果结果非零(Non Zero)就转移(只能跳到后面的指令)IT If-Then16位存储器数据传送指令名字功能LDR 从存储器中加载(Load)字到一个寄存器(Register)中LDRH 从存储器中加载半(Half)字到一个寄存器中LDRB 从存储器中加载字节(Byte)到一个寄存器中LDRSH 从存储器中加载半字,再经过带符号扩展后存储一个寄存器中LDRSB 从存储器中加载字节,再经过带符号扩展后存储一个寄存器中STR 把一个寄存器按字存储(Store)到存储器中STRH 把一个寄存器存器的低半字存储到存储器中STRB 把一个寄存器的低字节存储到存储器中LDMIA 加载多个字,并且在加载后自增基址寄存器STMIA 存储多个字,并且在存储后自增基址寄存器PUSH 压入多个寄存器到栈中POP 从栈中弹出多个值到寄存器中其它16位指令名字功能SVC 系统服务调用(Service Call)BKPT 断点(Break Point)指令。

北航ARM9嵌⼊式系统实验实验三uCOS-II实验实验三 uCOS-II实验⼀、实验⽬的在内核移植了uCOS-II 的处理器上创建任务。

⼆、实验内容1)运⾏实验⼗,在超级终端上观察四个任务的切换。

2)任务1~3,每个控制“红”、“绿”、“蓝”⼀种颜⾊的显⽰,适当增加OSTimeDly()的时间,且优先级⾼的任务延时时间加长,以便看清三种颜⾊。

3)引⼊⼀个全局变量BOOLEAN ac_key,解决完整刷屏问题。

4)任务4管理键盘和超级终端,当键盘有输⼊时在超级终端上显⽰相应的字符。

三、预备知识1)掌握在EWARM 集成开发环境中编写和调试程序的基本过程。

2)了解ARM920T 处理器的结构。

3)了解uCOS-II 系统结构。

四、实验设备及⼯具1)2410s教学实验箱2)ARM ADS1.2集成开发环境3)⽤于ARM920T的JTAG仿真器4)串⼝连接线五、实验原理及说明所谓移植,指的是⼀个操作系统可以在某个微处理器或者微控制器上运⾏。

虽然uCOS-II的⼤部分源代码是⽤C语⾔写成的,仍需要⽤C语⾔和汇编语⾔完成⼀些与处理器相关的代码。

⽐如:uCOS-II在读写处理器、寄存器时只能通过汇编语⾔来实现。

因为uCOS-II 在设计的时候就已经充分考虑了可移植性,所以,uCOS-II的移植还是⽐较容易的。

要使uCOS-II可以正常⼯作,处理器必须满⾜以下要求:(1)处理器的C编译器能产⽣可重⼊代码可重⼊的代码指的是⼀段代码(如⼀个函数)可以被多个任务同时调⽤,⽽不必担⼼会破坏数据。

也就是说,可重⼊型函数在任何时候都可以被中断执⾏,过⼀段时间以后⼜可以继续运⾏,⽽不会因为在函数中断的时候被其他的任务重新调⽤,影响函数中的数据。

(2)在程序中可以打开或者关闭中断在uCOS-II中,可以通过OS_ENTER_CRITICAL()或者OS_EXIT_CRITICAL()宏来控制系统关闭或者打开中断。

这需要处理器的⽀持,在ARM920T的处理器上,可以设置相应的寄存器来关闭或者打开系统的所有中断。

1章绪论1.国内嵌入式系统行业对“嵌入式系统”的定义是什么?如何理解?答:见教材1.1节。

2.嵌入式系统是从何时产生的,简述其发展历程。

答:见教材1.1节。

3.当前最常见的源码开放的嵌入式操作系统有哪些,请举出两例,并分析其特点。

答:见教材1.2.1节的嵌入式Linux和嵌入式实时操作内核UC /OS-I 。

4.举例说明嵌入式设备在工控设备中的应用。

答:见教材1.3节的“工业控制领域”。

5.未来嵌入式技术的发展趋势有哪些?答:见教材1.4节的嵌入式技术的发展趋势。

2章ARM技术与ARM体系结构1.简述ARM处理器内核调试结构原理。

答:对教材1.2节的图2-1进行描述。

2.分析ARM7TDMI-S各字母所代表的含义。

答:参考教材2.1.2 ARM核版本命名规则说明。

3.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异常模式,并指出处理器在什么情况下进入相应的模式。

ARM处理器共有7种工作模式:用户模式:非特权模式,也就是正常程序执行的模式,大部分任务在这种模式下执行。

在用户模式下,如果没异常发生,不允许应用程序自行改变处理器的工作模式,如果有异常发生,处理器会自动切换工作模式FIQ模式:也称为快速中断模式,支持高速数据传输和通道处理,当一个高优(fast)中断产生时将会进入这种模式。

IRQ模式:也称为普通中断模式,:当一个低优先级中断产生时将会进入这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ 模式下进行。

SVC模式:称之为管理模式,它是一种操作系统保护模式。

当复位或软中断指令执行时处理器将进入这种模式。

中止模式:当存取异常时将会进入这种模式,用来处理存储器故障、实现虚拟存储或存储保护。

未定义指令异常模式:当执行未定义指令时会进入这种模式,主要是用来处理未定义的指令陷阱,支持硬件协处理器的软件仿真,因为未定义指令多发生在对协处理器的操作上。

第1篇第一章:概述1.1 GIC ARM 简介GIC ARM,即通用中断控制器(General Interrupt Controller)ARM,是一种用于ARM架构处理器中的中断处理机制。

它能够处理来自多个中断源的中断请求,并按照优先级进行排序,以便CPU能够高效地处理这些中断。

1.2 GIC ARM 的作用GIC ARM 的主要作用是简化中断处理过程,提高CPU的响应速度和效率。

它通过以下方式实现:- 中断优先级管理:GIC ARM 可以根据中断源的优先级进行排序,确保高优先级的中断能够得到及时处理。

- 中断分发:GIC ARM 将中断请求分发到相应的处理单元,减少CPU的干预。

- 中断去抖动:GIC ARM 可以检测并抑制短暂的中断请求,避免因抖动导致的错误处理。

第二章:GIC ARM 架构2.1 GIC ARM 模块GIC ARM 包含以下几个模块:- GIC CPU接口:负责与CPU通信,接收中断请求并转发给CPU。

- GIC分发器:负责将中断请求分配到相应的处理单元。

- GIC处理器:负责处理中断请求,包括中断屏蔽、去抖动和优先级管理。

2.2 GIC ARM 的接口GIC ARM 提供以下接口:- GIC CPU接口:包括CPU接口寄存器,用于配置和查询GIC ARM的状态。

- GIC分发器接口:包括分发器接口寄存器,用于配置和查询分发器的状态。

- GIC处理器接口:包括处理器接口寄存器,用于配置和查询处理器的状态。

第三章:GIC ARM 配置3.1 GIC CPU接口配置配置GIC CPU接口需要以下步骤:- 配置CPU接口寄存器:设置中断优先级、启用或禁用中断等。

- 配置中断处理函数:为每个中断源指定相应的处理函数。

3.2 GIC分发器接口配置配置GIC分发器接口需要以下步骤:- 配置分发器接口寄存器:设置中断源、中断目标等。

- 配置中断优先级:设置每个中断源的优先级。

3.3 GIC处理器接口配置配置GIC处理器接口需要以下步骤:- 配置处理器接口寄存器:设置中断屏蔽、去抖动等。

程序:

#include "config.h"

#define KEY2 0x00004000 //P0.14控制LED2CON

#define LED2CON 0x00000800 //P0.11低电平时点亮LED2CON

#define time0 Fpclk/10 //初始状态下一周期低电平时间0.1s

#define time1 Fpclk //方波周期2s

//函数声明

void __irq IRQ_Timer0(void);

void __irq IRQ_Eint1(void);

//全局变量定义

uint32 i=0; //KEY2每按下一次,此变量加0.1s

int main(void)

{

//管脚功能选择初始化化

PINSEL0=0x20000000; //P0.14设置为EINT1

IODIR = LED2CON; //P0.11设置为输出

IOCLR = LED2CON; //P0.11输出清零,LED2CON点亮

//中断选择初始化化

VICIntEnable=0x00008010; //中断使能Timer0和EINT1

VICIntSelect=0x00000000; //设置中断类型为IRQ

VICVectCntl0=0x24; //Timer0分配为通道0

VICVectAddr0=(uint32)IRQ_Timer0;

VICVectCntl1=0x2F; //EINT1分配为通道1

VICVectAddr1=(int)IRQ_Eint1;

//外部中断输入初始化化

EXTMODE =0x00000002; //设置外部中断的输入极性为下降沿

EXTPOLAR=0x00000000;

EXTINT = 0x02; //清除EINT1的中断标志

//定时器初始化

T0TC=0; //定时器清零

T0PR=0; //不分频

T0MCR=0x19; //MR0匹配时产生中断,MR1匹配时定时器清零并产生中断

T0MR0=time0; //MR0定时初值0.1s

T0MR1=time1; //MR1定时初值2s

T0IR = 0x03; //清除MR0、MR1的中断标志

T0TCR=0x01; //启动定时器

while(1); //等待Timer0中断或EINT1中断

return(0);

}

/*******************************************************************************

*名称: IRQ_Timer0()

*功能: 定时器Timer0服务函数,取反LED2CON

*******************************************************************************/ void __irq IRQ_Timer0(void)

{

if((IOPIN&LED2CON)==0) //读取LEDCON2状态并取反

{

IOSET=LED2CON;

}

else

{

IOCLR=LED2CON;

}

while((T0IR&0x01)!=0) //等待TOMR0中断信号恢复为高电平

{

T0IR=0x01; //清除TOMR0中断标志

}

while((T0IR&0x02)!=0) //等待TOMR1中断信号恢复为高电平

{

T0IR=0x02; //清除TOMR1中断标志

}

VICVectAddr=0x00; /*向量中断结束*/

}

/******************************************************************************* *名称: IRQ_Eint1()

*功能: 外部中断EINT1服务函数,当低电平<1.9s时,加0.1s;超过1.9s后复位(低电平0.1s)*******************************************************************************/ void __irq IRQ_Eint1(void)

{

if(T0MR0<(time1-time0))

{

i+=time0; //低电平<1.9s时,定时时间加0.1s

T0MR0+=i;

}

else

{

T0MR0=time0; //低电平=1.9s时,定时时间复位

i=0;

}

while((EXTINT&0x02)!=0) //等待外部中断信号恢复为高电平

{

EXTINT=0x02; //清除EINT1中断标志

}

VICVectAddr=0x00; //返回

}

电路图:

流程图:

主函数流程图定时器中断服务函数流程图。