可控脉冲发生器的设计

- 格式:doc

- 大小:44.00 KB

- 文档页数:4

成绩评定表课程设计任务书摘要可控脉冲发生器是产生脉冲波形信号的电路,本次课设要求除了控制周期和占空比外,还需要具有初始化生成周期为2.5秒占空比为1:1的脉冲信号功能。

本文介绍了依据可控脉冲发生器功能要求进行内部电路方案设计的过程,并在此基础上将输入、输出以及各个控制端口的逻辑关系细化,制成flowchart,然后按照流程图的逻辑顺序用Verilog HDL语言描述出来,再用ModelSim进行功能仿真、分析仿真波形得出结果。

在QuartusII下进行逻辑综合和适配下载,最后在Xilinx公司的Cyclone的芯片EP1C6Q240C8中绑定管脚,进行硬件仿真,完整地建立了测试平台,完成了功能和时序仿真,从而保证了设计的功能与时序的正确性。

关键词占空比;周期;可控脉冲;仿真;QUARTUSII目录摘要 ............................................................................ III 引言 (1)1 总体电路结构设计 (2)1.1 电路功能与性能 (2)1.2主要算法和实现难点 (3)1.3电路接口 (3)1.4电路功能框图 (4)1.5 验证方案 (4)2 模块设计 (7)3 设计仿真与测试 (12)3.1仿真与测试的功能列表 (12)3.2仿真平台构建和仿真结果 (13)3.2.1 顶层仿真平台与激励 (13)3.2.2 电路功能仿真结果 (13)_Toc3770527063.2.3 电路后仿真结果 (15)3.3测试环境的搭建与测试结果 (15)3.3.1 测试环境模拟 (15)3.3.2 电路测试结果 (16)4 电路约束与综合实现 (16)4.1时序约束 (16)4.2引脚锁定约束 (17)4.3电路综合报告 (17)4.4设计实现与下载 (18)结论 (19)参考文献 (20)附录设计源代码 (21)引言VHDL的英文全名是Very-High-Speed Integrated Circuit Hardware Description Language Verilog作为IEEE的工业标准硬件描述语言,在电子工程领域,已成为事实上的通用硬件描述语言。

脉冲信号发生器的制作课程设计(一)脉冲信号发生器用220V/50XX的工频交流电供电.(注:直流电源部分仅完成设计即可,不需制作,用实验室稳压电源调试)XX按照以上技术完成要求设计出电路,绘制电路图,对设计的电路用Multisim2021或OrCAD/PspiceAD9。

2进行必要的仿真,仿真通过后购买元器件,用万用板焊接电路,然后对制作的电路完成调试,撰写设计报告,通过答辩。

XX课程设计总结报告要求:XX题目任务书XX XX概述(简要说明本设计的基本内容)XX技术性能指标XX分析技术要求,选择技术方案,确定原理方框图,分析工作原理XX单元电路的设计(工作原理、元器件的选择、有关仿真波形和实测波形)XX总电路原理图(图纸大小自定,但要符合标准,可手工绘制,亦可用相关C AD软件如Protel、Multisim、OrCAD/PspiceAD等绘制)XX 附录(元器件明细表、需要专门说明或论述的问题、)XX10、总结及体会11、制作的电路XX三、设计进度:XX1、三周(2021.12。

8-—2021.12.26XX2、进度:(1)第一周熟悉题目,分析要求,查找资料,选择方案,优化方案,确定原理方框图。

(2)第二周单元电路设计,选择元器件,进行必要的仿真,确定电路原理图,画出电路原理图,购买元器件.XX(3)第三周焊接电路,调试,通过测试,技术总结、完成训练报告,答辩.目录一、摘要 (1)二、技术性能指标…………………………………………(2)XX三、方案选择和确定 (3)四、单元电路的设计 (5)五、实验仿真………………………………………………(13)六、电路板安装调试………………………………………(14)XX七、附录 (18)八、总结及体会……………………………………………(20)XX摘要XX信号发生电路是一种不需要外加激励就能将直流能源转化成具有一定频率和一定幅度一定波形的交流能量输出电路,又成为振荡器或波形发生器.通过与波形变换电路相结合,它能产生**种波形,能满足现代通信,自动控制,热加工.音XX系统和数字系统等对**种信号的要求.本次课程设计的任务是设计并制作一个脉冲信号发生器,整体设计通过四个主要模块完成,每一个模块完成一个功能.采用文氏桥式电路产生一个1KXX正弦波信号,通过由555定时器连接成的施密特触发器,变换成同频率的方波,再经一个由同步二进制计数器74LS161接成的十进制计数器将1KXX 脉冲转换成100XX输出,进行第一次频率变换.最后经锁相环,实现100倍频目的.整个系统由220V交流供电,测试结果通示波器观察即可.XX 在此过程中,我们对组合逻辑电路、时序逻辑电路数、数字集成电路、小规模的门电路的功能及其有了进一步的了解和掌握 ,达到了更加熟练的应用这些器件的目的。

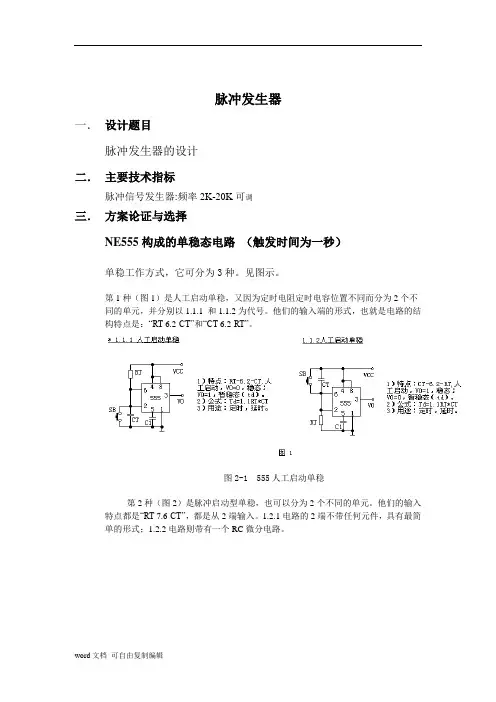

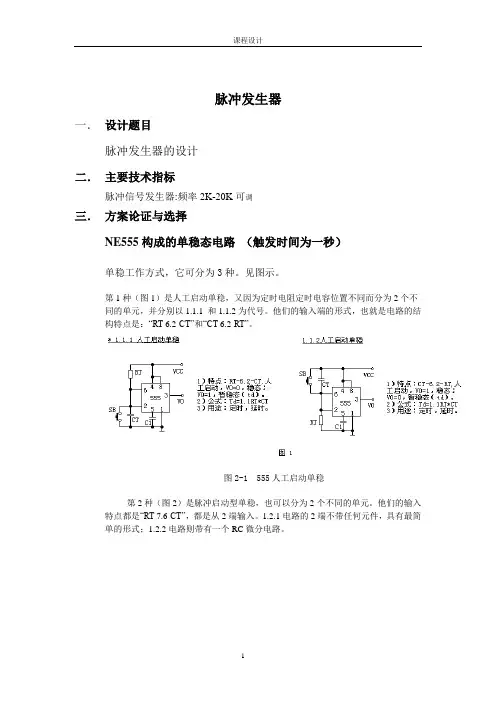

脉冲发生器一.设计题目脉冲发生器的设计二.主要技术指标脉冲信号发生器:频率2K-20K可调三.方案论证与选择NE555构成的单稳态电路(触发时间为一秒)单稳工作方式,它可分为3种。

见图示。

第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1 和1.1.2为代号。

他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

图2-1 555人工启动单稳第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。

他们的输入特点都是“RT-7.6-CT”,都是从2端输入。

1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。

图2-2 555脉冲启动单稳第3种(图3)是压控振荡器。

单稳型压控振荡器电路有很多,都比较复杂。

为简单起见,我们只把它分为2个不同单元。

不带任何辅助器件的电路为1.3.1;使用晶体管、运放放大器等辅助器件的电路为1.3.2。

图中列出了2个常用电路。

图2-3单稳型压控振荡电路四.系统总图图2-4 总体电路图波形发生器一、设计题目波形发生器的设计与制作二.主要技术指标输出频率为160Hz的正弦波、方波、三角波。

正弦波幅度10V;方波幅度6V;三角波幅度为4V。

三.方案论证及选择:正弦波:方案一、由R、C振荡电路产生,其中包括R、C串并联电路和R、C移相电路两种。

方案二、由L、C振荡电路产生。

方案三、由集成运放构成的RC桥式振荡电路产生。

包括放大、反馈、选频和稳幅等基本部分。

输出波形稳定性良好。

方波:方案一、方波可由NE555构成多谐振荡器来产生。

方案二、由运放构成的电压比较器,在运放的输出端引入限流电阻和两个背靠背的稳压管组成双向限幅方波产生电路。

三角波:方案一、由方波来产生:可以由NE555电路产生的方波或是集成运放产生的通过R、C积分来得到。

方案二、由同相输入迟滞比较器和积分器产生方案选择:通过对以上方案进行比较,我们选择的方案是:正弦波是由集成运放构成的RC 桥式振荡电路产生。

摘要:本实验是采用fpga方式基于Alter Cyclone2 EP2C5T144C8的简易脉冲信号发生器,可以实现输出一路周期1us到10ms,脉冲宽度:0.1us到周期-0.1us,时间分辨率为0.1us的脉冲信号,并且还能输出一路正弦信号(与脉冲信号同时输出)。

输出模式可分为连续触发和单次手动可预置数(0~9)触发,具有周期、脉宽、触发数等显示功能。

采用fpga计数实现的电路简化了电路结构并提高了射击精度,降低了电路功耗和资源成本。

关键词:FPGA;脉冲信号发生器;矩形脉冲;正弦信号;引言(一)方案设计与比较脉冲信号产生方案:方案一、采用专用DDS芯片的技术方案:目前已有多种专用DDS集成芯片可用,采用专用芯片可大大简化系统硬件制作难度,内部数字信号抖动小,输出信号指标高;但专用芯片控制方式比较固定,最大的缺点是进行脉宽控制,测量困难,无法进行外同步,不满足设计要求。

方案二、单片机法:利用单片机实现矩形脉冲,可以较方案以更简化外围硬件,节约成本,并且也可以实现灵活控制、能产生任意波形的信号发生器。

但是单片机的内部时钟一般是小于25Mhz,速度上无法满足设计要求,通过单片机产生脉冲至少需要三条指令,所需时间大于所要求的精度要求,故不可取。

方案二:FPGA法:利用了可编程逻辑器件的灵活性且资源丰富的特点,通过Quartus软件的设计编写,实现脉冲信号的产生及数控,并下载到试验箱中,这种方案电路简单、响应速度快、精度高、稳定性好故采用此种方案。

(二)理论分析与计算脉冲信号产生原理:输入量周期和脉宽,结合时钟频率,转换成两个计数器的容量,用来对周期和高电平的计时,输出即可产生脉冲信号。

脉冲信号的精度保证:时间分辨率0.1us,周期精度:+0.1%+0.05us,宽度精度:+0.1%+0.05us,为满足精度要求,所以所选时钟频率至少1/0.05us=20MHZ,由于试验箱上大于10MHZ只有50MHZ,故选时钟信号50MHZ,此时精度1/50MHZ=0.02us<0.05us,满足精度要求。

1 引言要求改变脉冲周期和输出脉冲个数的脉冲输出电路模块在许多工业领域都有运用。

采用数字器件设计周期和输出个数可调节的脉冲发生模块是方便可行的。

为了使之具有高速、灵活的优点,本文采用Atelra公司的可编程芯片FPGA设计了一款周期和输出个数可变的脉冲发生器。

经过板级调试获得良好的运行效果。

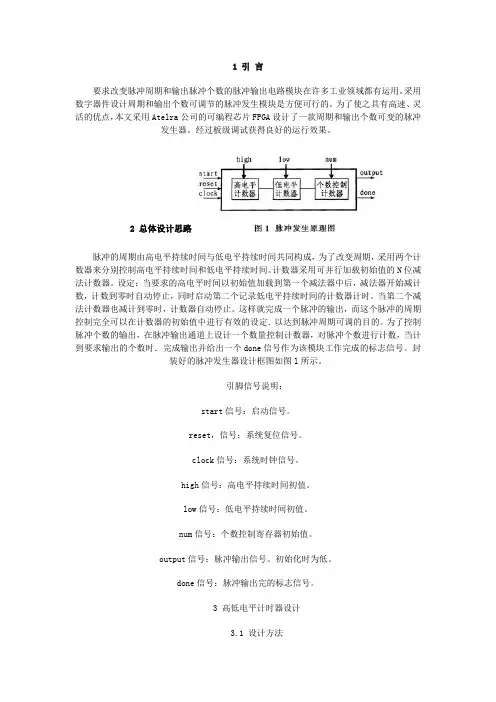

2 总体设计思路脉冲的周期由高电平持续时间与低电平持续时间共同构成,为了改变周期,采用两个计数器来分别控制高电平持续时间和低电平持续时间。

计数器采用可并行加载初始值的N位减法计数器。

设定:当要求的高电平时间以初始值加载到第一个减法器中后,减法器开始减计数,计数到零时自动停止,同时启动第二个记录低电平持续时间的计数器计时。

当第二个减法计数器也减计到零时,计数器自动停止。

这样就完成一个脉冲的输出,而这个脉冲的周期控制完全可以在计数器的初始值中进行有效的设定.以达到脉冲周期可调的目的。

为了控制脉冲个数的输出,在脉冲输出通道上设计一个数量控制计数器,对脉冲个数进行计数,当计到要求输出的个数时.完成输出并给出一个done信号作为该模块工作完成的标志信号。

封装好的脉冲发生器设计框图如图l所示。

引脚信号说明:start信号:启动信号。

reset,信号:系统复位信号。

clock信号:系统时钟信号。

high信号:高电平持续时间初值。

low信号:低电平持续时间初值。

num信号:个数控制寄存器初始值。

output信号:脉冲输出信号。

初始化时为低。

done信号:脉冲输出完的标志信号。

3 高低电平计时器设计3.1 设计方法为了产生所需要时间的高电平,可以利用一个可预置数的减法计数器来达到目的,计数器设计分为两个部分,一部分是可预置数的自控制减法计数器:另一部分是减法计数器工作完成后的检测计数器工作完成后输出一个时钟周期宽的脉冲作为该计数器工作完成信号,并可作为下一个计数器工作的启动信号。

原理框图如图2所示。

3.2 工作原理首先.外部的复位信号reset给出一个时钟周期宽的脉冲,复位内部各个信号及触发器。

可控脉冲发生器的设计一、 实验目的1、 了解可控脉冲发生器的实现机理。

2、 学会用示波器观察FPGA 产生的信号。

3、 学习用VHDL 编写复杂功能的代码。

二、 实验原理脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:三、 实验内容编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

四、 实验程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity exp10 isport( Clk : in std_logic; --时钟输入Rst : in std_logic; --复位输入⎩⎨⎧≤≤<≤=N T M M T Q 001%1001)1(⨯+=+=N M T N CLOCK占空比周期NU,ND : in std_logic; --输入:控制频率的改变MU,MD : in std_logic; --输入:控制占空比的改变Fout : out std_logic --波形输出);end exp10;architecture behave of exp10 issignal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);signal N_Count :std_logic_vector(10 downto 0);signal clkin : std_logic;signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断beginprocess(Clk) --计数器累加beginif(Clk'event and Clk='1') thenif(N_Count=N_Buffer) thenN_Count<="00000000000";elseN_Count<=N_Count+1;end if;end if;end process;process(Clk) --波形判断beginif(Clk'event and Clk='1') thenif(N_Count<M_Buffer) thenFout<='1';elsif(N_Count>M_Buffer and N_Count<N_Buffer) thenFout<='0';end if;end if;end process;process(Clk)beginif(Clk'event and Clk='1') thenClk_Count<=Clk_Count+1;end if;clkin<=Clk_Count(12);end process;process(clkin) --频率及占空比的改变1beginif(clkin'event and clkin='0') thenif(Rst='0') thenM_Buffer<="010********";N_Buffer<="10000000000";elsif(NU='0') thenN_Buffer<=N_Buffer+1;elsif(ND='0') thenN_Buffer<=N_Buffer-1;elsif(MU='0') thenM_Buffer<=M_Buffer+1;elsif(MD='0') thenM_Buffer<=M_Buffer-1;end if;end if;end process;end behave;五、时序仿真图。

延时可控高压脉冲发生器的设计延时可控高压脉冲发生器的设计延时可控高压脉冲发生器的设计1引言以往研制的高压脉冲发生器采用V型管作为高压脉冲形成级,该管为冷阴极结构形式,一般工作电压在10~15kV范围内,输出高压脉冲相对外触发的延时随直流供电电压的不同而有较大变化,抖动也较大,且长时间工作后,延时和抖动都要增大。

用于触发Marx发生器及高电压脉冲触发装置需要更高的高压触发脉冲,且需在5~30kV范围内连续可调,具有前沿快、延时准确稳定、抖动小、抗干扰能力强等性能。

设计高压脉冲形成级是本机的重点,关键是选择能满足本机各项技术指标要求的高电压、大电流、快速开关管。

为了提高触发系统的延时精度,采用精度为10ns的数字延时单元,延时在10ns~99μs范围,步进10ns,以CPU8031为控制核心的集成电路实现人机对话,增强可靠性和先进性。

直流高压供电采用DC/DC变换技术,封装在金属盒内,实现了电源小型化,增强了抗干扰能力。

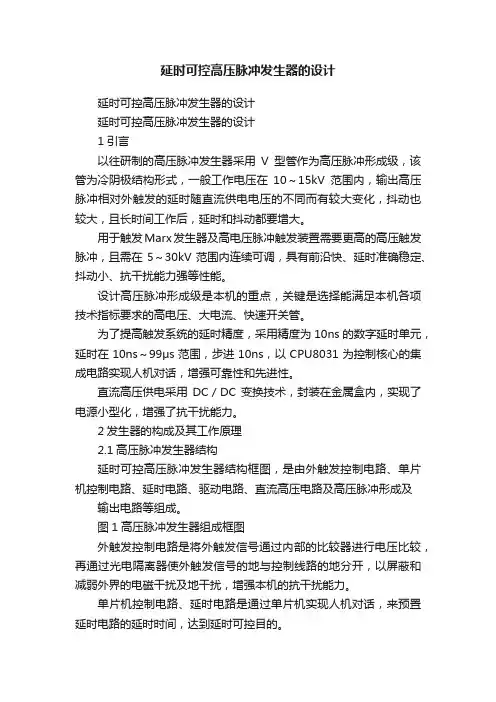

2发生器的构成及其工作原理2.1高压脉冲发生器结构延时可控高压脉冲发生器结构框图,是由外触发控制电路、单片机控制电路、延时电路、驱动电路、直流高压电路及高压脉冲形成及输出电路等组成。

图1高压脉冲发生器组成框图外触发控制电路是将外触发信号通过内部的比较器进行电压比较,再通过光电隔离器使外触发信号的地与控制线路的地分开,以屏蔽和减弱外界的电磁干扰及地干扰,增强本机的抗干扰能力。

单片机控制电路、延时电路是通过单片机实现人机对话,来预置延时电路的延时时间,达到延时可控目的。

驱动电路是将延时电路输出幅度较低的脉冲信号变为较高幅度的脉冲信号,用以驱动后级高压脉冲形成电路。

直流高压电路采用DC/DC变换,低压24V经振荡电路产生频率较高交流信号,再经高频脉冲变压器升压及多级倍压输出5~30kV连续可调的直流高压,为高压脉冲形成电路供电。

高压脉冲形成输出电路是本机重要部分,主要是形成和输出负高压脉冲。

脉冲发生器一.设计题目脉冲发生器的设计二.主要技术指标脉冲信号发生器:频率2K-20K可调三.方案论证与选择NE555构成的单稳态电路(触发时间为一秒)单稳工作方式,它可分为3种。

见图示。

第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1 和1.1.2为代号。

他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

图2-1 555人工启动单稳第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。

他们的输入特点都是“RT-7.6-CT”,都是从2端输入。

1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。

图2-2 555脉冲启动单稳第3种(图3)是压控振荡器。

单稳型压控振荡器电路有很多,都比较复杂。

为简单起见,我们只把它分为2个不同单元。

不带任何辅助器件的电路为1.3.1;使用晶体管、运放放大器等辅助器件的电路为1.3.2。

图中列出了2个常用电路。

图2-3单稳型压控振荡电路四.系统总图图2-4 总体电路图波形发生器一、设计题目波形发生器的设计与制作二.主要技术指标输出频率为160Hz的正弦波、方波、三角波。

正弦波幅度10V;方波幅度6V;三角波幅度为4V。

三.方案论证及选择:正弦波:方案一、由R、C振荡电路产生,其中包括R、C串并联电路和R、C移相电路两种。

方案二、由L、C振荡电路产生。

方案三、由集成运放构成的RC桥式振荡电路产生。

包括放大、反馈、选频和稳幅等基本部分。

输出波形稳定性良好。

方波:方案一、方波可由NE555构成多谐振荡器来产生。

方案二、由运放构成的电压比较器,在运放的输出端引入限流电阻和两个背靠背的稳压管组成双向限幅方波产生电路。

三角波:方案一、由方波来产生:可以由NE555电路产生的方波或是集成运放产生的通过R、C积分来得到。

方案二、由同相输入迟滞比较器和积分器产生方案选择:通过对以上方案进行比较,我们选择的方案是:正弦波是由集成运放构成的RC 桥式振荡电路产生。

摘要脉冲序列检测器广泛应用于现代数字通信系统中,随着通信技术的发展,对多路脉冲序列信号检测要求越来越高。

现代通信系统的发展方向是功能更强、体积更小、速度更快、功耗更低,大规模可编程逻辑器件FPGA器件的集成度高、工作速度快、编程方便、价格较低,易于实现设备的可编程设计,这些优势正好满足通信系统的这些要求。

随着器件复杂程度的提高,电路逻辑图变得过于复杂,不便于设计。

VHDL(VHSIC Hardware Description Language)是随着可编程逻辑器件的发展而发展起来的一种硬件描述语言。

VHDL具有极强的描述能力,能支持系统行为级、寄存器输级和门级三个不同层次的设计,实现了逻辑设计师多年来梦寐以求的“硬件设计软件化”的愿望,给当今电子通信系统设计带来了革命性的变化。

本文针对传统的脉冲序列检测器方案,提出了一种基于对脉冲序列检测器设计的新方案,该方案相对于传统的设计方法更适合于现代数字通信系统,不但大大减少了周边的设备,也使系统设计更加灵活,稳定性更好,性价比更高,可以满足多种环境下的检测系统的要求。

关键词:多路数据选择器、Multisim、计数器、序列检测器目录摘要 (1)1目录 (1)2.设计内容及设计要求 (2)3.1 实验目的 (3)3.2参考电路 (4)3.3实验内容及主电路图 (5)3.4多谐振荡器的介绍 (6)3.5计数器的介绍 (9)3.6数据分析 (12)3.7数据选择器的介绍 (14)4实验结果 (16)4.1实验结果的分析 (17)设计总结 (18)致谢 (19)参考文献 (20)2设计内容及技术要求1、设计并制作一个脉冲序列发生器,周期性的产生8位长度的任意脉冲序列,脉冲序列可以通过设置电路自由设置。

2、能够检测出设置的脉冲序列,在每出现一次设置的脉冲序列时,点亮一次LED;3、时钟脉冲周期为1HZ;4、对设置的脉冲序列值通过适当的方式进行指示;5、电源:220V/50HZ的工频交流电供电;6、(直流电源部分仅完成设计仅可,不需制作,用实验室提供的稳压电源调试,但要求设计的直流电源能够满足电路要求)7、按照以上要求设计电路,绘制电路图,对设计的的电路用Multisim或OrCAD/PspiceAD9进行仿真,用万用板焊接元器件,制作电路,完成调试、测试,撰写设计报告。

虞立工(杭州华日电冰箱股份有限公司 杭州 310019)摘要:介绍了以MCS-51单片机为主控器,以MCP4561数字电位器为核心实现可调数字式脉 冲发生电路的设计。

该系统电路简单、可靠,脉冲信号频率、脉宽和幅值可调,输出波形平稳。

关键词:MCS-51单片机; 脉冲发生器; 数字电位器Abstract :In this paper, it introduces the design of a controllable digital pulse generator circuit which is based on MCS-51 single chip microcomputer as the main controller and MCP4561 digital potentiometer as the core. The result shows that it is of simplicity and reliability, and pulse frequency, pulse width and signal amplitude can be adjusted and the output waveform is smooth.Key words:MCS-51 single chip microcomputer; pulse generator; digital potentiometer引言脉冲信号发生器在工业应用、生物医学、家用电器控制等领域中,有着广泛的应用。

在控制步进电机运行 过程中,脉冲发生器可以发出脉冲信号,按照步进电机的结构特点,顺序分配脉冲,实现控制角位移、旋转速度、旋转方向。

大部分的脉冲信号发生器是利用定时电路产生脉冲,而频率和幅值都是用电位器进行调节。

而机械接触式的电位器可靠性和精度不高,而用单片机在软件方面实现数字可调又会耗费很多编程人员的很多时间和精力。

本文介绍采用Microchip 公司的MCP4561数字电位器,来代替机械接触式的电位器,用MCS-51单片机控制,实现输出脉冲信号的脉宽、频率和幅值可调。

毕业设计论文可编程脉冲信号发生器的设计摘要基于单片机的可编程脉冲信号发生器,通过4x4的非编码矩阵键盘键入脉冲信号的指标参数频率、占空比和脉冲个数,在单片机的控制处理下发出满足信号指标的脉冲信号,并在液晶显示屏的制定位置显示出相关参数。

复位电路采用上电复位和手动复位的复合复位方式,保证单片机在上电和程序运行进入死循环时,单片机均能正常复位。

利用在工作方式1下的定时器和计数输出低频脉冲信号,以及在工作方式2下能够自动重复赋初值的定时器输出高频脉冲信号,从而使频率和占空比满足指标要求。

通过程序设计,使单片机每次发出信号后等到重置信号进行下一次脉冲信号的输出,有效的提高了单片机的使用效率。

本课题设计利用单片机技术,通过相应的软件编程和较简易的外围硬件电路来实现,其产生的脉冲信号干扰小,输出稳定,可靠性高,人机界面友好,操作简单方便,成本低,携带方便,扩展性强。

关键的是,脉冲信号频率、脉冲个数和脉冲占空比可调节,可通过键盘输入并由显示器显示出来。

本课题设计所要达到的指标要求:(1)脉冲信号频率0.1HZ到50KHZ可调并在液晶显示屏指定位置显示。

(2)脉冲信号个数0到9999可调并在液晶显示屏指定位置显示。

(3)脉冲信号占空比任意可调并在液晶屏显屏指定位置示出来。

关键词:单片机,脉冲信号,频率,脉冲个数,占空比Programmable pulse signal generator designABSTRACTThe programmable pulse signal generator based on single chip, through the 4x4 non-coding matrix keyboard inputing pulse signal parameters of frequency, duty cycle and pulse number, pulse signal is sent to meet the targets of signal processing chip.The related parameters are displayed on the setting position on the liquid crystal. The reset circuit by power-on reset and manual reset, ensure the SCM in power and run into dead circulation can be reset. Use in work mode 1 timer and counter output low frequency pulse signal, and in work mode 2 to timer output high frequency pulse signal ,automaticly repeat initialization, so as to make the frequency and duty ratio meet the requirements. Through the program design, the microcontroller each signal and then wait for the reset signal, the signal at the output of the pulse next time, effectively improve the efficiency in the use of single-chip microcomputer.The subject of the use of single-chip technology, which achieved through the corresponding software and the simple peripheral hardware circuit. The advantages of which are the small interference of the pulse signal, output stability, high reliability, friendly man-machine interface, easy operation, low cost, portability, scalability strong. The keys, pulse frequency, pulse number and pulse duty ratio are adjustable, which can be inputed through the keyboard and displayed through LCD.The requirements of this topic design:(1) The pulse signal frequency of 0.1HZ to 50KHZ is adjustable and can be displaied on the specify location in the LCD screen.(2) Pulse signal number of 0 to 9999 is adjusted and can be displaied on the specify location in the LCD screen.(3)Pulse duty ratio is adjustable and can be displaied on the specify location in the LCD screen.KEY WORDS: single chip computer,pulse,hardware circuit,pulse number,duty ratio目录前言 (1)第1章可编程脉冲发生器的相关模块 (4)1.1 AT89C51单片机 (4)1.1.1 AT89C51单片机的结构 (4)1.1.2 AT89C51单片机的引脚功能 (5)1.1.3 AT89C51单片机的中断系统 (9)1.1.4 AT89C51单片机的定时/计数器 (11)1.2 SMC 1602A LCD液晶显示屏 (12)第2章可编程脉冲信号发生器的硬件设计 (14)2.1 硬件系统的总体设计 (14)2.1.1 系统的总体框图 (14)2.1.2 原理阐述 (14)2.2 硬件系统各部分构成 (14)2.2.1电源电路 (14)2.2.2矩阵键盘 (15)2.2.3脉冲信号输出电路 (16)2.3系统电路原理图 (19)第3章可编程脉冲信号发生器的软件设计 (20)3.1矩阵键盘的程序设计 (20)3.2液晶屏显示的程序设计 (21)3.3脉冲生成的程序设计 (23)3.3程序流程图 (24)3.3.1主程序流程图 (24)3.3.2键盘分析子程序流程图 (25)3.3.3显示子程序流程图 (26)3.3.3数值处理子程序流程图 (27)3.3.3脉冲信号生成子程序流程图 (28)3.3.4源程序 (28)第4章可编程脉冲信号发生器的程序编译、调试及仿真 (29)4.1系统程序的编译 (29)4.2系统调试 (30)4.2.1硬件调试 (30)4.2.2软件调试 (30)4.3系统仿真 (32)4.3.1系统仿真图 (32)4.3.2系统的改善 (35)结论 (36)谢辞 (37)参考文献 (38)附录 (40)外文资料翻译 (1)前言信号发生器是一种能产生标准信号的电子仪器,是工业生产和电工、电子实验中经常使用的电子仪器之一。

可调脉冲设计与分析摘要我们知道,555电路在应用和工作方式上一般可归纳为3类。

每类工作方式又有很多个不同的电路。

在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如:多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。

这样一来,电路变的更加复杂。

为了便于我们分析和识别电路,更好的理解555电路,这里我们这里按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。

每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。

555时基电路是一种将模拟功能与逻辑功能巧妙地结合在同一硅片上的组合集成电路。

该电路可以在最基本的典型应用方式的基础上,根据实际需要,经过参数配置和电路的重新组合,与外接少量的阻容元件就能构成不同的电路,因而555电路在波形的产生与变换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。

关键字:NE555目录第一章可调脉冲发生器设计与分析简介 (3)1.1可调脉冲发生器设计与分析绪论 (3)第二章可调脉冲发生器设计与分析设计与分析 (4)2.1方案与论证 (4)2.2总体框图及模块设计 (5)2.3总体电路设计 (7)2.4系统测试,抗干扰及注意细节 (9)第三章可调脉冲发生器设计与分析结果分析论证 (9)3.1硬件调试 (9)3.2结果分析得出结论 (10)参考文献 (11)第一章可调脉冲发生器设计与分析简介555 芯片是定时器,是一种模拟和数字功能相结合的中规模集成器件。

一般用双极性工艺制作的称为555,用CMOS 工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。

555 定时器的电源电压范围宽,可在4.5V~16V 工作,7555 可在3~18V 工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS 或者模拟电路电平兼容1.1可调脉冲发生器设计与分析绪论ne555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。

可控脉冲发生器的设计

一、 实验目的

1、 了解可控脉冲发生器的实现机理。

2、 学会用示波器观察FPGA 产生的信号。

3、 学习用VHDL 编写复杂功能的代码。

二、 实验原理

脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个

M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件

时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:

三、 实验内容

编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

四、 实验程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity exp10 is

port( Clk : in std_logic; --时钟输入

Rst : in std_logic; --复位输入

⎩⎨⎧≤≤<≤=N T M M T Q 001%1001

)1(⨯+=+=N M T N CLOCK

占空比周期

NU,ND : in std_logic; --输入:控制频率的改变

MU,MD : in std_logic; --输入:控制占空比的改变

Fout : out std_logic --波形输出

);

end exp10;

architecture behave of exp10 is

signal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);

signal N_Count :std_logic_vector(10 downto 0);

signal clkin : std_logic;

signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断begin

process(Clk) --计数器累加

begin

if(Clk'event and Clk='1') then

if(N_Count=N_Buffer) then

N_Count<="00000000000";

else

N_Count<=N_Count+1;

end if;

end if;

end process;

process(Clk) --波形判断

begin

if(Clk'event and Clk='1') then

if(N_Count<M_Buffer) then

Fout<='1';

elsif(N_Count>M_Buffer and N_Count<N_Buffer) then

Fout<='0';

end if;

end if;

end process;

process(Clk)

begin

if(Clk'event and Clk='1') then

Clk_Count<=Clk_Count+1;

end if;

clkin<=Clk_Count(12);

end process;

process(clkin) --频率及占空比的改变1

begin

if(clkin'event and clkin='0') then

if(Rst='0') then

M_Buffer<="010********";

N_Buffer<="10000000000";

elsif(NU='0') then

N_Buffer<=N_Buffer+1;

elsif(ND='0') then

N_Buffer<=N_Buffer-1;

elsif(MU='0') then

M_Buffer<=M_Buffer+1;

elsif(MD='0') then

M_Buffer<=M_Buffer-1;

end if;

end if;

end process;

end behave;

五、时序仿真图。