MC9S12_增强型捕捉定时器模块

- 格式:pdf

- 大小:796.85 KB

- 文档页数:46

手把手教你写S12XS128程序(17)--Timer模块介绍11、简述MC9S12XS128定时器模块与MC9S12DG128 ECT部分功能完全类似,以下均以ECT模块介绍xs128定时器模块。

HC12 增强型捕捉计时器模块在HCS12标准定时器的基础上增加了一些特点,用以扩展它的应用范围,特别是在汽车ABS 方面。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

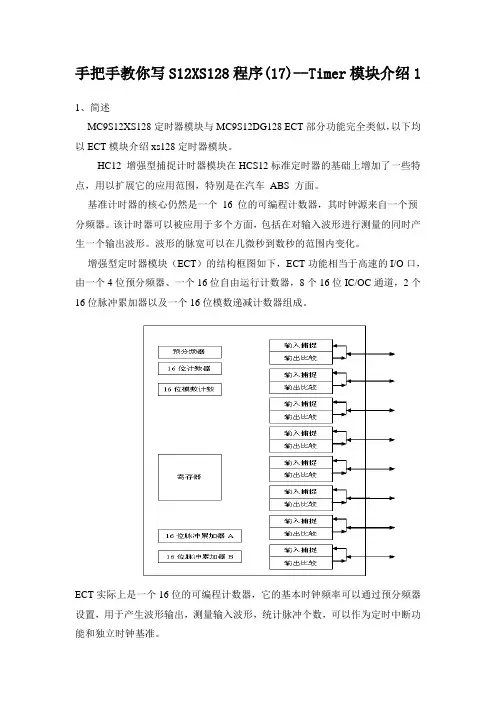

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到T SCR($06)的T SFRZ 位被置1。

把手教你写S12XS128程序(18)--Timer模块介绍2IC 通道组IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC /OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。

非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。

当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

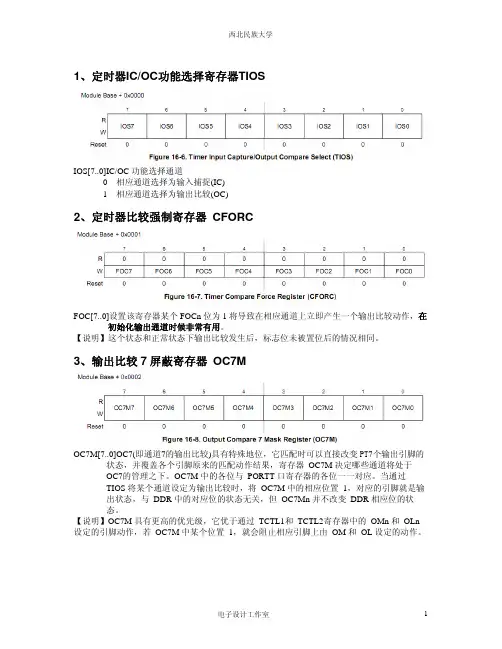

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

S12(X)单片机BDM调试器使用技巧第五届全国大学生“飞思卡尔”杯智能气车竞赛限制采用最新的MC9S12XS128(以下简称XS128)单片机作为主控芯片,替代MC9S12DG128。

XS128是Freescale公司推出的S12系列单片机中的一款增强型16位单片机。

片内资源丰富,接口模块有SPI、SCI、IIC、A/D、PWM等常见模块,在汽车电子应用领域具有广泛用途。

XS128和以往大赛使用的S12DG128系列单片机一样,调试接口都是使用Freescale公司传统的BD M(Background Debug Module)接口。

1 MC9S12XS128单片机介绍(1)CPU:增强型16位HCS12 CPU,片内总线时钟最高40 MHz;(2)片内资源:8 KB RAM、128 KB程序闪存、2 KB数据闪存;(3)串行接口模块:SCI、SPI;(4)脉宽调制模块(PWM)可设置成4路8位或者2路16位,逻辑时钟选择频率宽;(5)1个16路12位精度A/D转换器;(6)控制器局域网模块(CAN);(7)增强型捕捉定时器。

MC9S12XS128单片机有112、80和64引脚3种封装形式。

80-pin封装的单片机没有引出用于扩展方式的端口,仅引出了一个8路A/D接口。

竞赛可使用112或80引脚封装器件。

2 BDM接口和使用BDM调试器内部有一个8位的MC9HC08JB16单片机,该单片机有USB接口,可与PC 机信息交互。

HC08单片机和S12单片机间仅使用一根 I/O线通信,这根相连的信号线名为BKGD。

HC08单片机将BKGD置为输出,以串行发送命令,发送完成后转为输入,以接收信息。

S12单片机收到命令后转为输出,根据调试器发来的命令回送信息,然后立即转入接收态。

BDM工具以此方式实现S12单片机的在线调试、内部闪存的烧写等功能。

关于BDM接口的实现,读者可以参考Freescale任何一款S12单片机的器件手册,其对BDM接口的命令字、交互模式等都有详细描述。

PWM工作原理S12微控制器PWM模块是由独立运行的8位脉冲计数器PWMCNT和两个比较寄存器PWMPER和PWMDTY组成。

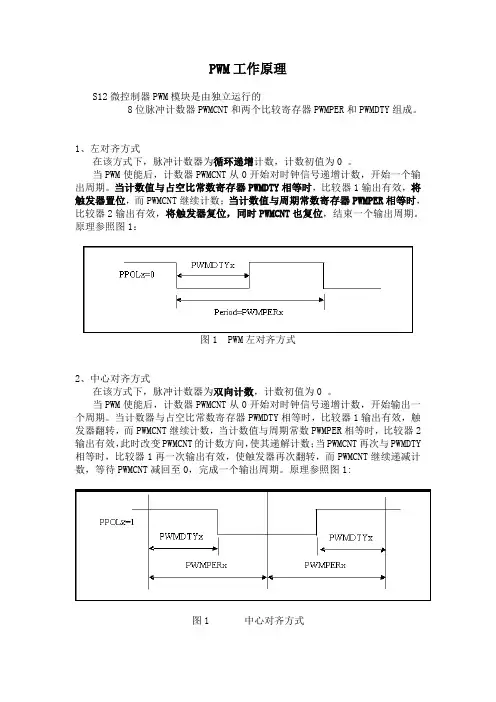

1、左对齐方式在该方式下,脉冲计数器为循环递增计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始一个输出周期。

当计数值与占空比常数寄存器PWMDTY相等时,比较器1输出有效,将触发器置位,而PWMCNT继续计数;当计数值与周期常数寄存器PWMPER相等时,比较器2输出有效,将触发器复位,同时PWMCNT也复位,结束一个输出周期。

原理参照图1:图1 PWM左对齐方式2、中心对齐方式在该方式下,脉冲计数器为双向计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始输出一个周期。

当计数器与占空比常数寄存器PWMDTY相等时,比较器1输出有效,触发器翻转,而PWMCNT继续计数,当计数值与周期常数PWMPER相等时,比较器2输出有效,此时改变PWMCNT的计数方向,使其递解计数;当PWMCNT再次与PWMDTY 相等时,比较器1再一次输出有效,使触发器再次翻转,而PWMCNT继续递减计数,等待PWMCNT减回至0,完成一个输出周期。

原理参照图1:图1 中心对齐方式3、周期计算方法左对齐方式:输出周期 = 通道周期× PWMPERx中心对齐方式:输出周期 = 通道周期× PWMPERx × 24、脉宽计算方法左对齐方式:占空比 = [ (PWMPERx - PWMDTYx) / PWMPERx ] × 100%中心对齐方式:占空比 = [ PWMDTYx / PWMPERx ] × 100%S12XS128 【例程】程序描述:由通道PTP3口输出频率为1K,占空比为50%的方波程序如下:#include <hidef.h> /* common defines and macros */#include <mc9s12dg128.h> /* derivative information */#pragma LINK_INFO DERIVATIVE "mc9s12dg128b"/***********初始化函数*************//*时钟初始化程序*/void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1){ //锁相环时钟=2*16*(2+1)/(1+1)=48MHzREFDV=1; //总线时钟=48/2=24MHzSYNR=2;while(!(CRGFLG&0x08));CLKSEL=0x80; //选定锁相环时钟}/*PWM初始化程序*/void PWM_Init(void){PWME_PWME3=0x00; // Disable PWM 禁止PWMPRCLK=0x33; // 0011 0011 A=B=24M/8=3M 时钟预分频寄存器设置 PWMSCLA=150; // SA=A/2/150=10k 时钟设置PWMSCLB=15; // SB=B/2/15 =100k 时钟设置PWMCLK_PCLK3=1; // PWM3-----SB 时钟源的选择PWMPOL_PPOL3=1; // Duty=High Time 极性设置PWMCAE_CAE3=0; // Left-aligned 对齐方式设置PWMCTL=0x00; // no concatenation 控制寄存器设置PWMPER3=100; // Frequency=SB/100=1K 周期寄存器设置PWMDTY3=50; // Duty cycle = 50% 占空比寄存器设置PWME_PWME3=1; // Enable PWM 使能}/**********主函数**************/void main(void){PLL_Init();PWM_Init();/* put your own code here */EnableInterrupts;for(;;) {} /* wait forever *//* please make sure that you never leave this function */}增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,八个16位IC/OC通道,二个16位脉冲累加器以及一个16位模数递减计数器组成。

MC9S12XS简介MC9S12XS简介1.1 S12XS介绍新16位微控制器S12XS的系列是一个兼容,减少版本的S12XE系列。

这个系列提供了一种简便的方法开发从低端到高端化应用程序的通用平台,减少硬件和软件的设计。

12XS系列提供32位的所有优势和效率性能的16位MCU,同时保持低成本,低功耗,EMC和代码大小目前享有的效率优势。

S12XS 系列运行在等待状态的情况下为所有外围设备和存储器16位宽访问。

该S12XS系列有112引脚LQFP封装,80引脚QFP,64引脚LQFP封装选择,与S12XE系列高度兼容。

除了在每个模块提供I / O 端口外,还有多达18个具有从停止或等待模式被唤醒的中断功能的I / O端口。

外围设备包括MSCAN,SPI,两个SCIs,一个8通道24位定时器周期中断,8 -通道16位定时器,8通道PWM,高达16 通道12位AD转换器。

1.1.1特性16位CPU12XS-向上兼容S12指令集,除了删除五个模糊指令(MEM,WAV ,WAVR,REV,REVW)-增强索引寻址-获取大量数据段独立PPAGEINT(中断模块)- 7个级别的嵌套中断-灵活的分配中断源到每个中断的层次。

-外部非屏蔽高优先级中断(XIRQ)-下面的输入可以作为唤醒中断- IRQ和非屏蔽XIRQ-CAN总线接收引脚-SCI接收引脚-根据不同的封装选择了20针在端口J,H和P的上升或下降沿敏感的配置MMC管理(模块映射控制)DBG(调试模块)-监测与标签的CPU总线型或力量型断点要求- 64 × 64位循环跟踪缓冲区的捕捉改变流或内存访问信息BDM(背景调试模式)OSC_LCP(振荡器)-低功率的闭环控制皮尔斯振荡器利用一个4MHz至16MHz石英晶体振荡器-良好的抗干扰-全摆幅皮尔斯选择利用一个2MHz至40MHz的晶振-根据跨导最佳启动的边缘典型晶体IPLL(内部过滤,调频锁相回路时钟发生器)-无需外部元件-可配置选项为减少传播EMC辐射(频率调制谱)CRG(时钟和复位产生)-看门狗-实时中断-时钟监视器-快速唤醒自我的停止时钟模式内存选项-64K,128K的和256K字节的闪存-闪存的基本特征- 64位数据加上8位并发ECC(纠错码),允许单个位失败校正和双故障检测-擦除扇区大小1024字节-自动编程和擦除算法-保护计划,以防止意外编程或擦除-安全选项,以防止未经授权的访问- 4K和8K字节数据闪存空间- 16位数据加上6位并发ECC(纠错码),允许单个位失败校正和双故障检测-擦除扇区大小256字节-自动编程和擦除算法- 4K,8K与第12K字节RAM16通道,12位模拟数字转换器- 8/10/12位分辨率- 3微秒,10位单次转换时间-左或右对齐结果数据-外部和内部转换触发功能-内部振荡器在停止模式转换-唤醒从模拟比较低功耗模式-连续转换模式- 16路模拟输入通道-多通道扫描-管脚也可以作为数字I / OMSCAN(1Mbit/s,CAN2.0的A,B软件兼容模块)- 1兆位每秒,CAN2.0的A,B软件兼容模块-标准和扩展数据帧- 0 - 8个字节数据的长度-可编程的比特率高达1 Mbps-五接收FIFO的存储方案缓冲区-三优先发送内部缓冲区-灵活的标识验收滤波器可编程为:- 2 x 32位- 4 x 16位- 8 × 8位-唤醒集成了低通滤波器的选择-环回自检-只能收听到CAN总线监控-16位发送/接收信息时间戳TIM(标准定时器模块)- 8 × 16的输入捕捉或输出比特的通道比较- 16位自由运行计数器的8位精度预分频器- 1个16位脉冲累加器PIT(周期性中断定时器)-多达4个独立的定时器超时周期-超时期限为1至224总线时钟周期选择-超时中断和周边触发器-定时器开始可以对齐高达8通道× 8位或4通道x 16位脉宽调制器-每通道占空比和周期都是可编程的-中心或左对齐输出-可编程时钟选择逻辑的和频率范围串行外设接口模块(SPI)-可设置为8位或16位数据的大小-全双工或单线双向-双缓冲的发送和接收-主或从模式-最高位先或LSB先移-串行时钟相位和极性选择两个串行通信接口(SCI)-全双工或单线运行-标准标记/空间不返回到归零(NRZ)格式-可选的IrDA 1.4返回到零反转(RZI)可编程脉冲宽度格式- 13位波特率选择-可编程的字符长度-可编程极性的发射机和接收机-接收唤醒的积极边缘-间隔检测和传输冲突检测支持片上电压调节器-两个平行的,与带隙基准的线性稳压器-低电压检测(LVD)认证的低电压中断(LVI)号-上电复位(POR)电路-低电压复位(LVR)的低功耗唤醒定时器(API)的-内部振荡器驾驶递减计数器-微调到+ / -10%的准确度-超时时间为0.2ms的范围内,从同一个0.2ms?13秒的决议输入/输出-最多91个通用输入/输出(I / O)引脚取决于封装选择和2个输入专用管脚-磁滞和可配置上拉/下拉输入引脚上的所有设备-在所有输出引脚可配置驱动力量封装选择- 112引脚小外形四方扁平封装(LQFP封装)- 80引脚四方扁平封装(QFP)- 64引脚小外形四方扁平封装(LQFP封装)操作条件-宽单电源电压范围3.135 V至5.5 V的全性能-单独的电源内部电压调节器和I / O优化的EMC滤波容许- 40MHz的最大CPU总线频率-环境温度范围:-40°C至125°C-温度选项:- -40°C至85°C- -40°C至105°C- -40°C至125°C1.1.2 工作模式模式种类:正常的单芯片模式特别的单主动背景调试模式芯片模式1.1.3 信号的详细说明1.1.3.1 EXTAL,XTAL - 振荡器引脚EXTAL和XTAL是晶体驱动和外部时钟引脚。

mc9s12xe系列单片机参考手册--中文1.3系统时钟介绍时钟和复位发生器模块(CRG)提供的核心和外设模块的所有内部时钟信号。

图1-8显示了从CRG所有模块的时钟连接。

在clock generation中查询CRG时钟产生的细节规范。

系统时钟可以提供多种方式,使系统的工作频率范围要支持:•片上锁相环(PLL)•锁相环自我时钟•振荡器由PLL或振荡器产生的时钟提供主系统时钟频率,核心时钟和总线时钟。

如图1-8所示,这些系统时钟用于驱动整个MCU的core,RAM,和外设。

闪存程序存储器和EEPROM可由总线时钟和振荡器时钟提供时钟信号。

“使用振荡器时钟作为时基,驱动程序,并提供NVM的擦除时间基准。

CAN模块可配置的时钟源来自总线时钟或直接从振荡器时钟。

这允许用户在提供的两种时钟信号的基础上,选择它的时钟性能。

为了确保时钟的存在,MCU包括一个片上时钟监视器,监视器连接到振荡器的输出。

时钟监视器可以被配置为调用PLL自震荡模式或在超过一定时间没有振荡器时钟出现,产生一次系统复位。

除了时钟监视器,MCU还提供了时钟质量检查模块执行时钟准确的检查。

时钟质量检查计数器在一个定义的时间窗口内检查预先设定了的时钟边沿,以确保时钟的正确运行。

检查程序可以被以下具体的事件调用,如唤醒或时钟监视器故障。

MCU可以处在不同的模式,而这与MCU资源的映射和总线接口配置操作相关。

这些内容将在1.4.1芯片配置摘要有提到。

MCU可以有不同的电源操作模式,当并不需要系统满负荷运行时,方便省电的模式是可选的。

这些内容将在1.4.2功率模式有提到。

1.4操作模式有些功能模块是可编程的,可以对某个模块进行冻结,而BGD模块的处于活动对于方便调试是有积极意义的,这在1.4.3冻结模式有提到。

对于系统的完整性,支持独立的系统状态功能,在1.4.4系统状态的说明有提到。

MCU有六个不同的模式而模式与系统资源配置相关。

不同的模式,ROMCTL与 EROMCTL在RESET信号的上升沿的状态,MCU的安全状态都会影响以下设备的特点:•外部总线接口配置•可能会影响Flash中的存储器映射,或不会•调试功能启用或禁用操作模式是由MODC,MODB和MODA在复位时的信号状态决定的。

MC9S12系列器件说明(电气特性)一.MC9S12系列的名称定义(以MC9S12DJ64CFU为例):MC9S12:Controller Family 该控制器系列统称9:代表FLASHS12:内核型号DJ64:Device Title 器件名称64:64K的FLASHC:Temperature Options 温度选择FU:Package Option 封装结构选择温度选择表定义(Temperature Option):C = -40°C to 85°CV = -40°C to 105°CM = -40°C to 125°C封装结构选择定义(Package Options)FU = 80QFPPV = 112LQFP二.MC9S12DJ64特征:·HCS12 核心:16-bit HCS12 CPUMEBI多路复用外部总线接口 (Multiplexed External Bus Interface)MMC模块映射控制 (Module Mapping Control)INT中断控制 (Interrupt control)BKP 断点(Breakpoints)BDM 后台调试模式(Background Debug Mode)·CRG 时钟和复位发生器(low current Colpitts or Pierce oscillator, PLL, reset, clocks, COP watchdog, real time interrupt, clock monitor)·8位和4位的带中断功能的接口:-数字滤波-可编程边缘触发(上升沿/下降沿)·存储器:-64K Flash EEPROM-1K byte EEPROM-4K byte RAM·2个八通道的数字/模拟转换器:-精度达到10bit-外部转换触发功能·1M bit/每秒,CAN2.0 A,B软件兼容模块:-5个接受和3个发送缓冲单元-4个独立的中断通道,分别对应Rx, Tx, error 和 wake-up-低通滤波器唤醒功能-自测工作回送功能(Loop-back for self test operation)·增强型捕捉定时器功能(Enhanced Capture Timer)-16位主计数器(带7位预分频率器)-8个可编程输入捕捉通道/输出比较通道-4个8位/2个16位脉冲累加器(pulse accumulator)·8个PWM通道:-周期和占空比系数可编程控制-八个8位通道/四个16位通道-独立的单个脉冲宽度和占空比控制-向中心对齐和向左对齐输出-频率范围很广的可编程时钟选择逻辑单元-快速紧急关闭输入-可作为中断输入·串行接口:-2个异步SCI(Serial Communications Interfaces)-同步SPI(Serial Peripheral Interface)·Byte Data Link Controller(BDLC):·Inter-IC Bus (IIC):-兼容CI2总线标准-多主机工作模式(Multi-master operation)-软件可编程256个不同的串行时钟频率·112引脚封装/80引脚封装-带驱动能力的5VI/O线路-5V A/D转换-50MHz工作频率,相当于25MHz总线速度-支持开发应用-单线程后台调试模块Obackground debug TM mode (BDM) -片上硬件断点调试(On-chip hardware breakpoints)三.模块框图:四.MC9S12DJ64引脚图:MC9S12DJ64有112LQFP(low profile quad flat pack)和80QFP(quad flat pack)两种封装结构。

>手把手教你写S12XS128程序(17)--Timer模块介绍1时间:2009-12-29 11:51来源:电子设计吧作者:dzsj8 点击:380次1、简述MC9S12XS128定时器模块与MC9S12DG128 ECT部分功能完全类似,以下均以ECT模块介绍xs128定时器模块。

HC12 增强型捕捉计时器模块在HCS12标准定时器的基础上增加了一些特点,用以扩展它的应用范围,特别是在汽车ABS 方面。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到T SCR($06)的T SFRZ 位被置1。

等待:计数器保持运行,直到T SCR($06)的T SWAI 位被置1。

正常:计时器和计数器均保持运行,直到T SCR($06)的T EN 位和M CCTL($26)的MCEN 位被分别清0。

手把手教你写S12XS128程序(18)--Timer模块介绍2时间:2009-12-30 22:12来源:电子设计吧作者:dzsj8 点击:366次IC 通道组IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC/OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。