简述8251a的编程结构

- 格式:doc

- 大小:13.03 KB

- 文档页数:3

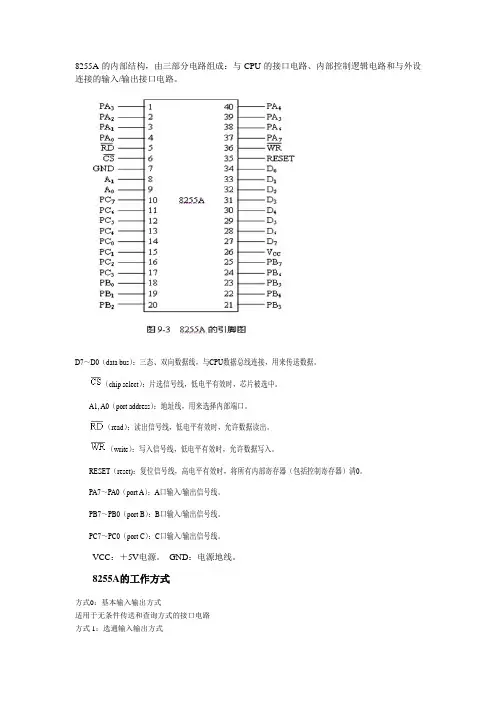

8255A的内部结构,由三部分电路组成:与CPU的接口电路、内部控制逻辑电路和与外设连接的输入/输出接口电路。

D7~D0(data bus):三态、双向数据线,与CPU数据总线连接,用来传送数据。

(chip select):片选信号线,低电平有效时,芯片被选中。

A1, A0(port address):地址线,用来选择内部端口。

(read):读出信号线,低电平有效时,允许数据读出。

(write):写入信号线,低电平有效时,允许数据写入。

RESET(reset):复位信号线,高电平有效时,将所有内部寄存器(包括控制寄存器)清0。

PA7~PA0(port A):A口输入/输出信号线。

PB7~PB0(port B):B口输入/输出信号线。

PC7~PC0(port C):C口输入/输出信号线。

VCC:+5V电源。

GND:电源地线。

8255A的工作方式方式0:基本输入输出方式适用于无条件传送和查询方式的接口电路方式1:选通输入输出方式适用于查询和中断方式的接口电路方式2:双向选通传送方式适用于与双向传送数据的外设适用于查询和中断方式的接口电路8255A初始化编程8255A的A,B,C三个端口的工作方式是在初始化编程时,通过向8255A的控制端口写入控制字来设定的。

8255A由编程写入的控制字有两个:方式控制字和置位/复位控制字。

方式控制字用于设置端口A, B, C的工作方式和数据传送方向;置位/复位控制字用于设置C口的PC7~PC0中某一条口线PC i(i=0~7)的电平。

两个控制字公用一个端口地址,由控制字的最高位作为区分这两个控制字的标志位。

(1)方式控制字的格式8255A工作方式控制字的格式如图7.11所示。

D0:设置PC3~PC0的数据传送方向。

D0=1为输入;D0=0为输出。

D1:设置B口的数据传送方向。

D1=1为输入;D1=0为输出.D2:设置B口的工作方式。

D2=1为方式1;D2=0为方式0。

可编程串行通信接口芯片8251A可编程串行通信接口芯片8251A2010-05-25 15:058251 A是一个通用串行输入/输出接口,可用来将86系列CPU以同步或异步方式与外部设备进行串行通信。

它能将主机以并行方式输入的8位数据变换成逐位输出的串行信号;也能将串行输入数据变换成并行数据传送给处理机。

由于由接口芯片硬件完成串行通信的基本过程,从而大大减轻了CPU的负担,被广泛应用于长距离通信系统及计算机网络。

8251A是一个功能很强的全双工可编程串行通信接口,具有独立的双缓冲结构的接收和发送器,通过编程可以选择同步方式或者异步方式。

在同步方式下,既可以设定为内同步方式也可以设定为外同步方式,并可以在内同步方式时自动插入一个到两个同步字符。

传送字符的数据位可以定义为5~8位,波特率0~64K可选择。

在异步方式下,可以自动产生起始和停止位,并可以编程选择传送字符为5~8位之间的数据位以及1、1/2位之中的停止位,波特率0~19.2K可选择。

同步和异步方式都具有对奇偶错、覆盖错以及帧错误的检测能力。

一、8251A内部结构及功能图8.5.1为8251A结构框图。

作为常用的通信接口,和8255A类似,8251A 的结构也可以归纳为以下三个部分:第一部分是和CPU或者总线的接口部分,其中包括数据总线缓冲器、读/写控制逻辑。

数据总线缓冲器用来把8251A和系统数据总线相连,在CPU执行输入/输出指令期间,由数据总线缓冲器发送和接收数据,此外,控制字,命令字和状态信息也通过数据总线缓冲器传输,读/写控制逻辑电路用来配合数据总线缓冲器工作。

CPU通过数据总线缓冲器和读写控制逻辑向8251A写入工作方式和控制命令字,对芯片初始化;向8251A写入要发送字符的数据代码,送到发送缓冲器进行并行到串行的转换,并且将接收的、已转换成并行代码的接收缓冲器中的字符数据读入CPU。

第二部分是数据格式转换部分,包括发送缓冲器、并行数据到串行数据转换的发送移位器,接收缓冲器和串行数据到并行数据转换的接收移位器,以及发送控制电路和接收控制电路。

可编程通信接口8251A(USART)1.8251A的基本结构8251A的基本结构包括5个功能模块(1)数据总线缓冲器——用于暂存接收,发送数据,CPU发来的命令及8251的工作状态。

(2)读/写控制逻辑——接收来自CPU控制总线的控制信号,控制数据的传送方向。

(3)接收器——从接收数据线RXD上接收串行数据,按指定方式将其转换成并行数据。

(4)发送器——接收CPU送来的并行数据,按指定方式将其转换成串行数据通过发送数据线TXD发送出去。

(5)调制解调器控制电路——提供4个通用的控制信号,即(数据终端准备好),(数据设备准备好),(请求发送)和(准许发送),以备8251A与外设联络。

2.8251A的工作过程(1)8251A发送数据的过程①当发送缓冲器为空时,信号TXRDY有效(或状态字的D0=1),以示发送器准备好,等待CPU送入数据。

②CPU将要发送的数据写入8251A的发送缓冲器;③发送的数据进行“并→串”转换;④插入起始位、奇/偶位和停止位或同步字符等,数据一位一位从TXD端串行输出。

(2)8251A接收数据的过程①在RXD端检测到起始位或同步字符;②开始在RXD线上采集数据;③将接收到的数据“串→并”转换,并进行奇偶校验和检查错误;④将采样到的、经过变换的8位数据由接收缓冲器送入数据总线缓冲器;⑤信号RXRDY有效(或状态字的D1=1),以示8251A已接收到一个数据,待CPU读取。

3.8251A的初始化在如前面已经强调过的,在使用可编程接口之前必须进行初始化,即在使用8251A进行数据传输前,对其进行编程,将相关方式指令字、命令指令字写入8251A。

8251A初始化的具体步骤如图7-3所示。

图7-3 8251A 初始化流程图4. CPU 对8251A 的操作和控制8251A 有两个端口地址,偶地址为输入/输出数据端口地址,奇地址为控制/状态端口地址。

引脚线C/与A 0连接:A 0=0,访问输入/输出数据端口A 0=1,访问控制/状态端口控制信号:、、C/、合成对8251A 的操作如表7-1所示。

串行接口芯片8251A8251A基本功能⏹可用于同步和异步通信方式(通信方式通过对方式字编程实现):☐同步方式:波特率0-64Kbps,每个字符可为5~8位,可使用内部同步检测和外部同步检测,能自动插入同步字符。

☐异步方式:波特率0-19.2Kbps,每个字符可为5~8位,自动增加起始位、停止位和校验位。

时钟TxC,RxC的时钟频率为传输波特率的1,16和64倍。

⏹全双工,具有双缓冲器接收器和发送器;⏹出错检测,具有奇偶、溢出和帧错等检测电路。

8251A的内部结构8251A的内部结构主要包括:数据总线缓冲器、接收缓冲器、接收控制电路、发送缓冲器、发送控制电路、调制/解调控制电路、读/写控制逻辑电路等数据总线缓冲器发送缓冲器发送控制电路接收缓冲器接收控制电路D0~D7SYNDETRxDRxRDY读写控制电路C / DCLKRESETRDWRCSDSRCTSDTRRTSRxCTxCTxETxRDYTxD调制解调控制电路内部总线8251A的内部结构⏹发送器:包括发送缓冲器和发送控制电路☐采用异步方式时,则由发送控制电路自动在其首尾加上起始位、奇偶校验位和停止位,然后从起始位开始,经移位寄存器从数据输出线TxD逐位串行输出。

发送速率取决于TxC接收的发送时钟频率,可以编程定义是发送速率的1、16、64倍。

8251A的内部结构☐采用同步方式,则在发送数据之前,发送器将自动送出1个或2个同步字符,然后才逐位串行输出数据。

◆如果CPU与8251A之间采用中断方式交换信息,那么TxRDY可作为向CPU发出的中断请求信号,表示发送缓冲器已空,可以接收CPU下一个数据。

◆当发送器中的8位数据串行发送完毕时,由发送控制电路向CPU发出TxE有效信号,表示发送器中移位寄存器已空。

8251A的内部结构⏹接收器:包括接收缓冲器和接收控制电路从RxD引脚上接收串行数据转换成并行数据后存入接收缓冲器。

☐异步方式:在RxD线上检测低电平,将检测到的低电平作为起始位,8251A开始进行采样,完成字符装配,并进行奇偶校验和去掉停止位,变成了并行数据后,送到数据输入寄存器,同时发出RxRDY信号送CPU,表示已经收到一个可用的数据。

8251A的编程字(1)工作方式控制字D1D0确定是工作于同步方式还是异步方式。

D1D0=00为同步方式,当方式设为同步时,方式控制字后必须装入同步字符,并由同一个方式控制字规定装入单同步字符还是双同步字符;D1D0≠00为异步方式,且有3种组合来选择输入的时钟频率与波特率之间的系数。

D3D2确定每个字符的数据位(不包括奇偶校验位)。

D5D4确定是否校验和奇偶校验的性质。

D7D6含义因同步方式或异步方式而异。

异步方式(D1D0≠00)时用来确定停止位个数。

同步方式时D6用来确定是内同步(SYNDET脚为输出)还是外同步(SYNDET为输入),D7用来确定同步字符个数。

外同步方式时,同步字符只用于发送,接收时不作用。

例:某异步通讯,数据位为8位,1位起始位、2位停止位、奇校验、波特率系数为16。

则有:11011110B=0DEHMOV DX,309H ;8251A命令口MOV AL,0DEHOUT DX,AL(2)工作命令控制字D0设置为1允许8251A开始发送操作。

只有命令字的D0=1,引脚T X DRY(通知CPU:发送器准备好)才可能有效(为1)。

可作为发送中断屏蔽位。

D1设置为1强制引脚DTR有效,表示数据终端准备好,通知调制解调器:8251A已准备好。

D2设置为1允许8251A开始接收数据。

只有命令字D2=1,RXRDY(通知CPU接收器准备好的引脚)才有可能为1。

允许接收时必须使错误标志复位(见D4)。

在同步方式时还必须指定进入同步搜索操作(见D7)。

D3设置为1迫使TXD端发送低电平,以此作断点字符。

D4设置为1则对状态字中的所有操作出错标志(FE,OE,PE)复位。

D5设置为1强制RTS引脚(请求发送)有效,向调制解调器提出发送请求。

D6设置为1强制8251A内部复位,使之回到准备接收方式字的状态。

D7只用于同步方式。

为使8251A进入同步搜索操作,将输入的信息和同步字符比较,一致则使SYNDET/BRKDET(同步/断点检测)引脚有效,开始对数据的接收操作。

8251A的内部结构(1)接收器接收器包括接收缓冲器和接收控制逻辑两部分。

接收器的功能是接收在RXD引脚上的串行数据,并按规定的格式把它转换成并行数据,存放在数据总线缓冲器中。

①接收缓冲器接收缓冲器主要由移位寄存器和数码寄存器组成。

接收器接收传送到RXD(接收数据输入端)引脚上的串行数据,并对串行数据流的特殊位(奇偶位,停止位等)和字符(同步字符)进行检查、处理,按规定的格式将串行数据转换为并行数据存放在缓冲器中。

接收移位寄存器和接收数据缓冲器组成了双缓冲器结构。

②接收控制逻辑这一部分控制串行数据的接收,包括三条控制线:R X RDY(Receiver Ready)接收器准备好,输出,高电平有效。

R X C(Receiver Clock)接收时钟,输入。

SYNDET/BRKDET(SYNchronous DETect/BreaK DETect)同步检测/断点检测,输出/输入,高电平有效。

(2)发送器发送器包括发送缓冲器和发送控制逻辑两部分。

①发送缓冲器和发送过程发送数据缓冲器接收由CPU送来的并行数据,按初始化编程指定的数据格式转换成串行数据流送至发送移位寄存器,在TXC的下降沿从TXD引脚发送出去。

发送数据缓冲器和发送移位寄存器组成了发送的双缓冲器结构。

②发送控制逻辑该部分控制串行数据的发送操作,包括3条控制线:T X RDY(Transmitter ReaDy)发送器准备好,输出,高电平有效。

T X E(Transmitter Empty)发送器空,输出,高电平有效。

T X C(Transmitter Clock)发送时钟,输入。

(3)读/写控制逻辑读/写控制逻辑接收CPU的有关控制信号,据此确定对8251A的操作。

该部分共有6条对外引线。

CLK 时钟,输入。

RESET 复位,输入,高电平有效。

RESET有效,8251A被强行复位到空闲状态。

只有在重新初始化后才能脱离空闲状态。

(Chip Select)片选,输入,低电平有效。

简述8251a的编程结构

是一种通用异步收发器,也是一种串行通信接口芯片。

它可以实现数据的收发、控制、同步等功能。

在计算机通信领域中,8251A 被广泛应用于串行通信接口的设计中。

8251A的编程结构可以分为两部分,分别是控制寄存器和状态寄存器。

控制寄存器用于设置串行通信的参数,状态寄存器则用于反映串行通信的状态。

控制寄存器的结构如下:

| 位数 | 功能 | 说明 |

| ---- | ---- | ---- |

| 7 | DLAB | 波特率发生器访问位 |

| 6 | SB | 停止位数 |

| 5 | PE | 奇偶校验使能 |

| 4 | PM | 奇偶校验模式 |

| 3 | SM | 串行模式选择 |

| 2 | 2 | 保留 |

| 1 | 1 | 保留 |

| 0 | 1 | 保留 |

其中,DLAB位用于选择波特率发生器的访问,SB位用于选择停止位的数量,PE位用于使能奇偶校验,PM位用于选择奇偶校验模式,SM位用于选择串行通信的模式。

状态寄存器的结构如下:

| 位数 | 功能 | 说明 |

| ---- | ---- | ---- |

| 7 | FE | 帧错误 |

| 6 | OR | 溢出错误 |

| 5 | PE | 奇偶校验错误 |

| 4 | TB | 发送缓冲器空 |

| 3 | RB | 接收缓冲器满 |

| 2 | DSR | 数据终端就绪 |

| 1 | CTS | 清除发送 |

| 0 | RI | 接收到的数据 |

其中,FE位用于表示帧错误,OR位用于表示溢出错误,PE位用于表示奇偶校验错误,TB位用于表示发送缓冲器是否为空,RB位用于表示接收缓冲器是否已满,DSR位用于表示数据终端是否就绪,CTS 位用于表示清除发送,RI位用于表示接收到的数据。

在使用8251A进行串行通信时,需要对控制寄存器和状态寄存器进行编程。

具体步骤如下:

1. 设置波特率:首先要设置波特率,可以通过设置波特率发生器的值来实现。

在设置波特率时,需要先将DLAB位设置为1,然后再向数据寄存器中写入波特率发生器的值。

2. 设置数据格式:接下来需要设置数据格式,包括数据位数、奇偶校验、停止位数等。

可以通过设置控制寄存器的SB、PE、PM等位来实现。

3. 发送数据:在发送数据时,需要先判断发送缓冲器是否为空,如果为空,则可以向发送缓冲器中写入数据。

写入数据后,可以通过检测状态寄存器的TB位来判断发送缓冲器是否已满。

4. 接收数据:在接收数据时,需要先判断接收缓冲器是否已满,如果已满,则可以从接收缓冲器中读取数据。

读取数据后,可以通过检测状态寄存器的RB位来判断接收缓冲器是否已空。

总之,8251A的编程结构比较简单,只需要设置控制寄存器和读取状态寄存器即可实现串行通信的功能。

在实际应用中,需要根据具体的需求进行编程,才能实现更加灵活、高效的通信。