Nios2软核搭建

- 格式:pptx

- 大小:15.57 MB

- 文档页数:41

NIOS2完整教程NIOS II 是一款高度可配置的32位嵌入式软核处理器,由Intel旗下的Altera(现在归属于英特尔)推出。

它具有低功耗、高性能和可扩展性的特点,适用于各种嵌入式应用领域。

下面是一份简要的NIOSII完整教程,帮助您了解如何开始使用NIOSII。

1. Nios II 架构Nios II 架构包括处理器核、总线接口、存储器和外设设备。

处理器核包括CPU和一些协处理器,如乘法器、除法器等。

总线接口用于连接处理器核、存储器和外设设备。

存储器用于存储指令和数据。

外设设备包括UART、GPIO、SPI、I2C等。

2. Nios II 开发环境搭建首先,您需要安装Altera的Quartus软件来进行Nios II的开发。

Quartus提供了一个开发工具套件,包括编译器、仿真器和调试器。

您还需要安装Nios II EDS,这是一个集成开发环境,用于配置和生成Nios II处理器的软件。

安装完软件后,您可以创建一个新的Nios II项目。

3. Nios II 项目配置在Quartus中创建新的Nios II项目时,您需要指定处理器类型、时钟频率和存储器大小等参数。

您还可以选择添加外设设备和协处理器。

一旦项目创建完成,您可以使用Nios II EDS来配置处理器和外设设备,并生成相关的软件。

4. Nios II 软件开发Nios II 支持多种软件开发工具,包括C/C++编译器、汇编器和调试器。

您可以使用C/C++编译器来编写和调试应用程序。

您还可以使用汇编器来编写高性能的关键代码。

调试器可以帮助您检测和修复应用程序中的错误。

5. Nios II 系统调试在开发过程中,您可能需要进行系统调试,以解决应用程序的问题。

Nios II 支持硬件和软件调试。

硬件调试通过连接JTAG接口进行,可以在硬件级别上进行调试。

软件调试使用Nios II调试器进行,可以在软件级别上进行调试。

6. Nios II 系统验证在完成软件开发和调试后,您可以进行系统验证,确保系统的正确性和稳定性。

基于Nios Ⅱ嵌入式软核多处理器系统研究通过对硬件互斥核,程序存储器分区,重叠地址空间,启动地址和异常地址的分析,提出了多处理器系统共享片上存储器、FLASH存储器和外设资源的解决方法,为Nios Ⅱ嵌入式多处理器系统的设计提供了有效的方法和途径。

0 引言基于SoPC 技术开发的嵌入式Nios Ⅱ软核多处理器系统具有可自主设计,重构性好,软硬件裁剪容易,系统扩充升级方便,能兼顾性能、体积、功耗、成本、可靠性等方面的要求。

研发嵌入式Nios Ⅱ软核多处理器系统,是提高嵌入式系统性价比和实用性一种有效途径。

1 片上Nios Ⅱ嵌入式软核多处理器系统嵌入式系统的核心是RISC 处理器,具有代表性的RISC软核处理器是Nios Ⅱ处理器。

软核处理器是指用编程的方法生成的处理器。

是一种将硬件逻辑、智能算法、硬件描述语言和编程有机的结合出来,设计处理器硬件电路的新技术。

片上Nios Ⅱ嵌入式多处理器系统优势在于设计者可根据的实际的需要,自主选择Nios Ⅱ处理器的类型和数目并进行设置,对存储器和外围设备进行优化配置,最大限度提高片内资源和系统资源的利用率。

1.1 Nios Ⅱ处理器由Nios Ⅱ软核处理器构建的系统,对系统软硬件容易进行裁剪,并可集成在一个FPGA 芯片上,构建系统和实时评估非常迅速、方便,可大大地缩短设计周期,降低设计风险。

1.2 多处理器系统类型按共享资源分为非共享资源多处理器系统和共享资源多处理器系统两种。

非共享资源多个处理器系统中的多个Nios Ⅱ处理器完全是独立的,不共享系统资源,处理器相互之间无干扰,系统结构不太复杂。

共享资源多处理器系统在共享资源的情况下,要确保多个Nios Ⅱ处理器安全、可靠的工作,它对提高每个处理器的性能、减小体积,降低成本和功耗有利,但系统软件的设计较为复杂。

win7 64位/win7/64/按处理器拓扑结构分为2 种,一种是非层次结构,处理器与系统组件的连接容易;另一种是层次结构,它可根据实际需要来确定Nios Ⅱ处理器的数目,优化系统的内部结构,有效利用FPGA芯片的资源。

n i o s-i i-入门手册一、建立quartus ii工程首先,双击quartus ii 9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file –>New Project Wizard 出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file –>New ->Block Diagram/Schematic File 后如图1.7所示。

图1.7二、构建一个nios ii 软核(1)首先点击Tools ->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors -> Nios ii Processor 如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

源,提供“测试和设置”操作。

当处理器测试到Mutex核可用时,就会在一个具体操作中暂时占有Mutex核,之后当处理器完成对存储器的读写操许所有其他函数访问Mutex核。

Altera_avalon_mutex_trylock()

Altera_avalon_mutex_is_mine()

功能:判断CPU是否拥有Mutex

图1 双Nios II软核处理器系统体系结构图2 基于Mutex核的双核系统通信流程图 图3 SDRAM地址空间分配图图4 双Nios II软核处理器系统的配置

是我们所编写的软件程序。

在获得相关共享资源前,软件总是询问并获得Mutex 核。

2.2 软件设计

本设计中,两个处理器的软件程图5 验证程序在双核系统的运行结果理器来说,有五个主要的代码段需要映射到存储器的固定地址中:.text ,存放实际执行的代码;.r o d a t a ,存放实际执行代码中所使用的常量;.rwdata ,存放读写变量和指针;。

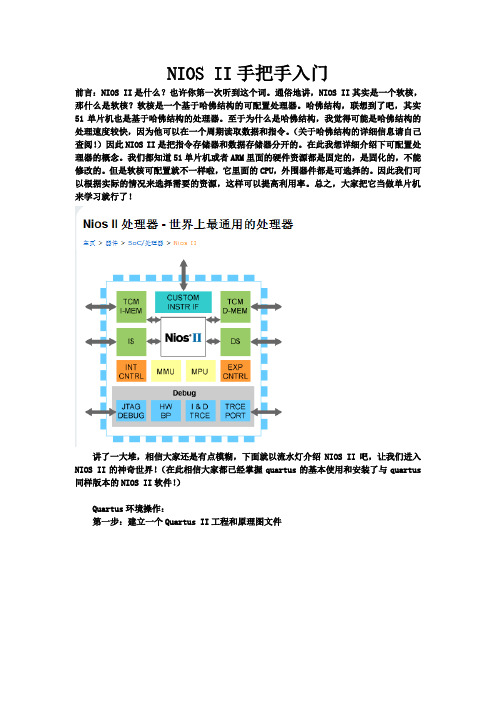

NIOS II手把手入门前言:NIOS II是什么?也许你第一次听到这个词。

通俗地讲,NIOS II其实是一个软核,那什么是软核?软核是一个基于哈佛结构的可配置处理器。

哈佛结构,联想到了吧,其实51单片机也是基于哈佛结构的处理器。

至于为什么是哈佛结构,我觉得可能是哈佛结构的处理速度较快,因为他可以在一个周期读取数据和指令。

(关于哈佛结构的详细信息请自己查阅!)因此NIOS II是把指令存储器和数据存储器分开的。

在此我想详细介绍下可配置处理器的概念。

我们都知道51单片机或者ARM里面的硬件资源都是固定的,是固化的,不能修改的。

但是软核可配置就不一样啦,它里面的CPU,外围器件都是可选择的。

因此我们可以根据实际的情况来选择需要的资源,这样可以提高利用率。

总之,大家把它当做单片机来学习就行了!讲了一大堆,相信大家还是有点模糊,下面就以流水灯介绍NIOS II吧,让我们进入NIOS II的神奇世界!(在此相信大家都已经掌握quartus的基本使用和安装了与quartus 同样版本的NIOS II软件!)Quartus环境操作:第一步:建立一个Quartus II工程和原理图文件第二步:打开配置NIOS II窗口第三步:配置NIOS II内核和外围器件(双击system contents窗口中component library下拉菜单的Nios II processor)接下来选择程序存储区和数据存储器还有通用8位IO 口。

然后配置通用IO口:(下面是选择器件区窗口,可以看到上面配置的器件!!)双击CPU,把复位矢量和异常矢量分配好:第四步:好了,到现在为止我们已经配置好一个简单的NIOS II内核,接下来就是漫长的等待吧!第五步:在原理图中添加内核symbol(其中内核复位信号是低电平复位!!)第六步:软件(C或C++)编程现在看一下NIOS II软件编写窗口吧,是不是跟单片机开发的有点类似!清空其他工程后,建立一个应用项目:file—new—Nios II C/C++ Application然后建立一个C程序文件:大家可以先把程序写下来,按下保存!等下会有相应的解释。

NIosII软处理器快速入门2007-08-15 20:18:01 来源:与非网关键字:FPGA NIosIINios简单介绍:Nios II是一个用户可配置的通用RISC嵌入式处理器。

在这儿,我引用了Altera公司关于NiosII的官方介绍:Altera推出的Nios? II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获得超过200 DMIPS的性能,用户可以从三种处理器以及超过60个的IP核中选择所需要的,Nios II系统为用户提供了最基本的多功能性,设计师可以以此来创建一个最适合他们需求的嵌入式系统。

Nios II处理器的优点和特性使用Nios II处理器的用户可以根据他们的需要来调整嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

提高系统性能* 一系列的处理器核可供选择,其中包括了超过200 DMIPS性能的核* 实现任何数量的处理器或将不同的处理器核组和在一起* 增加了已有的处理器,在FPGA中添加一个或更多的Nios II软核处理器更低的系统成本* 通过将处理器、外设、存储器和I/O接口集成到一个单一的FPGA中,从而降低了系统成本、复杂性和功耗* 通过将Nios II处理器嵌入到低成本的FPGA中只需花费35美分或者更低(编者:对大多数用户而言,NiosII所占逻辑资源的成本大约是10-20元人民币,具体取决于所选FPGA 的类型和NiosII的配置)应对产品的生命周期* 提供易用的设计工具从而快速将产品推向市场。

* 提供永久的,免费的许可从而使基于Nios II处理器的产品避免了处理器的更新换代而带来的损失。

功能强大、易用的开发工具* 通过使用Nios II集成开发环境(IDE),从而加速了软件的开发* 利用Altera的强大的SOPC Builder系统开发工具和Quartus II设计软件可以在几分钟内设计一个系统使用完全功能的开发包* 使用易用的Nios II 开发包开始一个设计* 使用易用的Nios II开发包开始设计* 可以选择具有低成本特性的Cyclone FPGA开发套件,或高性能的Stratix FPGA开发套件稍微了解一下NiosII后,我们就来开始设计、应用它吧!下面我们就设计一个最简单的NiosII系统,使用NiosII去控制一个LED灯,通过这个例子我们可以了解整个介绍NiosII的设计流程第一节:EDA软件的安装。

NiosII软件设计与运行流程本实验是于实验1相连的,本实验主要完成在NiosII硬件系统完成及下载于FPGA中的基础上,进行软件开发、下载和调试,具体流程如下:1、向FPGA下载配置文件。

以下的实验将更多地与SOPC实验系统联系。

本次实验是使用清华大学电工电子实验中心的GW48-SOPC实验系统(康芯公司),下载前连接好下载通信线,打开电源,打开光盘上关于此实验系统的PDF/PPT默认设置说明,确认实验系统所有开关和跳线处于默认设置位置。

用10芯通信线将实验系统左侧的“Byterblaster II”接口与适配板上的JTAG Port口相连;将实验系统左侧的跳线短路帽接插“ByBt II”端,编程电压选择跳线短路帽插3.3V(此电压接错不会损坏系统)。

按动实验系统左下角的电路模式控制键,选择模式5(在上方的数码管会显示5字),这时实验系统将进入附录中附图1的电路连接模式(有12中不同的可选硬件电路模式)。

注意模式5的8个键控特点:每按键一次,输出电平反相一次,电平高低由此键上方的发光管显示;还注意到此时FPGA输出的32个I/O口接了8个数码管,每4个I/O口接一个数码管,且在每一数码管外接了一个16进制至7段译码的译码器,这样可以大大节省I/O口的耗用。

FPGA的主要端口是用标准信号名PIOx标注的,具体引脚号在引脚锁定时查阅附录的附表1;例如附图1中连接FPGA的键8端口标准信号名是“PIO7”,查附表1,横项GW48-SOPC对应Pin240。

现在可以开始下载配置文件,以便在FPGA中建立NiosII硬件环境。

打开QuartusII,再打开实验一的工程,选择菜单Tools→Programmer,弹出图2-1所示窗口,首先选择接口模式,对于Mode栏确认选择JTAG模式;如果是首次安装并使用该软件,要作下载接口模式选择:点击图2-1左侧的Hardware Setup按纽,将弹出图2-2所示窗口。

Nios II软核处理器快速入门(实践篇)重要提示:开始之前请确认已经安装了Altera Quartus II 5.0和Altera Nios II 5.01集成开发环境,以及有效的license文件。

详细阅读目标板原理图。

内容特点:本文以实例方式详细介绍了如何创建Nios II软核处理器及简单应用。

启动Quartus II,选择File -> New Project Wizards,开始项目向导,如下图:Next进入下一个向导,填入你的项目名称和文件夹位置,如下图:Next进入下一个向导,这是一个添加设计文件向导,如下图:由于现在我们没有任何的设计文件可以添加,直接Next进入下一个向导,这是一个选择目标板上器件型号向导,根据我们使用的目标板,请选择EP1C6T144C8,如下图:完成目标器件添加后,Next进入下一个向导,这是一个EDA toos向导,如下图:根据实际情况,如果没有EDA tool,请直接Next进入下一个向导,如下图:Finish完成新建工程。

通过File -> New建立一个新的SCH文件,如下图:将其另存为你需要的文件名称。

接着进行器件和管脚设置,通过Assigned -> Device菜单进入下面的对话框。

然后按“Device & Pin Options…”按钮设置相关选项。

由于我们的目标板将INIT_DONE管脚分配给了Button使用,如果这个选项被选中,我们需要去掉Enable INIT_DONE output前的钩,如下图:我们的目标板使用了EPCS1配置器件,因此在“Configuration”中的“Use configuration device”栏中需要选择EPCS1,如下图:由于我们的目标板上FPGA的管脚还接入了其它器件,在此工程中未使用到,因此需要在“Unused Pins”中选择“As inputs,tri-stated”(非常重要,否则有可能造成目标板上的器件烧毁!!!),如下图:然后按“确定”按钮,再“OK”按钮退出器件设置。